HC4020 14 STAGE BINARY COUNTER

HC4040 12 STAGEBINARY COUNTER

.HIGH SPEED

f

= 73 MHz (TYP.) at VCC=5V

MAX

.LOWPOWER DISSIPATION

ICC=4µA(MAX.) at TA=25oC

.HIGH NOISE IMMUNITY

V

NIH=VNIL

=28%VCC(MIN.)

.OUTPUT DRIVE CAPABILITY

10 LSTTL LOADS

.SYMMETRICAL OUTPUT IMPEDANCE

|IOH|=IOL=4 mA (MIN.)

.BALANCEDPROPAGATION DELAYS

t

PLH=tPHL

.WIDE OPERATING VOLTAGE RANGE

VCC(OPR)= 2 V to 6 V

.PIN AND FUNCTION COMPATIBLE WITH

4020B/4040B

DESCRIPTION

The M54/74HC4020/HC4040 are high speed

CMOS 14/12-STAGE BINARY COUNTER

fabricated in silicon gate C2MOStechnology. They

have the same high speed performance of LSTTL

combined with true CMOSlow consumption.

A clear input is used to reset the counter to the all

lowlevelstate.Ahighlevelon CLEARaccomplishes

the reset function. A negative transition on the

CLOCKinput incrementsthe counterby one.

For HC4020 twelve kind od divided output are

provided; 1st and 4th stage to 14th stage.

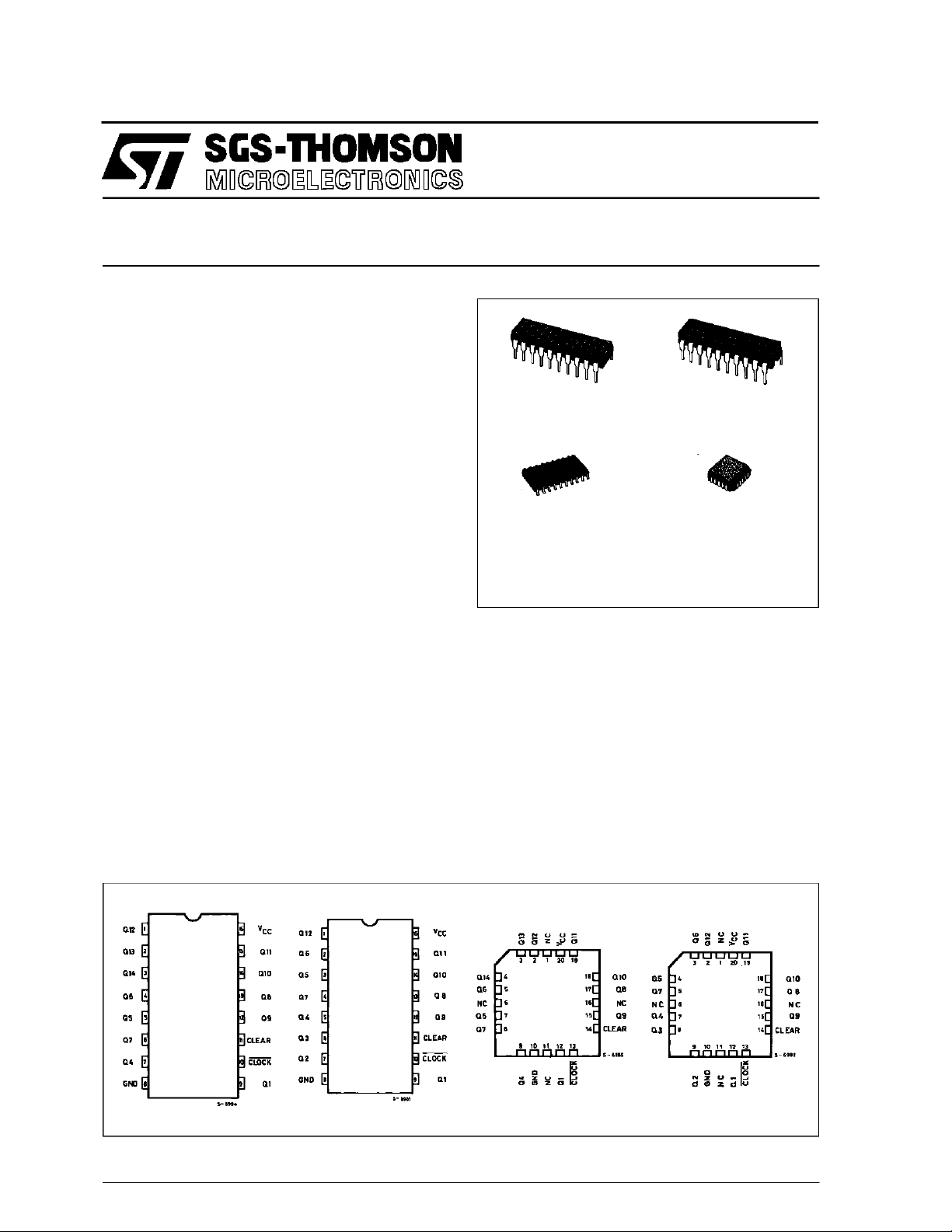

M54/74HC4020

M54/74HC4040

B1R

(PlasticPackage)

M1R

(MicroPackage)

ORDER CODES :

M54HC X XXF1R M74HC XXXM1R

M74HC X XXB1R M74HCXXXC1R

The maximum division available at last stage is

1/16384 x fINatclock.

For HC4040 each division stage has an output; the

final frequency is 1/4096 xfIN.

All inputs are equipped with protection circuits

against static discharge and transient excess

voltage.

F1R

(CeramicPackage)

C1R

(Chip Carrier)

PIN CONNECTION (top view)

HC4 020 HC4 040 HC4020 HC4040

March1993

1/13

M54/M74HC4020/4040

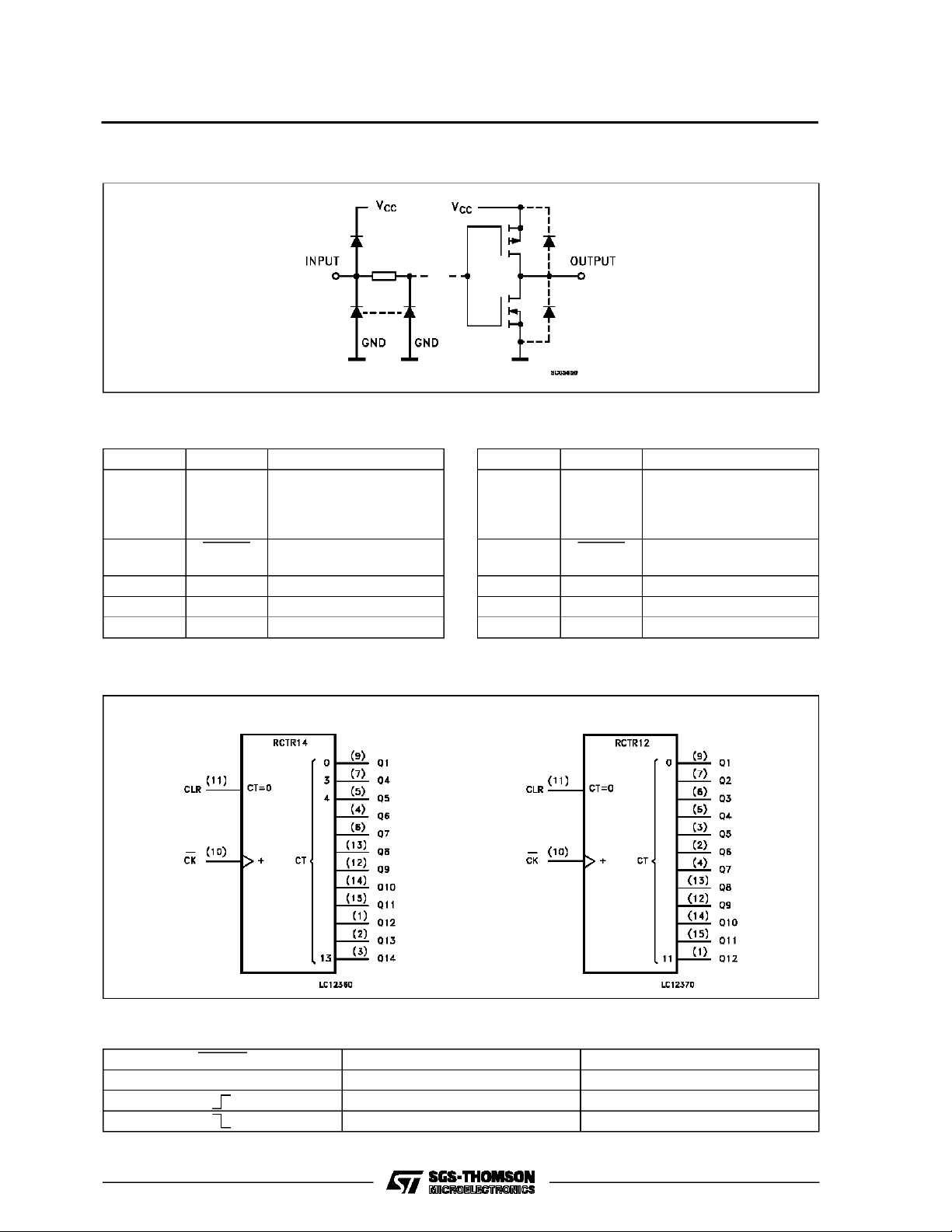

INPUT AND OUTPUT EQUIVALENT CIRCUIT

PIN DESCRIPTION (HC4020)

PIN No SYMBOL NAME AND FUNCTION

9, 7, 6, 5,

3, 2, 4, 13,

12, 14, 15,

1

10 CLOCK Clock Input (LOW to

11 CLEAR Reset Inputs

8 GND Ground (0V)

16 V

Q1, Q4 to

Q14

CC

Parallel Outputs

HIGH, edge triggered)

Positive Supply Voltage

IEC LOGIC SYMBOLS

HC4020 HC404 0

PIN DESCRIPTION (HC 4040)

PIN No SYMBOL NAME AND FUNCTION

9, 7, 6, 5,

3, 2, 4, 13,

12, 14, 15,

1

10 CLOCK Clock Input (LOW to

11 CLEAR Reset Inputs

8 GND Ground (0V)

16 V

Q1 to Q12 Parallel Outputs

HIGH, edge triggered)

CC

Positive Supply Voltage

TRUTH TABLE

CLOCK CLEAR OUTPUT STATE

2/13

X H ALL OUTPUTS = ”L”

L NO CHANGE

L ADVANCE TO NEXT STATE

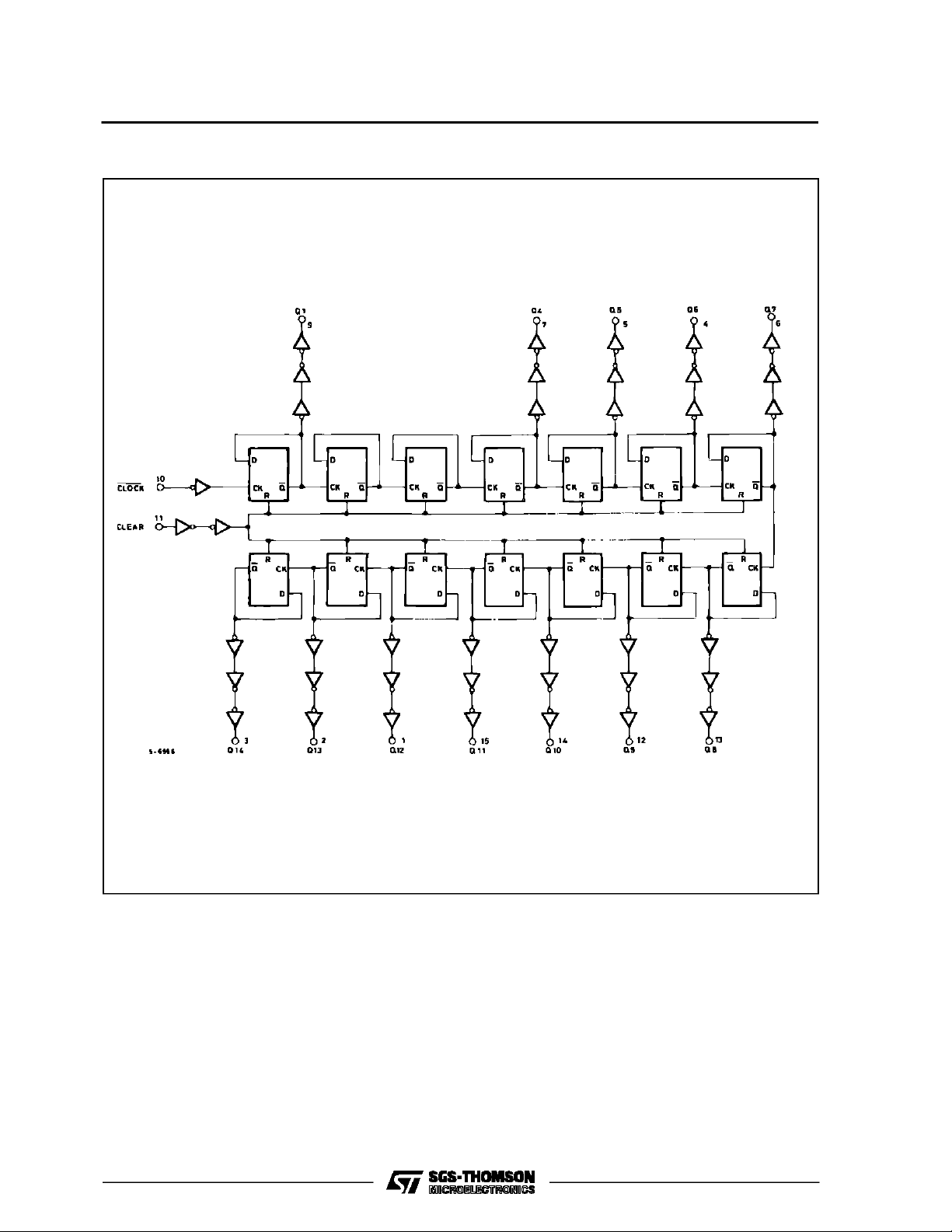

LOGIC DIAGRAM (HC4020)

M54/M74HC4020/4040

3/13

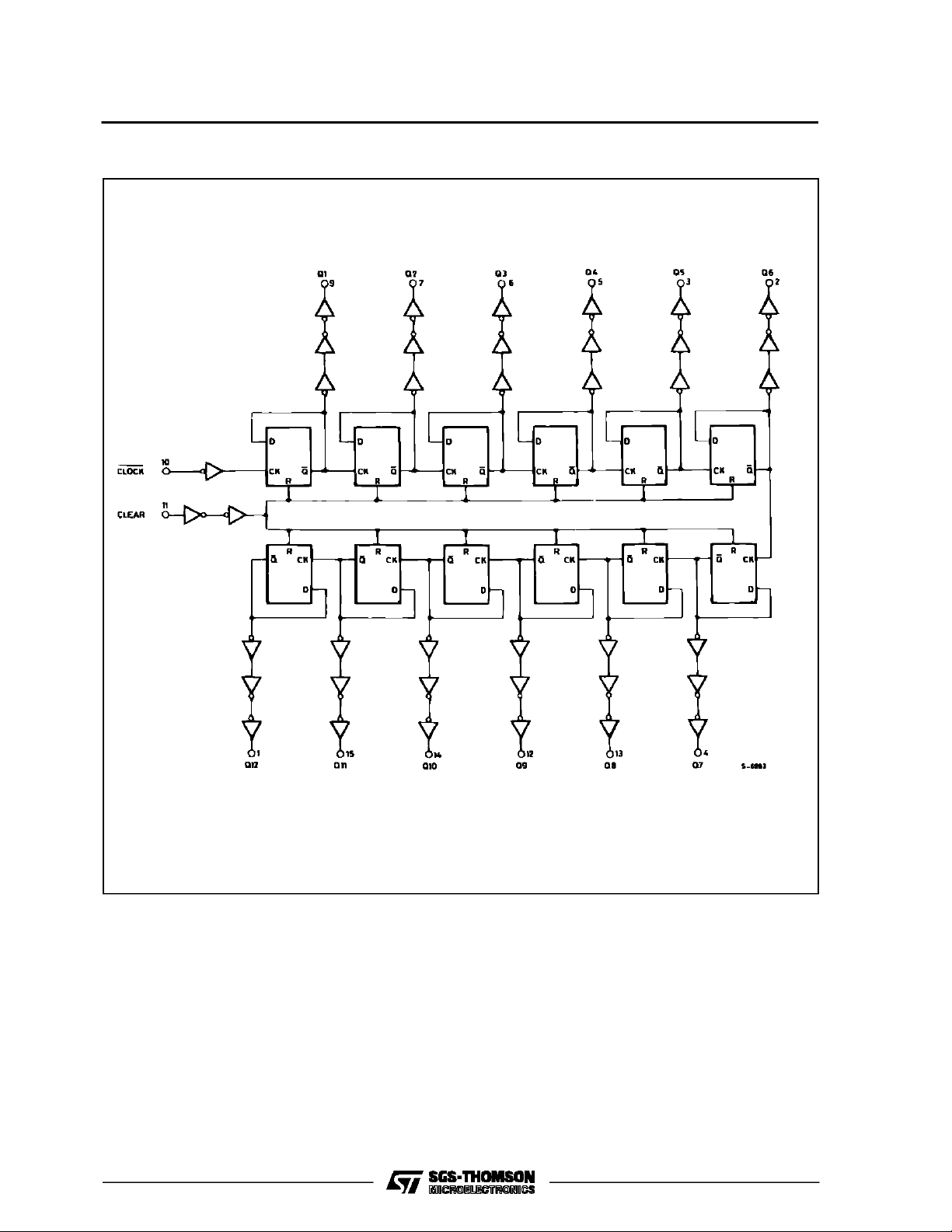

M54/M74HC4020/4040

LOGIC DIAGRAM (HC4040)

4/13

Loading...

Loading...