M54/74HC299

M54/74HC323

HC2998 BIT PIPOSHIFTREGISTERWITHASYNC HRONOUS CLEAR

HC3 23 8BITPIPOSH IFTREGI STERWITHSYN CHRO NOU S CL EAR

.HIGH SPEED

f

= 42 MHz(TYP.) ATVCC=5V

MAX

.LOWPOWERDISSIPATION

ICC=4µA (MAX.) AT TA=25°C

.HIGH NOISEIMMUNITY

V

NIH=VNIL

.OUTPUT DRIVECAPABILITY

10 LSTTL LOADS FOR QA’TO QH’

15 LSTTL LOADS FOR QATO QH

=28%VCC(MIN.)

B1R

(PlasticPackage)

F1R

(CeramicPackage)

.SYMMETRICALOUTPUT IMPEDANCE

IOH =IOL= 6mA(MIN.) FORQA,TOQH,

IOH =IOL= 4mA(MIN.) FORQA,TOQ

.BALANCEDPROPAGATION DELAYS

t

PLH=tPHL

.WIDE OPERATING VOLTAGE RANGE

VCC(OPR)= 2 V TO 6 V

.PIN AND FUNCTIONCOMPATIBLE

WITH 54/74LS299

H

M1R

(MicroPackage)

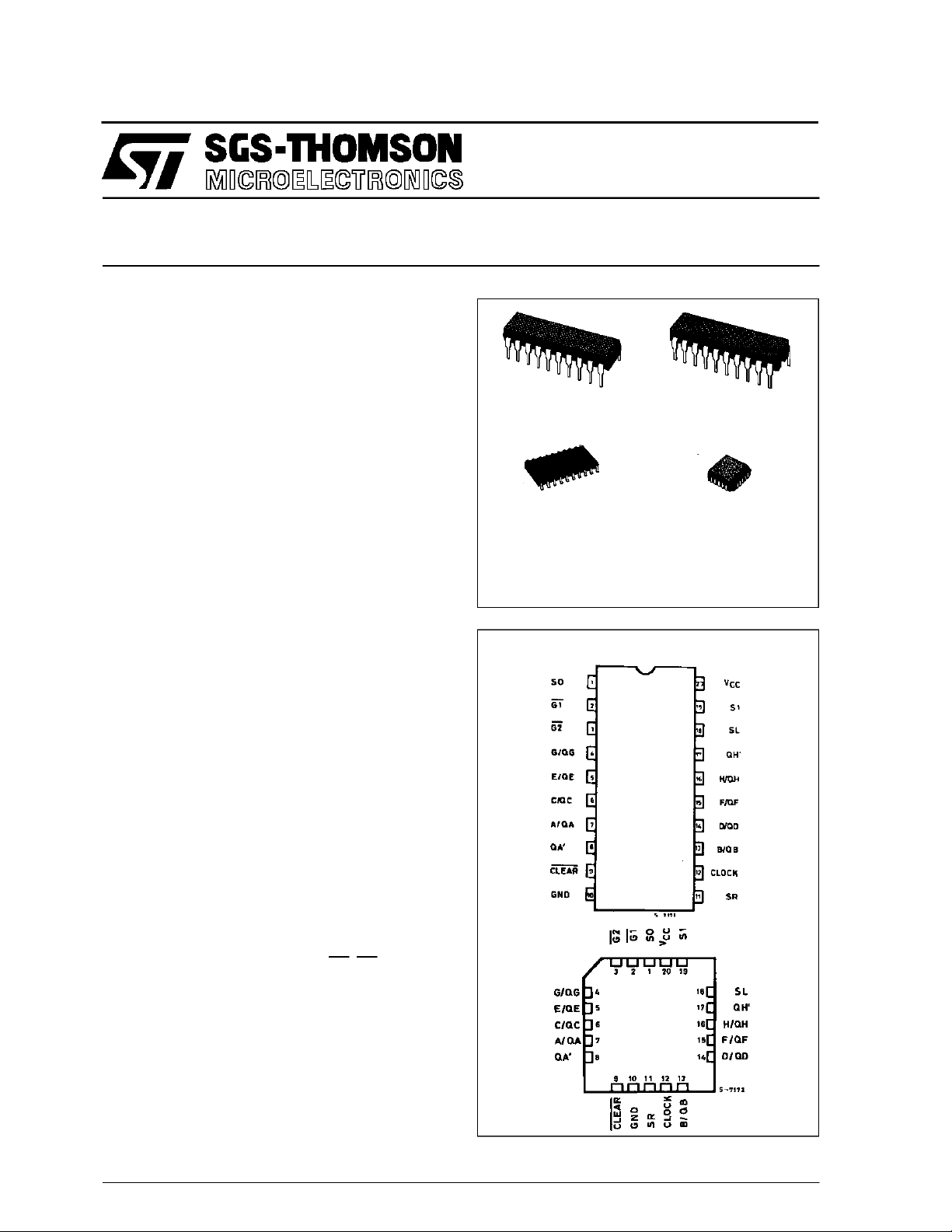

ORDER CODES :

M54HC X XXF 1 R M74H CXXXM1 R

M74HC X XXB1R M74H CXXXC1R

C1R

(Chip Carrier)

DESCRIPTION

The M54/74HC299/323 are high speed CMOS 8BIT PIPO SHIFT REGISTERS (3-STATE) fabricated withsilicon gateC2MOS technology.

They achieve the high speed operation similar to

equivalent LSTTL whilemaintaining the CMOS low

powerconsumption.

These devices have four modes (HOLD, SHIFT

LEFT,SHIFTRIGHTandLOADDATA).Eachmode

is chosen by two function select inputs (S0, S1).

When one orboth enableinputs, (G1, G2)are high,

the eight input/output terminals are in the highimpedance state ; however sequential operation or

clearing of the register is not affected.

Clear function on the HC299 is asynchronous to

CLOCK,while theHC323iscleared synchronous to

clock.

All inputs are equipped with protection circuits

against static discharge and transient excess voltage.

PIN CONNECTIONS(top view)

NC =

No Internal

Connection

October 1993

1/15

M54/M74HC299/323

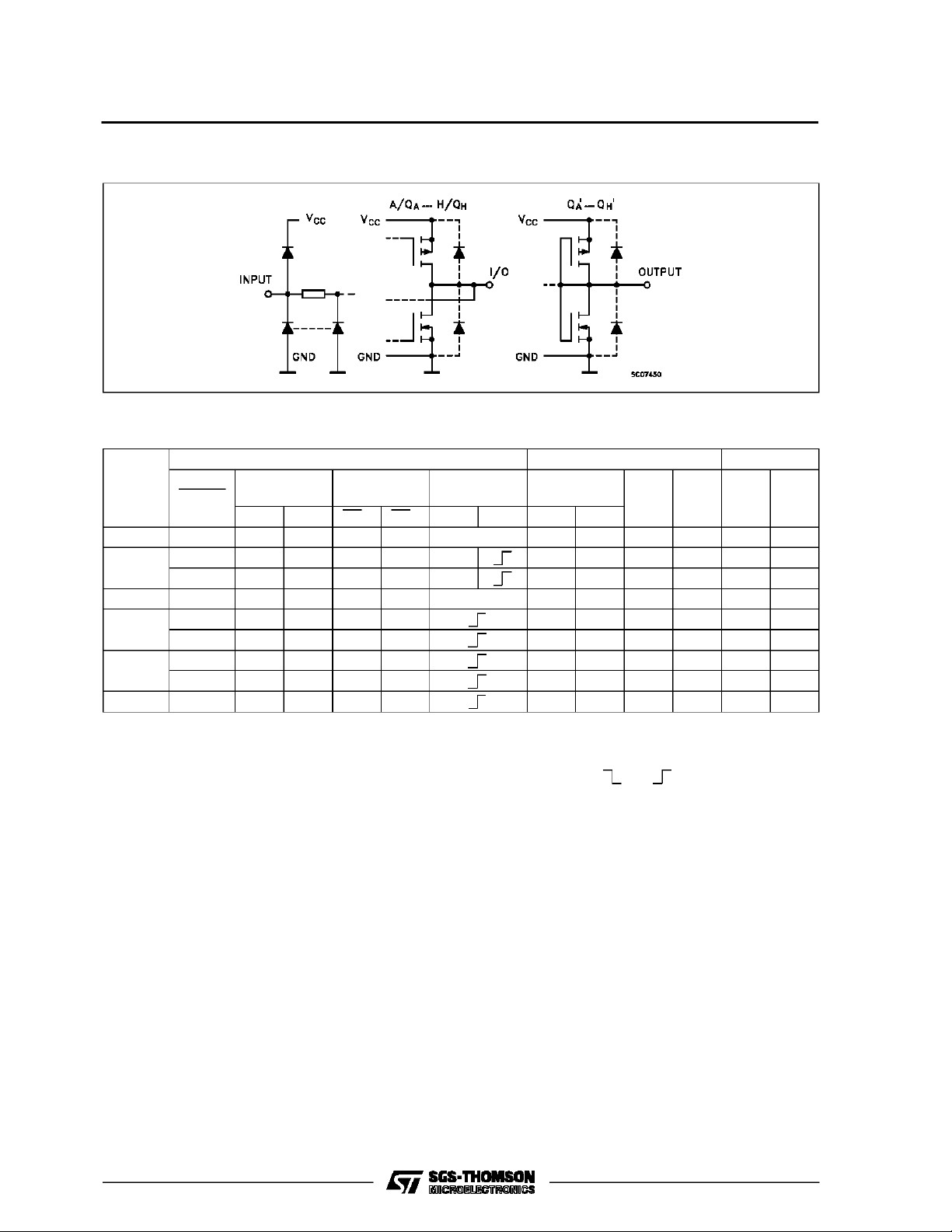

INPUT AND OUTPUT EQUIVALENT CIRCUIT

TRUTH TABLE

INPUTS INPUTS/OUTPUTS OUTPUTS

MODE

CLEAR

FUNCTION

SELECTED

S1 S0 G1 * G2 * (299) (323) SL SR

ZLHHXXXXXZZLL

CLEAR

L LXLLX XXLLLL

L XLLLX XXLLLL

HOLD H L L L L X X X QA0 QH0 QA0 QH0

SHIFT

RIGHT

SHIFT

LEFT

H L H L L X H H QGn H QGn

H L H L L X L L QGn L QGn

H H L L L H X QBn H QBn H

H H L L L L X QBn L QBn L

LOAD H H H X X X X a h a h

* When oneorboth output controls arehigh, theeight, input/outputterminalsareinthehighimpedance state: however sequential operationorclearing

of the registeris not affected.

Z : HIGHIMPEDANCE

Qn0 : THELEVELOF An BEFORE THE INDICATEDSTEADYSTATEINPUT CONDITIONSWERE ESTABLISHED.

Qnn : THELEVELON Qn BEFORETHE MOST RECENTACTIVETRANSITION INDICATEDBY OR

a, h : THELEVEL OFTHE STEADYSTATEINPUTS A, H,RESPECTIVELY.

X : DON’TCARE

OUTPUT

CONTROL

CLOCK SERIAL

A/QA H/QH QA’ QH’

2/15

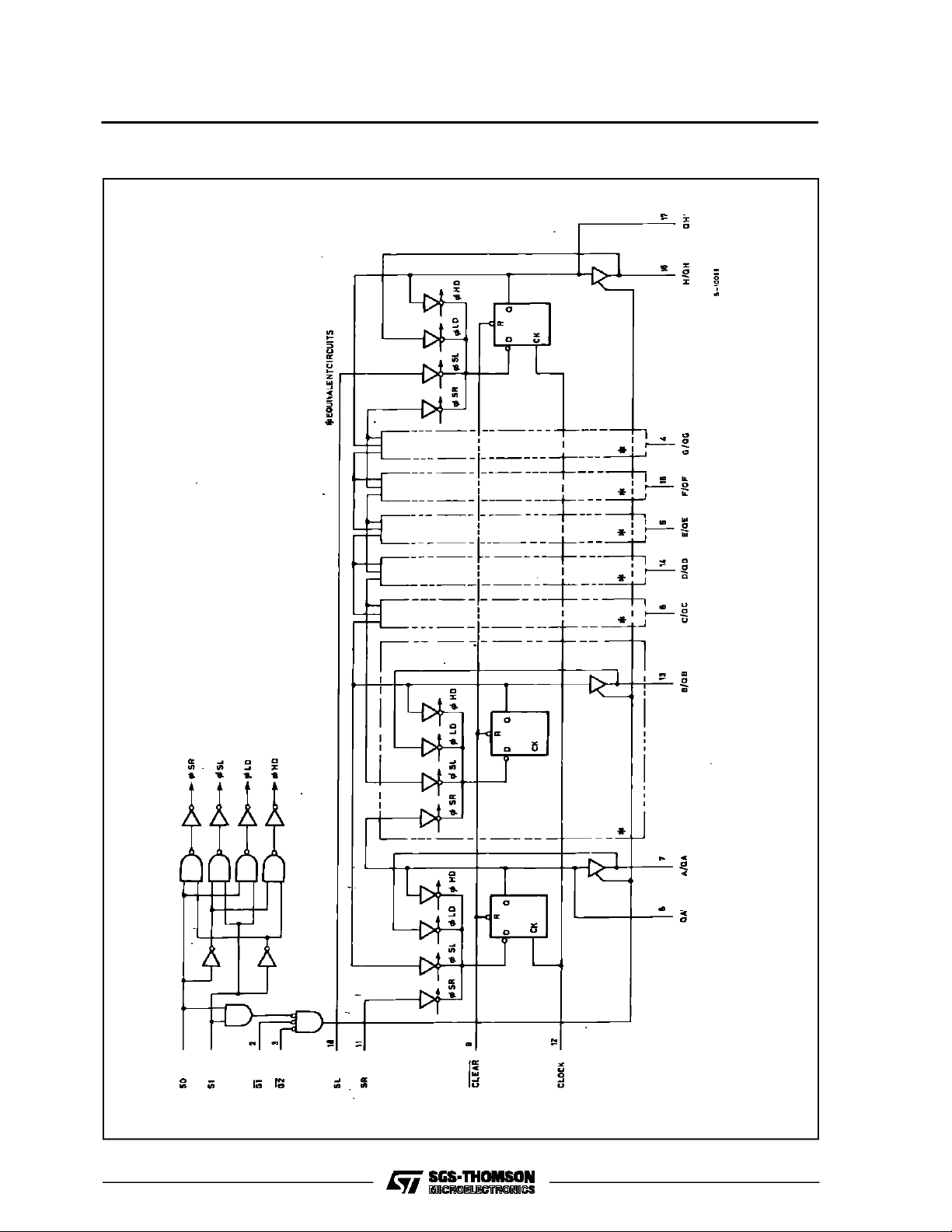

LOGIC DIAGRAM (HC 299)

M54/M74HC299/323

3/15

M54/M74HC299/323

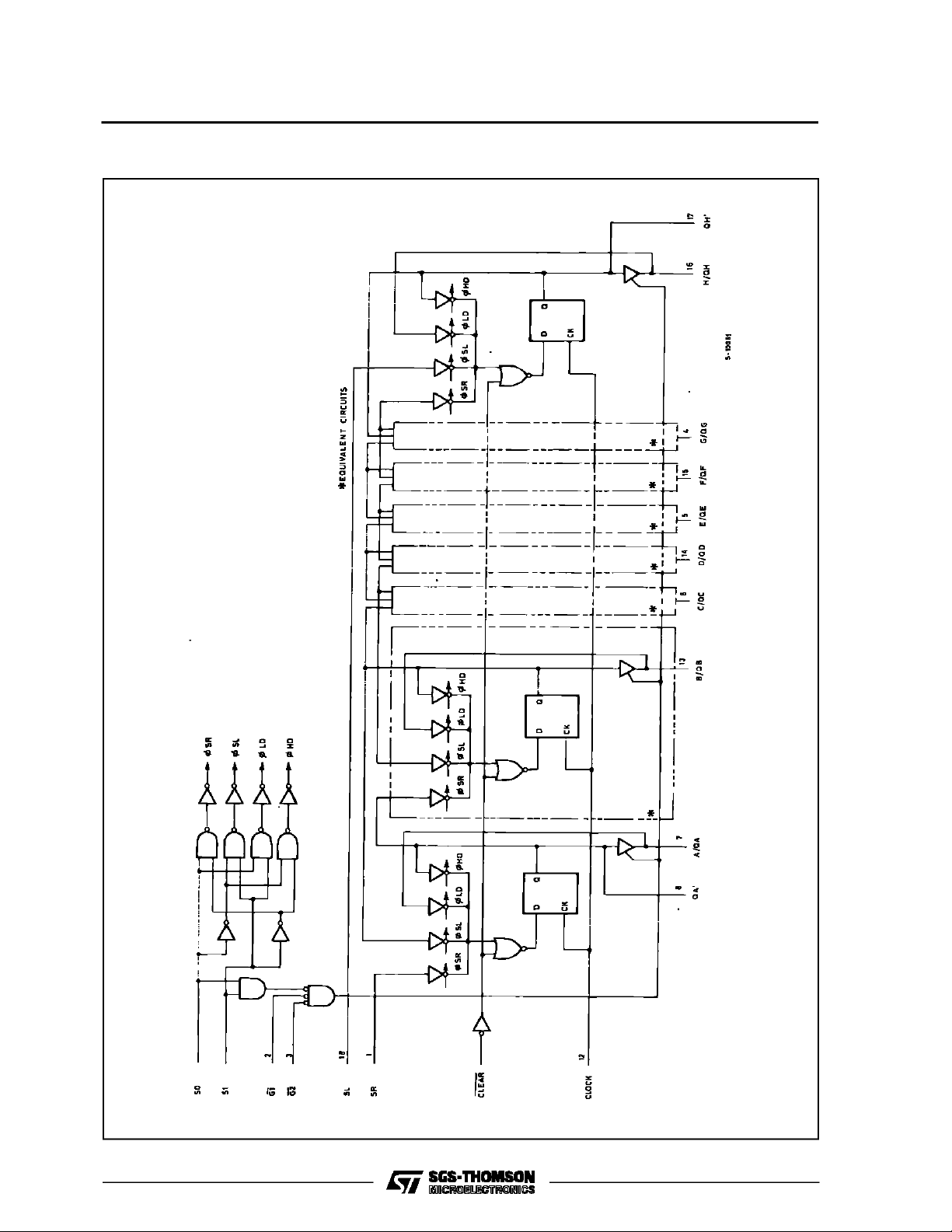

LOGIC DIAGRAM (HC 323)

4/15

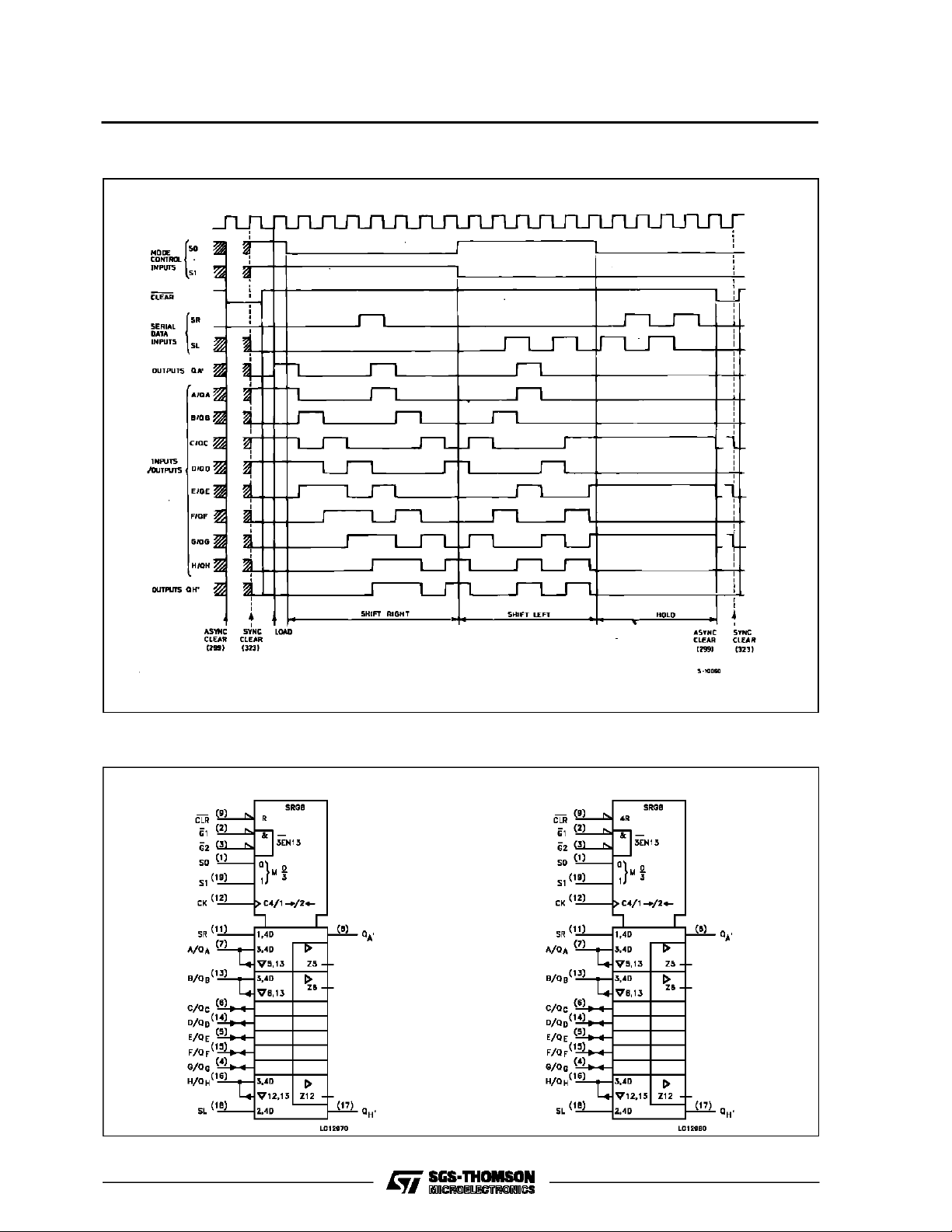

TIMING CHART

M54/M74HC299/323

IEC LOGIC SYMBOLS

HC299 HC299

5/15

Loading...

Loading...