.HIGH SPEED

tPD= 12 ns(TYP.) AT VCC=5V

.LOWPOWERDISSIPATION

ICC=4µA(MAX.) AT TA=25°C

.OUTPUTDRIVE CAPABILITY

10 LSTTL LOADS

.SYMMETRICALOUTPUT IMPEDANCE

IOH =IOL= 4 mA(MIN.)

.BALANCEDPROPAGATION DELAYS

t

PLH=tPHL

.HIGH NOISE IMMUNITY

V

NIH=VNIL

=28%VCC(MIN.)

.WIDE OPERATINGVOLTAGE RANGE

VCC(OPR)= 2 V TO6 V

.PIN ANDFUNCTION COMPATIBLE

WITH 54/74LS194

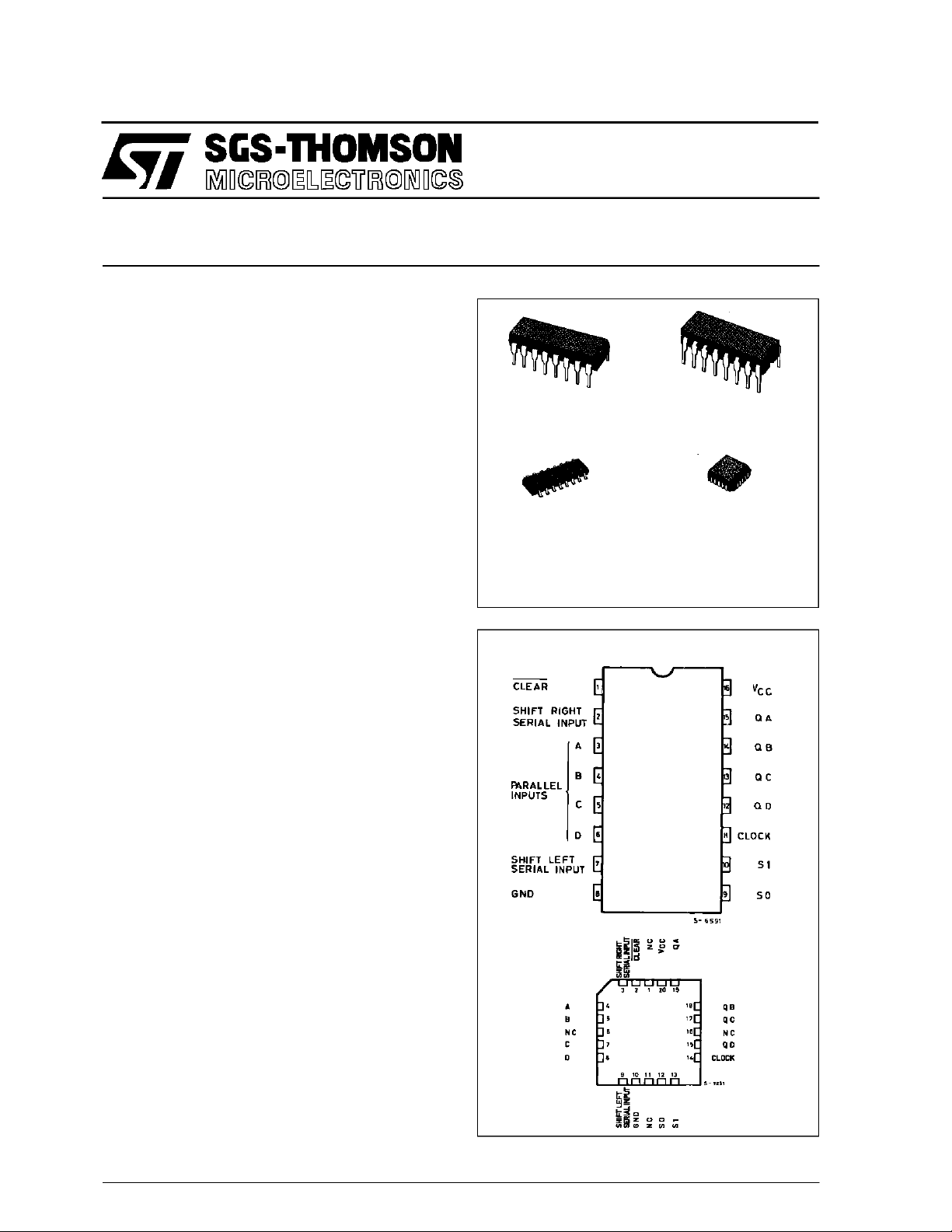

M54HC194

M74HC194

4 BITPIPO SHIFT REGISTER

B1R

(PlasticPackage)

M1R

(MicroPackage)

ORDER CODES :

M54HC 194F1R M74H C194M1R

M74HC 194B1R M74HC1 94C1R

F1R

(CeramicPackage)

C1R

(Chip Carrier)

DESCRIPTION

TheM54/74HC194 isahighspeedCMOS4BITPIPO

SHIFTREGISTER fabricated insilicongate C2MOS

technology. It has the same high speed performance

ofLSTTLcombined withtrue CMOSlowpowerconsumption.This SHIFT REGISTER is designed to incorporatevirtuallyallofthefeaturesasystemdesigner

maywantina shiftregister. Itfeatures parallel inputs,

parallel outputs, right shift and left shift serial inputs,

clearline.Theregisterhas fourdistinctmodesofoperation: PARALLEL (broadside) LOAD;SHIFTRIGHT

(in the direction QAQD); SHIFT LEFT ; INHIBIT

CLOCK(donothing).Synchronous parallel loadingis

accomplishedbyapplyingthefourdatabitsandtaking

bothmode control inputs, S0 and S1 high.The data

areloaded intotheir respective flip-flops and appear

at the outputs after the positive transition of the

CLOCK input. During loading, serial data flow is inhibited.Shiftright isaccomplished synchronouslywith

therising edge oftheclockpulsewhenS0is highand

S1 is low.Serial dataforthis mode is entered at the

SHIFTRIGHTdata input. When S0 is lowand S1 is

high,datashiftsleftsynchronously andnewdataisentered at the SHIFT LEFTserialinput. Clockingof the

flipflopsisinhibitedwhenbothmodecontrolinputsare

low.The modecontrol inputs should bechangedonly

whentheCLOCKinput ishigh. Allinputsareequipped

with protection circuits against static discharge and

transientexcessvoltage.

NC =

No Internal

Connection

PIN CONNECTIONS(top view)

October 1992

1/12

M54/M74HC194

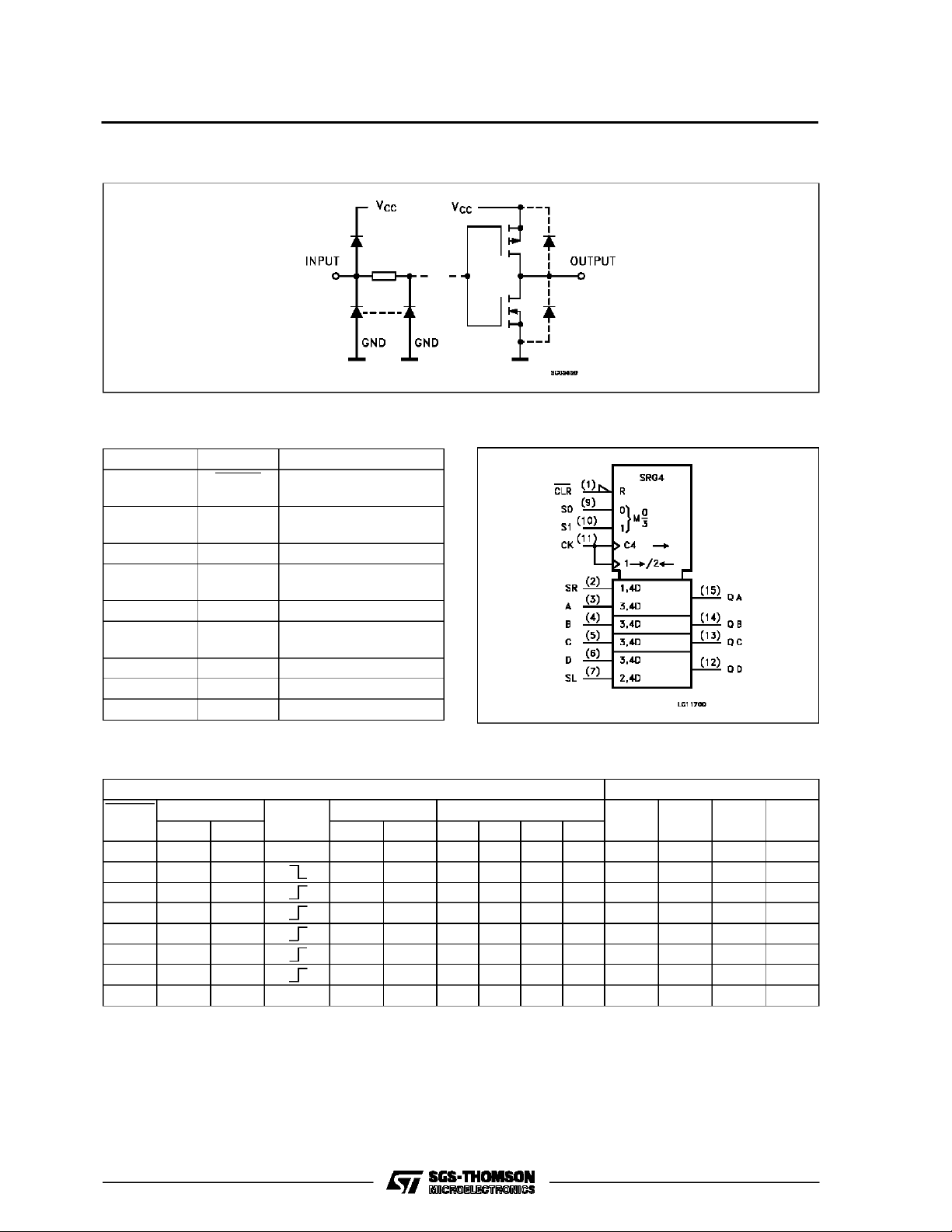

INPUT AND OUTPUT EQUIVALENT CIRCUIT

PIN DESCRIPTION

PIN No SYMBOL NAME AND FUNCTION

1 CLEAR Asynchronous Reset

Input (Active LOW)

2 SR Serial Data Input (Shift

Right)

3, 4, 5, 6 A to D Parallel Data Input

7 SL Serial Data Input (Shift

Left)

9, 10 S0, S1 Mode Control Inputs

11 CLOCK Clock Input (LOW to

HIGH Edge-triggered)

15, 14, 13, 12 QA to QD Paralle Outputs

8 GND Ground (0V)

16 V

CC

Positive Supply Voltage

IEC LOGIC SYMBOL

TRUTH TABLE

INPUTS OUTPUS

CLEAR MODE

S1 S0 LEFT RIGHT ABCD

L X X X X X XXXX L L L L

H X X X X XXXXQA0QB0QC0QD0

H H H X X abcd a b c d

H L H X H XXXX HQAnQBnQCn

H L H X L XXXX L QAnQBnQCn

H H L H X XXXXQBnQCnQDnH

H H L L X XXXXQBnQCnQDnL

H L L X X X XXXXQA0QB0QC0QD0

X: Don’t Care : Don’t Care

a ~d : The level of steady state input voltage at inputA ~ D respactively

QA0~ QD0 : No change

QAn~ QDn : The level of QA, QB,QC, respectively, before themst recent positive transition oftheclock.

CLOCK

SERIAL PARALLEL

QA QB QC QD

2/12

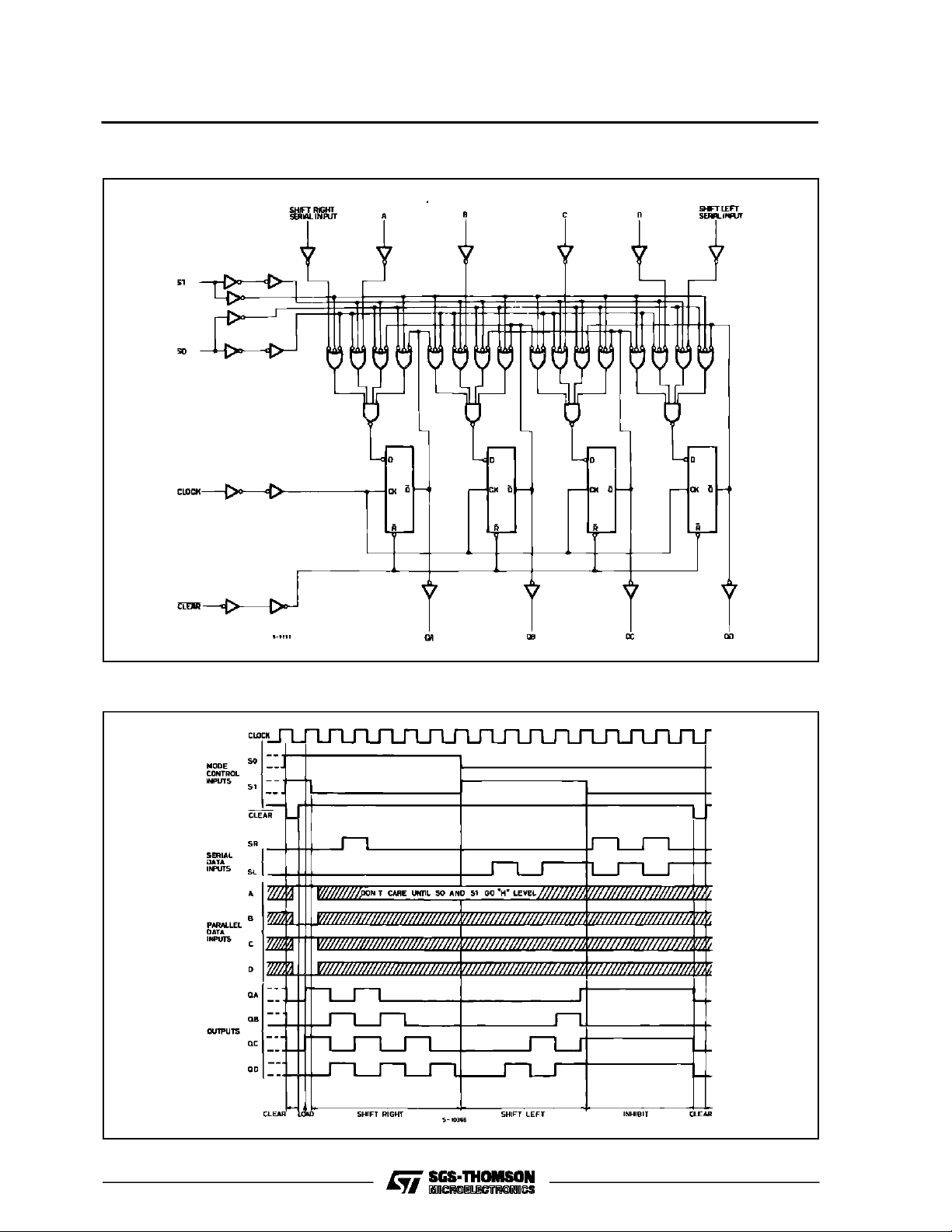

LOGIC DIAGRAM

M54/M74HC194

TIMING CHART

3/12

M54/M74HC194

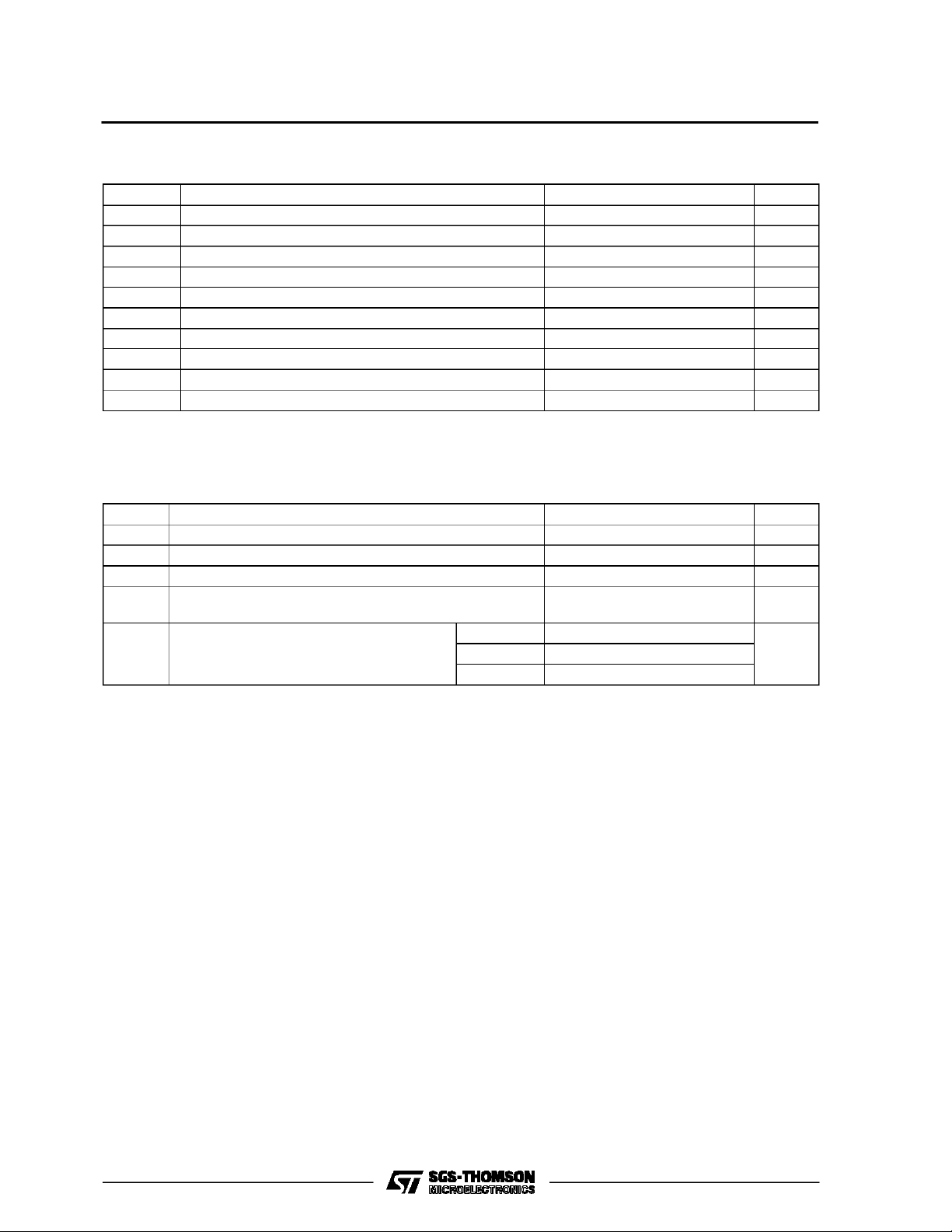

ABSOLU TE MAXIMU M RATINGS

Symbol Parameter Value Unit

V

CC

V

V

O

I

IK

I

OK

I

O

I

or I

CC

P

D

T

stg

T

L

AbsoluteMaximumRatingsarethose values beyondwhichdamage tothedevicemayoccur. Functionaloperationunder these conditionisnotimplied.

(*)500 mW: ≅ 65oC derateto300mWby 10mW/oC: 65oCto85oC

RECO MM ENDED O PERAT IN G C O NDITI O NS

Symbol Parameter Value Unit

V

CC

V

I

V

O

T

op

t

r,tf

Supply Voltage -0.5 to +7 V

DC Input Voltage -0.5 to VCC+ 0.5 V

I

DC Output Voltage -0.5 to VCC+ 0.5 V

DC Input Diode Current ± 20 mA

DC Output Diode Current ± 20 mA

DC Output Source Sink Current Per Output Pin ± 25 mA

DC VCCor Ground Current ± 50 mA

GND

Power Dissipation 500 (*) mW

Storage Temperature -65 to +150

Lead Temperature (10 sec) 300

Supply Voltage 2 to 6 V

Input Voltage 0 to V

Output Voltage 0 to V

Operating Temperature: M54HC Series

M74HC Series

CC

CC

-55 to +125

-40 to +85

Input Rise and Fall Time VCC= 2 V 0 to 1000 ns

V

= 4.5 V 0 to 500

CC

V

= 6 V 0 to 400

CC

o

C

o

C

V

V

o

C

o

C

4/12

Loading...

Loading...