FUNCTION LOOK AHEAD CARRY GENERATOR

.HIGH SPEED

tPD= 14 ns(TYP.) at VCC=5V

.LOWPOWER DISSIPATION

ICC=4µA(MAX.) at TA=25°C

.HIGH NOISE IMMUNITY

V

NIH=VNIL

=28%VCC(MIN.)

.OUTPUT DRIVE CAPABILITY

10 LSTTL LOADS

.SYMMETRICAL OUTPUT IMPEDANCE

IOH =IOL= 4 mA(MIN.)

.BALANCEDPROPAGATION DELAYS

t

PLH=tPHL

.WIDE OPERATING VOLTAGE RANGE

VCC(OPR)= 2 V to 6 V

.PIN ANDFUNCTION COMPATIBLE

WITH 54/74LS182

DESCRIPTION

The M54/74HC182 is a high speed CMOS FUNCTION LOOK AHEAD CARRY GENERATOR

fabricated insilicongate C2MOStechnology. It has

the same high speed performance of LSTTL combined with true CMOS low power consumption.

These circuit are capable of anticipating a carry

acrossfour binary addersor group of adders. They

arecascadable to perform full look-ahead across nbit adders. Carry, generate-carry, and

propagate-carry functions are providedas shown in

the pinconnection table. When used in conjunction

with the HC181 arithmetic logic unit, these generators provide high-speed carry look-ahead

capability for any word length. Each HC182 generates the look-ahead (anticipated carry) across a

groupoffourALU’sand,inaddition, othercarrylookaheadcircuits may be employed toanticipate carry

across sections of four look-ahead packages up to

n-bits. Themethod of cascading circuits to perform

multi-levellook-ahead isillustrated under typical application data.

Carry input and outputof the ALUs are in their true

form, andthe carrypropagate (P) and carrygenerate (G) are in negated form ; therefore, the carry

functions(inputs, outputs,generate, andpropagate)

of the look-ahead generators are implemented in

the compatible forms for direct connection to the

ALU. Reinterpretation of carry functions as explained ontheHC181datasheetarealsoapplicable

toandcompatible withthelook-aheadgenerator. All

inputs areequipped with protection circuits against

staticdischarge and transient excess voltage.

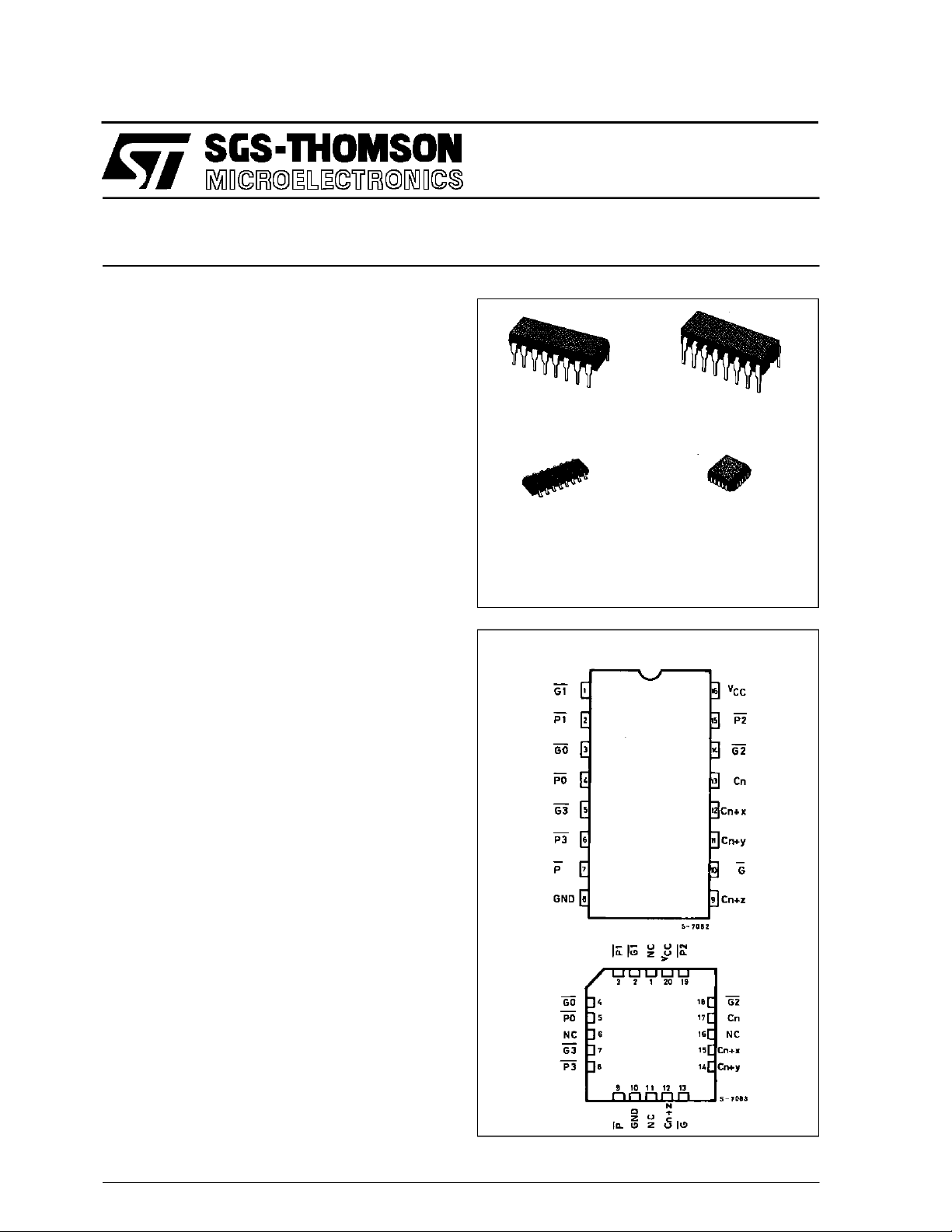

M54HC182

M74HC182

B1R

(PlasticPackage)

M1R

(MicroPackage)

ORDER CODES :

M54HC 182F1R M74H C182M1R

M74HC 182B1R M74HC1 82C1R

PIN CONNECTIONS(top view)

NC =

No Internal

Connection

F1R

(CeramicPackage)

C1R

(Chip Carrier)

March1993

1/12

M54/M74HC182

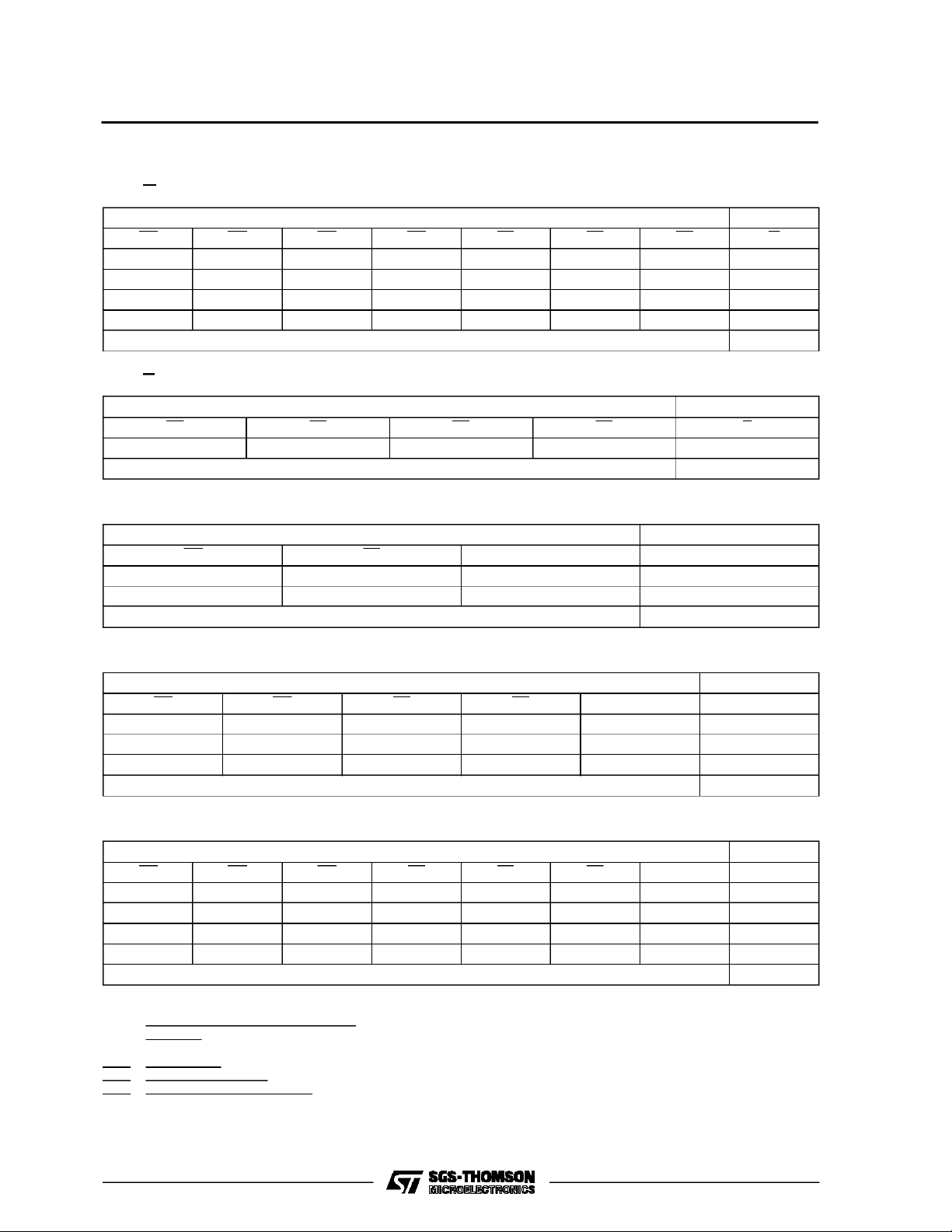

FUNCTION TABLES

FOR G OUTPUT

INPUTS OUTPUT

G3 G2 G1 G0 P3 P2 P1 G

LXXXXXXL

XLXXLXXL

XXLXLLXL

XXXLLLLL

ALL OTHER COMBINATIONS H

FOR P OUTPUT

INPUTS OUTPUT

P3 P2 P1 P0 P

LLLLL

ALL OTHER COMBINATIONS H

FOR Cn+x OU TPUT

INPUTS OUTPUT

G0 P0 Cn Cn+x

LXXH

XLHH

ALL OTHER COMBINATIONS L

FOR Cn+y OU TPUT

INPUTS OUTPUT

G1 G0 P1 P0 Cn Cn+y

LXXXXH

XLLXXH

XXLLHH

ALL OTHER COMBINATIONS L

FOR Cn+z OU TPUT

INPUTS OUTPUT

G2 G1 G0 P2 P1 P0 Cn Cn+z

LXXXXXXH

XLXLXXXH

XXLLLXXH

XXXLLLHH

ALL OTHER COMBINATIONS L

Cn+x = G0 + P0Cn

Cn+y = G1 + P1G0 + P1P0Cn

Cn+z = G2 + P2G1 + P2P1G0 + P2P1P0Cn

G = G3+ G3 + P3G2 + P3P2G1 + P3P2P1G0

P = P3P2P1P0

or

Cn+x = Y0 + (X0 + Cn)

Cn+y = Y1 + [X1+ Y0(X0+ Cn)]

Cn+z = Y2 + {X2 + Y1[X1 + Y0(X0+Cn)]}

G = Y3 + (X3 + Y2)(X3+ X2 + Y1)(X3 + X2 + X1 + Y0)

P = X3 + X2 + X1 + X0

2/12

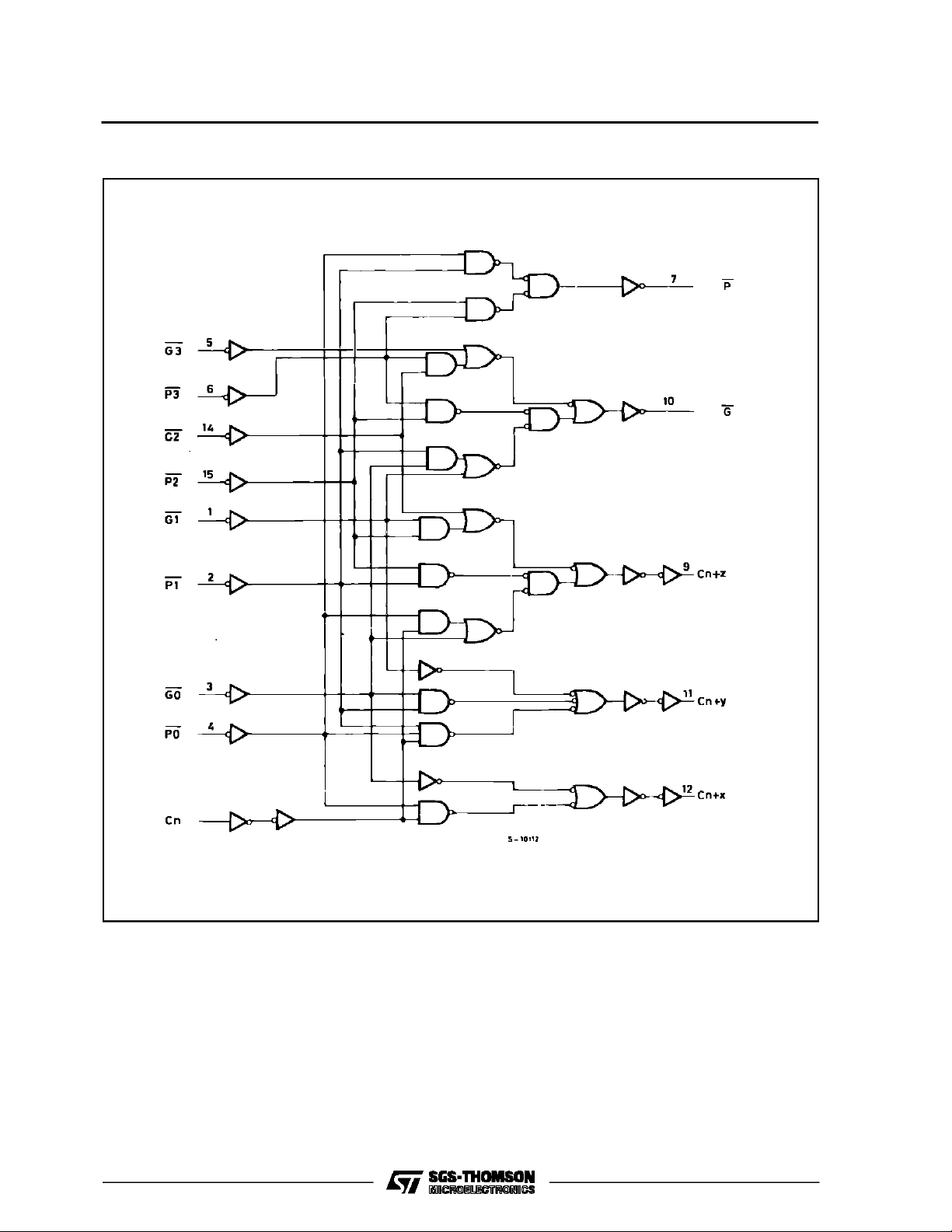

LOGIC DIAGRAM

M54/M74HC182

3/12

M54/M74HC182

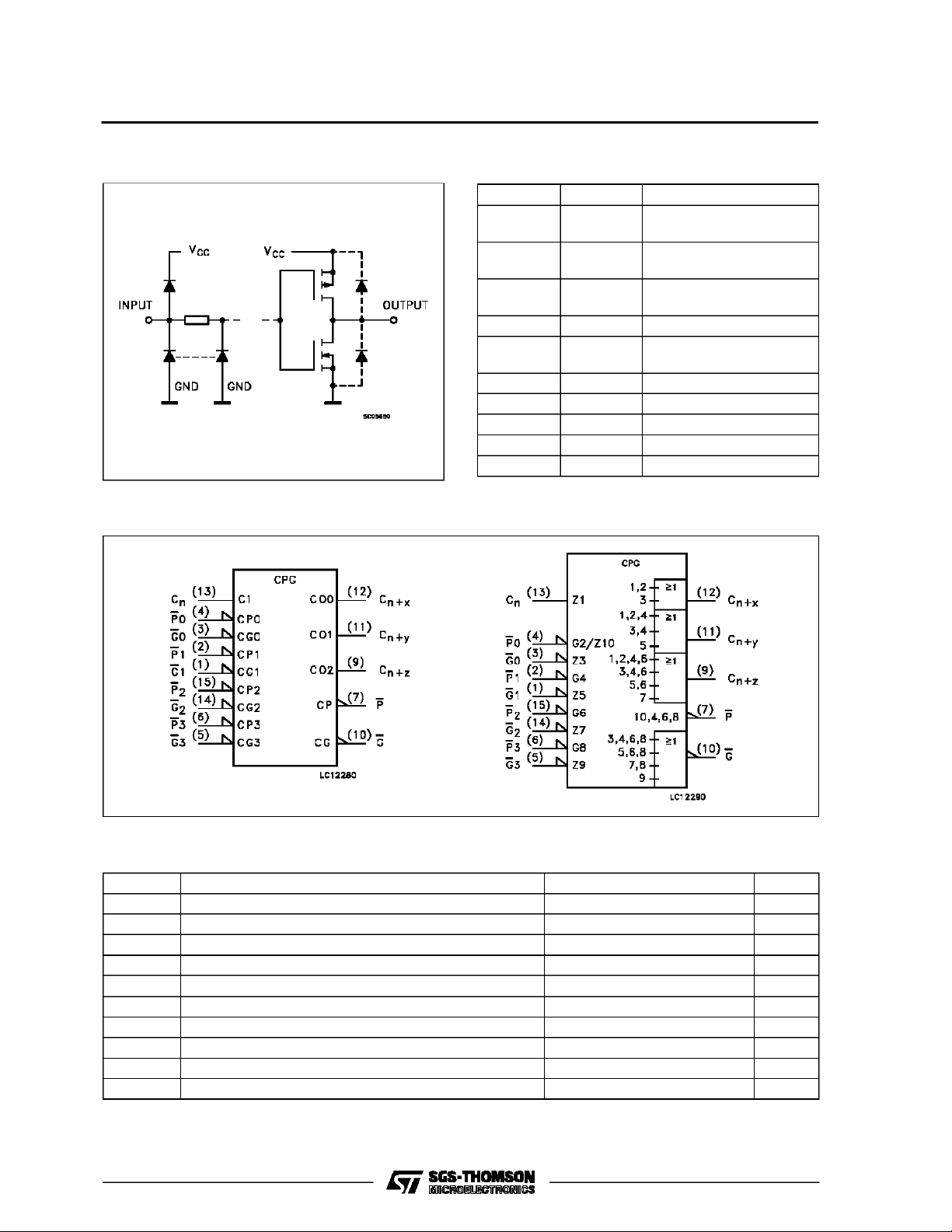

INPUT AND OUTPUT EQUIVALENT CIRCUIT PIN DESCRIPTION

PIN No SYMBOL NAME AND FUNCTION

3, 1, 14, 5 G0 to G3 Carry Generate Inputs

4, 2, 15, 6 P0 to P3 Carry Propagate Inputs

7 P Carry Propagate Output

9 Cn+z Function Output

10 G Carry Generate Output

11 Cn+y Function Output

12 Cn+x Function Output

13 Cn

8 GND Ground (0V)

16 V

IEC LOGIC SYMBOLS

CC

(Active LOW)

(Active LOW)

(Active LOW)

(Active LOW)

Positive Supply Voltage

ABSOLU TE MAXI MU M RAT INGS

Symbol Parameter Value Unit

V

CC

V

V

O

I

IK

I

OK

I

O

or I

I

CC

P

D

T

stg

T

AbsoluteMaximumRatings arethose valuesbeyond whichdamage tothedevice mayoccur. Functionaloperation under these conditionisnotimplied.

(*)500 mW:≅ 65oC derate to 300mW by 10mW/oC: 65oCto85oC

4/12

Supply Voltage -0.5 to +7 V

DC Input Voltage -0.5 to VCC+ 0.5 V

I

DC Output Voltage -0.5 to VCC+ 0.5 V

DC Input Diode Current ± 20 mA

DC Output Diode Current ± 20 mA

DC Output Source Sink Current Per Output Pin ± 25 mA

DC VCCor Ground Current ± 50 mA

GND

Power Dissipation 500 (*) mW

Storage Temperature -65 to +150

Lead Temperature (10 sec) 300

L

o

C

o

C

Loading...

Loading...