ARITHMETIC LOGIC UNIT/FUNCTION GENERATOR

.HIGH SPEED

tPD= 13 ns(TYP.) AT VCC=5V

.LOWPOWER DISSIPATION

ICC=4µA(MAX.) at TA=25°C

.HIGH NOISE IMMUNITY

V

NIH=VNIL

=28%VCC(MIN.)

.OUTPUTDRIVE CAPABILITY

10 LSTTL LOADS

.SYMMETRICAL OUTPUT IMPEDANCE

IOH =IOL= 4 mA (MIN.)

.BALANCEDPROPAGATIONDELAYS

t

PLH=tPHL

.WIDE OPERATING VOLTAGE RANGE

VCC(OPR)= 2 V to 6 V

.PIN AND FUNCTION COMPATIBLE

WITH 54/74LS181

DESCRIPTION

The74HC181 is a high speed CMOSARITHMETIC

LOGIC UNIT/FUNCTION GENERATOR fabricated

withsilicongateC2MOStechnology. It has the same

highspeedperformanceofLSTTLcombinedwithtrue

CMOS low power consumption. These circuits perform 16 binary arithmetic operations on two 4-bit

words as shown intables 1 and2. These operations

areselectedby the fourfunction-select lines (S0, S1,

S2,S3) andinclude addition, subtraction, decrement,

and straight transfer. When performing arithmetic

manipulations, theinternal carriesmustbeenabled by

applying a low-levelvoltage to themode control input

(M).Afullcarrylook-ahead schemeismadeavailable

in these devices for fast, simultaneous carry generationby meansof two cascade-outputs (pins15 and

17)forthefourbitsinthepackage. Whenusedinconjunction withthe M54HC182 orM74HC182, full carry

look-ahead circuits,high-speed arithmetic operations

canbeperformed. These circuits willaccomodate active-highoractive-lowdata,ifthepindesignations are

interpreted as shown below. Subtraction is accomplished by 1,s complement addition where the 1’s

complement ofthesubtrahendisgenerated internally.

Theresultant output is1–B–1, whichrequires anendaround or forced carry to produce A–B.The181can

alsobeutilized as a comparator. The A = B outputis

internally decoded fromthe functionoutputs (F0, F1,

F2, F3) so thatwhen two words of equal magnitude

areappliedattheAandB inputs, itwillassumeahigh

level toindicated equality (A =B).TheALUshould be

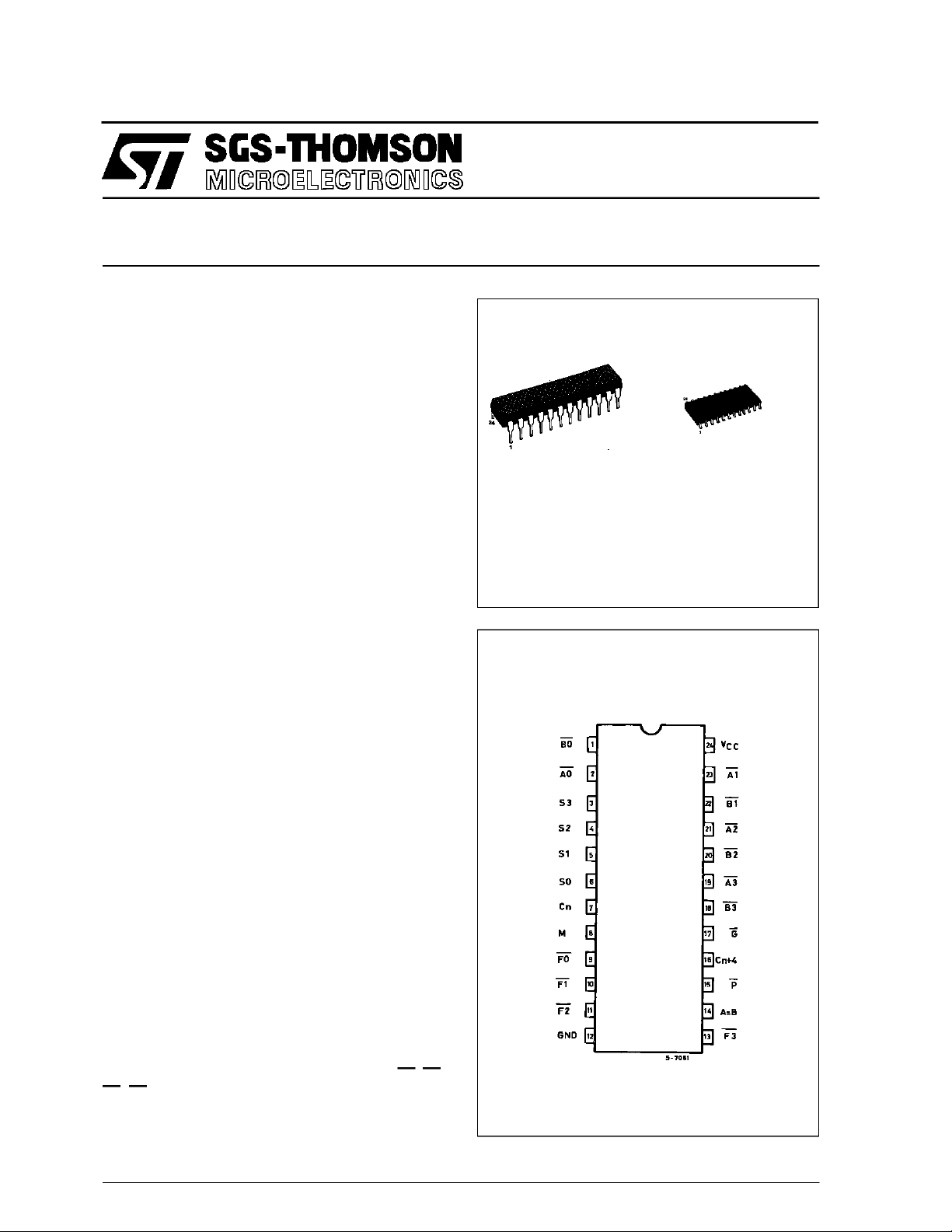

M74HC181

B1R

(Plastic Package)

ORDER CODES :

M74HC 181M1R M74HC 181B1R

PIN CONNECTIONS(top view)

* Open drain OutputStructure

M1R

(MicroPackage)

October 1993

1/13

M74HC181

DESCRIPTION (continued)

inthesubtractmodewithCn=Hwhenperforming this

comparison. The A =B output isopen-drain sothat it

canbe wire-AND connected togiveacomparison for

morethatfourbits. Thecarry output (Cn+4) canalso

be used to supply relative magnitude information.

Again,theALUshould beplacedinthesubtractmode

byplacing thefunction selectinputsS3,S2, S1,S0at

L,H, H, L, respectively. These circuits have beendesigned to notonlyincorporate allofthedesigner’s re-

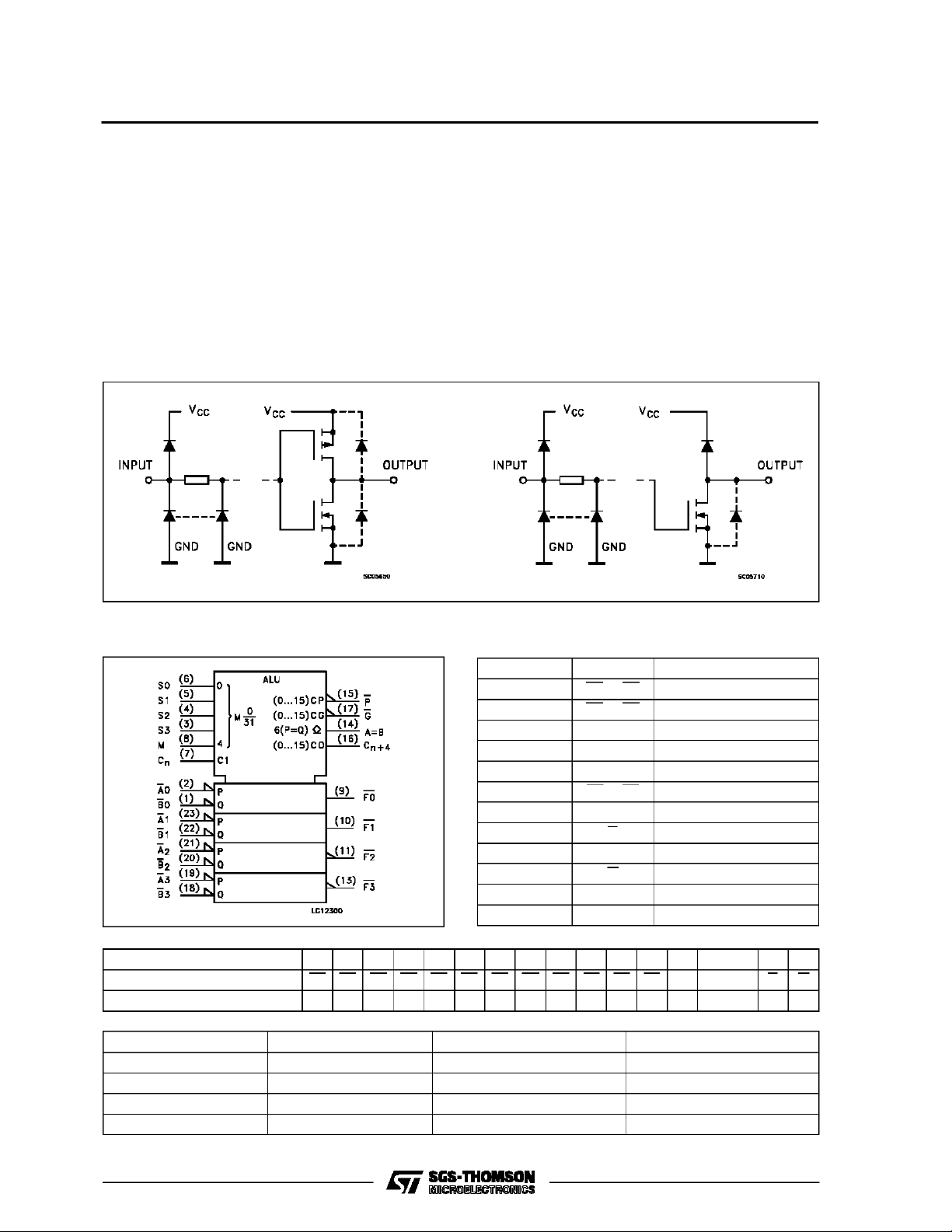

INPUT AND OUTPUT EQUIVALENT CIRCUITS

quirements for arithmetic operations, but also to provide 16 possible functions of two Boolean variables

withouttheuse ofexternalcircuitry.These logic functionsareselectedbyuseofthefourfunction-selectinputs(S0,S1, S2,S3) withthemode-control input (M)

atahighlevel to disable the internal carry.Allinputs

areequipped withprotectioncircuitsagainst staticdischarge and transient excessvoltage.

ONLY OUTPUT A = B

IEC LOGIC SYMBOLS

PIN NUMBER 2 1 23 22 21 20 19 18 9 10 11 13 7 16 15 17

ACTIVE LOW DATA (Table 1) A0 B0 A1 B1 A2 B2 A3 B3 F0 F1 F2 F3 Cn Cn + 4 P G

ACTIVE HIGH DATA (Table 1) A0 B0 A1 B1 A2 B2 A3 B3 F0 F1 F2 F3 Cn Cn + 4 X Y

PIN DESCRIPTI ON

PIN No SYMBOL NAME AND FUNCTION

2, 23, 21, 19 A0 to A3 Word A Inputs

1, 22, 20, 18 B0 to B3 Word B Inputs

6, 5, 4, 3 S0 to S3 Function Select Inputs

7 Cn Inv. Carry Input

8 M Mode Control Input

9, 10, 11, 13 F0 to F3 Function Outputs

14 A = B Comparator Output

15 P Carry Propagate Output

16 Cn + 4 Inv. Carry Output

17 G Carry Generate Output

12 GND Ground (0V)

24 V

CC

Positive Supply Voltage

2/13

Input Cn Output Cn + 4 Active LOW Data (Figure 1) Active HIGH Data (Figure 2)

HHA≥BA≤B

HLA<BA>B

LHA>BA<B

LLA≤BA≥B

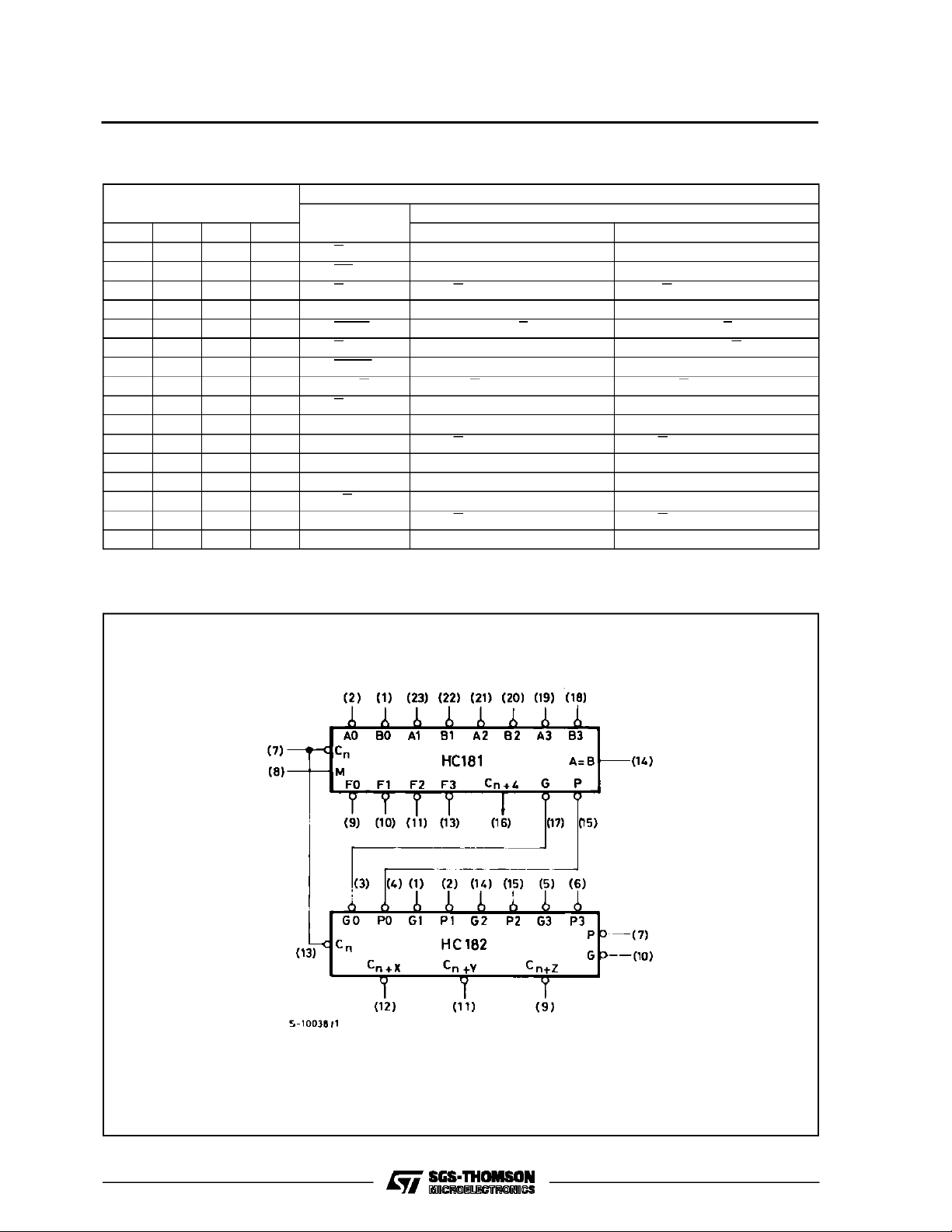

TRUTH TABLE 1

M74HC181

Selection

S3 S2 S1 S0 Cn = L (no carry) Cn = H (with carry)

L L L L F = A F = A Minus 1 F = A

L L L H F = AB F = AB Minus 1 F = AB

L L H L F = A + B F = AB Minus 1 F = (AB)

L L H H F = 1 F = Minus 1 (2’s Compl) F = Zero

L H L L F=A+B F=APlus (A + B) F = A Plus (A + B) Plus 1

L H L H F = B F = AB Plus (A + B) F = AB Plus (A + B) Plus 1

LHHLF=A⊕B F = A Minus B Minus 1 F = A Minus B

L H H H F=A+B F=A+B F=(A+B)Plus 1

H L L L F = AB F = A Plus (A + B) F = A Plus (A + B) Plus 1

HLLHF=A⊕B F = A Plus B F = A Plus B Plus 1

H L H L F = B F = AB Plus (A + B) F = AB Plus (A + B) Plus 1

H L H H F=A+B F=A+B F=(A+B)Plus 1

H H L L F = 0 F = A Plus A * F = A Plus A Plus 1

H H L H F = AB F = AB Plus A F = AB Plus A Plus 1

H H H L F = AB F = AB Plus A F = AB Plus A Plus 1

H H H H F = A F = A F = A Plus 1

* Eachbit is shiftedto the nextmore significantposition.

M = H Logic

Functions

ACTIVE LOW DATA

M = L: Arithmetic Operations

FIGURE 1

3/13

M74HC181

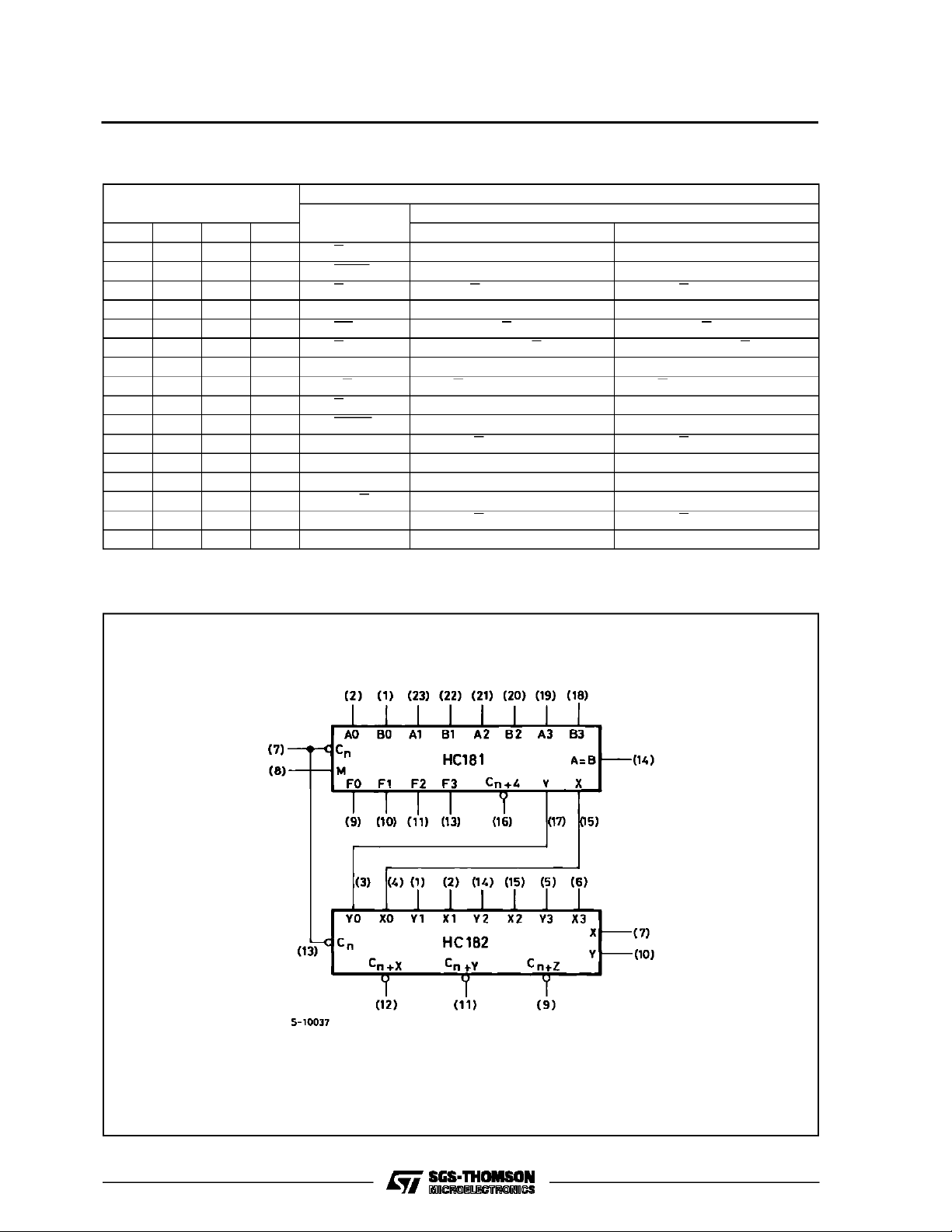

TRUTH TABLE 2

Selection

S3 S2 S1 S0 Cn = H (no carry) Cn = L (with carry)

L L L L F = A F = A F = A Plus 1

L L L H F=A+B F=A+B F=(A+B)Plus 1

L L H L F=AB F=A+B F=(A+B)Plus 1

L L H H F = 0 F = Minus 1 (2’s Compl) F = Zero

L H L L F = AB F = A Plus (AB) F = A Plus AB Plus 1

L H L H F = B F = (A + B) Plus AB F = (A + B) Plus (AB) Plus 1

LHHLF=A⊕B F = A Minus B Minus 1 F = A Minus B

L H H H F = AB F = AB Minus 1 F = AB

H L L L F = A + B F = A Plus AB F = A Plus AB Plus 1

HLLHF=A⊕B F = A Plus B F = A Plus B Plus 1

H L H L F = B F = (A + B) Plus AB F = (A + B) Plus AB Plus 1

H L H H F = AB F = AB Minus 1 F = AB

H H L L F = 1 F = A Plus A * F = A Plus A Plus 1

H H L H F = A + B F = (A + B) Plus A F = (A + B) Plus A Plus 1

H H H L F = A + B F = (A + B) Plus A F = (A + B) Plus A Plus 1

H H H H F = A F = A Minus 1 F = A

* Eachbit is shiftedto the nextmore significantposition.

M = H Logic

Functions

ACTIVE HIGH DATA

M = L: Arithmetic Operations

FIGURE 2

4/13

Loading...

Loading...