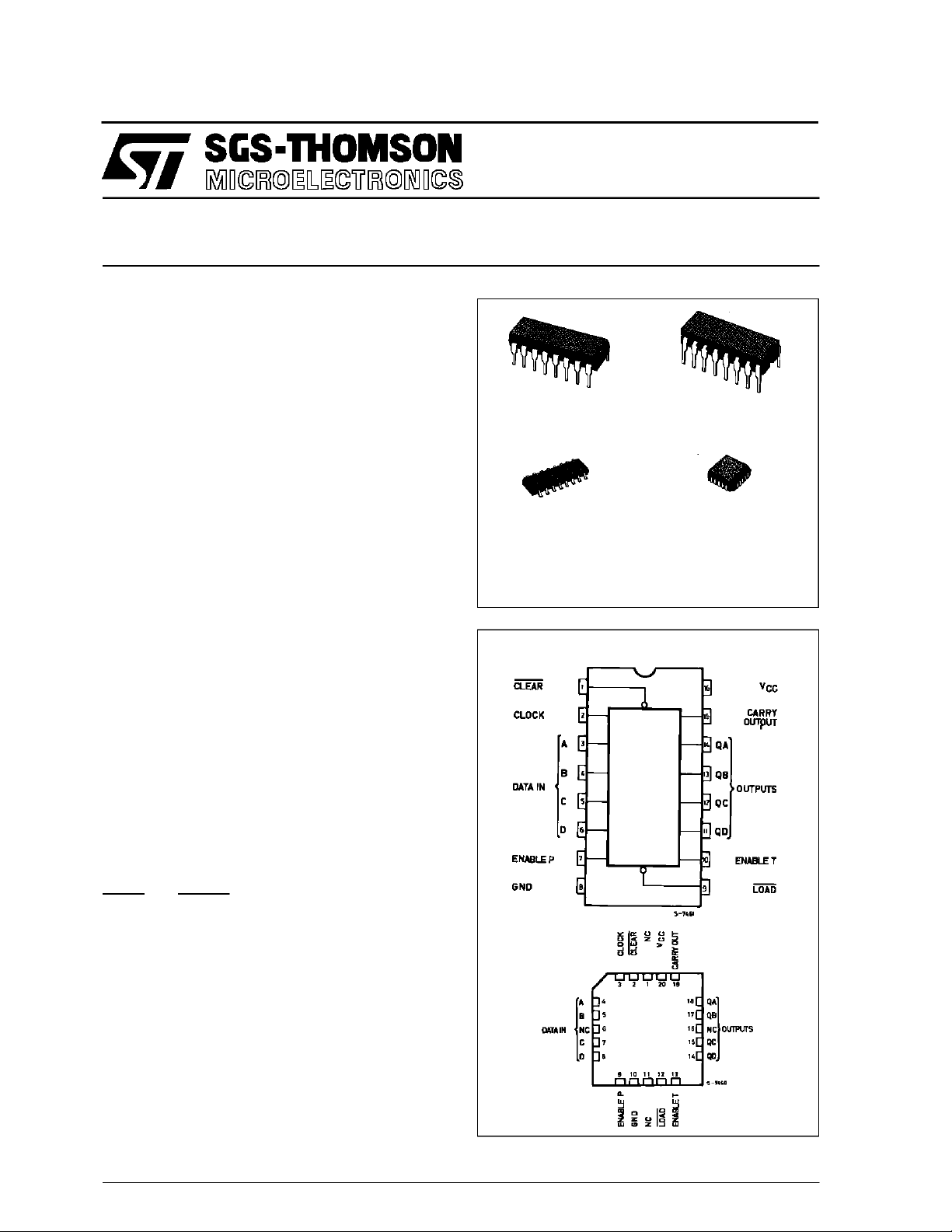

SYNCHRONOUS PRESETTABLE 4-BIT COUNTER

.HIGH SPEED

f

= 63 MHz(TYP.) AT VCC=5V

MAX

.LOWPOWER DISSIPATION

ICC=4µA(MAX.) AT 25°C

.OUTPUT DRIVE CAPABILITY

10 LSTTL LOADS

.BALANCEDPROPAGATION DELAYS

t

PLH=tPHL

.HIGH NOISEIMMUNITY

V

NIH=VNIL

=28%VCC(MIN.)

.WIDE OPERATING VOLTAGERANGE

VCC(OPR)= 2 V TO 6 V

.PIN AND FUNCTION COMPATIBLE

WITH 54/74LS160 ∼ 163

DESCRIPTION

M54/74HC160 Decade, Asynchronous Clear

M54/74HC161 Binary, Asynchronous Clear

M54/74HC162 Decade, Synchronous Clear

M54/74HC163 Binary, Synchronous Clear

The M54/74HC160, 161, 162 and 163 are high

speed CMOS SYNCHRONOUS PRESETTABLE

COUNTERS fabricated with silicon gate C2MOS

technology.

They have the same the high speed operationsimilar to equivalent LSTTL while maintaining the

CMOS low power dissipation.

The M54/74HC160/162 are BCD Decade counters

and theM54/74HC161/163 are4bitbinary counters.

The CLOCKinputis active on the risingedge. Both

LOADand CLEAR inputsare active Low.

Presetting of all four IC’s is synchronous on the rising edge of the CLOCK.

The function on the M54/74HC162/163 is synchronous to CLOCK, while the M54/74HC160/161

counters are cleared asynchronously.

Two enable inputs(TE and PE) and CARRYoutput

areprovided toenable easycascading of counters,

which facilities easy implementation of N-bit

counters without using external gates.

All inputs are equipped with protection circuits

against static discharge and transient excess voltage.

M54/74HC160/161

M54/74HC162/163

B1R

(PlasticPackage)

M1R

(MicroPackage)

ORDER CODES :

M54HC X XXF1R M74H CXXXM1R

M74HC X XXB1R M74HCX X XC1R

PIN CONNECTIONS(top view)

NC =

No InternalCon-

F1R

(CeramicPackage)

C1R

(Chip Carrier)

April1993

1/16

M54/M74HC160/161/162/163

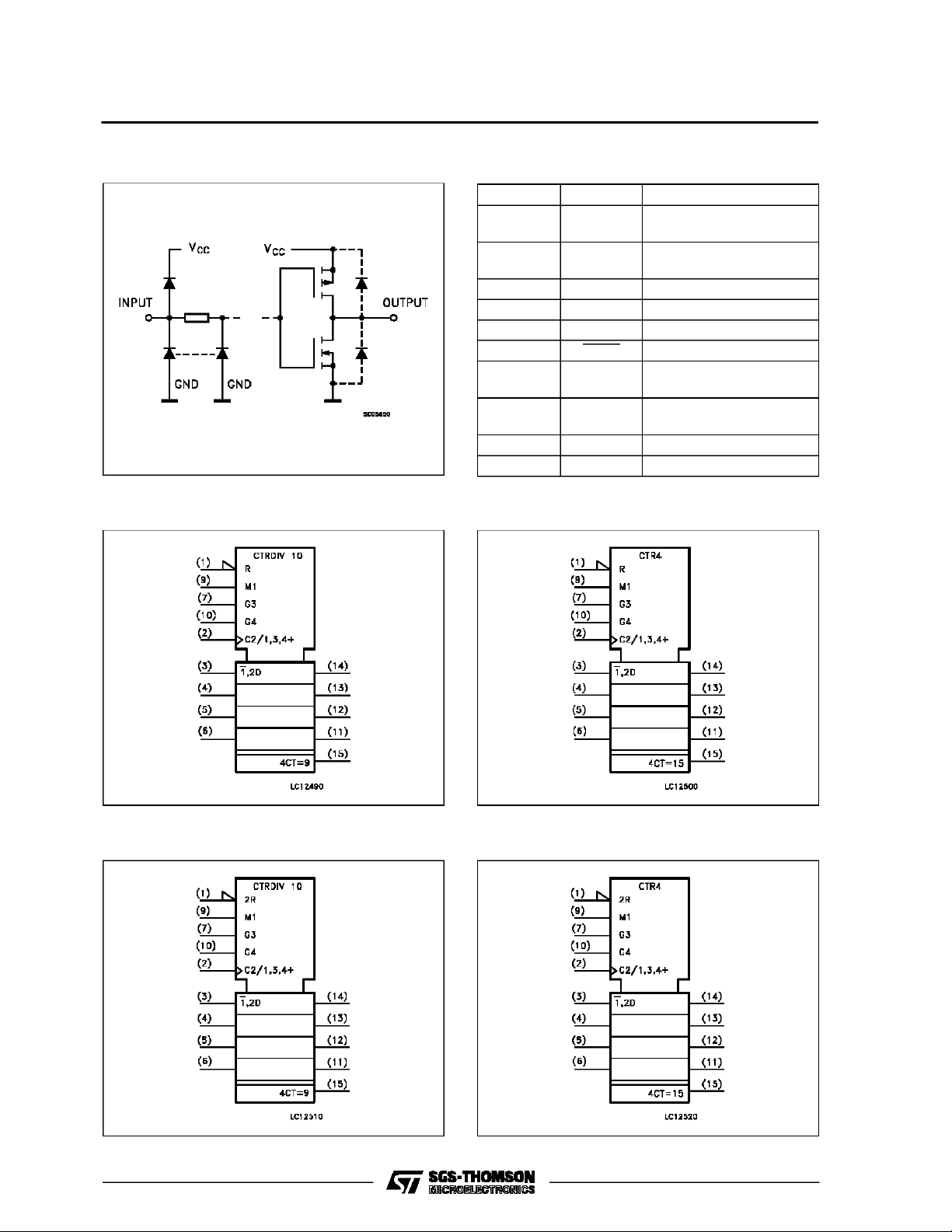

INPUT AND OUTPUT EQUIVALENT CIRCUIT

PIN DESCRIPTION

PIN No SYMBOL NAME AND FUNCTION

1 CLEAR Asynchronous Master

reset

2 CLOCK Clock Input (LOW to

HIGH, Edge-triggered)

3, 4, 5, 6 A, B, C, D Data Inputs

7 ENABLE P Count Enable Input

10 ENABLET Count Enable Carry Input

9 LOAD Parallel Enable Input

14, 13, 12,11QA to QD Flip Flop Outputs

15 CARRY

OUTPUT

8 GND Ground (0V)

16 V

CC

Terminal Count Output

Positive Supply Voltage

IEC LOGIC SYMBOL (HC161)IEC LOGIC SYMBOL (HC160)

IEC LOGIC SYMBOL (HC162) IEC LOGIC SYMBOL (HC163)

2/16

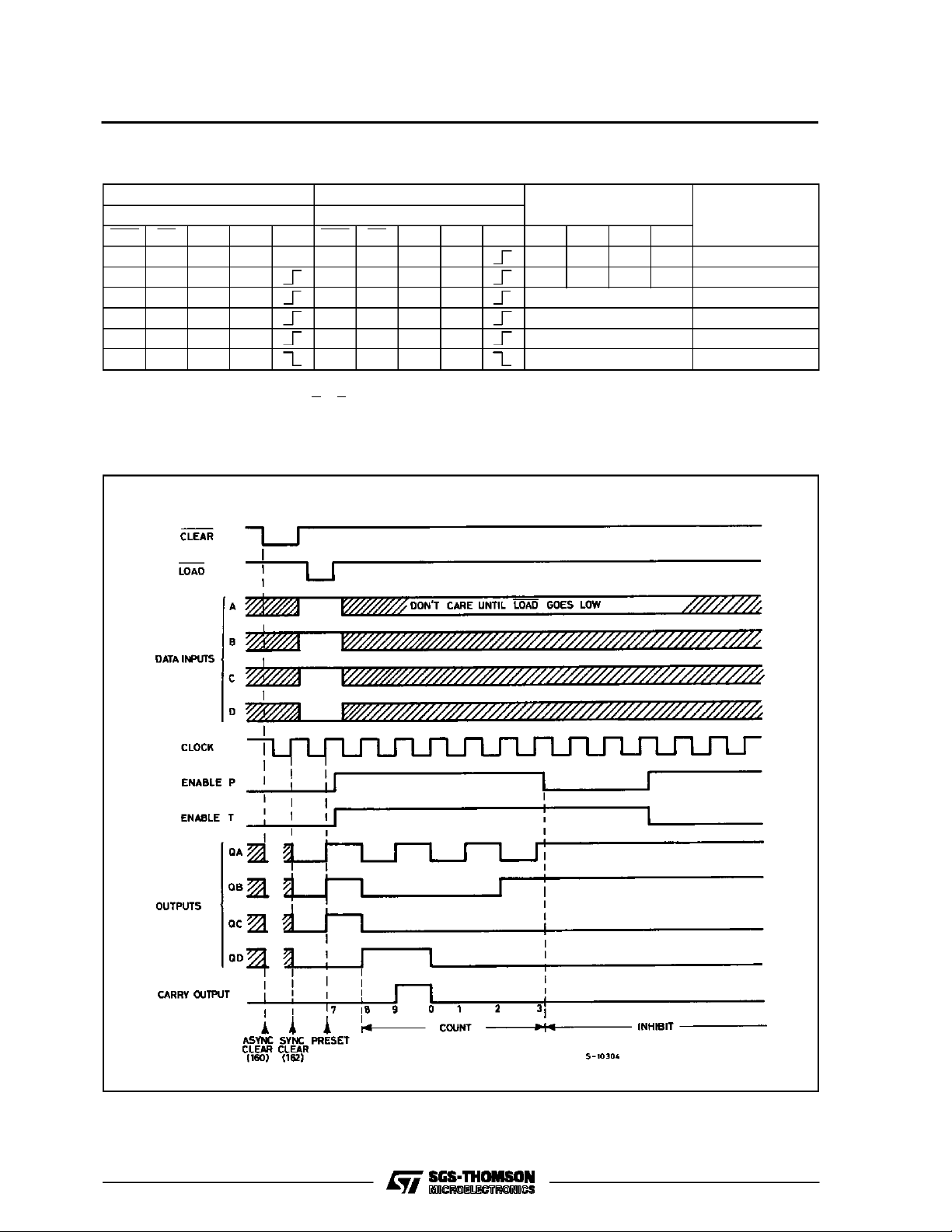

TRUTH TABLE

M54/M74HC160/161/162/163

M54/74HC160/161 M54/74HC162/163

INPUTS INPUTS

CLR LD PE TE CK CLR LD PE TE CK QA QB QC QD

LXXXXLXXX LLLLRESET TO ”0”

H L X X H L X X A B C D PRESET DATA

H H X L H H X L NO CHANGE NO COUNT

H H L X H H L X NO CHANGE NO COUNT

HHHH HHHH COUNT UP COUNT

H X X X X X X X NO CHANGE NO COUNT

Note: X :Don’tCare

A, B, C, D : Logi levelofdata inputs

Carry : CARRY =TE • QA• QB• QC• QD............ (M54/74HC160/162)

:CARRY =TE • QA• QB• QC• QD............ (M54/74HC161/163)

OUTPUTS

FUNCTION

TIMING CHART (HC160/162 : decade counter)

3/16

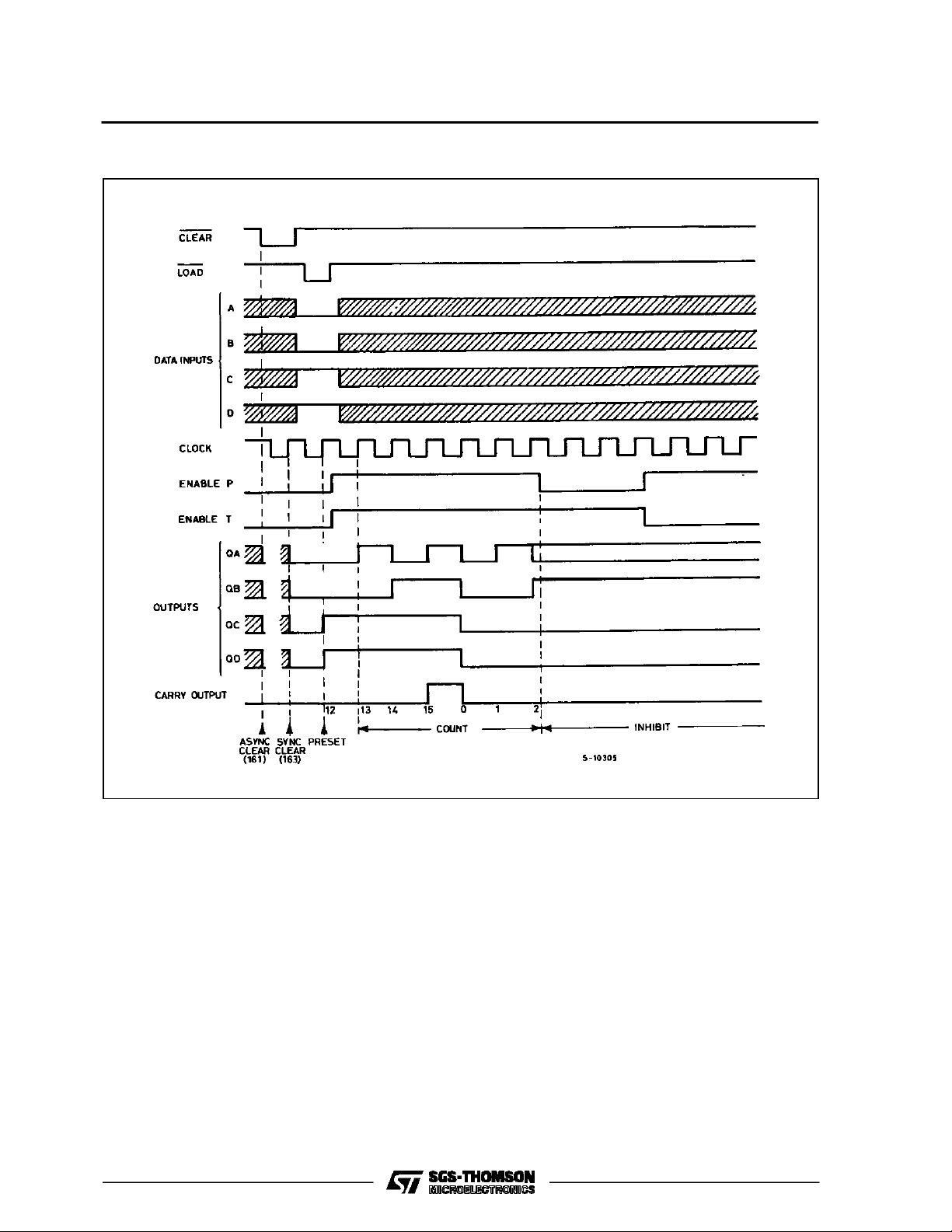

M54/M74HC160/161/162/163

TIMING CHART (HC161/163 : binary counter)

4/16

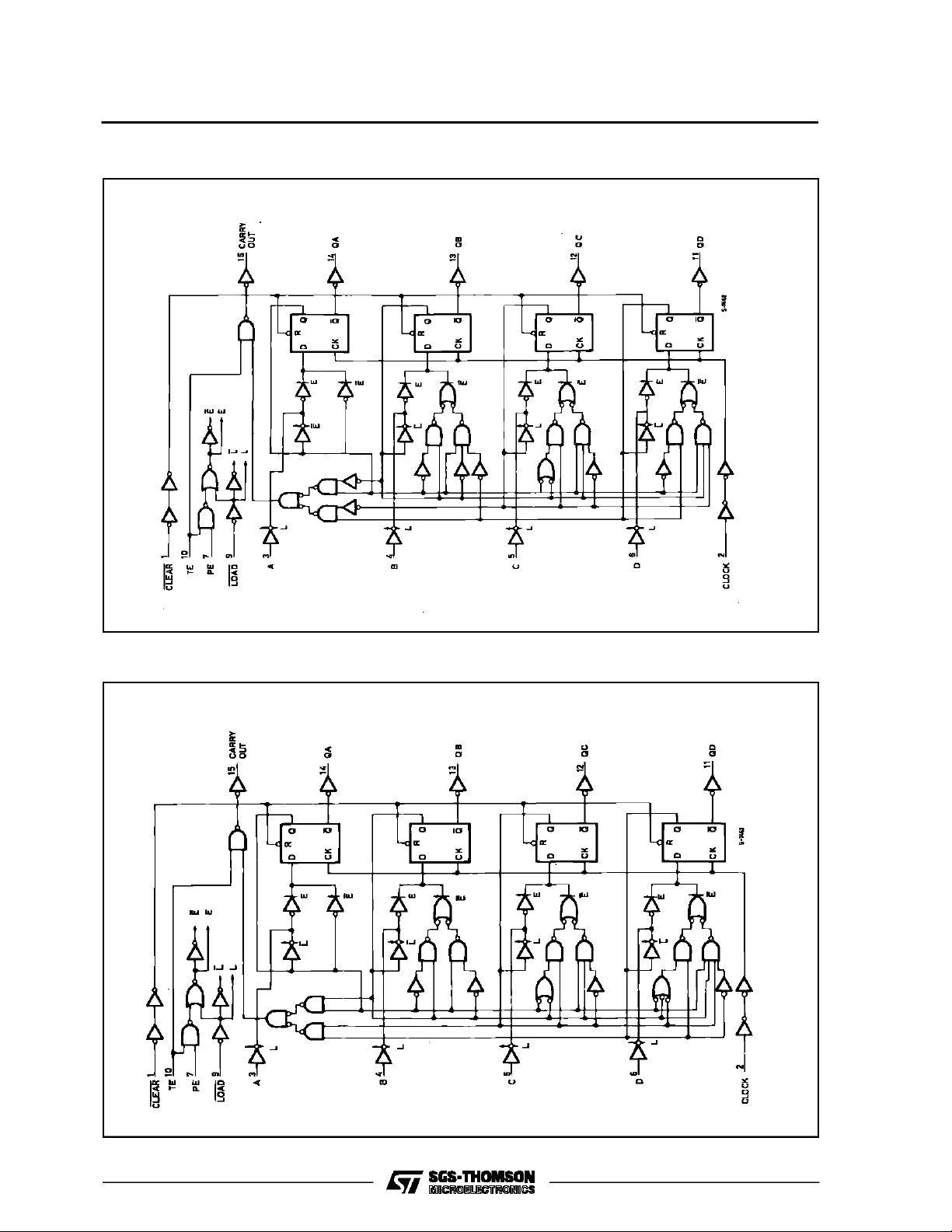

LOGIC DIAGRAM

HC160

M54/M74HC160/161/162/163

LOGIC DIAGRAM

HC161

5/16

Loading...

Loading...