64K x 72-bit Entry NETWORK PACKET SEARCH ENGINE

FEATURES SUMMARY

■ 64K DATA ENT RIES IN 72-B IT MODE

■ TABLE MAY BE PARTITIONED INTO UP TO

EIGHT(8) OCTANTS

(Data entry width in each octant is configurab le

as 36, 72, 144, or 288 bits.)

■ UP TO 100MILLIONSUSTAINED SEA RCHE S

PER SE COND IN 72-B I T and 144-B IT

CONFIGURATIONS

■ UP TO 50 MILLION SEARCHES PER

SECOND IN 36-BIT and 288-BIT

CONFIGURATIONS

■ SEARCHES ANY SUB-FIELD IN A SINGLE

CYCLE

■ OFFERS BIT-BY-BIT and GLOBAL MASKING

■ SYNCHRONOUS, PIPELINED OPERATION

■ UP TO 31 SEARCH ENGINES CA SCADAB LE

WITHOUT PERFORMANCE DEGRADATION

■ WHEN CASCADED, THE DATABASE

ENTRIES CAN SCAL E F ROM 496K TO 3968K

DEPENDING O N THE WIDTH OF THE ENTRY

■ GLUELESS INTERFACE TO INDUSTRY-

STANDARD SRAMS

■ SIMPLE HARDWARE INSTRUCTION

INTERFACE

■ IEEE 1149.1 TEST ACCESS PORT

■ OPERATING SUPPLY VOLTAGES INCLUDE:

(Operating Core Supply Voltage) = 1.5V for

V

DD

66 and 83MSPS; 1.65V for 100MSPS

(Operating Supply Voltage for I/O) = 2.5

V

DDQ

or 3.3V

■ 388 PBGA, 35mm x 35mm

M7040N

PRELIMINARY DATA

Figure 1. 388-ball PBGA Package

388-ball PBGA

35mm x 35mm

May 2002

1/159

M7040N

TABLE OF CONTENTS

DESCRIPTION ....................................................................7

Overview......................................................................7

Performance...................................................................7

Applications....................................................................7

Product Range (Table 1.) . ........................................................7

Switch/Router Implementation Using the M7040N (Figure 2.) .............................7

SignalNames(Table2.)..........................................................8

Connections (Figure 3.). . . ........................................................9

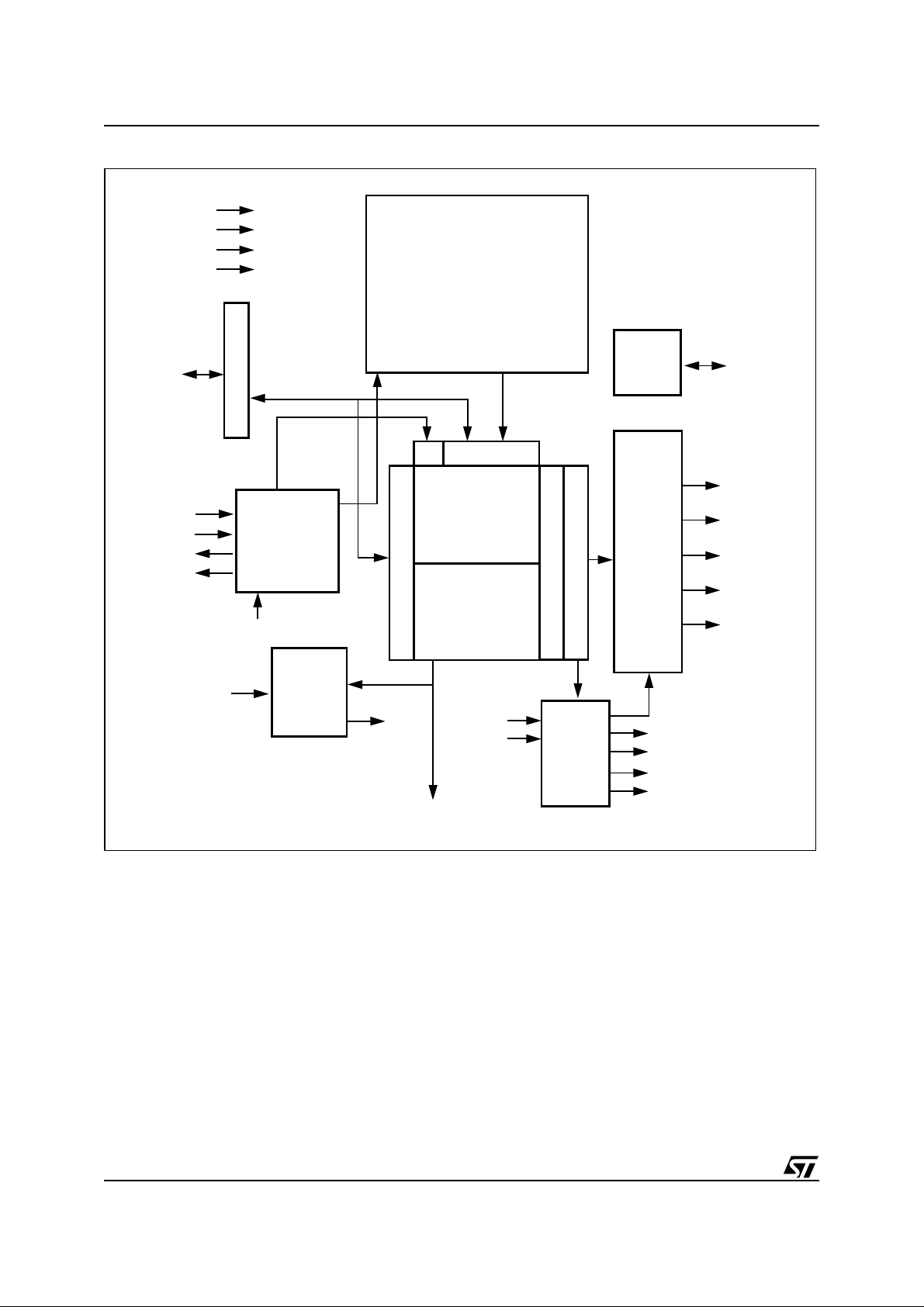

M7040NBlockDiagram(Figure4.).................................................10

MAXIMUMRATING................................................................11

AbsoluteMaximumRatings(Table3.) ..............................................11

DC AND AC PARAMETERS . . .......................................................12

DC and AC Measurement Conditions (Table 4.). . . ....................................12

M7040N 1.8, 2.5, or 3.3V A C Testing Load (Figure 5.) ..................................13

M7040N 1.8, 2.5, or 3.3V Input Waveform (Figure 6.) ..................................13

M7040N1.8,2.5,or3.3VI/OOutputLoadEquivalent(Figure7.) .........................13

Capacitance (Table 5.) . . . .......................................................14

DCCharacteristics(Table6.).....................................................14

ACTimingWaveformswithCLK2X(Figure8.)........................................15

ACTimingWaveformswithCLK1X(Figure9.)........................................16

ACTimingParameterswithCLK2X(Table7.)........................................17

ACTimingParameterswithCLK1X(Table8.)........................................18

OPERATION.....................................................................19

CommandBusandDQBus ......................................................19

DatabaseEntry(DataArrayandMaskArray).........................................19

Arbitration Logic. . . .............................................................19

PipelineandSRAMControl.......................................................19

FullLogic.....................................................................19

Connection Descriptions . . .......................................................19

CLOCKS........................................................................21

Clocks(CLK2XandPHS_L)(Figure10.)............................................21

Clocks(CLK1X)(Figure11.)......................................................21

ClocksforAllTimingDiagrams(Figure12.)..........................................22

PLLUSAGE .....................................................................22

2/159

M7040N

REGISTERS.....................................................................22

RegisterOverview(Table9.)......................................................22

ComparandRegisters...........................................................23

ComparandRegisterSelectionDuringSEARCHandLEARNInstructions(Figure13.).........23

MaskRegisters................................................................23

AddressingtheGlobalMasksRegisterArray(Figure14.) ...............................23

SEARCH-Successful Registers (SSR[0:7]). ..........................................24

SEARCH-Successful Register (S S R ) Description (Table 10.).............................24

TheCommandRegister .........................................................25

CommandRegisterFieldDescriptions(Table11.).....................................25

TheInformationRegister.........................................................26

InformationRegisterFieldDescriptions(Table12.) ....................................26

TheReadBurstAddressRegister(RBURREG).......................................27

ReadBurstRegisterDescription(Table13.)..........................................27

The Write Burst Address Register (WBURREG). . . ....................................27

WriteBurstRegisterDescription(Table14.)..........................................27

TheNFARegister..............................................................27

NFARegister(Table15.).........................................................27

SEARCH ENGINE ARCHITECTURE . .................................................28

DataandMaskAddressing.......................................................28

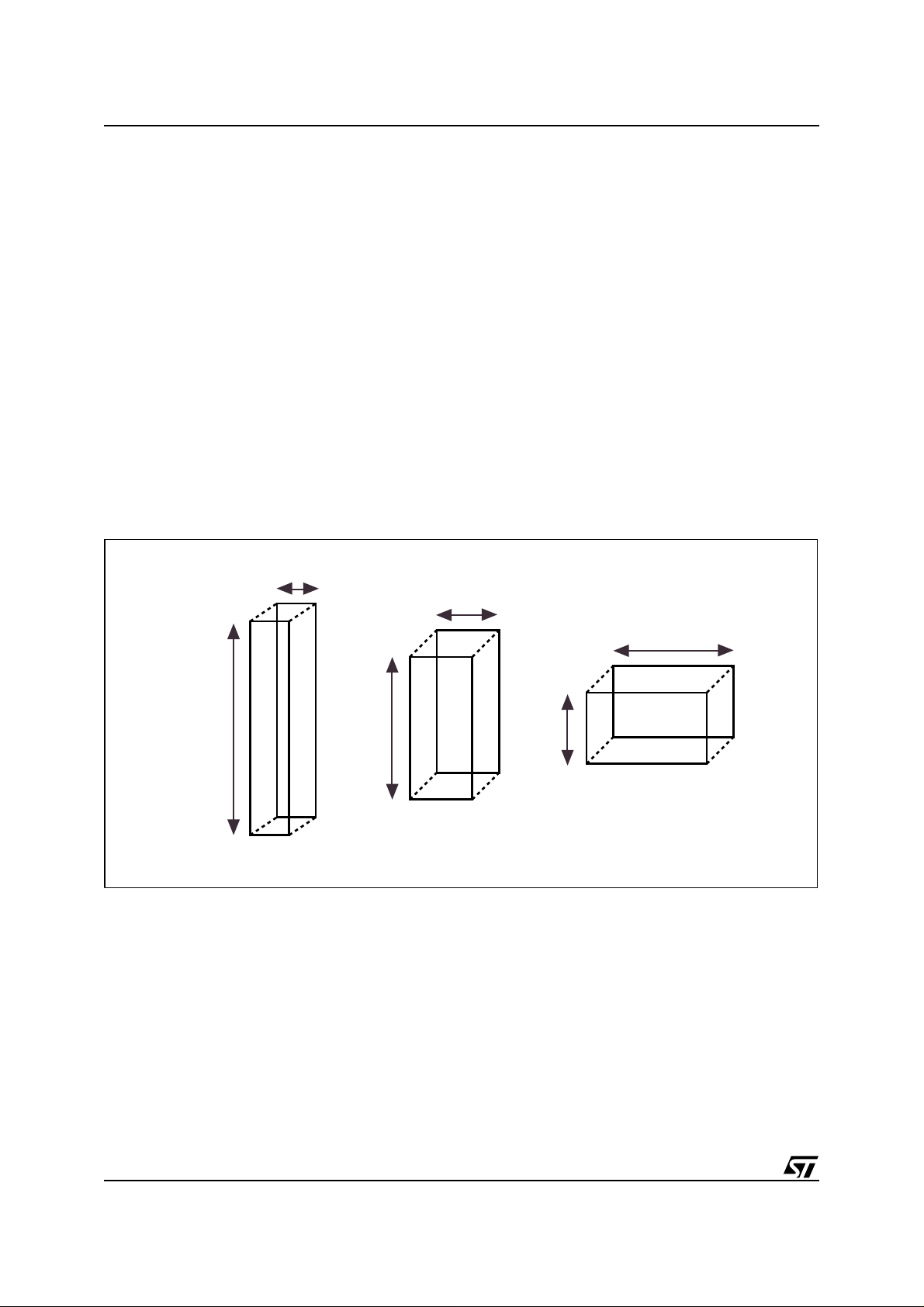

M7040NDatabaseWidthConfiguration(Figure15.) ...................................28

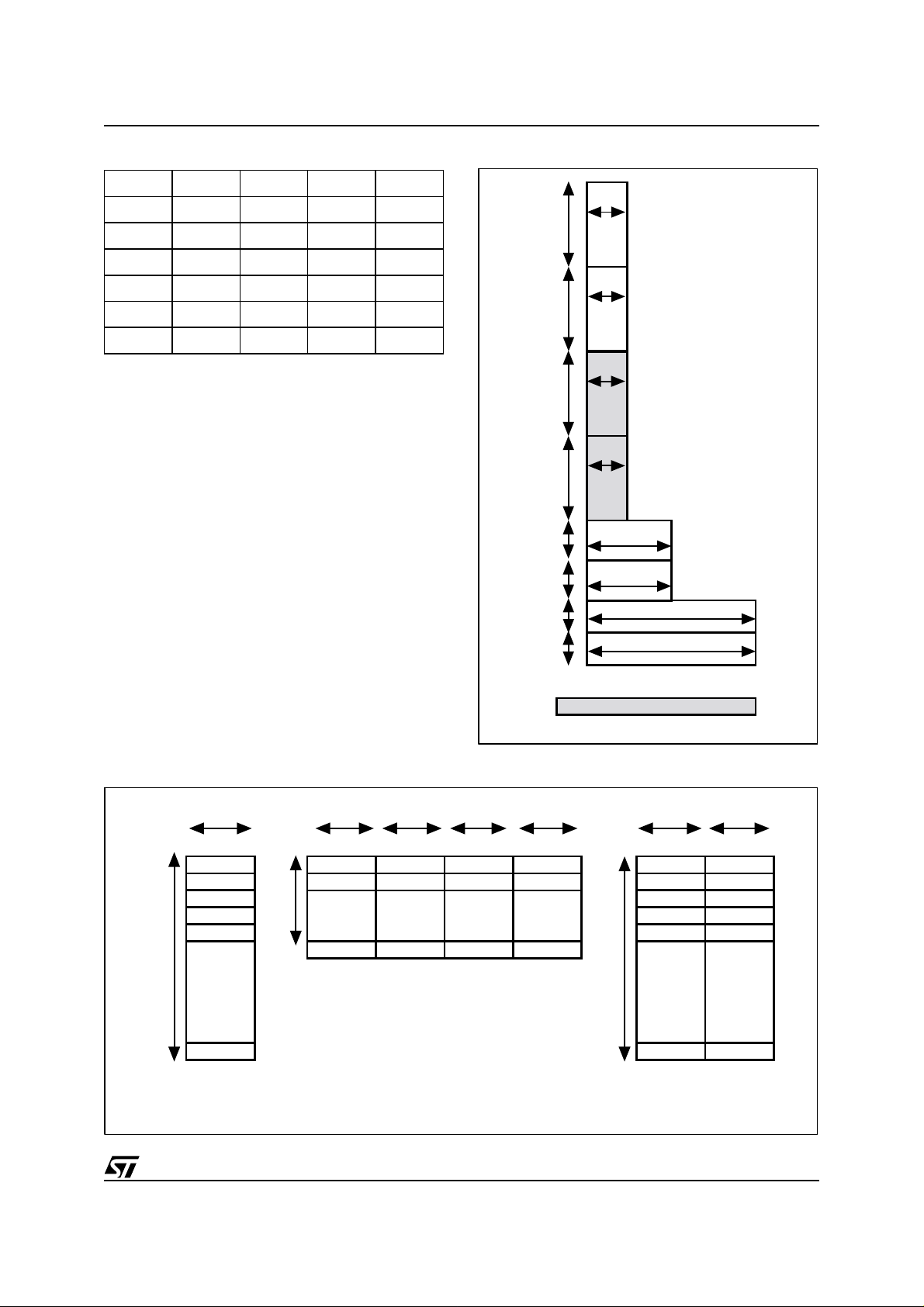

BitPositionMatch(Table16.).....................................................29

Multi-widthConfigurationExample(Figure16.) .......................................29

M7040NDataandMaskArrayAddressing(Figure17.).................................29

COMMAND CODES AND PARAMETERS ..............................................30

CommandCodes...............................................................30

CommandsandCommandParameters.............................................30

CommandCodes(Table17.) .....................................................30

CommandParameters(Table18.).................................................31

READCOMMAND.................................................................32

SingleLocationREADCycleTiming(Figure18.)......................................33

BurstREADoftheDataandMaskArrays(BLEN=4)(Figure19.)........................33

READCommandParameters(Table19.)............................................34

DataandMaskArray,SRAMReadAddressFormat(Table20.)..........................34

READAddressFormatforInternalRegisters(Table21.)................................35

READAddressFormatforDataandMaskArrays(Table22.)............................35

3/159

M7040N

WRITECOMMAND................................................................35

SingleLocationWRITECycleTiming(Figure20.) .....................................36

BurstWRITEoftheDataandMaskArrays(BLEN=4)(Figure21.)........................37

(Single)WRITEAddressFormatforDataandMaskArraysorSRAM(Table23.).............37

WRITEAddressFormatforInternalRegisters(Table24.)...............................38

WRITEAddressFormatforDataandMaskArray(BurstWrite)(Table25.)..................38

ParallelWRITE................................................................38

SEARCH COMMAND . .............................................................38

72-bitConfigurationwithSingleDevice...........................................38

HardwareDiagramforaTablewithOneDevice(Figure22.).............................39

72-BitConfigurationSEARCHTimingDiagramforOneDevice(Figure23.).................40

x72TablewithOneDevice(Figure24.).............................................41

LatencyofSEARCHfromInstructiontoSRAMAccessCycle,72-bit(Table26.)..............41

ShiftofSSFandSSVfromSADR(Table27.).........................................41

72-bit SEARCH on Tables Configured as x72 Using up to Eight M 7040N Devices.........42

Hit/MissAssumption(Table28.)...................................................43

HardwareDiagramforaTablewithEightDevices(Figure25.) ...........................43

x72TablewithEightDevices(Figure26.)............................................44

Timing Diagrams for x72 Using up to Eight M7040N Devices.............................45

LatencyofSEARCHfromInstructiontoSRAMAccessCycle(Table29.)...................48

ShiftofSSFandSSVfromSADR(Table30.).........................................48

72-bit Search on Tables Configured as x72 Using Up To 31 M7040N Devices . . ..........48

Hit/MissAssumption(Table31.)...................................................49

HardwareDiagramforaTablewith31Devices(Figure30.) .............................50

HardwareDiagramforaBlockofUpToEightDevices(Figure31.)........................51

x72Tablewith31Devices(Figure32.)..............................................52

TimingDiagramsforx72UsingUpTo31M7040NDevices..............................53

LatencyofSEARCHfromInstructiontoSRAMAccessCycle(Table32.)...................64

ShiftofSSFandSSVfromSADR(Table33.).........................................64

144-bitConfigurationwithSingleDevice..........................................64

HardwareDiagramforaTablewith1Device(Figure44.) ...............................65

Timing Diag ram for a 144-bit SEARCH for 1 Device (Figure 45.) . . . .......................66

x144TablewithOneDevice(Figure46.)............................................67

LatencyofSEARCHfromInstructiontoSRAMAccessCycle,144-bit(Table34.).............67

ShiftofSSFandSSVfromSADR(Table35.).........................................67

144-bitSearchonTablesConfiguredasx144UsingUptoEightM7040NDevices........68

Hit/MissAssumption(Table36.)...................................................69

HardwareDiagramforaTablewithEightDevices(Figure47.) ...........................69

x144TablewithEightDevices(Figure48.)...........................................70

TimingDiagramsforx144UsingUptoEightM7040NDevices...........................71

LatencyofSEARCHfromInstructiontoSRAMAccessCycle,144-bit(Table37.).............74

ShiftofSSFandSSVfromSADR(Table38.).........................................74

4/159

M7040N

144-bitSearchonTablesConfiguredasx144UsingUpto31M7040NDevices...........74

Hit/MissAssumption(Table39.)...................................................75

HardwareDiagramforaTablewith31Devices(Figure52.) .............................76

HardwareDiagramforaBlockofUptoEightDevices(Figure53.)........................77

x144Tablewith31Devices(Figure54.).............................................78

Timing Diagrams for x144 Using Up to 31 M7040N Devices .............................79

LatencyofSEARCHfromInstructiontoSRAMAccessCycle,144-bit(Table40.).............90

ShiftofSSFandSSVfromSADR(Table41.).........................................90

288-bit SE ARCH on Tables Configured as x2 88 Using a Single M7040N Device ..........90

HardwareDiagramforaTablewithOneDevice(Figure66.).............................91

TimingDiagramfor288-bitSEARCH(OneDevice)(Figure67.) ..........................92

x288TablewithOneDevice(Figure68.)............................................93

LatencyofSEARCHfromCyclesCandDtoSRAMAccessCycle(Table42.)...............93

ShiftofSSFandSSVfromSADR(Table43.).........................................93

288-bit SE ARCH on Tables x288-confi gured Using Up to Eight M7040N Devices .........94

Hit/MissAssumption(Table44.)...................................................95

HardwareDiagramforaTablewithEightDevices(Figure69.) ...........................96

x288TablewithEightDevices(Figure70.)...........................................97

Timing Diagrams for x288-configured Using Up to Eight M7040N Devices . . ................98

LatencyofSEARCHfromCyclesCandDtoSRAMAccessCycle,288-bit(Table45.)........101

ShiftofSSFandSSVfromSADR(Table46.)........................................101

288-bitSearchonTablesConfiguredasx288UsingUpto31M7040NDevices..........101

Hit/MissAssumption(Table47.)..................................................103

HardwareDiagramforaTablewith31Devices(Figure74.) ............................103

HardwareDiagramforaBlockofUptoEightDevices(Figure75.).......................104

x288Tablewith31Devices(Figure76.)............................................105

Timing Diagrams for x288 Using Up to 31 M7040N Devices ............................106

LatencyofSEARCHfromCyclesCandDtoSRAMAccessCycle,288-bit(Table48.)........117

ShiftofSSFandSSVfromSADR(Table49.)........................................117

MIXED SEARCHES . . . ............................................................117

TablesConfiguredwithDifferentWidthsUsinganM7040NwithCFG_LLOW ..............117

TablesConfiguredtoDifferentWidthsusinganM7040NwithCFG_LHIGH................117

TimingDiagramforMixedSEARCH(OneDevice)(Figure88.)..........................118

Multi-WidthConfigurationsExample(Figure89.).....................................119

SearcheswithCFG_LSetHIGH(Table50.).........................................119

LRAMANDLDEVDESCRIPTION...................................................119

LEARNCOMMAND ..............................................................120

TimingDiagramofLEARN:TLSZ=00(Figure90.)...................................121

TimingDiagramofLEARN:TLSZ=01(ExceptontheLastDevice)(Figure91.).............122

TimingDiagramofLEARNonDevice7:TLSZ=01(Figure92.).........................123

LatencyofSRAMWRITECyclefromSecondCycleofLEARNInstruction(Table51.)........123

5/159

M7040N

DEPTH-CASCADING . ............................................................124

Depth-CascadingUptoEightDevices(OneBlock) ...................................124

Depth-Cascading Up to 31 Devices (4 Blocks) .......................................124

Depth-CascadingtoGeneratea“FULL”Signal.......................................124

Depth-CascadingtoFormaSingleBlock(Figure93.).................................125

Depth-CascadingFourBlocks(Figure94.)..........................................126

“FULL” Generation in a Cascaded Table (Figure 95.)..................................127

SRAM ADDRESSING . ............................................................128

Generating an SRAM Bus Address (Table 52.).......................................128

SRAMPIOAccess ............................................................128

SRAMREADwithaTableofOneDevice .........................................128

SRAMREADAccessforOneDevice(Figure96.)....................................129

SRAMREADwithaTableofUptoEightDevices ..................................130

TablewithEightDevices(Figure97.)..............................................131

SRAMREADThroughDevice0inaBlockofEightDevices(Figure98.)...................132

SRAMREADTimingforDevice7inaBlockofEightDevices(Figure99.) .................133

SRAMREADwithaTableofUpto31Devices.....................................134

Table of 31 Devices Made of Four Blocks (Figure 100.) ................................135

SRAM READ Through Device 0 in a Bank of 31 De vice s (Device 0 Timing) (Figure 10 1.) . . ...136

SRAM READ Through Device 0 in a Bank of 31 Devices (Device 30 Timing) (Figure 102.) . ...137

SRAMWRITEwithaTableofOneDevice.........................................138

SRAMWRITEAccessforOneDevice(Figure103.) ..................................139

SRAMWRITEwithaTableofUptoEightDevices..................................140

TablewithEightDevices(Figure104.).............................................141

SRAM WRITE T hrough Device 0 in a Block of Eight Devices (Figure 105.). . ...............142

SRAMWRITETimingforDevice7inaBlockofEightDevices(Figure106.)................143

SRAMWRITEwithTable(s)ofUpto31Devices ...................................144

Table of 31 Devices (Four Blocks) (Figure 107.). . . ...................................145

SRAM WRITE T hrough Device 0 in a Bank of 31 Devices (Device 0 Timing) (Figure 108.). . ...146

SRAM WRITE T hrough Device 0 in a Bank of 31 Devices (Device 30 Timing) (Figure 109.). ...147

JTAG(1149.1)TESTING ..........................................................148

SupportedOperations(Table53.).................................................148

TAPDeviceIDRegister(Table54.) ...............................................148

PARTNUMBERING ..............................................................149

PACKAGE MECHANICAL INFORMATION . . . .........................................150

APPENDIX......................................................................152

REVISIONHISTORY..............................................................158

6/159

DESCRIPTION

Overview

ST Microelectronic s, Inc.’s M7040N Search Engine incorporates patent-pending Associative Processing Technology™ (APT) and is designed t o

be a high-performance, pipelined, s y nc hronous,

64K-entry network database search engine. The

M7040N database ent ry size can be 72 bits, 144

bits, or 288 bits. In the 72-bit entry mode, the size

of the database is 64K entries. In the 144-bit

mode, the size of the dat abas e is 32K entries, and

in the 288-bit mode, the size of the database is

16K entries. The M7040N is configurable to support multiple databases with different entry sizes.

The 36-bit entry table can be implemented using

the Global Mask Registers (G MRs) building-database size of 128K entries with a single device.

Performance

The Search Engine can sustain 100 million transactions per second when the database is programmed or configured as 72 or 144 bits. When

the database is programme d to have an entry size

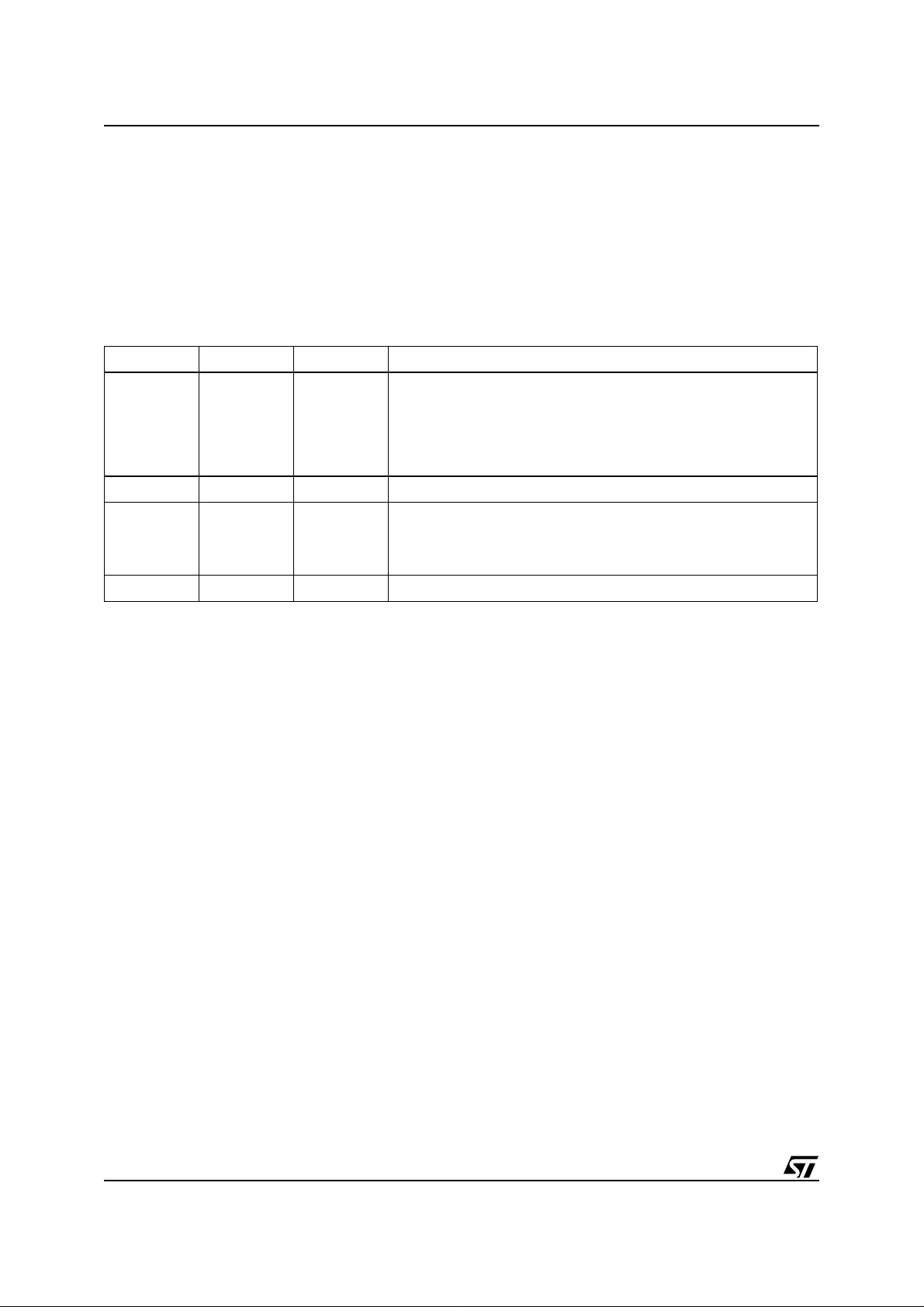

Table 1. Product Range

M7040N

of 36 or 288 bits, the Search En gine will perform at

50 million transactions per second. STM ’s

M7040N can be used to accelerate net work protocols such as Longest-prefix Match (CIDR), ARP,

MPLS, an d other Layer 2, 3, and 4 protocols.

Applications

Thishigh-speed, high-capacity Search Engine can

be deployed in a variety of networking and communications applications. The perform anc e and

features of t he M7040N make it attrac tive in applications such as Enterprise LAN switches and routers and broadband switchin g and/or routing

equipment supporting multiple data rates at OC–

48 and beyond. The Search E ngine is designed to

be scalable in order to support network database

sizes to 3968K entries specifically for environments that require large network poli cy databases.

Figure 4, page 10 shows t he block diagram for the

M7040N device.

Part Number

M7040N-100ZA1 1.65V 2.5 or 3.3V 100MHz Commercial

M7040N-083ZA1 1.5V 2.5 or 3.3V 83MHz Commercial

M7040N-066ZA1 1.5V 2.5 or 3.3V 66MHz Commercial

Operating

Supply Voltage

Operating I/O

Voltage

Speed Temperature Range

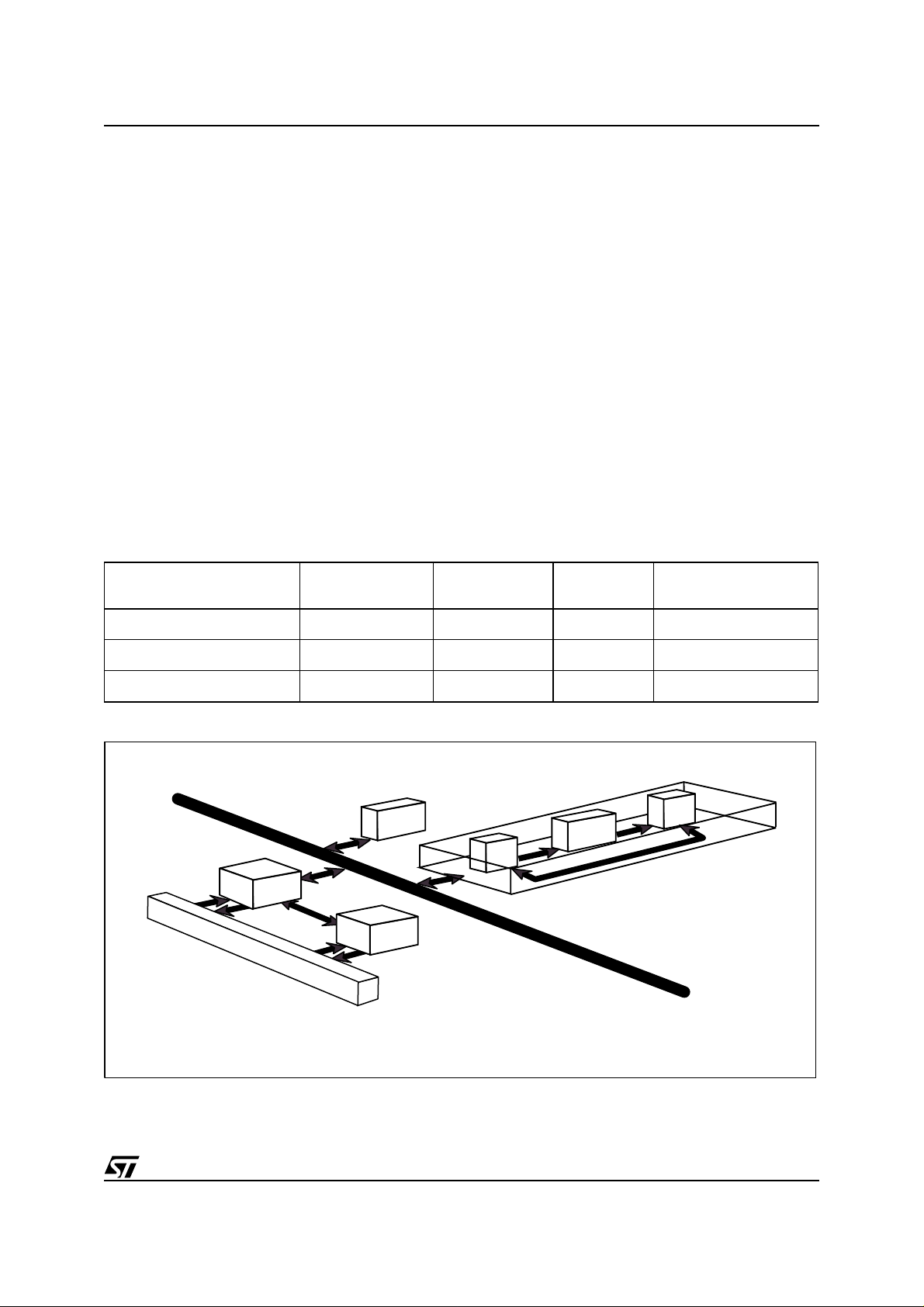

Figure 2. Switch/Router Implementation Using the M7040N

System Bus

Network Line Interfaces

Switch

Fabric

Program

Memory

Switch

Processor

Host

ASIC

Search

Engine

SRAM

Bank

AI04272

7/159

M7040N

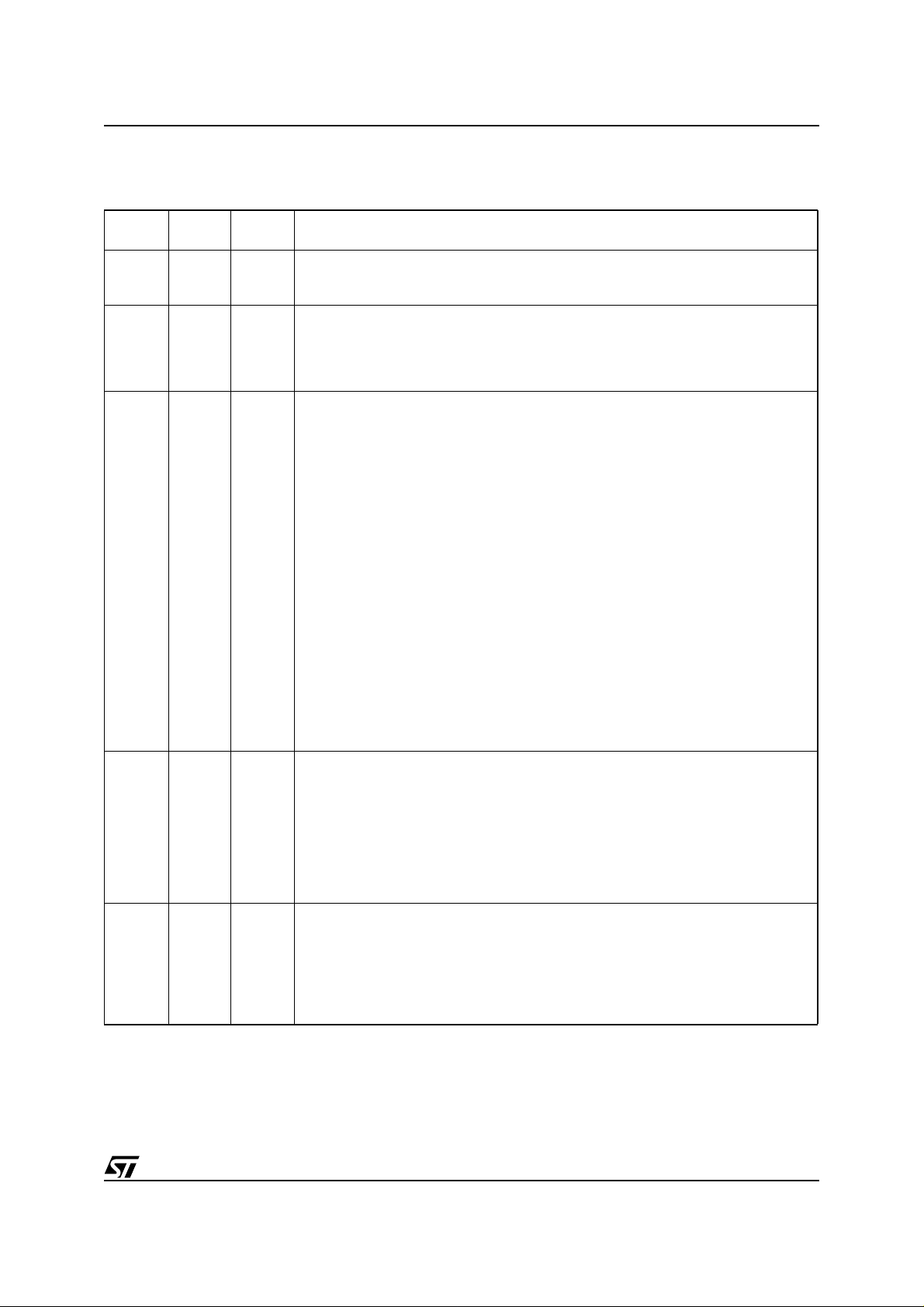

Table 2. Signal Names

Symbol

CLK_MODE

CLK2X_CLK1X I Master Clock

PHS_L I Phase

TEST_CO

(2)

TEST I Test Input (ST Use Only)

TEST_FM I Test Input (ST Use Only)

RST_L I Reset

TEST_PB

(3)

CFG_L I Configuration

Command and DQ Bus

CMD[10:0] I Command Bus

CMDV I Command Valid

DQ[71:0] I/O Address/Data Bus

(4)

ACK

(4)

EOT

SSF T SEARCH Successful Flag

SSV T

MULTI_HIT O Multiple Hit Flag

HIGH_SPEED I 100MHz Indicator

CLKTUNE[3:0] I PLL Tuner

Type

(1)

Description

Clocks and Reset

I Clock Mode

I Test Output (ST Use Only)

I Test Input (ST Use Only)

T READ Acknowledge

T End of Transfer

SEARCH Successful Flag

Valid

SRAM Interface

SADR[23:0] T SRAM Address

CE_L T SRAM Chip Enable

WE_L T SRAM Write Enable

OE_L T SRAM Output Enable

ALE_L T Address Latch Enable

Cascade Interface

LHI[6:0] I Local Hit In

LHO[1:0] O Local Hit Out

BHI[2:0] I Block Hit In

BHO[2:0] O Block Hit Out

FULI[6:0] I Full In

FULO[1:0] O Full Out

FULL O Full Flag

Device Identification

ID[4:0] I Device Identification

Supplies

Chip Core Supply (1.5V for

V

DD

n/a

66 and 83MSPS; 1.65 for

100MSPS)

V

DDQ

Chip I/O Supply (2.5 or

n/a

3.3V)

Test Access Port

TDI I

TCK I

Test Access Port’s Test

Data In

Test Access Port’s Test

Clock

TDO T

TMS I

TRST_L I Test Access Port’s Reset

Note: 1. Signal types are: I = Input only; I/O = Input or Output; O = Output; and T = Tristate

See DESCRIPTIONS FOR CONNECTION DIAGRAM (Figure 3, page 9), page 152 for individual connection details.

2. In the previous versions of this specification, this signal was called, “CLK_OUT.”

3. In previous versions of this specification, this signal was called, “PLL_BYPASS.”

4. ACK and EOT Signals require a weak, external pull-down resistor of 47 KΩ or 100 KΩ.

8/159

Test Access Port’s Test

Data Out

Test Access Port’s Test

Mode Select

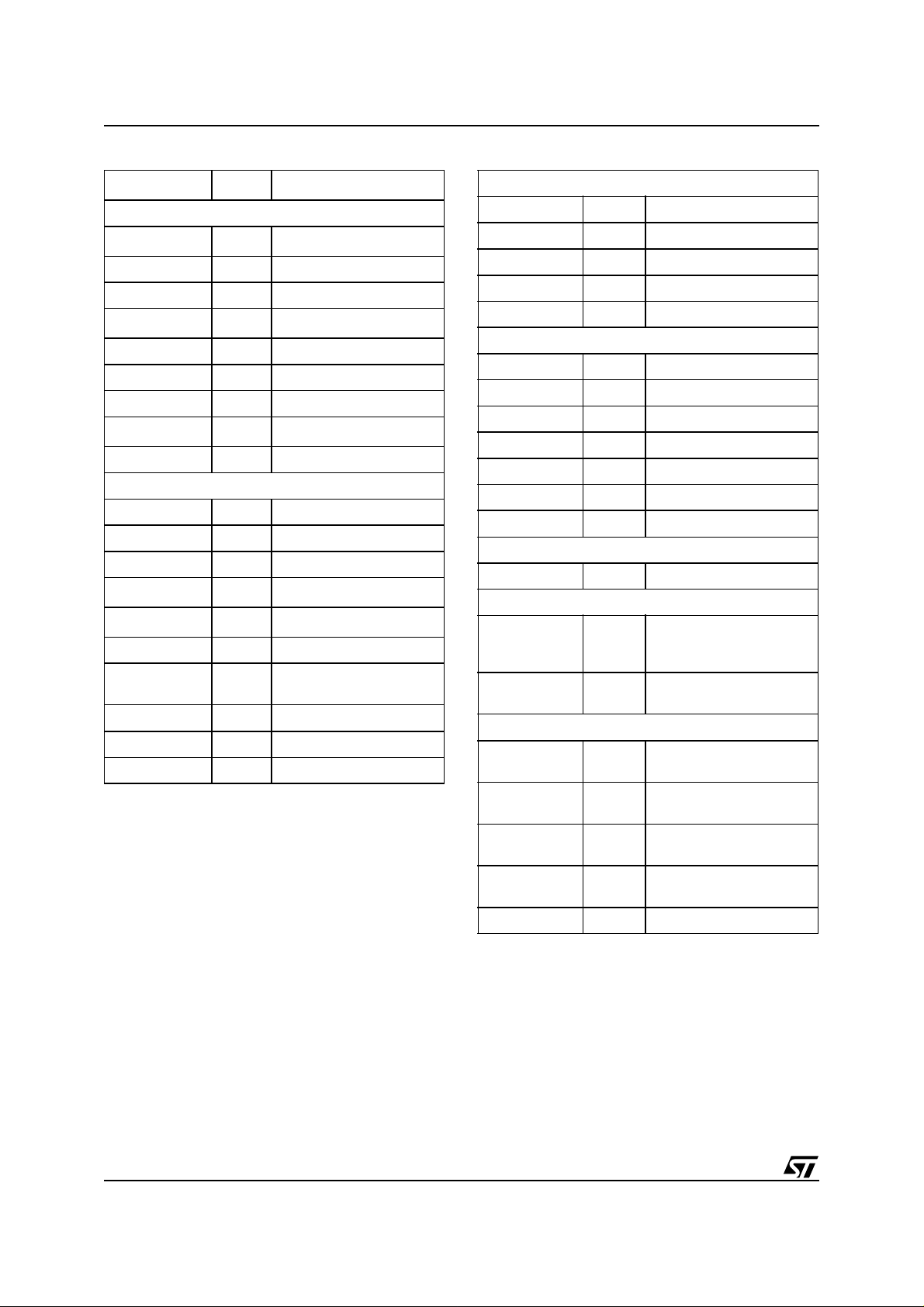

Figure 3. Connections

123456789

CLK

V

TDI

TCK

ID0

ID1

ID3

LHI0

LHI2

LHI6

LHO0

DDQ

BHI1

DDQ

DDQ

FULL

V

TEST

CO

DQ71

DDQ

V

DQ69

SS

V

TMS

V

TDO

L

V

V

DDQ

V

ID2

V

ID4

LHI1

NC1

V

LHI3

LHI4

LHI5

V

LHO1

V

BHI0

V

BHI2

MULTI_

V

HIT

V

BHO1

V

V

SS

V

FULI1

DDQ

FULI4FULI3

FULI5

NC2

V

FULO0

V

V

DDQ

V

ACK

V

EOT

SS

V

V

DDQ

V

DQ70

SS

CLK

DQ68

TUNE2

DD

DD

DD

DD

DDQ

DQ63

DQ67

DQ61

DQ65

V

V

DD

DD

V

V

SS

SS

V

SS

V

SS

V

SS

DD

V

SS

V

SS

V

SS

V

DD

DD

V

DD

DD

V

DD

DD

V

DD

DD

V

DD

DD

V

DD

DD

V

SS

V

SS

V

SS

V

SS

DD

V

SS

DD

V

DD

SS

VSSV

DD

SS

V

V

DD

DD

DD

DQ64

V

DDQ

DQ66

DQ62

1234567 8 91011

AA

AB

AC

AD

AE

A

TUNE3

B

C

TRST_

D

E

F

G

H

J

K

L

V

M

N

BHO0

P

V

R

BHO2

T

FULI0

U

FULI2

V

V

W

FULI6

Y

FULO1

RST_L

TEST_

AF

V

DDQ

DQ59

V

V

V

V

DQ60

V

DDQ

M7040N

11

10

DQ53

DQ57

V

DQ55

DDQ

V

NC8

DD

DD

V

V

SS

SS

V

V

SS

SS

V

NC3

DD

DD

DQ54

DQ58

DQ56

DQ52

DQ43

DQ51

DQ45

DQ47

V

DQ49

DDQ

V

V

V

DQ50

DQ48

V

DDQ

SS

SS

V

SS

SS

DQ46

DQ44

V

DDQ

SS

SS

12 13 14 15 16

DQ35

DQ37

DQ41

V

DDQ

DQ39

V

V

V

V

V

V

DQ42

DQ40

DQ33

V

V

DD

DD

DD

V

V

V

V

V

V

V

V

V

V

DQ38

DQ36

DD

DD

V

SS

SS

V

SS

SS

V

SS

SS

V

SS

SS

V

SS

SS

V

SS

SS

V

DD

DD

V

DD

DD

V

DDQ

DQ34

DD

SS

V

SS

V

SS

SS

V

SS

V

SS

DD

DD

12 13 14 15

DQ31

DQ29

V

V

V

V

V

V

V

V

V

DQ32

DQ30

DQ17

DQ15

DQ13

V

V

DQ16

DQ18

DQ14

19

V

DDQ

DQ11

NC7

V

SS

V

SS

NC4

DQ12

V

DDQ

19 20

17 18

V

DQ25

DDQ

DQ27

V

DD

VDDV

DD

VSSV

SS

V

SS

V

SS

V

SS

V

SS

VSSV

SS

V

DD

V

DD

DQ28

V

DDQ

DQ21

V

DDQ

DQ23

V

DQ19

DD

DD

V

V

DD

SS

SS

V

SS

SS

V

SS

SS

V

SS

SS

V

SS

SS

SS

V

V

DD

DD

DD

V

DQ26

DQ24

16

DD

SS

DQ20

V

DDQ

DQ22

17 18

21

20

DQ9

DQ7

V

V

SS

V

SS

V

DQ10

DQ8

22 23 24

TEST_

DQ3

DQ5

V

DD

SS

SS

DD

TEST_

DQ1

DDQ

V

V

V

DQ6

DQ4

21

V

V

DD

DD

V

V

SS

SS

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

VSSV

SS

V

V

DD

DD

V

DQ0

DDQ

DQ2

22 23 24 25 26

25 26

CLK

HIGH_

V

DDQ

FM

SPEED

V

CFG_L

PB

SADR

V

DD

DD

SADR

V

SS

DD

SADR

V

SS

DD

SADR

V

SS

DD

SADR

V

DD

SS

V

NC6

SS

SADR

SADR

SS

11

SADR

V

SS

13

SADR

V

DD

DD

V

V

DD

DD

SADR

V

DD

DD

SADR

V

DD

DD

SADR

V

DD

DD

CLK_

V

DD

DD

MODE

PHS_L

OE_L

SS

V

V

CE_L

SS

V

NC5

CMDV

SS

V

V

CMD1

SS

DD

V

V

CMD3

SS

DD

V

CMD5

SS

DD

V

CMD6

SS

DD

V

CMD8

DD

DD

V

V

DDQ

SSFSSV

CMD10

5

DDQ

12

DDQ

15

DDQ

19

21

22

DDQ

A

TUNE0

SADR

B

SS

0

V

C

DDQ

1

SADR

D

2

3

SADR

E

4

V

F

DDQ

6

SADR

G

8

7

SADR

H

9

SADR

J

10

SADR

K

14

SADR

L

16

SADR

M

17

SADR

N

18

SADR

P

20

V

R

DDQ

SADR

T

23

CLK1x/

U

CLK2x

WE_L

V

ALE_L

W

CMD0

Y

CMD2

AA

CMD4

AB

V

AC

DDQ

CMD7

AD

CLK

AE

SS

TUNE1

AF

CMD9

AI04646

9/159

M7040N

Figure 4. M7040N Block Diagram

PHS_L

CLK1X_CLK2X

RST_L

CLK_MODE

DQ [71:0]

Compare/PIO Data

CMD [10:0]

CMDV

ACK

EOT

Command

Decode

and PIO Access

ID [4:0]

Comparand Registers[15:0]

Global Mask Registers [15:0]

Information and Command Register

Burst Read Register

Burst Write Register

Next Free Address Register

Search Successful Index Registers [7:0]

(All registers are 72-bit-wide)

Compare/PIO Data

Cmd

Configurable as

128K x 36

64K x 72

32K x 144

16K x 288

Data Array

Configurable as

128K x 36

Address Decode

Priority Encode

64K x 72

32K x 144

16K x 288

Mask Array

Match Logic

TAP

Controller

Pipeline

and

SRAM

Control

TAP

SADR [23:0]

OE_L

WE_L

CE_L

ALE_L

Full LogicFULL [6:0]

FULL

LHI [6:0]

BHI [2:0]

FULO [1:0]

Arbitration

Logic

LHO [1:0]

BHO [2:0]

SSF

SSV

AI04645

10/159

M7040N

MAXIMUM RATING

Stressingthedeviceabovetheratinglistedinthe

“Absolute Maximum Ratings” table may cause

permanent damage to the device. These are

stress ratings only and operation of t he dev ice at

these or any other conditions above those indicated in the Operating sections of this specification is

Table 3. Absolute Maximum Ratings

Symbol Parameter Value Unit

T

STG

(1)

T

SLD

V

DD

V

DDQ

V

DDQ

V

DDQ

I

O

Note: 1. Solderingtemperaturenotto exceed260°C for 10 seconds (total thermal budget not to exceed 150°C for longer than 30 seconds).

Storage Temperature (VDDOff)

Lead Solder Temperature for 10 seconds 235 °C

VDDOperating Supply Voltage

V

Voltage for I/O (3.3V)

DDQ

V

Voltage for I/O (2.5V)

DDQ

V

Voltage for I/O (1.8V)

DDQ

Output Current 100 mA

not implied. Exposure to Absolute Maximum Ra ting conditions for extended periods m ay affect device reliability. Refer also to the

STMicroelectronics SURE Program and other relevant quality documents.

–0to70 °C

CLK1X = 83MHz 1.575 V

CLK1X = 100MHz 1.733 V

3.5 V

2.625 V

1.9 V

11/159

M7040N

DC AND AC PARAMETERS

This section summarizes the operating and m easurement conditions, as well as the DC and AC

characteristics of the device. The parameters in

the following DC and AC Charact eristic tables are

derived from tests performed under the Measure-

Table 4. DC and AC Measurement Conditions

Sym Parameter Min Max Units

ment Conditions listed i n the relevant tables. Designers should check that the operating conditions

in their projects match the measurement co nditions when using the quoted parameters.

V

DDVDD

V

DDQVDDQ

V

DDQVDDQ

V

DDQVDDQ

t

A

Operating Supply Voltage

Voltage for I/O (3.3V)

Voltage for I/O (2.5V)

Voltage for I/O (1.8V)

Ambient Operating Temperature 0 70 °C

Supply Voltage Tolerance –5+5%

Input Pulse Levels (V

Input Pulse Levels (V

Input Pulse Levels (V

DDQ

DDQ

DDQ

= 3.3V)

= 2.5V)

= 1.8V)

Input Rise and Fall Times at 0.3V and 2.7V (V

Input Rise and Fall Times at 0.25V and 2.25V (V

Input Timing Reference Levels (V

Input Timing Reference Levels (V

Input Timing Reference Levels (V

Output Timing Reference Levels (V

Output Timing Reference Levels (V

Output Timing Reference Levels (V

DDQ

DDQ

DDQ

DDQ

DDQ

DDQ

= 3.3V)

= 2.5V)

= 1.8V)

Output Load

Note: 1. Maximum allowable applies to overshoot only (V

2. Minimum allowable applies to undershootonly.

CLK1X = 83MHz 1.425 1.575 V

CLK1X = 100MHz 1.568 1.733 V

3.1 3.5 V

2.375 2.625 V

1.7 1.9 V

GND to 3.0 V

GND to 2.5 V

GND to 1.8 V

DDQ

= 3.3V)

DDQ

= 2.5V)

≤ 2ns (see Figure 6,

page 13)

≤ 2ns (see Figure 6,

page 13)

1.5 V

1.25 V

0.9 V

= 3.3V)

= 2.5V)

= 1.8V)

1.5 V

1.25 V

0.9 V

(see Figure 5 and

Figure 7, page 13)

is 3.3Vsupply).

DDQ

ns

ns

V

12/159

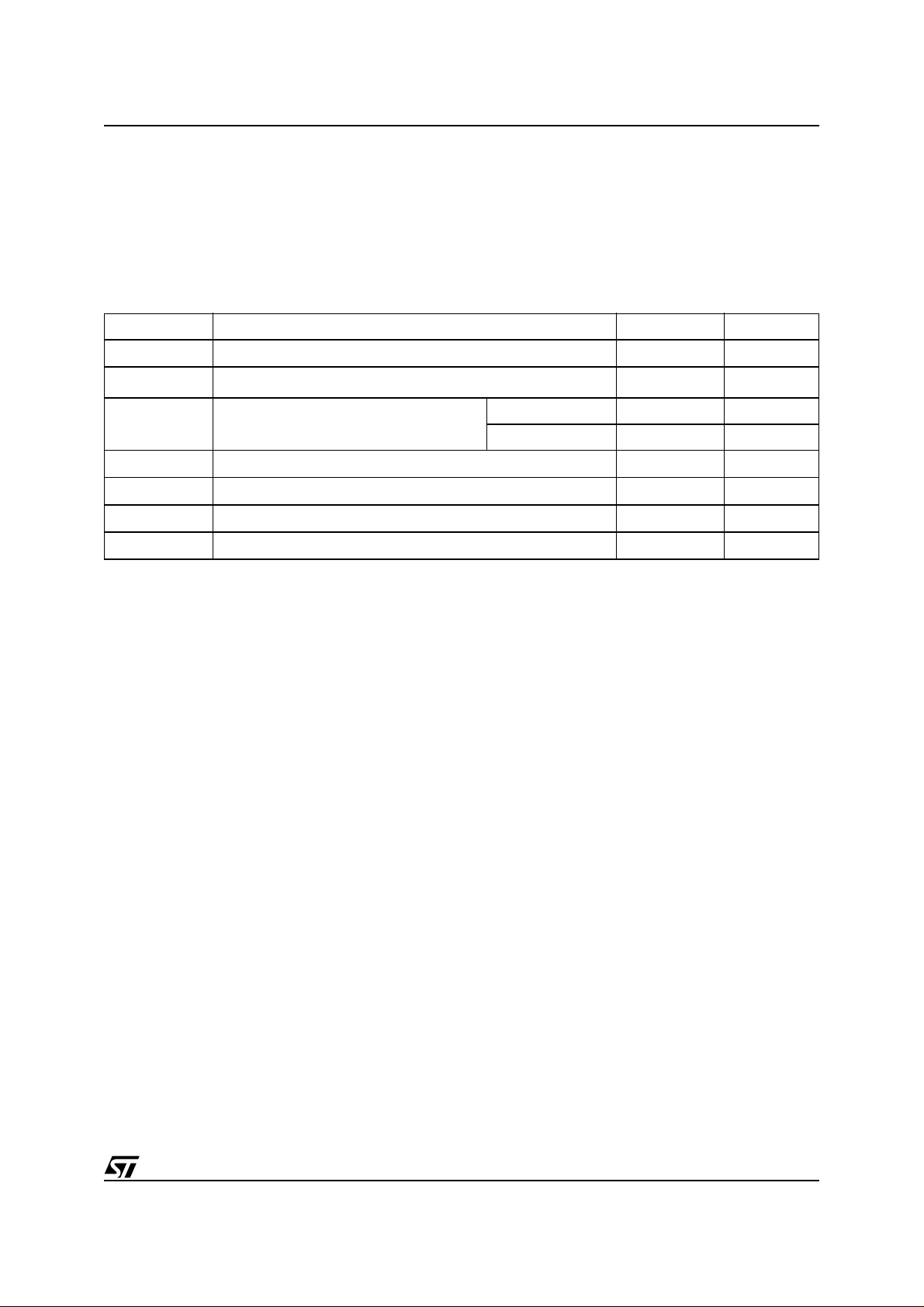

Figure 5. M7040N 1.8, 2.5, or 3.3V AC Testing Load

50ΩZ0 = 50Ω

M7040N

D

OUT

VL= 1.25V for V

VL= 1.50V for V

C

L

Figure 6. M7040N 1.8, 2.5, or 3.3V Inp ut Waveform

+2.5V V

+3.0V V

DDQ

DDQ

= 2.5V /

= 3.3V

90%

10%

GND

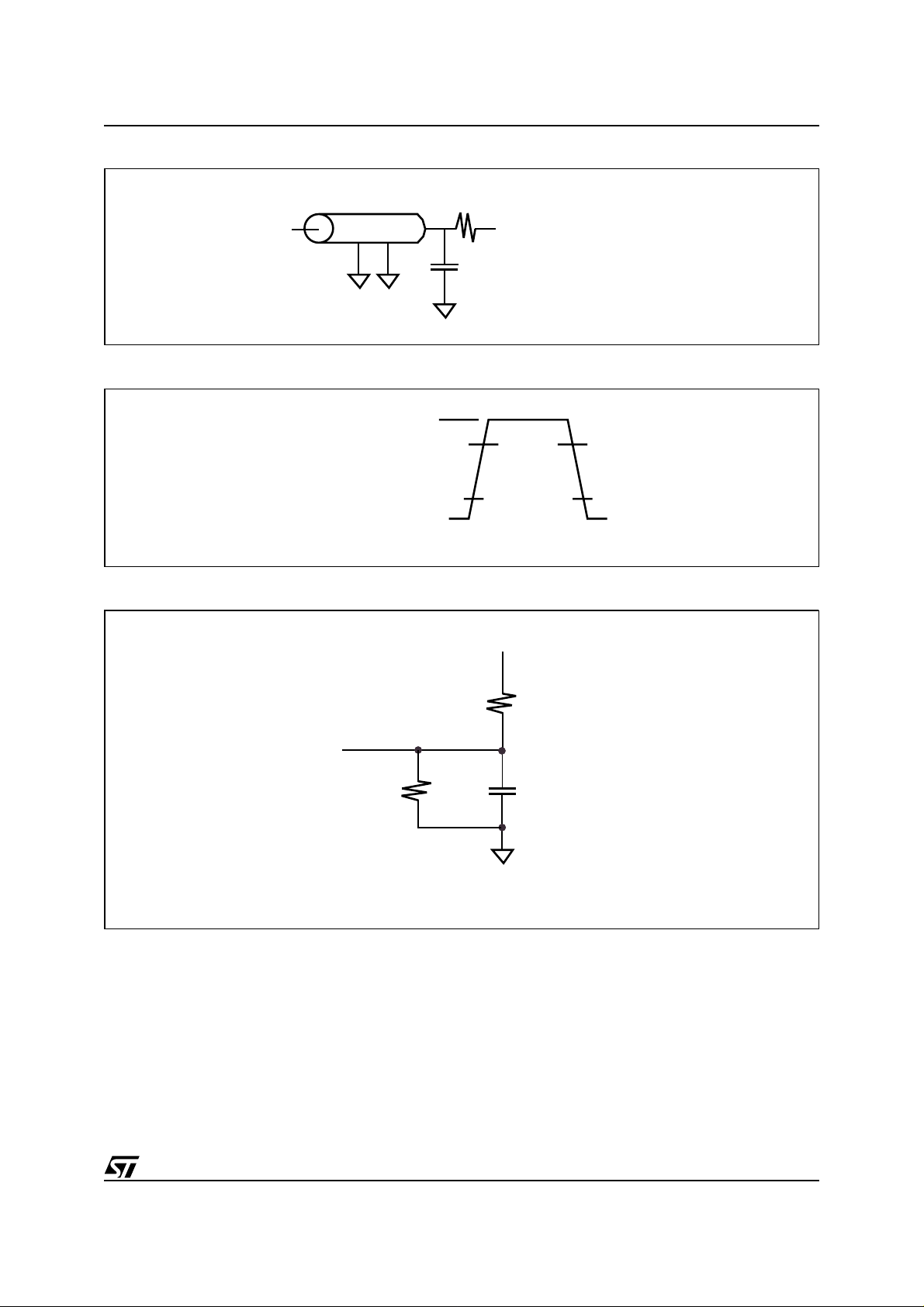

Figure 7. M7040N 1.8, 2.5, or 3.3V I/O Output Load Equivalent

V

DDQ

DDQ

DDQ

90%

10%

AI04752

= 2.5V

= 3.3V

AI04751

208Ω for V

158Ω for V

DDQ

DDQ

= 2.5V

= 3.3V

Q

192Ω for V

175Ω for V

Note: 1. Output loading is specified with CL = 5pF as in Figure 7. Transition is measured at ± 200 mV from steady-state voltage.

2. TheloadusedforV

testing is shown in Figure 7.

OH,VOL

DDQ

DDQ

= 2.5V

= 3.3V

5pF

For Hi-Z and VOL/V

OH

(1, 2)

AI04753

13/159

M7040N

Table 5. Capacitance

Symbol Parameter

C

IN

C

IO

Note: 1. Effectivecapacitance measured withpower supply. Sampled only, not100% tested.

2. At 25°C, f = 1MHz.

3. Outputs deselected.

Input Capacitance

(3)

Output Capacitance

Test Condition

V

IN

V

OUT

Table 6. DC Characteristics

Sym Parameter

Test Condition

(1,2)

=0V

=0V

(1)

Min Max Unit

6pF

6pF

Min Max Unit

Input Leakage Current

I

LI

I

Output Leakage Current

LO

Input Low Voltage (V

V

IL

Input High Voltage (V

V

IH

Input Low Voltage (V

V

IL

Input High Voltage (V

V

IH

Input Low Voltage (V

V

IL

Input High Voltage (V

V

IH

Output Low Voltage (V

V

OL

Output High Voltage (V

V

OH

Output Low Voltage (V

V

OL

Output High Voltage (V

V

OH

Output Low Voltage (V

V

OL

Output High Voltage (V

V

OH

DDQ

DDQ

DDQ

1.65V Supply Current at VDD(max)

1.5V Supply Current at V

I

DD1

1.5V Supply Current at V

V

DDQ=VDDQ

V

DDQ=VDDQ

= 3.3V)

= 3.3V)

DDQ

= 2.5V)

= 2.5V)

DDQ

= 1.8V)

= 1.8V) 0.7 * V

DDQ

= 3.3V) V

DDQ

= 3.3V) V

DDQ

= 2.5V) V

DDQ

= 2.5V) V

DDQ

= 1.8V) V

DDQ

= 1.8V) V

DDQ

(max)

DD

(max)

DD

(max), VIN= 0 to V

(max), VIN= 0 to V

DDQ=VDDQ

DDQ=VDDQ

DDQ=VDDQ

DDQ=VDDQ

DDQ=VDDQ

DDQ=VDDQ

(min), IOL= 16mA

(min), IOH= 8mA

(min), IOL=8mA

(min), IOH= 8mA

(min), IOL=8mA

(min), IOH= 8mA VDD– 0.45

100MHz Search Rate 6.0 A

83MHz Search Rate 5.0 A

66MHz Search Rate 4.0 A

100MHz Search Rate, I

I

3.3V Supply Current at VDD(max)

DD2

83MHz Search Rate, I

66MHz Search Rate, I

100MHz Search Rate, I

2.5V Supply Current at VDD(max)

I

DD2

83MHz Search Rate, I

66MHz Search Rate, I

Note: 1. Valid for Ambient Operating Temperature: TA=0to70°C; VDD=1.5V.

OUT

OUT

OUT

OUT

OUT

OUT

DDQ

DDQ

=0mA

=0mA

=0mA

=0mA

=0mA

=0mA

(max)

(max)

–10 +10 µA

–10 +10 µA

–0.3 0.8 V

V

2.0

DDQ

+0.3

–0.3 0.7 V

V

1.7

–0.3

DDQVDDQ

DDQ

0.35 * V

+0.3

DDQ

+0.3

0.4 V

2.4 V

0.4 V

2.0 V

0.45 V

350 mA

300 mA

240 mA

350 mA

300 mA

240 mA

V

V

V

V

V

14/159

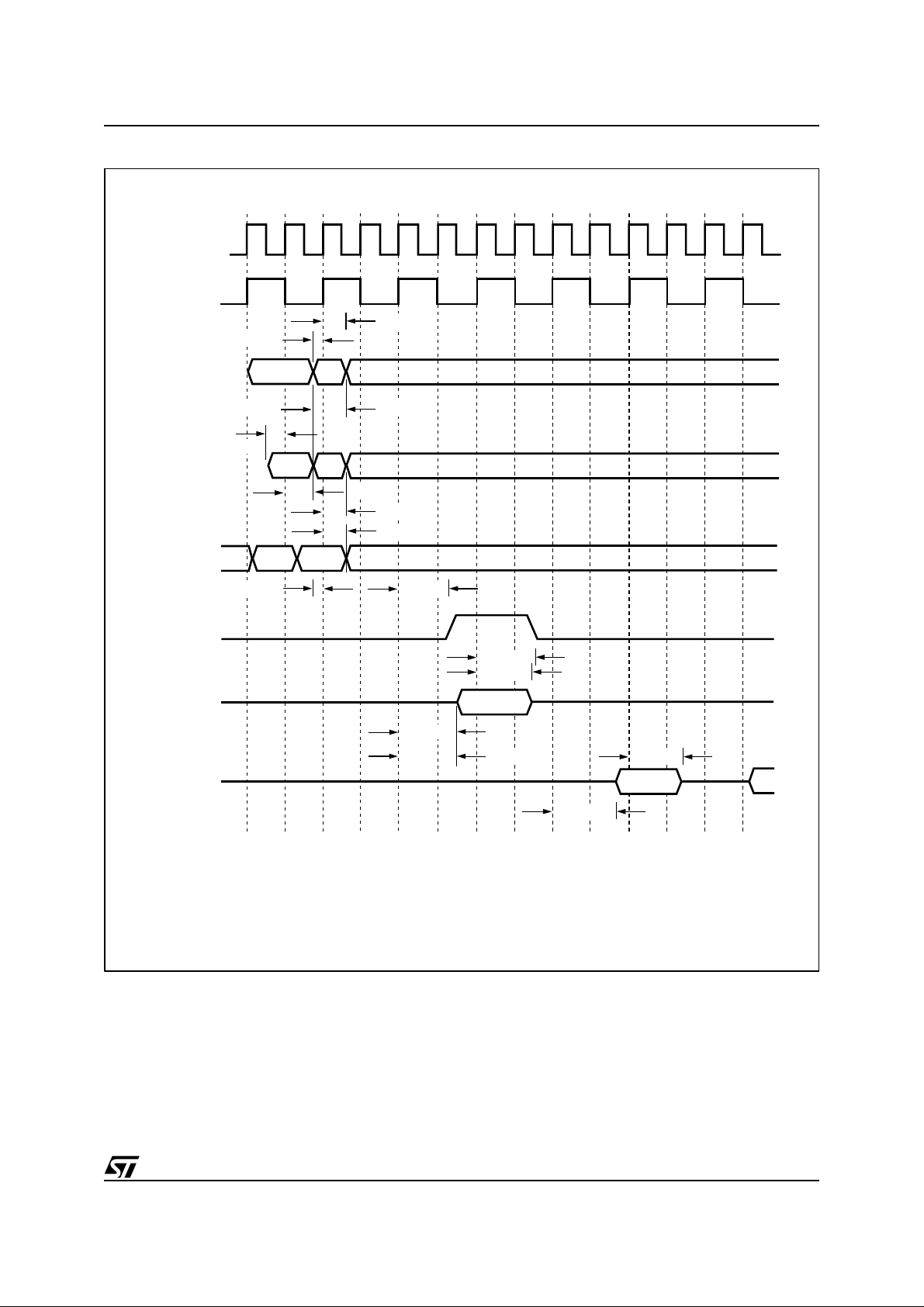

Figure 8. AC Tim ing Waveforms with CLK2X

M7040N

CLK2X

CLK

Signal

Group 0

Signal

Group 1

Signal

Group 2

Signal

Group 3

Signal

Group 4

Signal

Group 5

tISCH

tISCH

tICSCH

Cycle

0

tISCH

Cycle

1

Cycle

2

Cycle

tIHCH

3

tIHCH

tIHCH

tIHCH

tICHCH

tCKHOV

Cycle

4

tCKHSV

Cycle

5

Cycle

6

tCKHOV

tCKHSHZ

tCKHSLZ

Cycle

7

Cycle

8

tCKHDV

Cycle

9

Cycle

10

tCKHDZ

Cycle

11

Cycle

12

Signal Group 0: PHS_L, RST_L

Signal Group 1: DQ, CMD, CMDV

Signal Group 2: LHI, BHI, FULI

Signal Group 3: LHO, BHO, FULO, FULL

Signal Group 4: SADR, CE_L, OE_L, WE_L, ALE_L, SSF, SSV

Signal Group 5: DQ, ACK, EOT

AI04748

15/159

M7040N

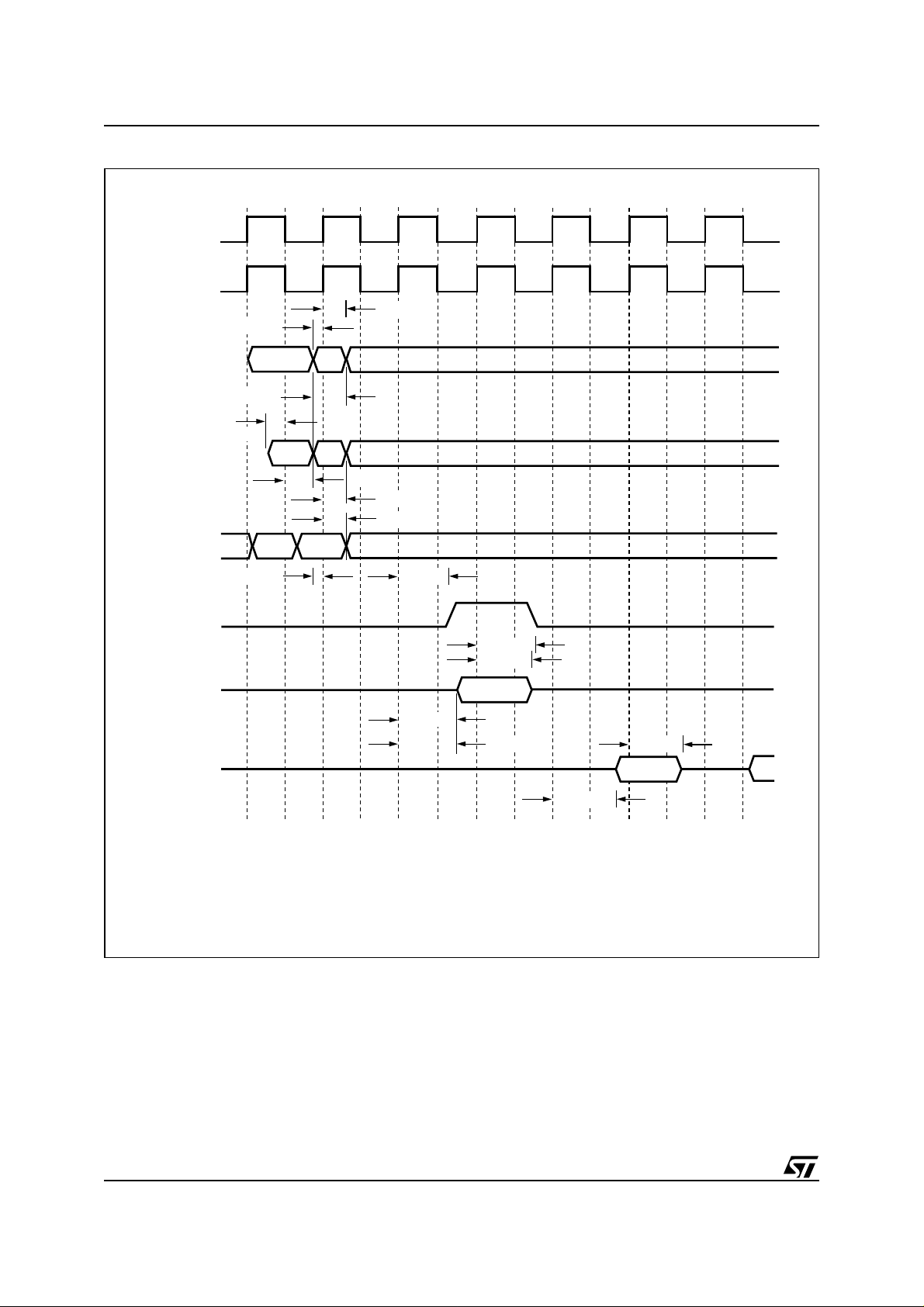

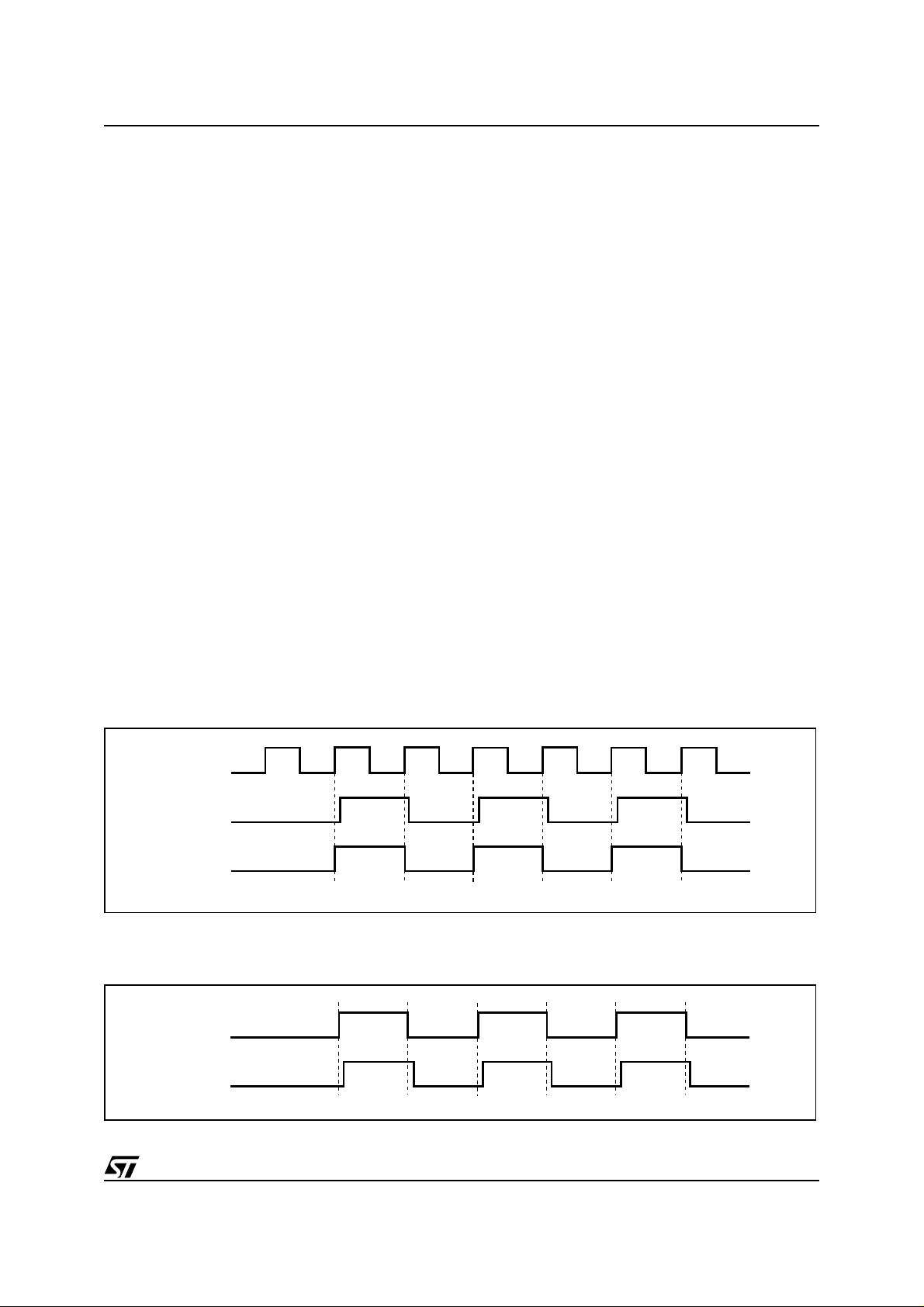

Figure 9. AC Tim ing Waveforms with CLK1X

CLK1X

CLK

Signal

Group 0

Signal

Group 1

Signal

Group 2

Signal

Group 3

Signal

Group 4

Signal

Group 5

tISCH

tISCH

tICSCH

Cycle

0

tISCH

Cycle

1

Cycle

2

Cycle

tIHCH

3

tIHCH

tIHCH

tICHCH

tCKHOV

Cycle

4

tCKHSV

Cycle

5

Cycle

6

tCKHOV

tCKHSHZ

tCKHSLZ

Cycle

7

Cycle

8

tCKHDV

Cycle

9

Cycle

10

tCKHDZ

Cycle

11

Cycle

12

Signal Group 0: PHS_L, RST_L

Signal Group 1: DQ, CMD, CMDV

Signal Group 2: LHI, BHI, FULI

Signal Group 3: LHO, BHO, FULO, FULL

Signal Group 4: SADR, CE_L, OE_L, WE_L, ALE_L, SSF, SSV

Signal Group 5: DQ, ACK, EOT

16/159

AI04749

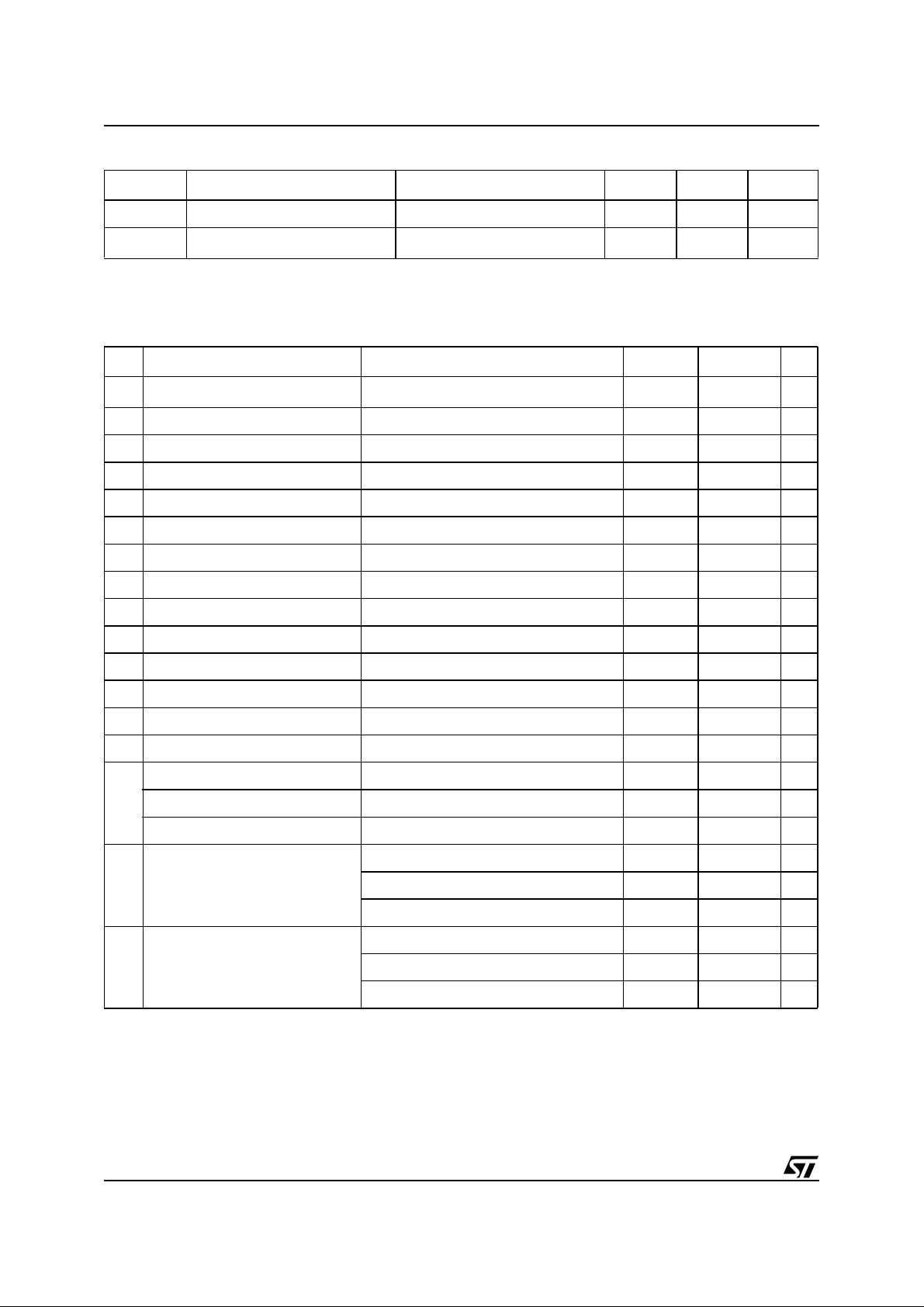

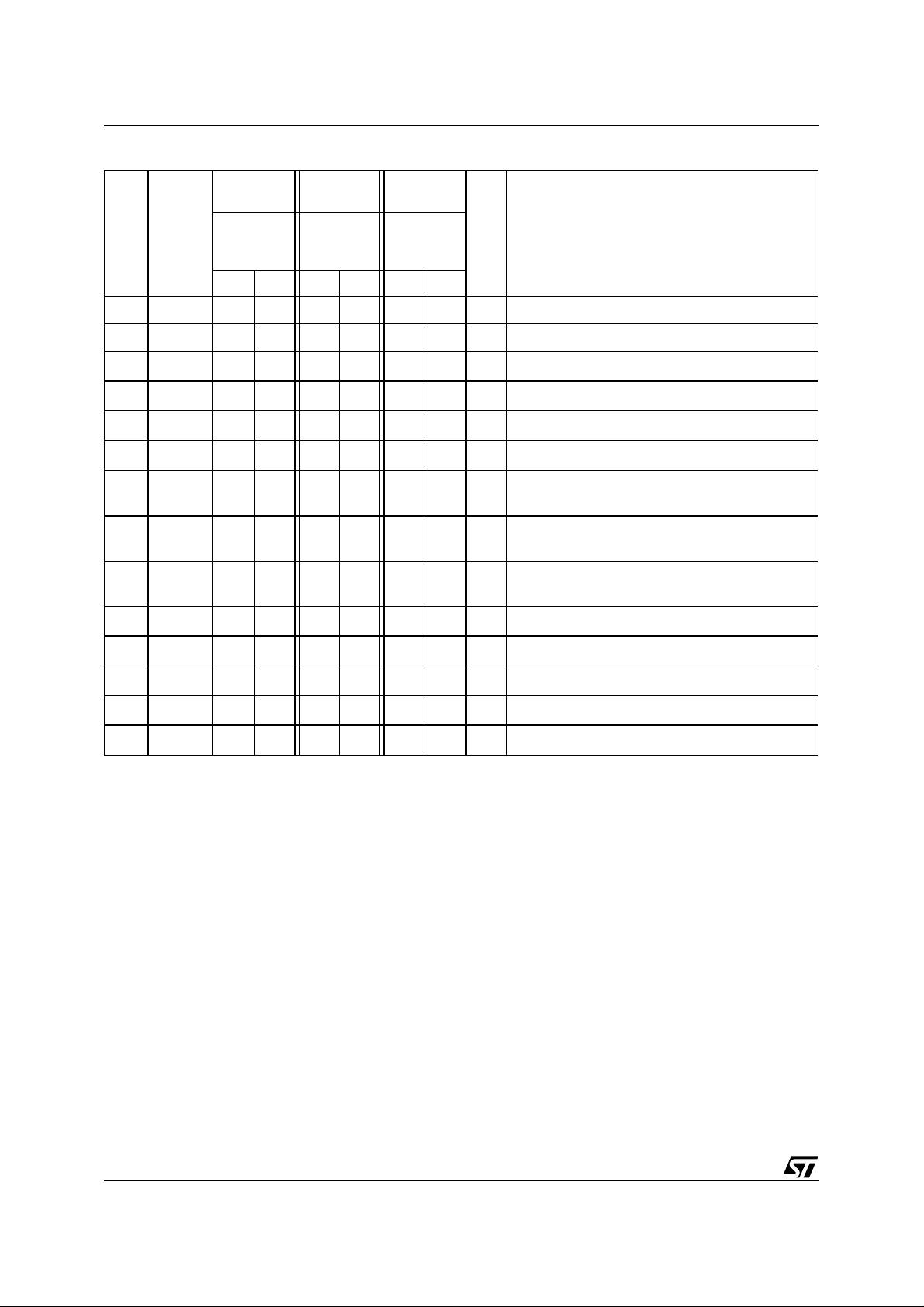

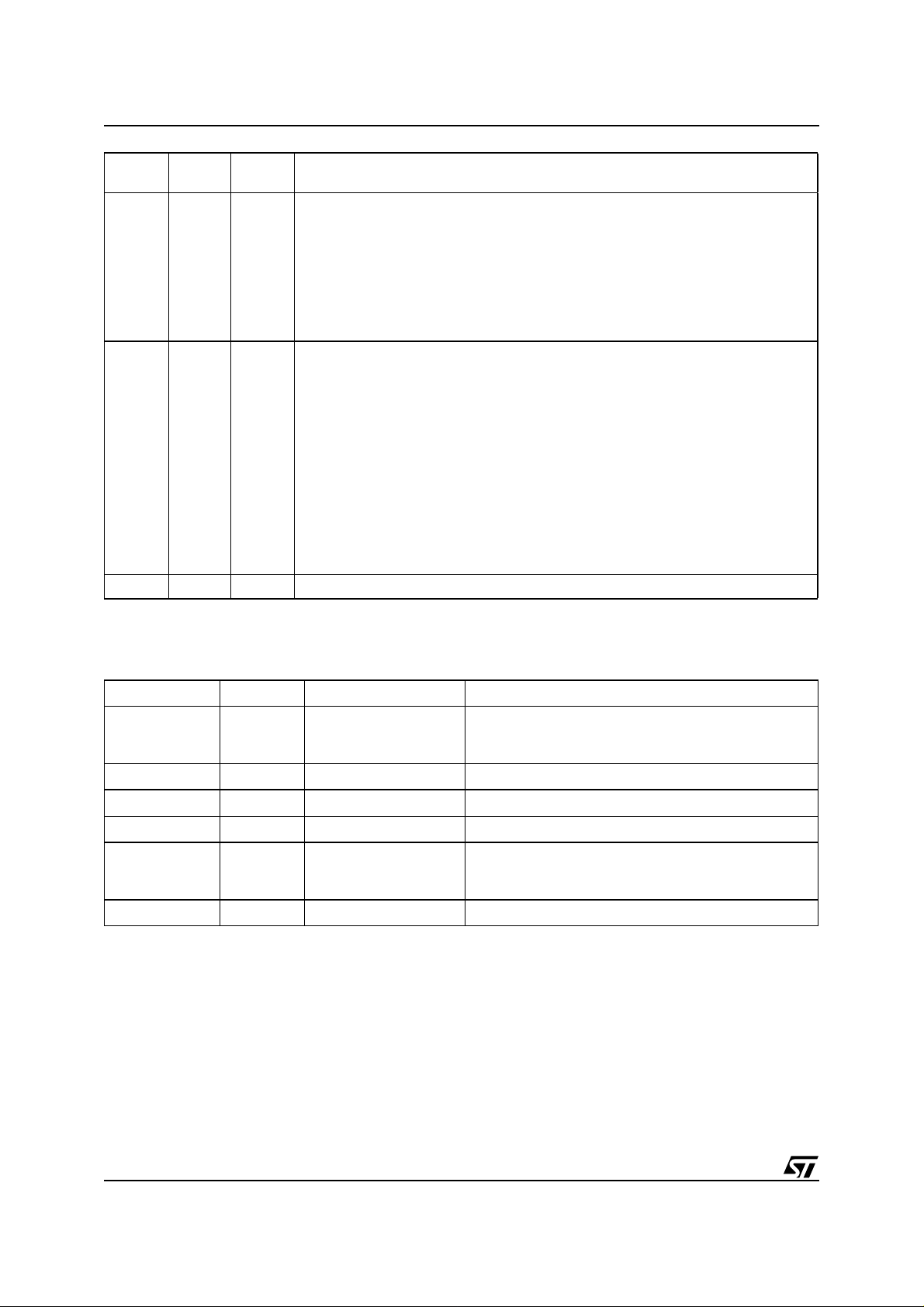

Table 7. AC Timing Parameters with CLK2X

M7040N-

066

Row Sym

(V

DDQ

3.3V, 2.5V)

Min Max Min Max Min Max

f

1

CLOCK

t

2

CLOK

t

3

CKHI

t

4

CKLO

t

5

ISCH

t

6

IHCH

t

7

ICSCH

t

8

ICHCH

t

9

CKHOV

t

10

CKHDV

t

11

CKHDZ

t

12

CKHSV

t

13

CKHSHZ

t

14

CKHSLZ

Note: 1. Valid for Ambient Operating Temperature: TA=0to70°C; VDD=1.5V.

2. Values are based on 50% signal levels.

3. Based on an AC load of CL = 30pF (see Figure 5, Figure 6, and Figure 7, page 13).

4. These parameters are sampled and not 100% tested, and are based on an AC load of 5pF.

40 133 40 166 40 200 MHz CLK2X frequency

3.0 2.4 2.0 ns

3.0 2.4 2.0 ns

2.5 1.8 1.5 ns

0.6 0.6 0.5 ns

4.2 3.5 3.0 ns

0.6 0.6 0.5 ns

7.0 6.5 6.0 ns

=

M7040N-

083

(V

DDQ

3.3V, 2.5V,

1.8V)

=

M7040N-

100

=

(V

DDQ

3.3V, 2.5V)

Unit

0.5 0.5 0.5 ms PLL lock time

CLK2X high pulse

CLK2X low pulse

Input Setup Time to CLK2X rising edge

Input Hold Time to CLK2X rising edge

Cascaded Input Setup Time to CLK2X rising

(2)

edge

Cascaded Input Hold Time to CLK2X rising edge

8.5 7.0 6.5 ns

9.0 7.5 7.0 ns

8.5 7.0 6.5 ns

9.0 7.5 7.0 ns

6.5 6.0 5.5 ns

Rising edge of CLK2X to LHO, FULO, BHO, FULL

(3)

valid

Rising edge of CLK2X to DQ valid

Rising edge of CLK2X to DQ high-Z

Rising edge of CLK2X to SRAM bus valid

Rising edge of CLK2X to SRAM bus high-Z

Rising edge of CLK2X to SRAM bus low-Z

Description

(2)

(2)

M7040N

(1)

(2)

(2)

(2)

(3)

(4)

(3)

(4)

(4)

17/159

M7040N

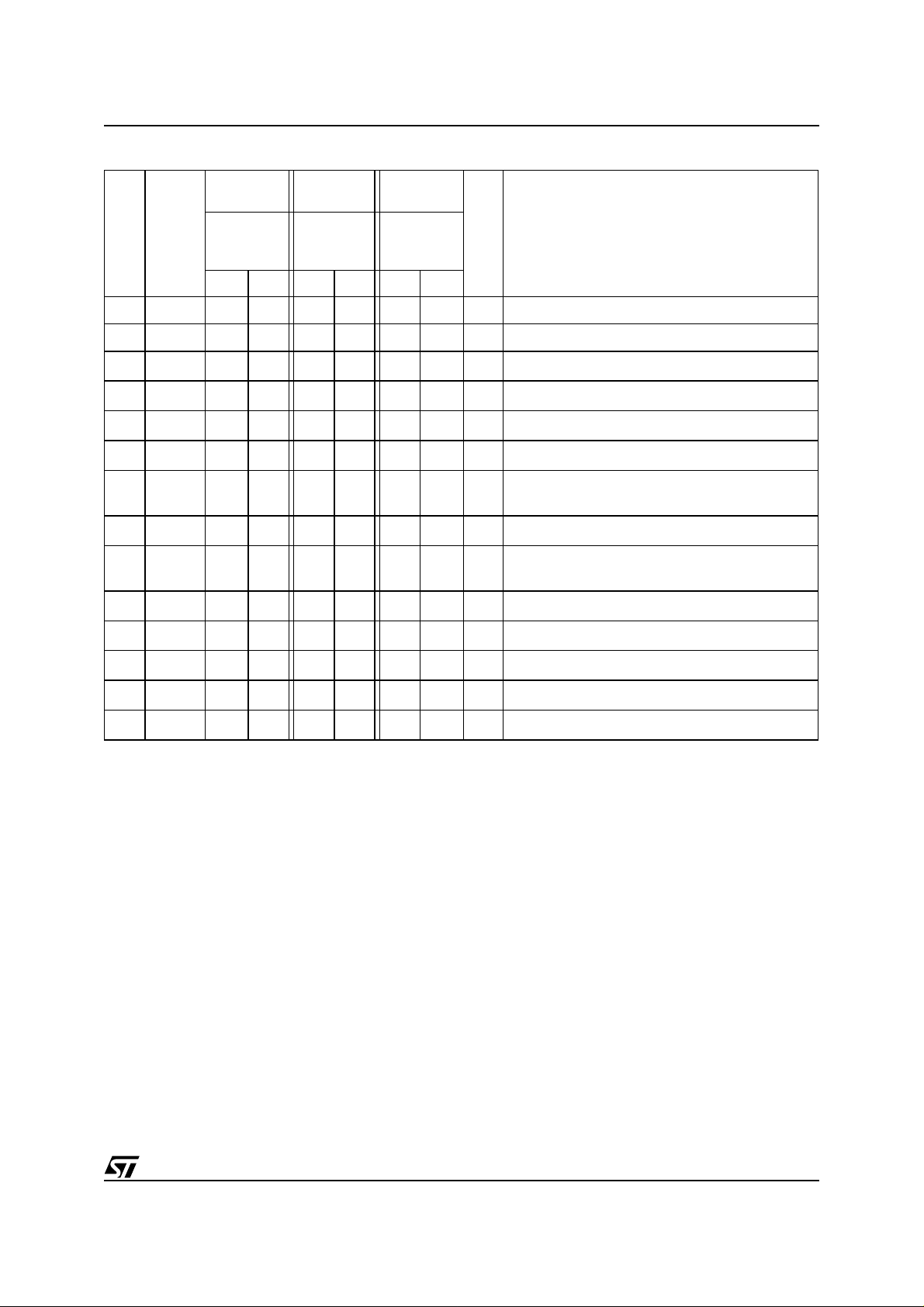

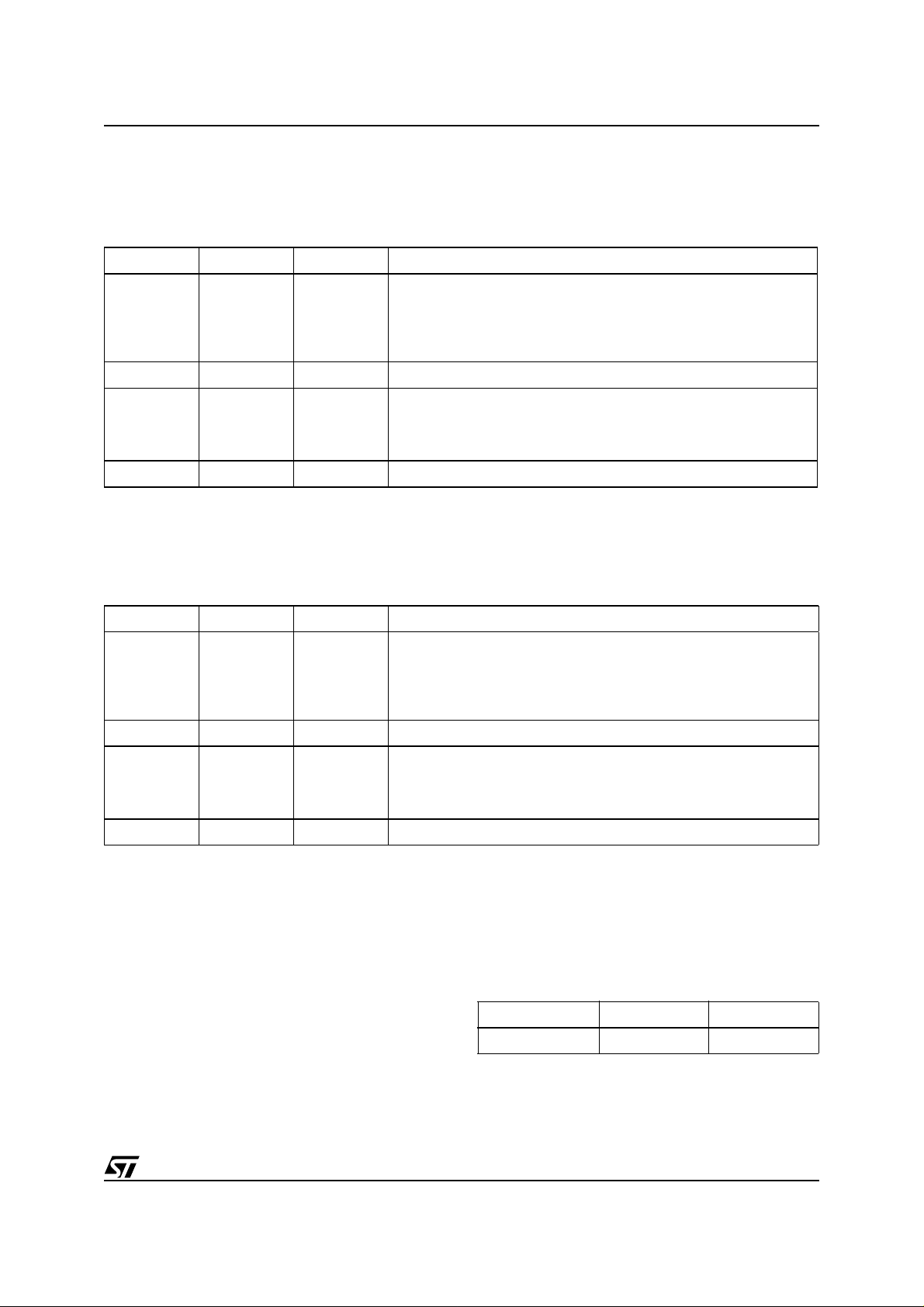

Table 8. AC Timing Parameters with CLK1X

Row Sym

f

1

CLOCK

t

2

CLOK

t

3

4

5

6

7

8

CKHI

t

CKLO

t

ISCH

t

IHCH

t

ICSCH

t

ICHCH

M7040N-

066

(V

DDQ

3.3V, 2.5V,

1.8V)

Min Max Min Max Min Max

20 66 20 83 20 100 MHz CLK1X frequency

6.75 5.4 4.5 ns

6.75 5.4 4.5 ns

2.5 1.8 1.5 ns

0.6 0.6 0.5 ns

4.2 3.5 3.0 ns

0.6 0.5 0.5 ns

M7040N-

M7040N-

083

=

(V

=

DDQ

3.3V, 2.5V,

1.8V)

(V

3.3V, 2.5V)

0.5 0.5 0.5 ms PLL lock time

100

DDQ

=

Unit

CLK1X high pulse

CLK1X low pulse

Description

(2)

(2)

Input Setup Time to CLK1X edge

Input Hold Time to CLK1X edge

(1)

(2)

(2)

Cascaded Input Setup Time to CLK1X rising

(2)

edge

Cascaded Input Hold Time to CLK1X rising

(2)

edge

t

9

CKHOV

t

10

CKHDV

t

11

CKHDZ

t

12

CKHSV

t

13

CKHSHZ

t

14

CKHSLZ

Note: 1. Valid for Ambient Operating Temperature: TA=0to70°C; VDD=1.5V.

2. Values are based on 50% signal levels and a 50/50% duty cycle of CLK1X.

3. Based on an AC load of CL = 30pF (see Figure 5, Figure 6, and Figure 7, page 13).

4. These parameters are sampled and not 100% tested, and are based on an AC load of 5pF.

8.5 7.0 6.5 ns

9.0 7.5 7.0 ns

8.5 7.0 6.5 ns

9.0 7.5 7.0 ns

6.5 6.0 5.5 ns

7.0 6.5 6.0 ns

Rising edge of CLK1X to LHO, FULO, BHO, FULL

(3)

valid

Rising edge of CLK1X to DQ valid

Rising edge of CLK1X to DQ high-Z

Rising edge of CLK1X to SRAM bus valid

Rising edge of CLK1X to SRAM bus high-Z

Rising edge of CLK1X to SRAM bus low-Z

(3)

(4)

(3)

(4)

(4)

18/159

OPERATION

Command Bus and DQ Bus

CMD[10:0] c arries the command and its associated parameter. DQ[71:0] is used for data transfer t o

and from the database entries. These entries comprise a data and a mask field that are organized as

data and mask arrays. The DQ Bus carries the

search data (of the data and mask arrays and internal registers) during the SEARCH command as

well as the address and data during READ and/or

WRITE operations. The DQ Bus can also carry the

address information for the flow-through a ccesses

to the external SRAMs and/or SS R AMs.

Database Entry (Data Array and Mask Array)

Eachdatabas e entry comprises a data and a mask

field. The resultant value of the entry is “1,”“0,” or

“X(don’t care),” depending on the value in the data

and mask bits. The on-chip priority encoder selects the first matching entry in the database that

is nearest to location “0.”

Arbitration Logic

When multiple Search Engines are cascaded to

create large databases, the databeing searched is

presented to all Search Engines simultaneously in

the cascaded system. If multiple matches occur

within t he cascaded devices, arbitration logic on

the Search Engines will enable the winning device

(witha matching entrythat is closest to address “0”

of the cascaded database) t o drive th e SRAM bu s.

Pipeline and SRAM Control

Pipeline latency is added to give enough time to a

cascaded system’s arbitration logic to determine

the device that will drive the index of the mat ching

entry on the SRAM bus. Pipeline logic adds latency to both the SRAM access cycles and the SSF

and SSV signals to align them to the host ASIC receiving the associated data.

Full Logic

Bit[0] in each of the 72-bit entries has a special

purpose for the LEARN command (0 = empty, 1 =

full). When all the data entries have bit[0] = 1, the

database asserts the FULL Fl ag, indicating all the

Search Engines in the depth-cascaded array are

full.

Connection Des cri ptions

CLOCK MODE (CLK_MODE). This signal allows

the selection of clock input to the CLK1X/CLK2X

pin. If the CLK_MODE pin is low, CLK2X must be

supplied on that pin. PHS_L must also be sup-

M7040N

plied. If the C LK _MODE pin is high, CLK1X must

be supplied on the CLK2X/CLK1X pin, and the

PHS_L signal is not required. When the

CLK_MODE is hi gh, PHS_L is unused and should

be externally grounded.

Master Clock (CLK2X/CLK1X). Depending on

the C LK_MODE pin, either the CLK2X or the

CLK1X must be supplied. M7040N samples c ontrol and data signals on both the edges of CLK1X

if CLK1X is supplied. M7040N samples all the dat a

and control pins on the positive edge of CLK2X if

the CLK2X and P H S_L signals are supplied. All

signals are driven out of the device on the rising

edge of CLK1X if CLK1X is supplied, and are driven on the rising edge of CLK2X (when PHS_L is

low) if CLK2X is supplied.

Phase (PHS_L). This signal runs at half the frequency of CLK2X and generates an internal clock

from CLK2X (see Figure 10, page 21).

Test Output (TEST_CO). This is test output and

will stay unconnected in the application of the device.

Test Input (TEST). This signal should be c onnected to ground.

Test Input (TEST_FM). This signal s hould be

connected to ground.

Reset (RST_L). Driving RST_L low initializes the

device to a known state.

Test Input (TEST_PB). This signal should be

connected to ground.

Configuration. When CFG_L is low, M7040N will

operate in backward compatibility mode with

M7010 and M7020. When CFG_L is low, the

CMD[10:9] should be externally grounded. With

CFG_L low, t he device will b ehav e identically with

M7010 and M7020, and the new feature added to

M7040N will be disabled.

When CFG_L is high, the additional command

CMD[10:9] c an be used and the following additional features will be supported:

1. 16 pairs of Global Mas ks are supported instead

of eight;

2. Parallel WRITE to the data and mask arrays is

supported (se e Parallel WRITE, page 38); and

3. conf iguring tables of up to three different widths

does not require table identification bits in the

data array, thus sav ing two bits from each 72-bit

19/159

M7040N

Command Bus (CMD[10:0]. [1:0] specifies the

command; [10:2] contains the command parameters. The descriptions of individual commands explains the details of the parameters. The encoding

of commands based on the [1:0] field are:

– 00: PIO READ

– 01: PIO WRITE

– 10 : SEARCH

– 11: LEARN

Command Valid (

CMDV). Qualifies the CMD bus

as follows:

– 0: No Co mmand

– 1: Command

Address/Data Bus (

DQ[71:0]). Carries the Read

and WRITE address as well as the data during

register, data, and mask array operations. It carries the comp are data during s earc h operations. It

also carries the SRAM address during SRAM PIO

accesses.

READ Acknowledge (ACK). Indicates that valid

data is available on the DQ Bus during register,

data, and mask array READ operations, or t he

data is available on t he SRAM data bu s during

SRAM READ operations.

Note: ACK Signals require a weak external pulldown resistor such as 47 or 100 KΩ.

End of Transfer (EOT). Indicates the end of

burst t ra ns fer during READ or WRITE burst operations.

Note: EOT Signals require a weak external pulldown resistor such as 47 KΩ or 100 KΩ.

SEARCH Succ essful Flag (SSF). When ass erted, t his signal indicates that the devi ce is the global winner in a SEARCH operation.

SEARCH Succ essful Flag Valid (SSV). W hen

asserted, this signal qualifies the SSF signal.

Multiple Hit Flag (MULTI_HIT). When asserted,

this signal indicates that there is more t han one location having a match on this device.

High Speed (HIGH_SPEED). When this signal is

high, the device willrun up to100MHzand perform

100 million searches per second. However, in this

mode, a T LSZ value of '00' is not supported in a

system of a single device. Furthermore, the device

will only support a TLSZ of '00' and '01' if more

than one device is cascaded to form database tables.

Clock Tune [3:0] (CLK_TUNE[3:0]). These test

pins should be set to logic level 1001.

SRAM Address (SADR[23:0]). This bus con-

tains address lines to access off-chip SRAMs that

contain ass ociative data. See Table 52, page 128

for the details of the generated SRAM address. In

a database of multiple M7040Ns, each corresponding bit of SADR from all cascaded devices

must be connected.

SRAM Chip Enable (CE_L). This is Chip Enable

control for external S R AMs. I n a database of multiple M7040Ns, CE_L of all cascaded devices

must be connected. This s ignal is then driven by

only one of the devices.

SRAMWriteEnable(WE_L). This is Write Enable co ntrol for external SRAMs. In a database of

multiple M7040Ns, WE_L of all cascaded dev ices

must be connected together. This signal is then

driven by only one of the devices.

SRAM Output Enable (OE_L). This is Output

Enable control for external SRAMs. Only the last

device drives this signal (with the LRA M bit set).

Address Latch Enable (ALE_L). When this signal is low, the addresses are valid on the SRAM

Address Bus. In a database of multiple M7040Ns,

the ALE_L of all cascaded dev ices must be connected. Th is signal is then driven by only one of

the devices.

Local Hit In (LHI[6:0]). These pins depth-cascade the device t o form a larger t able size. One

signal of th is bus is connected to the LHO[1] or

LHO[0] of each of the upstream devices in a bloc k.

Connect all unused LHI pins to a logic '0.' (For

more information, see DEPTH-CASCADING,

page 124.)

Local Hit Out (LHO[1:0]). LHO[1] and LHO[0]

are the same logical signal. LHO[1] or LHO[0] is

connected to one input of the LHI bus of up to four

downstream devices (in a block that contains up to

eight devices). (For more information, see

DEPTH-CASCADING, page 124.)

Block Hit In (BHI[2:0]). Input s from t he previous

BHO[2:0] are tied to the BHI[2:0] of the c urrent device (see DEPTH-CASCADING, page 124). In a

four-block system, the last block can contain only

seven devices because the ID code 11111 is used

for broadcast access.

Block Hit Out (BHO[2:0]). These outputs from

the last device in a block are connected to the

BHI[2:0] inputs of the devices in the downstream

blocks (see DE PTH-CA SC ADING, page 124).

20/159

M7040N

Full In (FUL I[6:0]). Each signal in this bus is con-

nected to FULO[0] or FULO[ 1] of an ups tream device to generate the FULL s ignal f or the depthcascaded block. For more information, see

DEPTH-CASCADING, page 124 to Generate Full

for a Block Section.

Full Out (FULO[1:0]). FULO[1] and FULO[0] are

the same logical signal. One of these two signals

must be connected t o the FULI of up to four downstream devices in a depth-cascaded table. Bit [0]

in the data array indicates if the entry is f ull (1) or

empty (0).This sign al is asserted if all of the bits in

the data array are '1s.' Refer to Depth-Cascading

to Generate a “FULL” S ignal, page 124.

Full Flag (FULL). When asserted, this signal indicates that the table consisting of many depthcascaded devices is full.

Device Identification (ID[4:0]). The binary-en-

coded device I D for a depth-cascaded system

starts at 00000 and goes up to 11110. 11111 is re-

CLOCKS

If the CLK_MO D E pin is low, M7040N receives the

CLK2X and PHS_L signals. It uses the PHS_L signal to divide CLK2X and generate an internal clock

(CLK), as shown in Figure 10. The M7040N uses

CLK2X and CLK for internal operations. If the

CLK_MODE pin is high, the M7040N recei ves the

CLK1X only. the M7040N uses an internal PLL to

double the frequency of CLK1X and then divides

served for a special broadcast address that selects all casc aded search engines in the system.

On a broadcast read-only, the device with the

LDEV bit set to '1' responds.

Chip Core Supply (V

Chip I/O Supply (V

). This is equal to 1.5V.

DD

). This is equal to either

DDQ

2.5 or 3.3V.

Test Data In (TDI). This is the Test Access Port’s

Test Data In.

Test Clock (TCK). This is the Test Access Port’s

Test Clock.

Test Data Out (TDO). This is the Test Access

Port’s Test Dat a Out.

Test Mode Select (TMS). This is the Test Access Port’s Test Mode Select.

Test Reset (TRST_L). This is the Test Access

Port’s Test Res et.

thatclock by two to generate a CLK for internal operations, as shown in Figure 11.

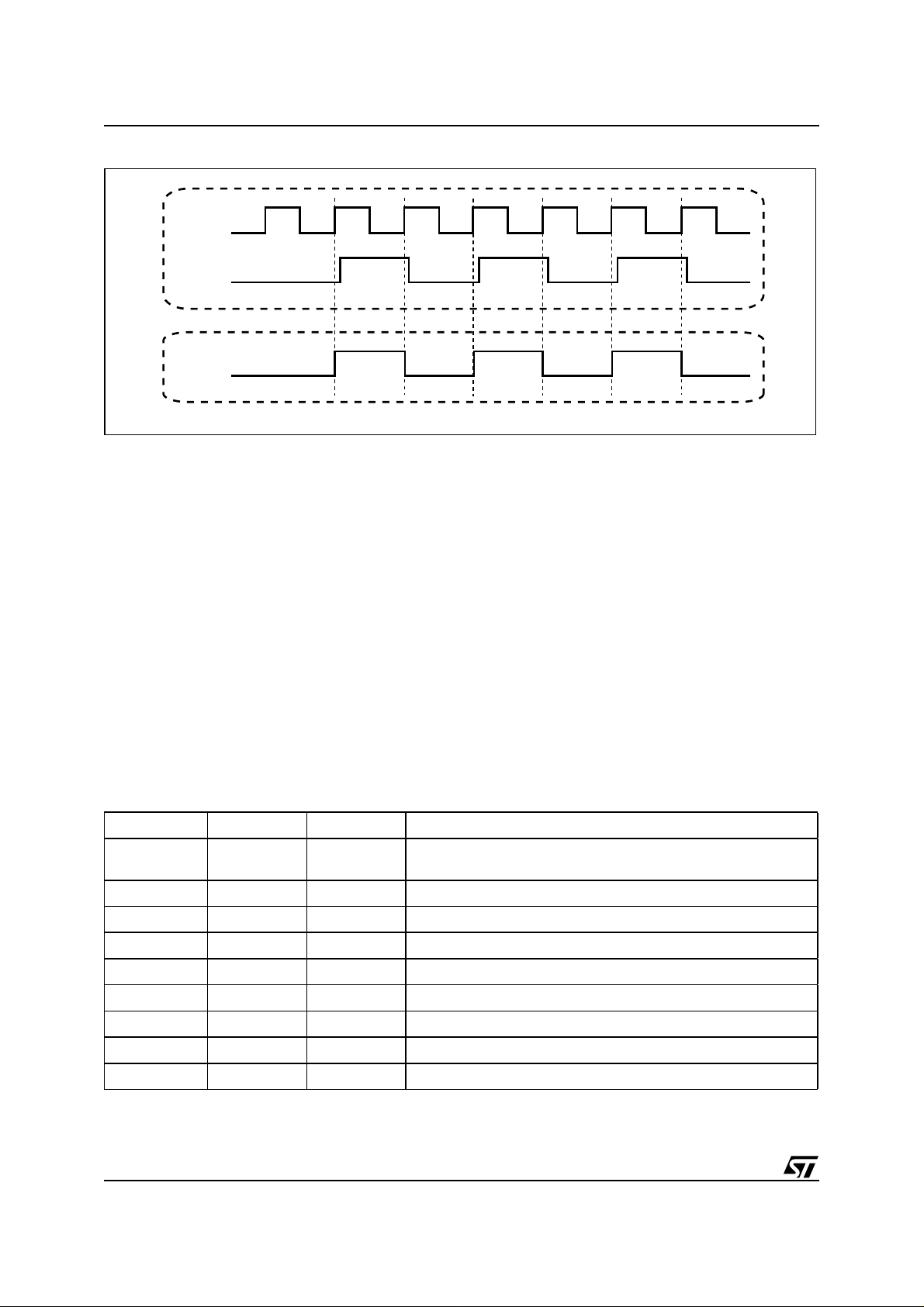

Note: For the purpose of showing timing diagrams, all such diagram s in this document will be

shown in CLK2X mode. For a timing diagram in

CLK1X mode, the following substitution can be

made (see Figure 12).

Figure 10. Clocks (CLK2X and PHS_L)

CLK2X

PHS_L

(1)

CLK

Note: Any reference to “CLK Cycles” means 1 cycle of the signal, “CLK.”

1. “CLK” is an internal signal.

Figure 11. Clocks (CLK1X)

CLK1X

(1)

CLK

1. “CLK” is an internal signal.

AI04750

AI04665

21/159

M7040N

Figure 12. Clocks for All Timing Diagrams

CLK2X

PHS_L

(Use for CLK1X MODE)

CLK1X

(Use for CLK1X MODE)

PLL USAGE

When the device first powers up, it takes 0.5 ms to

lock the internal phase-lock loop (PLL). During this

locking of the PLL, in addition to 32 extra CLK1X

cycles in CLK1X mode and 64 extra cycles in

CLK2X mode, the RST_L mu st be held low f or

proper initialization of the device. Setu p and hold

requirements will change in CLK1X mode if the

AI04666

duty cycle of the CLK1X is varied. All signals into

the device in CLK1X mode are sampled by a clock

that is generated by multiplying CLK1X by two.

Since PLL has a locking range, the de vice wi ll only

work between the range of frequencies spec ified

in the timing specification section.

REGISTERS

All r egisters in t he M7040N are 72 bits wide. The

M7040N contains 16 pairs of comparand storage

registers, 16 pairs of gl obal mas k registers

(GMRs), eight search successful index registers

and one each of command, information, burst

READ, burst WRITE, and next-free address registers. Table 9 provides an overview of all the

M7040N registers. The registers are ordered in ascending addres s order. Each register group is then

described in the following subsections.

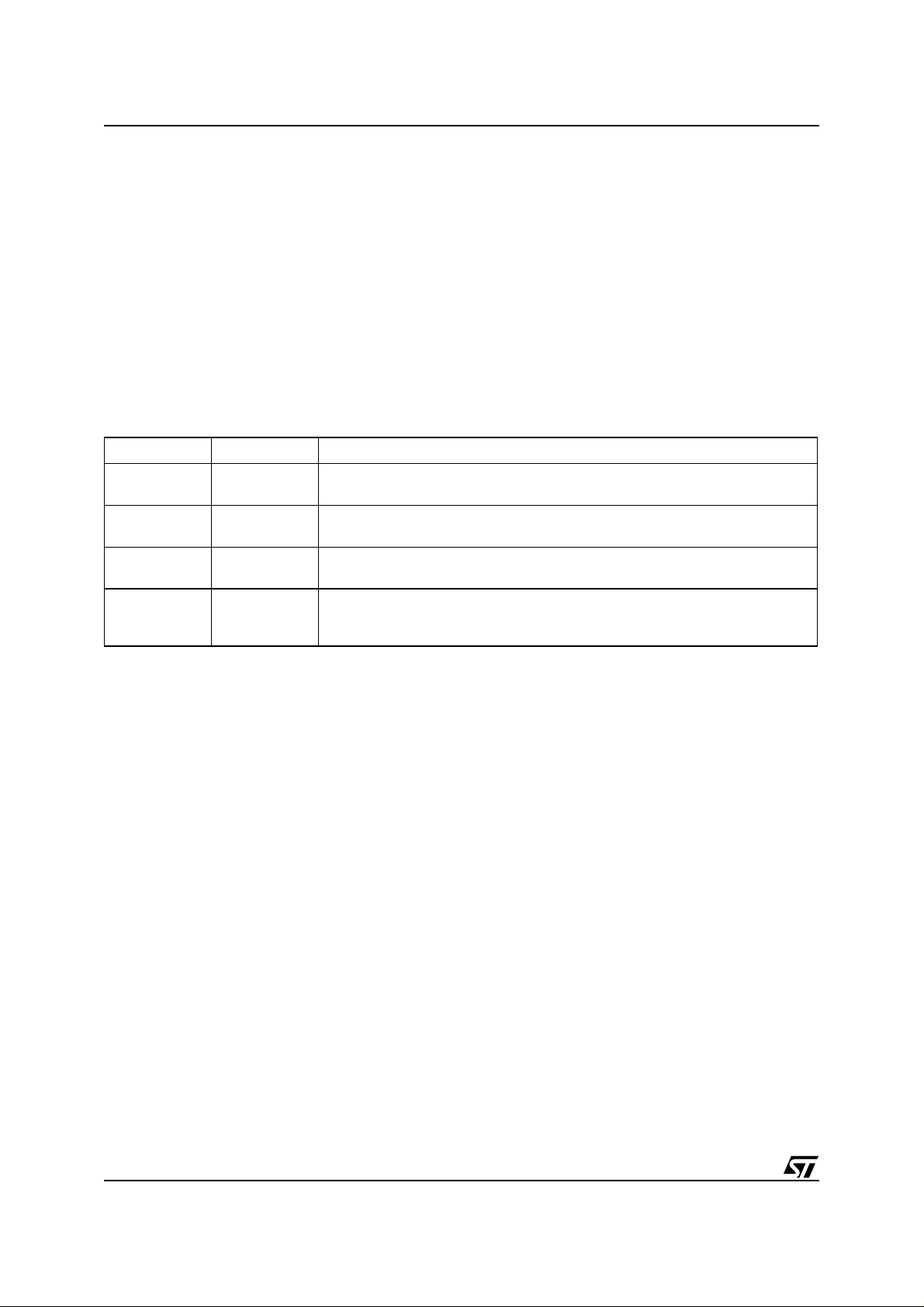

Table 9. Register Overview

Address Abbreviation Type Name

0–31 COMP0–31 R

32–47, 96–111 MASKS RW 16 Global Mask Registers Pairs.

48–55 SSR0–7 R 8 SEARCH Successful Index Registers.

56 COMMAND RW Command Register.

57 INFO R Information Register.

58 RBURREG RW Burst Read Register.

59 WBURREG RW Burst Write Register.

60 NFA R Next Free Address Register.

61–63 ––Reserved

32 Comparand Registers. Stores comparands from the DQ Bus for

learning later.

22/159

M7040N

Comparand Registers

The device contains 32 72-bit comparand registers (16 pairs) dynamically selected in every

SEARCH operation to store the comparand presented on t he DQ Bus. The LEARN command will

later use these registers when executed. The

M7040N stores the SEARCH command’sCycleA

comparand in the even-numbered regi ster and t he

Cycle B comparand in the odd-numbered register,

as shown in Figure 13.

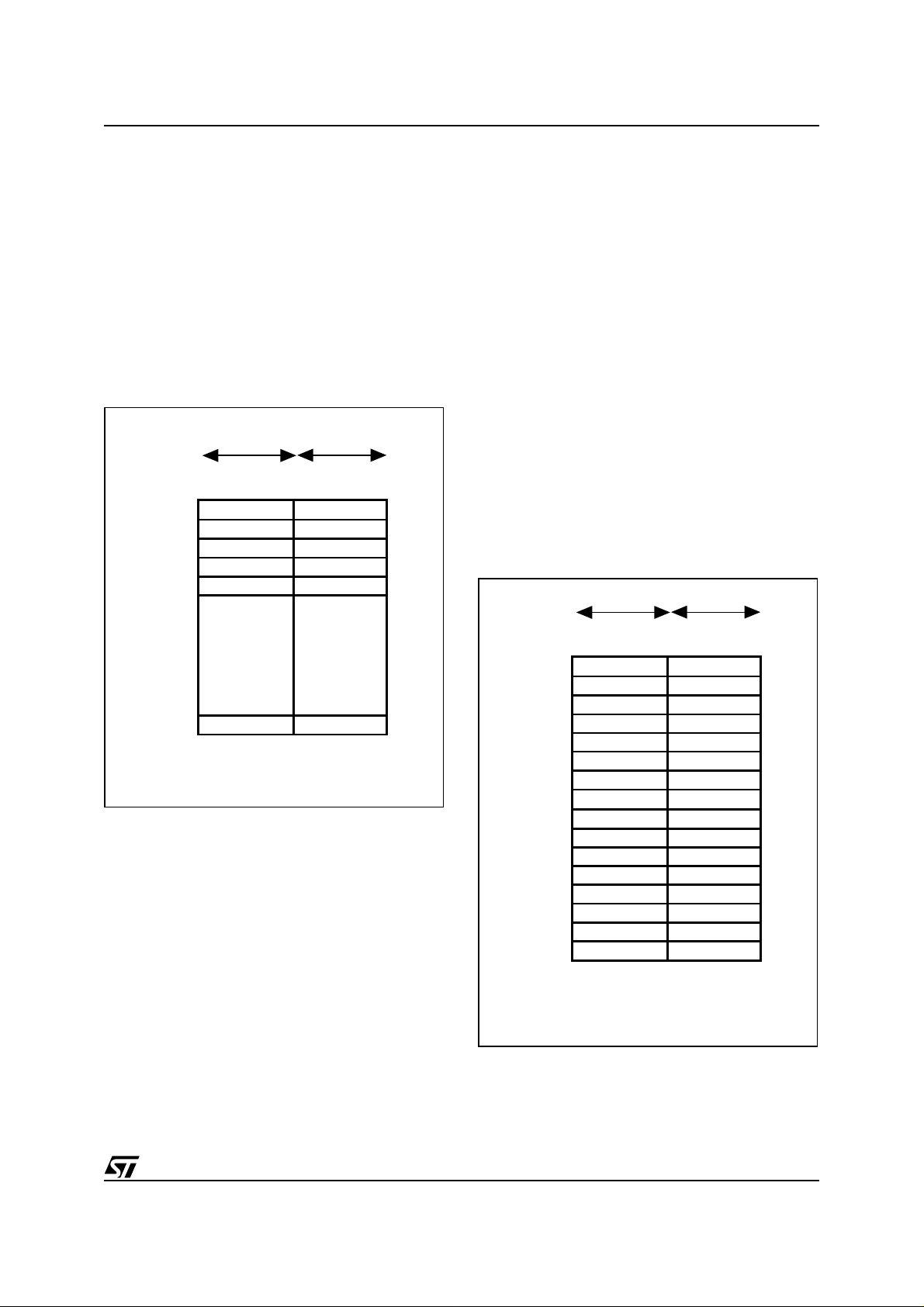

Figure 13. Comparand Register Selection

During SEARCH and LEARN

Instructions

7272

Address

Index

143 0

0

1

0

6

1

32

54

7

Mask Registers

The device cont ains 32 72-bit global mask registers (16 pairs) dynamically selected in every

SEARCH operation to s elect the search subfield.

The addressing of these registers is explained in

Figure 14. The four-bit GMR Index supplied on t he

command (CMD) bus can apply 16 pairs of global

masks during the SEARCH and WRITE operations, as shown below.

Note: In 72-bit SEARCH and WRITE opera tions,

the host ASI C must program both the even and

odd mask registers with the same values.

Each mask bit in the GMRs is used during

SEARCH and WRITE operations. I n SEARCH operations, setting the mask bi t to '1' enables compares; setting the mask bit to '0' dis ables

compares (forced match ) at the corresp onding bit

position. In WRITE operations to the data or mask

array, sett ing the mask bit to '1' enables WRITEs;

setting the m as k bit to '0' disables WRITEs at the

corresponding bit position.

Figure 14. Addressing the Global Masks

RegisterArray

7272

Address

Index

143 0

15

30 31

AI04667

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

SEARCH and WRITE Command

0

6

8

10

12

14

16

18

20

22

24

26

28

30

Global Mask Selection

11

13

15

17

1

32

54

7

9

19

21

23

25

27

29

31

AI04668

23/159

M7040N

SEARCH-Successful Registers (SSR[0:7])

The device contains eight search successful registers (SSRs) to hold the index of the location

where a successful search occurre d. The format of

each register is described in Table 10. T he

SEARCH command specifies which SSR stores

the index of a spec ific SEARCH command in Cycle B of the SEARCH Instruction. Subsequently,

the host ASIC can u se this register to access that

Table 10. SEARCH-Successful Register (SSR) Description

Field Range Initial Value Description

Index. This is the address of the 72-bit entry where a successful

search occurs. The device updates this field only when a search is

INDEX [15:0] X

– [30:16] 0 Reserved.

VALID [31] 0

– [71:32] 0 Reserved.

successful. If a hit occurs in a 144-bit entry-size quadrant, the LSB is

'0.' If a hit occurs in a 288-bit entry size quadrant, the two LSBs are

'00.' This index updates if the device is either a local or global winner

in a SEARCH operation.

Valid. During SEARCH operation in a depth-cascaded configuration,

the device that is a global winner in a match sets this bit to '1.' This bit

updates only when the device is a global winner in a SEARCH

operation.

data array, mask array, or ex ternal SRAM using

the index as part of the indirect access address

(see Table 20, page 34 and Table 23 , page 37)

The device with a valid bit set performs a REA D or

WRITE operation. All oth er dev ices suppress the

operation.

.

24/159

The Command Register

Table 11. Command Register Field Descriptions

Field Range

SRST [0] 0

DEVE [1] 0

TLSZ [3:2] 01

HLAT [6:4] 000

LDEV [7] 0

Initial

Value

Software Reset. If '1,' this bit resets the device, with the same effect as the hardware

reset. Internally, it generates a reset pulse lasting for eight CLK cycles. This bit

automatically resets to a '0' the reset cycle has completed.

Device Enable. If '0,' it keeps the SRAM Bus (SADR, WE_L, CE_L, OE_L, and

ALE_L), SSF, and SSV signals in 3-state condition and forces the cascade interface

output signals LHO[1:0] and BHO[2:0] to '0.' It also keeps the DQ Bus in input mode.

The purpose of this bit is to make sure that there are no bus contentions when the

devices power up in the system.

Table Size. The host ASIC must program this field to configure the chips into a table

of a certain size. This field affects the pipeline latency of the SEARCH and LEARN

operations as well as the READ and WRITE accesses to the SRAM (SADR[23:0],

CE_L, OE_L, WE_L, ALE_L, SSV, SSF, and ACK). Once programmed, the search

latency stays constant.

Latency # CLK Cycles

with HIGH_SPEED low

00: 1 device 4

01: 2-8 devices 5

10: 9-31 devices 6

11: Reserved

Latency # CLK Cycles

with HIGH_SPEED high

00: Not supported

01: 1 devices 5

10: 2-31 devices 6

11: Reserved

Latency of Hit Signals. This field adds latency to the SSF and SSV signals during

SEARCH, and ACK signal during SRAM READ access by the following number of

CLK cycles.

000: 0 100: 4

001: 1 101: 5

010: 2 110: 6

011: 3 111: 7

Last device in the cascade. When set, this is the last device in the depth-cascaded

table and is the default driver for the SSF and SSV signals.

In the event of a search failure, the device with this bit set drives the hit signals as

follows:

SSF = 0, SSV = 1

During non-search cycles, the device with this bit set drives the signals as follows:

SSF = 0, SSV = 0

M7040N

Description

25/159

M7040N

Field Range

LRAM [8] 0

CFG [24:9]

[71:25] 0 Reserved.

Initial

Value

0000

0000

0000

0000

Description

Last device on this SRAM Bus. When set, this device is the last device on this

SRAM bus in the depth-cascaded table and is the default driver for the SADR, CE_L,

WE_L, and ALE_L signals. In cycles where no M7040N device in a depth-cascaded

table drives these signals, this device drives the signals as follows:

SADR = FFFFFF,

CE_L = 1

WE_L = 1

ALE_L = 1

OE_L is always driven by the device for which this bit is set.

Database Configuration. The device is internally divided into eight quadrants of 8K x

72, each of which can be configured as 8K x 72, 4K x 144, or 2K x 288 as follows:

00: 8K x 72

01: 4K x 144

10: 2K x 288

11: low power, partition not used for SEARCH

Bits [10:9] apply to configuring the 1st quadrant in the address space.

Bits [12:11] apply to configuring the 2nd quadrant in the address space.

Bits [14:13] apply to configuring the 3rd quadrant in the address space.

Bits [16:15] apply to configuring the 4th quadrant in the address space.

Bits [18:17] apply to configuring the 5th quadrant in the address space.

Bits [20:19] apply to configuring the 6th quadrant in the address space.

Bits [22:21] apply to configuring the 7th quadrant in the address space.

Bits [24:23] apply to configuring the 8th quadrant in the address space.

The Information Register

Table 12. Information Register Field Descriptions

Field Range Initial Value Description

Revision [3:0] 0001

Implementation [6:4] 001 This is the M7040N implementation number.

Reserved [7] 0 Reserved.

Device ID [15:8] 00000100 This is the Device Identification Number.

MFID [31:16] 0000_0010_0000_1111

[71:32] Reserved.

Revision Number. This is the current device revision

number. Numbers start from one and increment by one

for each revision of the device.

Manufacturer ID. This field is the same as the

manufacturer ID and continuation bits in the TAP

controller.

26/159

The Read Burst Address Register (RBURREG)

These READ burst address register f ields m ust be

programmed before burst read.

Table 13. Read Burst Register Description

Field Range Initial Value Description

Address. This is the starting address of the data array or mask array

ADR [15:0] 0

[18:16] Reserved.

BLEN [27:19] 0

[71:28] Reserved.

during a burst READ operation. It automatically increments by 1 for

each successive read of the data array or mask array. Once the

operation is complete, the contents of this field must be reinitialized

for the next operation.

Length of Burst Access. The device is capable of writing from 4 up

to 511 locations in a single burst. The BLEN decrements

automatically. Once the operation is complete, the contents of this

field must be reinitialized for the next operation.

The Write Burst Address Register (WBURREG)

These WRITE burst address register fields must

be programmed before burs t write.

M7040N

Table 14. Write Burst Register Description

Field Range Initial Value Description

Address. This is the starting address of the data array or mask array

during a burst WRITE operation. It automatically increments by 1 for

ADR [15:0] 0

[18:16] Reserved.

BLEN [27:19] 0

[71:28] Reserved.

each successive write of the data array or mask array. Once the

operation is complete, the contents of this field must be reinitialized for

the next operation.

Length of Burst Access. The device is capable of writing from 4 up

to 511 locations in a single burst. The BLEN decrements

automatically. Once the operation is complete, the contents of this

field must be reinitialized for the next operation.

The NFA Register

Bit [ 0] ofeach 72-bit data entry is a special bit designated f or use in the operation of the LEA R N

command. In 72-bit quadrants, the bi t[0] indicates

whether a location is full (bit set to'1') or empt y (bit

set to '0'). Every WRITE/LEARN command loads

the address of first 72-bit location that contains a

'0' in the entry ’s bit[0]. This is stored in the NFA

register(see Table 15). If all the bits in a device are

set to '1,' the M7040N asserts FULO[1:0] to '1.'

In 144-bit-configured quadrants, the LSB of this

set bit '0' and bit 72 in a 144-bit word t o either '0' or

'1' to indicate full/empty status.

Note: Both bits (0 a nd 72) must be set to '0' or '1'

(e.g., '10' or '01' settings are invalid).

Table 15. NFA Regi ster

Address 71 - 16 15 - 0

60 Reserved Index

register is always set to '0.' The host ASIC must

27/159

M7040N

SEARCH ENGINE ARCHITECTURE

The M7040N consists of 64K x 72-bit storage c ells

referred to as d ata bits.There is a mask cell corresponding to each data cell. Figure 15 shows the

three organi zations of the device based on the value of the CFG bits in the command register.

During a SEARCH operation, the search data bit

(S), dat a array bit (D), mask array bit (M) and the

global mask bit (G) are used in the following manner to generate a match at that bit position (s ee

Table 16, page 29).

The entry with all matched bit positions results in a

successful search during a SEARCH operation.

In order for a successful search within a device to

make the device the local winner in the SEARCH

operation, all 72-bit positions must generate a

match for a 72-bit entry in 72-bit-configured quadrants, or all 144-bit positions must generate a

match for two consecutive ev en and odd 72-b it entries in quadrants configured a s 144 bits, or all

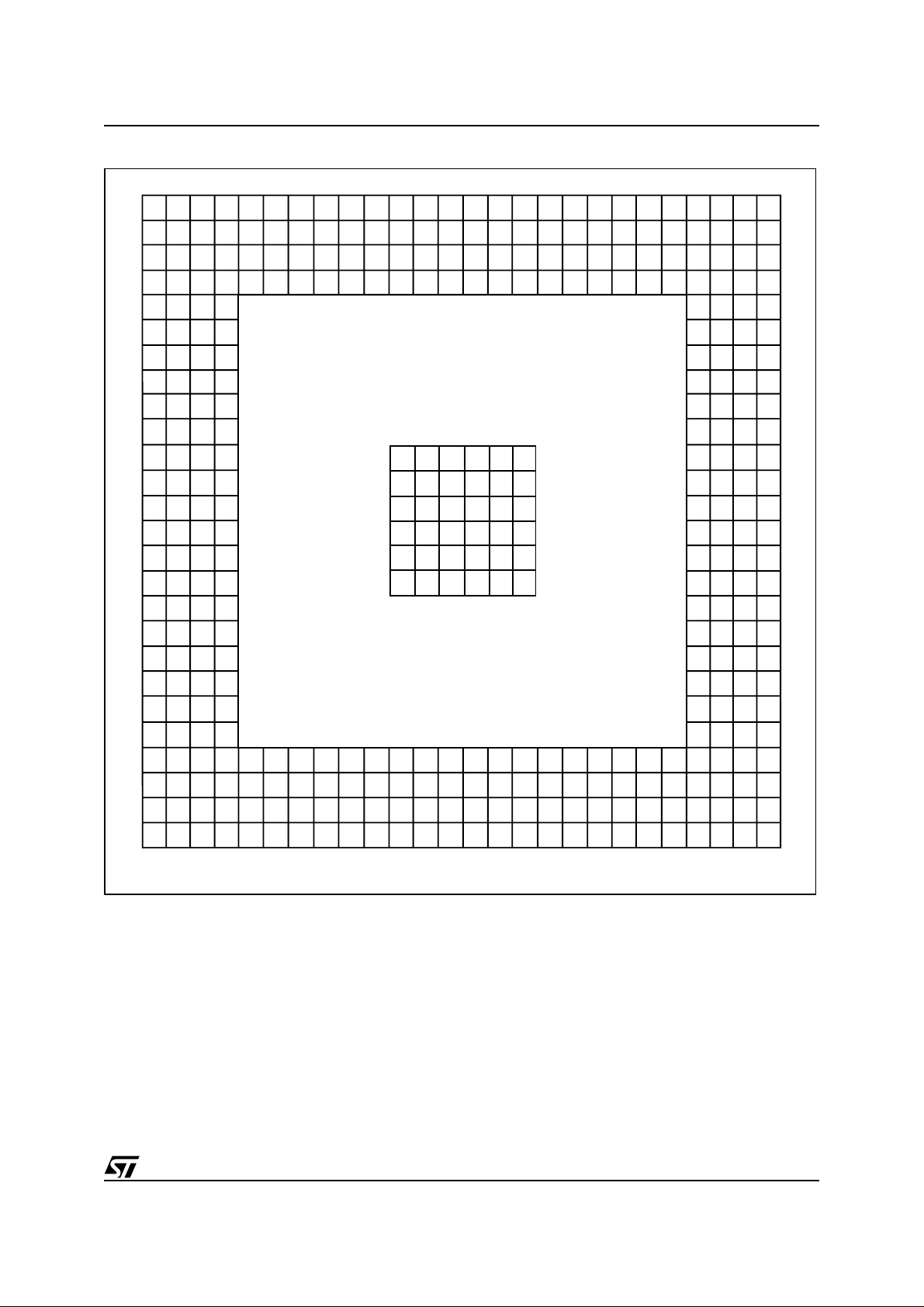

Figure 15. M7040N Database Width Configuration

288-bit positions must generate a m atch f or 4 consecutive entries aligned to 4 entry-pa ge boundaries of 72-bit entries in quadrants configured as

288 bits.

Anarbitration mechanism using a casc ade bus determines the global winning device among the local winning devices in a SEARCH cycle. The

global winning device drives t he SRAM Bus, SSV,

and the SS F signal s . In case of a SEARCH failure,

the devices with the LDEV and LRAM bits set

drive(s) the S RAM Bus, SSF, and SSV signals

The M7040N device can be configured to contain

tables of different widths, even within the same

chip. Figure 16, page 29 shows a sample configuration of different widths.

Data and Mask Addressing

Figure 17, page 29 shows the M7040N data array

and mask array addressing procedure.

72

64 K

CFG = 0000000000000000

Masks

Data

144

32 K

Masks

Data

CFG = 0101010101010101

288

16 K

CFG = 1010101010101010

Masks

Data

AI04669

28/159

M7040N

Table 16. Bit Position Match Figure 16. Multi-width Configu ration Example

G M S D Match

0XXX1

10XX1

11001

11010

11100

11111

8 K

8 K

8 K

8 K

72

72

72

72

Figure 17. M7040N Data and Mask Array Addressing

72 7272 72 7272

71 0

0

1

2

3

64 K

283 0

16K

65532 65533 65534 65535

CFG = 1010101010101010

(288- bit conf igurat ion)

4 K

4 K

2 K

144

144

288

2 K 288

CFG = 10 10 01 01 11 11 00 00

Inactive (low power)

143 0

3210

7654

32K

AI04670

72

10

32

54

76

65535

CFG = 0000000000000000

(72-bit Conf ig uration)

65534 65535

CFG = 0101010101010101

( 144-bit Configu ration)

AI04671

29/159

M7040N

COMMAND CODES AND PARAMETERS

A master device, such as an ASIC controller, issues c ommands to the M7040N using the Command Valid CMDV signal and the CMD Bus. The

following subsections describe the functions of the

commands.

Command Codes

The M70 40N implements four basic commands

shown in Table 17. The Com mand Code m us t be

presented to CMD[1:0] while keeping the command valid (CMDV) signal high for t wo CLK2X cycles. These two CLK2X cycles are designated as

“Cycle A” and “Cycle B” when the CLK_MODE pin

is low. In CLK2X mode, the controller ASIC must

Table 17. Command Codes

CMD Code Command Description

align the instructions with the PHS_L signal. The

command code must be presented to CMD[1:0]

while keeping the CMDV signal high for one

CLK1X cycle when the CLK_MODE pin is high. I n

CLK1X mode the high phase of the CLK1X is designated as Cycle A and the low phase of the

CLK1X is designated as C y cle B. The CMD[10:2]

field passes the parameters of the command in

Cycles A and B.

Commands and Command Parameters

Table 18, page 31 lists the CMD bus fields that

contain the M7040N command parameters as well

as their respective cycles.

00 READ

01 WRITE

10 SEARCH

11 LEARN

Reads one of the following: data array, mask array, device registers, or external

SRAM.

Writes one of the following: data array, mask array, device registers, or external

SRAM.

Searches the data array for a desired pattern using the specified register from the

global mask register array and local mask associated with each data cell.

The device has internal storage for up to 16 comparands that it can learn. The

device controller can insert these entries at the next free address (as specified by

the NFA register) using the LEARN Instruction.

30/159

Loading...

Loading...