8 Mbit (512K x16) 1.8V Asynchronous SRAM

FEATURES SUMMARY

■ SUPPLY VOLTAGE: 1.65 to 1.95V

■ 512K x 16 bits SRAM with OUTPUT ENABLE

■ EQUAL CYCLE and ACCESS TIMES: 70ns

■ SINGLE BYTE READ/W R ITE

■ LOW STANDBY CURRENT

■ LOW V

■ TRI-STATE COMMON I/O

■ AUTOMATIC POWER DOWN

■ DUAL CHIP ENABLE for EASY DEPTH

EXPANSION

DATA RETENTION: 1.0V

CC

M68AR512D

Figure 1. Packages

BGA

TFBGA48 (ZB)

6 x 7mm

BGA

TFBGA48 (ZB)

8 x 10mm

1/19October 2002

M68AR512D

TABLE OF CONTENTS

SUMMARY DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Figure 2. Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Table 1. Signal Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Figure 3. TFBGA Connections (Top view through package). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

Figure 4. Block Diagr am . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

MAXIMUM RATING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Table 2. Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

DC and AC PARAMETERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Table 3. Operating and AC Measurement Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 5. AC Measurement I/O Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 6. AC Measurement Load Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

Table 4. Capacitance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Table 5. DC Character i stics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

OPERATION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 6. Operating Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Read Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Figure 7. Address Controlled, Read Mode AC Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Figure 8. Chip Enable or Output Enable Controlled, Read Mode AC Waveforms . . . . . . . . . . . . . . 9

Figure 9. Chip Enable or UB/LB Controlled, Standby Mode AC Waveforms . . . . . . . . . . . . . . . . . . 9

Table 7. Read and Standby Mode AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Write Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 10. Write En a ble Controlled, Write AC Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 11. Chip Enable Controlled, Write AC Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Figure 12. UB/LB Controlled, Writ e AC Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 8. Write Mode AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 13. E1 Controlled, Low V

Figure 14. E2 Controlled, Low V

Data R e t e n tion A C Wavefo r ms . . . . . . . . . . . . . . . . . . . . . . . . 1 4

CC

Data R e t e n tion A C Wavefo r ms . . . . . . . . . . . . . . . . . . . . . . . . 1 4

CC

Table 9. Low VCC Data Retention Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

PACKAGE MECHANICAL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

TFBGA48 6x7mm - 6x8 ball array, 0.75 mm pitch, Bottom View Package Outline. . . . . . . . . . . . . 15

TFBGA48 6x7mm - 6x8 ball array, 0.75 mm pitch, Package Mechanical Data. . . . . . . . . . . . . . . . 15

TFBGA48 8x10mm - 6x8 ball array, 0.75 mm pitch, Bottom View Package Outline. . . . . . . . . . . . 16

TFBGA48 8x10mm - 6x8 ball array, 0.75 mm pitch, Package Mechanic al Data . . . . . . . . . . . . . . . 16

PART NUMBERING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 12. Ordering Information Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

REVISION HISTORY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 13. Document Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

2/19

SUMMARY DESCRIPTION

The M68AR512D is an 8 Mbit (8,388,608 bit)

CMOS SRAM, organized as 524,288 words by 16

bits. The device features fully static operation requiring no external clocks or timing strobes, with

equal address access and cycle times. It requires

a single 1.8V (

±150mV) supply. This device has a

Chip Select pin (E2) for easy memory ex pansion;

matic power-down feature, reducing the power

consumption by over 99%.

The M68AR512D is available in TFBGA48

(6x7mm and 8x10mm, 6x8 active ball array, 0.75

mm ball pitch) package. See the Ordering Information Scheme (Table 12) for details.

when it is active (E2 high) the device has an auto-

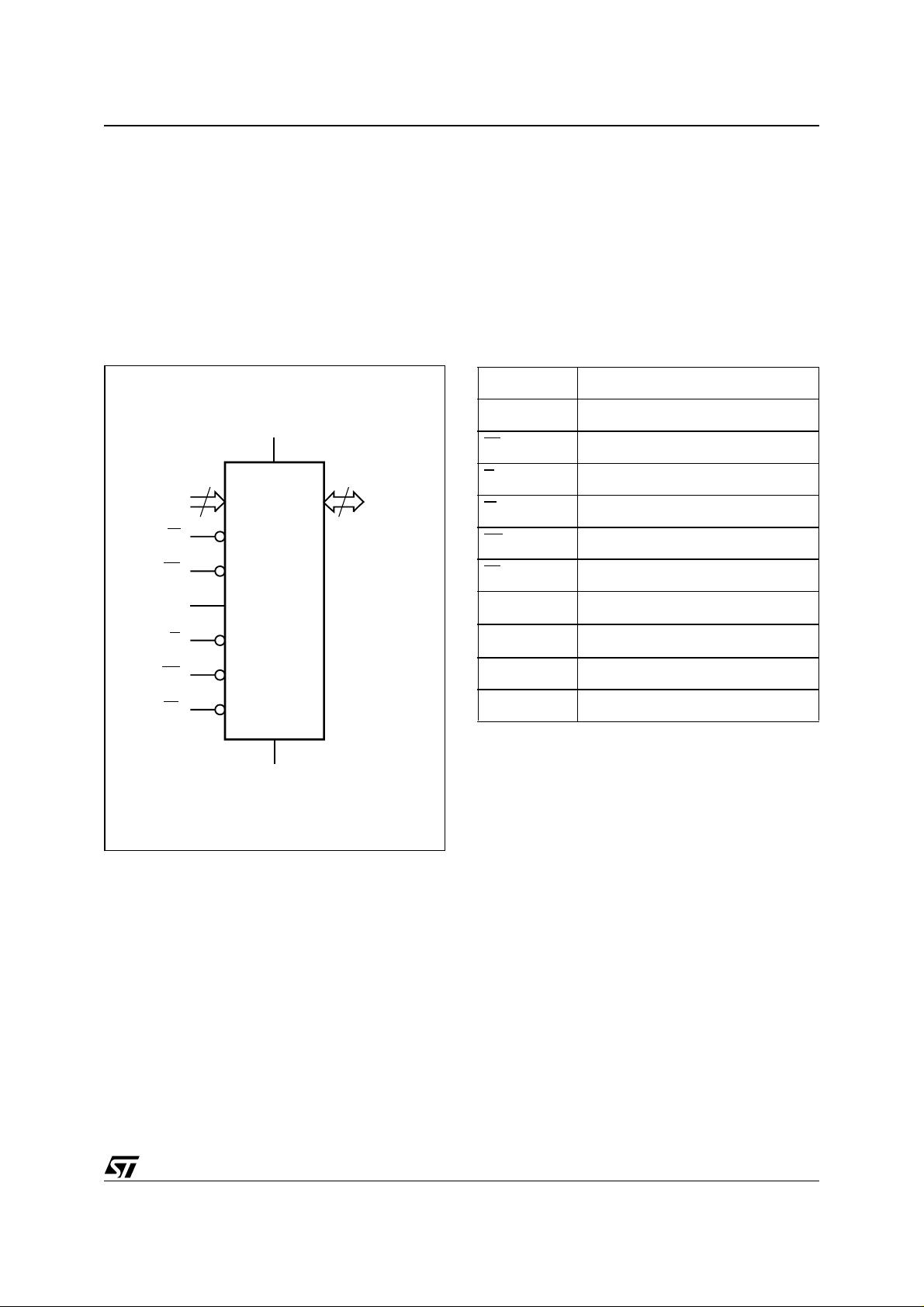

Figure 2. Logic Diagram Table 1. Signal Names

A0-A18 Address Inputs

M68AR512D

A0-A18

W

E1

E2

UB

LB

V

CC

19

M68AR512D

G

V

SS

16

DQ0-DQ15

AI03953C

DQ0-DQ15 Data Input/Output

, E2 Chip Enable

E1

G

W

UB

LB

V

CC

V

SS

NC Not Connected

DU Don’t Use as Internally Connected

Output Enable

Write Enable

Upper Byte Enable Input

Lower Byte Enable Input

Supply Voltage

Ground

3/19

M68AR512D

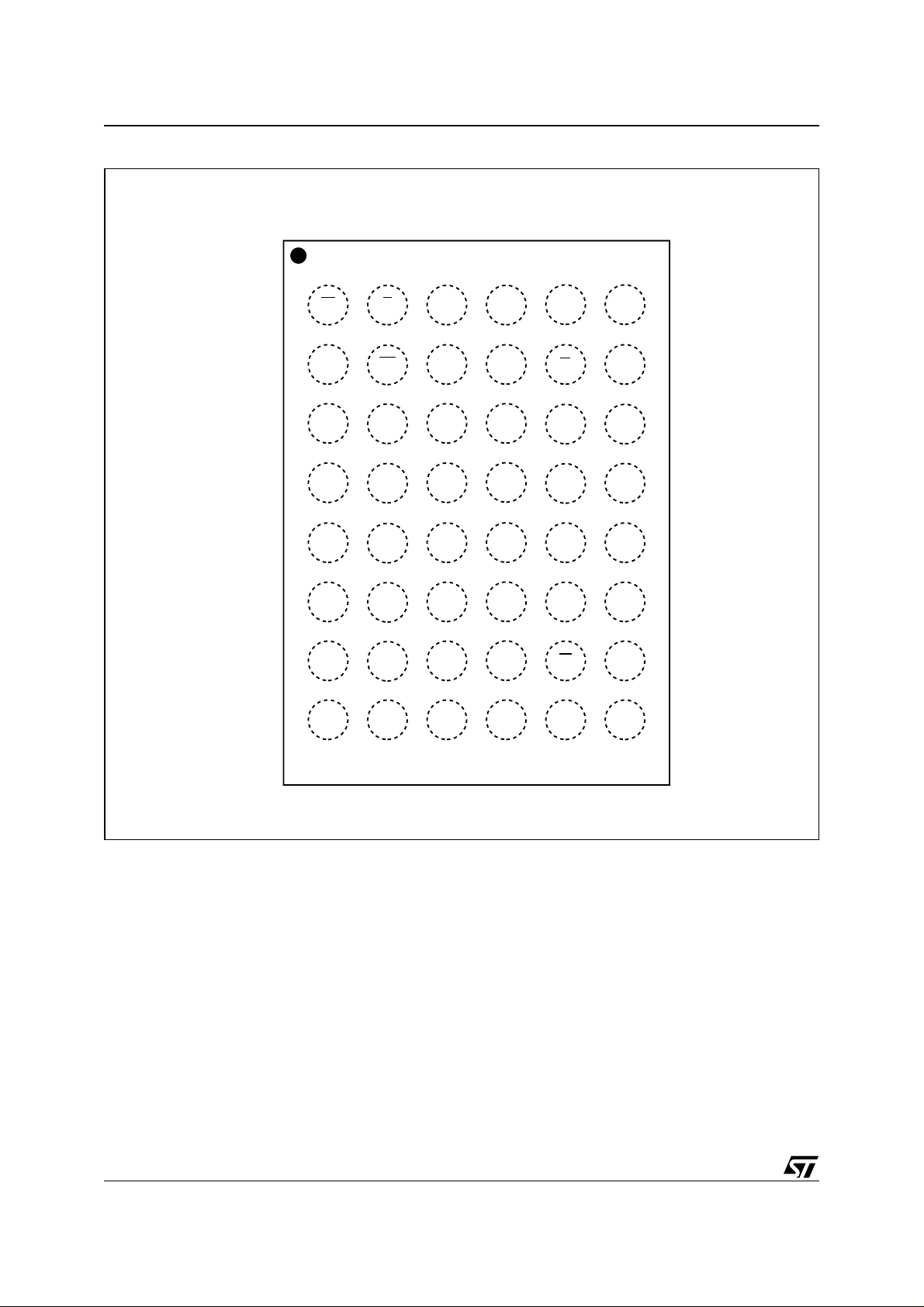

Figure 3. TFBGA Connections (Top view through package)

654321

A

B

C

D

E

F

G

H

DQ8

DQ9

V

SS

V

CC

DQ14

DQ15

UB

DQ10

DQ11

DQ12

DQ13

NC

A0GLB

A17

V

A9

SS

A1

A4 E1

A6A5

A7

A16

A15

A13

A10

A2 E2

DQ3

DQ4

DQ5A14

DQ0A3

DQ2DQ1

V

CC

V

SS

DQ6

DQ7WA12

DUA11A8A18

4/19

AI03960

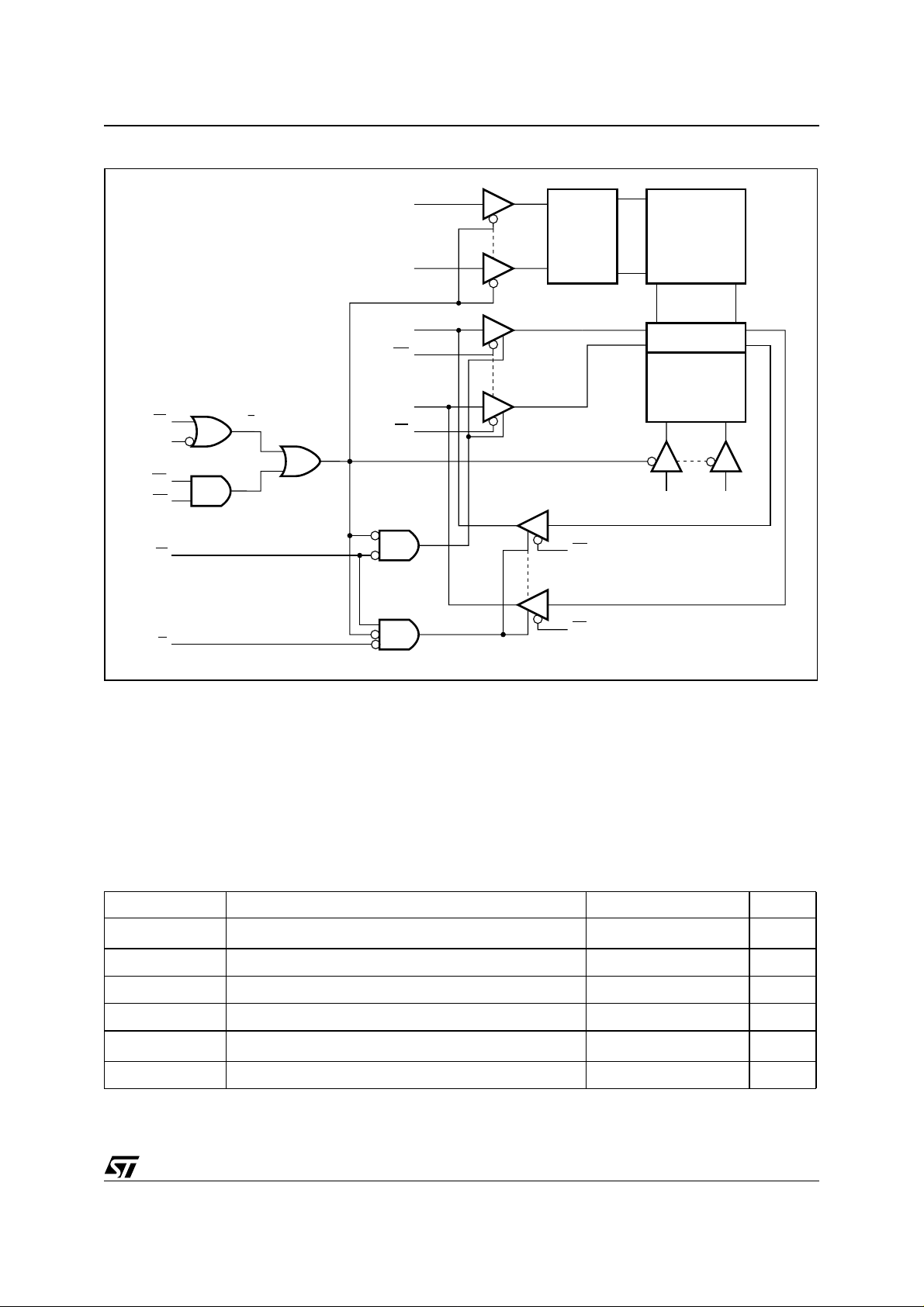

Figure 4. Block Diagram

A18

A8

ROW

DECODER

M68AR512D

MEMORY

ARRAY

DQ15

UB

E1

E2

UB

LB

Ex

W

G

DQ0

LBLB

MAXIMUM RATIN G

Stressing the device above the rating l isted in t he

Absolute Maximum Ratings" table may cause permanent damage to the device. These are stress

ratings only and operation of the device at t hese or

any other conditions ab ove those i ndicated in t he

Operating sections of this specificat ion is not im-

(8)

(8)

(8)

UB

(8)

LB

I/O CIRCUITS

COLUMN

DECODER

A0 A7

AI05452

plied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device

reliability. Refer also to the STMicroelectronics

SURE Program and other relevant quality documents.

Table 2. Absolute Maximum Ratings

Symbol Parameter Value Unit

(1)

I

O

T

A

T

STG

V

CC

(2)

V

IO

P

D

Note: 1. One output at a time, not to exceed 1 second durati on.

2. Up to a maximum operating V

Output Current 20 mA

Ambient Operating Temperature –55 to 125 °C

Storage Temperature –65 to 150 °C

Supply Voltage –0.5 to 2.5 V

Input or Output Voltage

–0.5 to V

CC

+0.5

Power Dissipation 1 W

of 1.95 V only.

CC

V

5/19

M68AR512D

DC AND AC PARAMETERS

This section summarizes the operat ing and measurement conditions, as well as the DC and AC

characteristics of the device. The parameters in

the following DC and AC Characteristic tables are

derived from tests performed under the M easure-

Table 3. Operating and AC Measurement Conditions

Parameter M68AR5 12D

Supply Voltage

V

CC

Ambient Operating Temperature

ment Conditions listed i n the relevant tables. Designers should check that the operating conditions

in their projects match the measurement conditions when using the quoted parameters.

1.65 to 1.95V

Range 1 0 to 70°C

Range 6 –40 to 85°C

Load Capacitance (C

Output Circuit Protection Resis tance (R

Load Resistance (R

)

L

)

1

)

2

30pF

15.3kΩ

11.3kΩ

Input Rise and Fall Times 1ns/V

Input Pulse Voltages

Input and Output Timing Ref. Voltages

Output Transition Timing Ref. Voltages

V

RL

0 to V

CC

V

/2

CC

= 0.3VCC; VRH = 0.7V

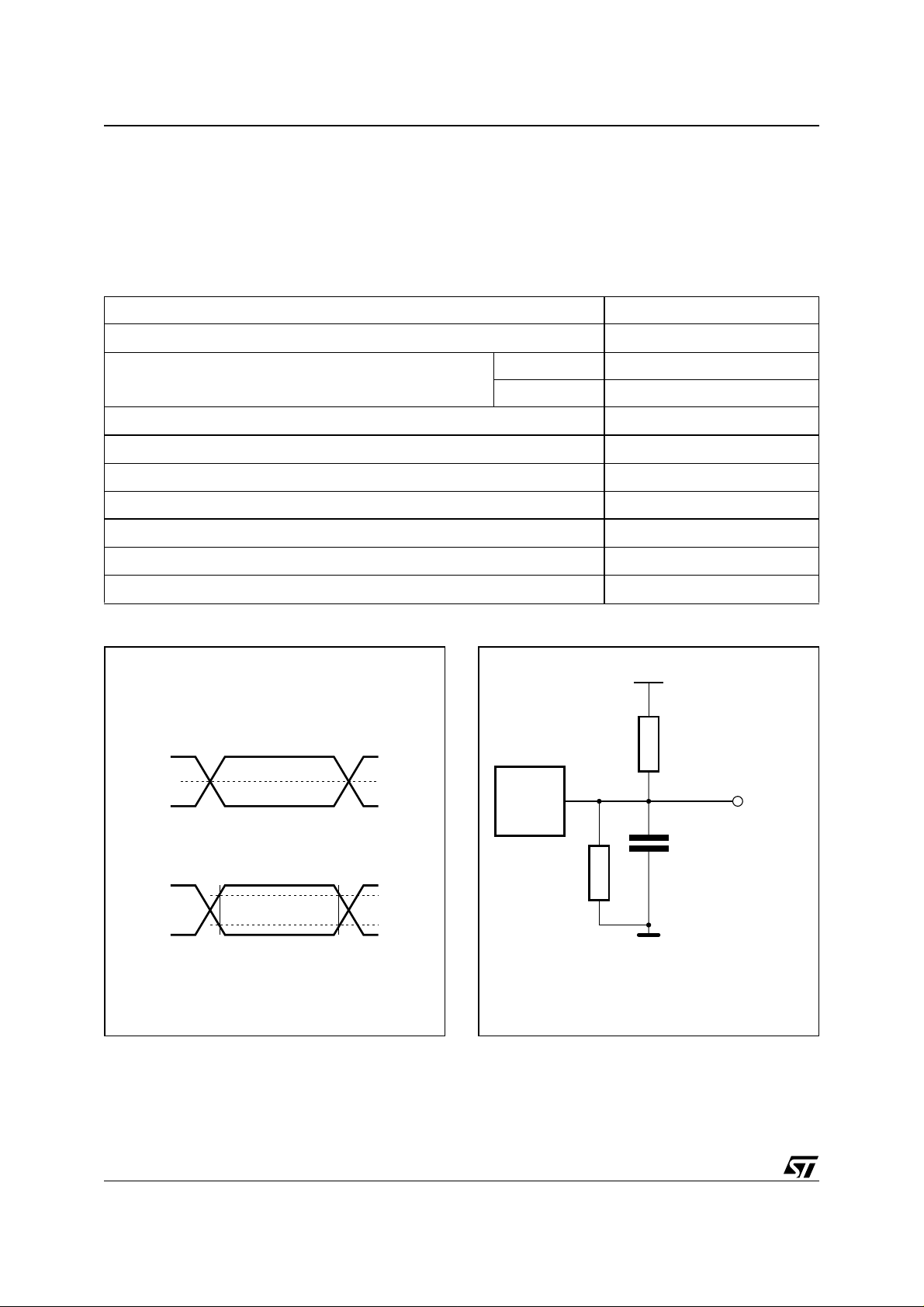

Figure 5. AC Measurement I/O Waveform Figure 6. AC Measurement Load Circuit

V

CC

I/O Timing Reference Voltage

V

CC

0V

Output Timing Reference Voltage

V

CC

0V

VCC/2

0.7V

0.3V

AI04831

DEVICE

UNDER

TEST

R

CC

CC

CL includes probe and 1TTL capacitance

R

1

OUT

C

L

2

CC

6/19

AI03853

Loading...

Loading...