128 Mbit (8Mb x16 or 4Mb x32, Uniform Block, Burst)

FEATURES SUMMARY

■ WIDE DATA BUS for HIGH BANDWIDTH

– M58LW128A: x16

– M58LW128B: x16/x32

■ SUPPLY VOLTAGE

–V

–V

■ SYNCHRONOUS/ASYNCHRONOUS READ

– Synchronous Burst read

– Pipelined Synchronous Burst Read

– Asynchronous Random Read

– Asynchronous Address Latch Controlled

– Page Read

■ ACCESS TIME

– Synchronous Burst Read up to 66MHz

– Asynchronous Page Mode Read 150/25ns

– Random Read 150ns

■ PROGRAMMING TIME

– 16 Word or 8 Double-Word Write Buffer

–12µs Word effective programming time

■ 128 UNIFORM 64 KWord MEMORY BLOCKS

■ BLOCK PROTECTION/ UNPROTECTION

■ PROGRAM and ERASE SUSPEND

■ OTP SECURITY AREA

■ COMMON FLASH INTERFACE

■ 100,000 PROGRAM/ERASE CYCLES per

BLOCK

■ ELECTRONIC SIGNATURE

– Manufacturer Code: 0020h

– Device Code M58LW128A: 881 8h

– Device Code M58LW128B: 8819h

= 2.7 to 3.6V core supply voltage for Pro-

DD

gram, Erase and Read operations

= 1.8 to VDD for I/O B u ffers

DDQ

Read

M58LW128A

M58LW128B

3V Supply Flash Memories

PRELIMINARY DATA

Figure 1. Packages

TSOP56 (N)

14 x 20mm

TBGA

TBGA64 (ZA)

10 x 13mm

TBGA

TBGA80 (ZA)

10 x 13mm

February 2003

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

1/65

M58LW128A, M58LW128B

TABLE OF CONTENTS

SUMMARY DESCRIPTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 2. Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Table 1. Signal Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Figure 3. TSOP56 Connections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

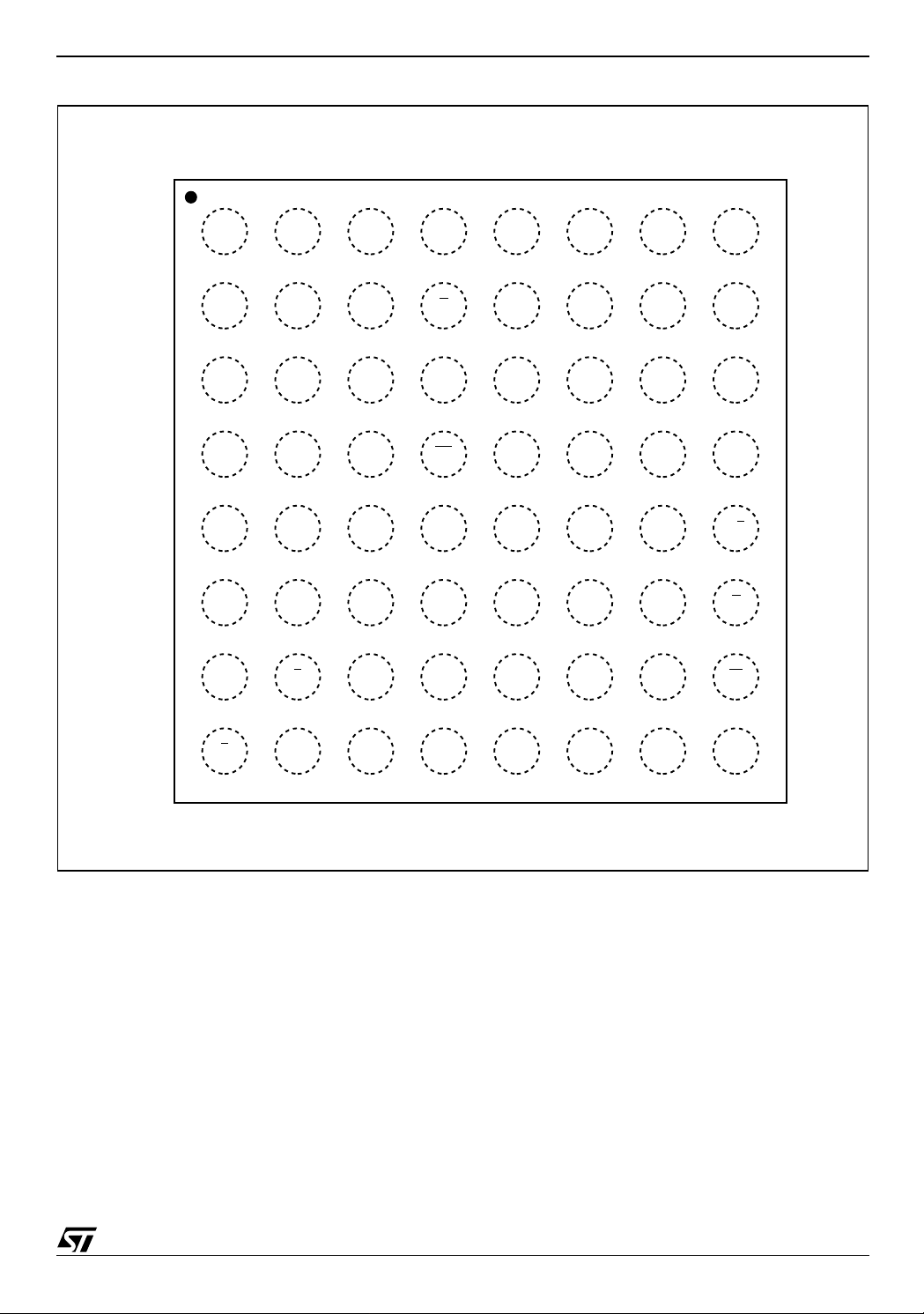

Figure 4. TBGA64 Connections for M58LW1 28A (Top view through package) . . . . . . . . . . . . . . . 9

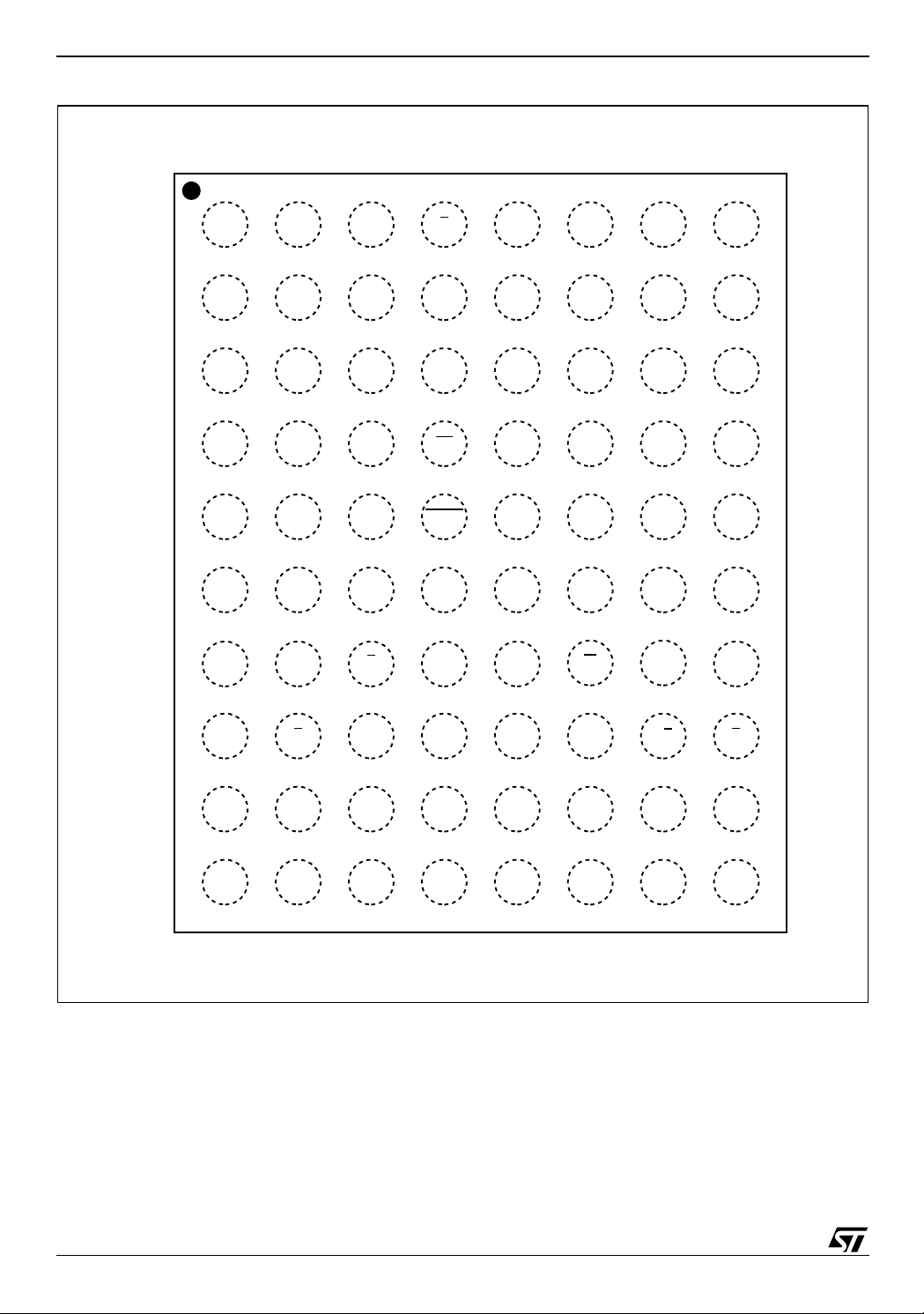

Figure 5. TBGA80 Connections for M58LW1 28B (Top view through package) . . . . . . . . . . . . . . 10

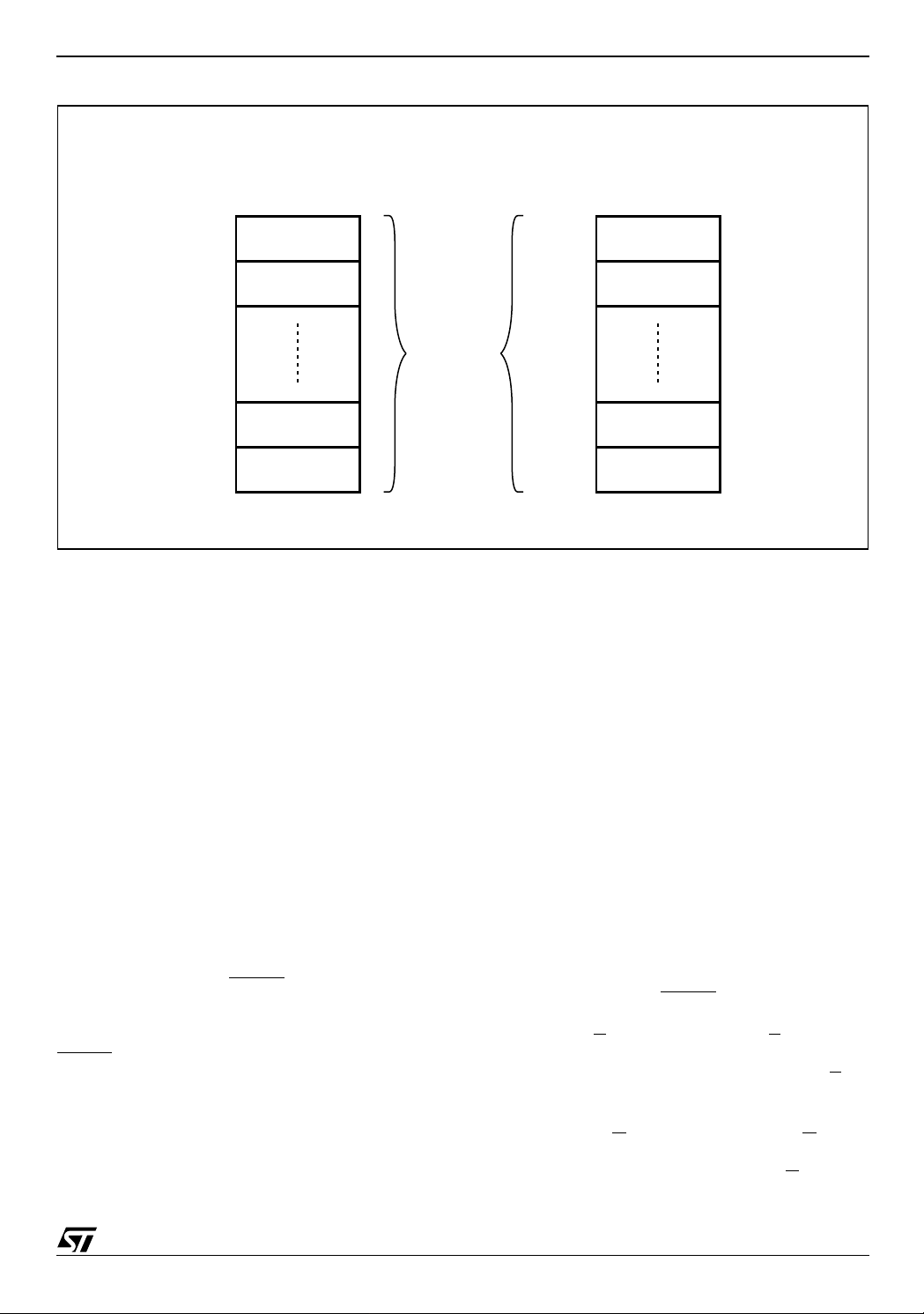

Figure 6. Block Addresses. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

SIGNAL DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Address Inputs (A1-A23). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Data Inputs/Outputs (DQ0-DQ31 ). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Chip Enable (E). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 1

Output Enable (G). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Write Enable (W). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Reset/Power-Down (RP). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Latch Enable (L). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Clock (K).. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Burst Address Advance (B). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Valid Data Ready (R). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Word Organization (WORD).. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Ready/Busy (RB). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Program/Erase Enable (V

V

Supply Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

DD

Input/Output Supply Voltage (V

Ground (V

Ground (V

). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

SS

). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

SSQ

). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

PP

). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

DDQ

BUS OPERATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Asynchronous Bus Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Asynchronous Bus Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Asynchronous Latch Controlled Bus Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Asynchronous Page Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Asynchronous Bus Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 4

Asynchronous Latch Controlled Bus Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Output Disable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Standby . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Power-Down.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 2. Asynchronous Bus Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Synchronous Bus Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

Synchronous Burst Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Synchronous Pipelined Burst Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

Synchronous Burst Read Suspend . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 3. Synchronous Burst Read Bus Operations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2/65

M58LW128A, M58LW128B

Table 4. Address Latch Cycle for Optimum Pipelined Synchronous Burst Read . . . . . . . . . . . . . 17

Figure 7. Synchronous Burst Read Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 8. Example Synchronous Pipelined Burst Read Operation . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 9. Example Burst Address Advance and Burst Abort operations. . . . . . . . . . . . . . . . . . . . 19

Burst Configuration Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Read Select Bit (M15) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

X-Latency Bits (M14-M11). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Y-Latency Bit (M9). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Valid Data Ready Bit (M8). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Burst Type Bit (M7).. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Valid Clock Edge Bit (M6).. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Latch Enable Bit (M3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Burst Length Bit (M2-M0). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 5. Burst Configuration Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 6. Burst Type Definition (x16 Bus Width). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 7. Burst Type Definition (x32 Bus Width). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 8. Burst Performance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

COMMAND INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Read Memory Array Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

Read Electronic Signature Comma nd . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Read Query Command.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Read Status Register Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

Clear Status Register Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Block Erase Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Write to Buffer and Program Command.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Program/Erase Suspend Comm and . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Program/Erase Resume Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Set Burst Configuration Register Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Block Protect Command.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Blocks Unprotect Command.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Table 9. Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 10. Read Electronic Signature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 11. Program, Erase Times and Program Erase Endurance Cycles . . . . . . . . . . . . . . . . . . 28

STATUS REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Program/Erase Controller Status (Bit 7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

Erase Suspend Status (Bit 6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Erase Status (Bit 5). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Program Status (Bit 4). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

VPP Status (Bit 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Program Suspend Status (Bit 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Block Protection Status (Bit 1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Reserved (Bit 0). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 12. Status Register Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

3/65

M58LW128A, M58LW128B

MAXIMUM RATING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 13. Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

DC and AC PARAMETERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 3

Table 14. Operating and AC Measurement Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Figure 10. AC Measurement Input Output Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Figure 11. AC Measurement Load Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 15. Capacitance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 16. DC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Figure 12. Asynchronous Bus Read AC Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 17. Asynchronous Bus Read AC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 13. Asynchronous Latch Controlled Bus Read AC Waveforms . . . . . . . . . . . . . . . . . . . . . 36

Table 18. Asynchronous Latch Controlled Bus Read AC Characteristics. . . . . . . . . . . . . . . . . . . 36

Figure 14. Asynchronous Page Read AC Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 19. Asynchronous Page Read AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Figure 15. Asynchronous Write AC Waveform, Write Enable Controlled . . . . . . . . . . . . . . . . . . . 38

Figure 16. Asynchronous Latch Controlled Write AC Waveform, Write Enable Controlled. . . . . . 38

Table 20. Asynchronous Write and Latch Controlled Write AC Characteristics, Write Enable

Controlled.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 17. Asynchronous Write AC Waveforms, Chip Enable Controlled. . . . . . . . . . . . . . . . . . . 40

Figure 18. Asynchronous Latch Controlled Write AC Waveforms, Chip Enable Controlled . . . . . 40

Table 21. Asynchronous Write and Latch Controlled Write AC Characteristics, Chip Enable

Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figure 19. Synchronous Burst Read AC Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Figure 20. Synchronous Burst Read - Continuous - Valid Data Ready Output. . . . . . . . . . . . . . . 43

Table 22. Synchronous Burst Read AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Figure 21. Reset, Power-Down and Power-Up AC Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 23. Reset, Power-Down and Power-Up AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 45

PACKAGE MECHANICAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Figure 22. TSOP56 - 56 lead Plastic Thin Small Outline, 14 x 20 mm, Package Outline . . . . . . . 46

Table 24. TSOP56 - 56 lead Plastic Thin Small Outline, 14 x 20 mm, Package Mechanical Data 46

Figure 23. TBGA64 - 10x13mm - 8 x 8 ball array, 1mm pitch, Package Outline. . . . . . . . . . . . . . 47

Table 25. TBGA64 - 10x13mm - 8 x 8 ball array, 1 mm pitch, Package Mechanical Data . . . . . . 47

Figure 24. TBGA80 - 10x13mm - 8 x 10 ball array, 1mm pitch, Package Outline. . . . . . . . . . . . . 48

Table 26. TBGA80 - 10x13mm - 8 x 10 ball array, 1mm pitch, Package Mechanical Data. . . . . . 48

PART NUMBERING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 27. Ordering Information Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

APPENDIX A. BLOCK ADDRESS TABLE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 28. Block Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

APPENDIX B. COMMON FLASH INTERFACE - CFI. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 29. Query Structure Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

4/65

M58LW128A, M58LW128B

Table 30. CFI - Query Address and Data Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 31. CFI - Device Voltage and Timing Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 32. Device Geometry Definition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 33. Block Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 34. Extended Query information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

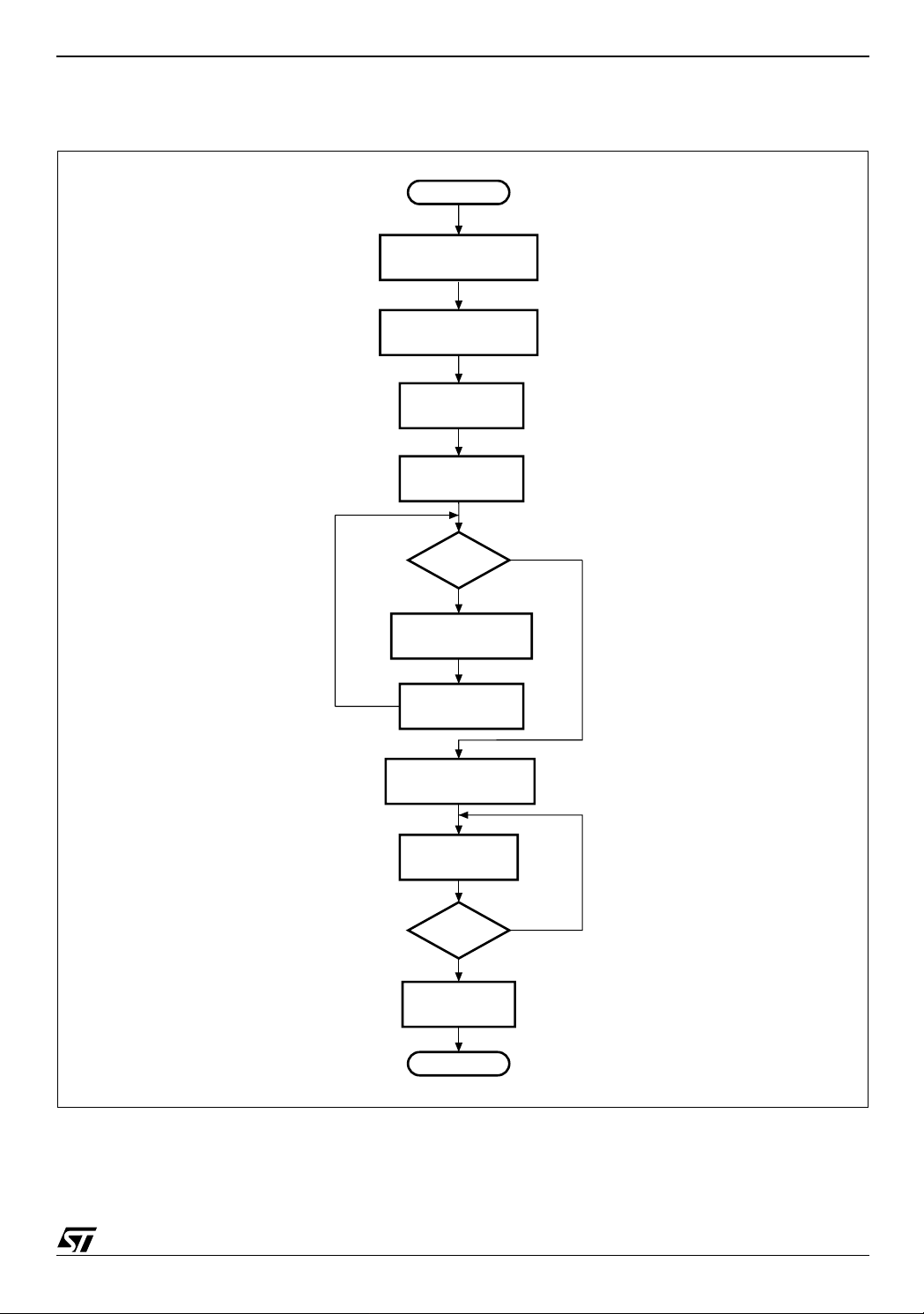

APPENDIX C. FLOW CHARTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Figure 25. Write to Buffer and Program Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . 57

Figure 26. Program Suspend & Resume Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . 58

Figure 27. Erase Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Figure 28. Erase Suspend & Resume Flowchart and Pseudo Code. . . . . . . . . . . . . . . . . . . . . . . 60

Figure 29. Command Interface and Program Erase Controller Flowchart (a). . . . . . . . . . . . . . . . 61

Figure 30. Command Interface and Program Erase Controller Flowchart (b). . . . . . . . . . . . . . . . 62

Figure 31. Command Interface and Program Erase Controller Flowchart (c) . . . . . . . . . . . . . . . . 63

REVISION HISTORY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 35. Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

5/65

M58LW128A, M58LW128B

SUMMARY DESCRIPTION

M58LW128 is a 1 28 Mbit (8Mb x16 or 4Mb x32)

non-volatile memory that can be read, erased and

reprogrammed. These operations can be performed using a single low voltage (2.7V to 3.6V)

core supply. On power-up the memo ry d efaults to

Read mode with an asynchronous bus where it

can be read in the same way as a non-burst Flash

memory.

The memory is divided into 128 blocks of 1Mbit

that can be erased ind ependently so it is possible

to preserve valid data while old data is erased.

Program and Erase command s are written to the

Command Interface of the memory. An on-chip

Program/Erase Controller simplifies the process of

programming or erasing the memory by taking

care of all of the special operations that are required to update the memory contents. The end of

a Program or Erase operation can be detected and

any error conditions identified in the Status Register. The command set required to control the

memory is consistent with JEDEC standards.

The Write Buffer allows the microprocessor to program up t o 16 W ords (or 8 Double Words) in parallel, both speeding up the programming and

freeing up the microprocessor to perform other

work. The minimum buffer size for a program operation is an 8 Word (or 4 Double Word) page. A

page can only be programmed once between

Erase operations.

Erase can be suspended in order to perform either

read or program in any ot her block and then resumed. Program can be suspended to read data in

any other block and then resumed. Each block can

be programmed and erased over 100,000 cycles.

Individual block protection against program or

erase is provided for data security. All blocks are

protected during power-up. Th e protection of the

blocks is non-volatile; after power-up the protec-

tion status of e ach block is restored to the state

when power was last removed. Software commands are provided to allow protection of some or

all of the blocks and to cancel all block protection

bits simultaneously. All program or erase operations are blocked when the Program Erase Enable

input Vpp is low.

The Reset/Power-Down pin is used to apply a

Hardware Reset to the memory and to set the device in Power-Down mode. It can also be used to

temporarily disable the protection mechanism.

In asynchronous mode Chip Enable, Output Enable and Write Enable signals control the bus operation of the memory. An Address Latch input can

be used to latch addresses in Latch Controlled

mode. Together they allow simple , yet powerful,

connection to most microprocessors, often without

additional logic.

In synchronous mode all Bus Read operations are

synchronous with the Clock. Chip Enable and Output Enable select the Bus Read operation; the address is Latched using the Latch Enable inputs

and the address is advanced using Burst Address

Advance. The signals are compatible with most

microprocessor burst interfaces.

A One Time Programmable (OTP) area is included

for security purposes. Either 512 Words (x16 Bus

Width) or 512 Double-Words (x32 Bus Width) is

available in the OTP area. The process of reading

from and writing to the OTP area is not published

for security purposes; contact STMicroelectronics

for details on how to use the OTP area.

The memory is offered in various packages . The

M58LW128A is available in TSOP56 (14 x 20 mm)

and TBGA64 (1mm pitch). The M58LW128B is

available in TBGA80 (1mm pitch).

6/65

M58LW128A, M58LW128B

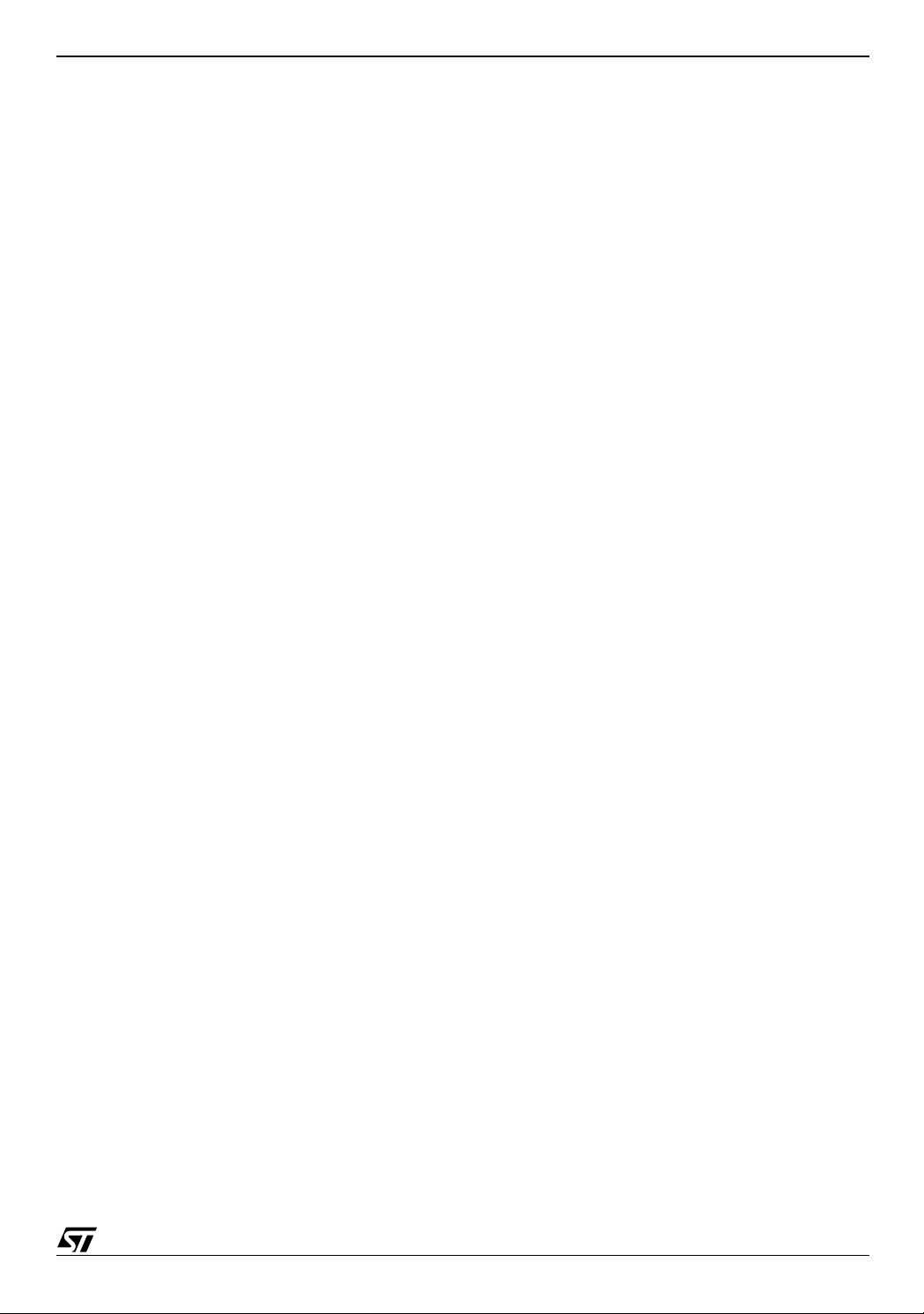

Figure 2. Logic Diagram

V

V

DD

23

A1-A23

V

PP

W

E

G

RP

L

B

K

(1)

WORD

Note: 1. M58LW12 8B onl y.

M58LW128A

M58LW128B

V

V

SS

DDQ

SSQ

16

DQ0-DQ15

16

DQ16-DQ31

RB

R

AI04314

Table 1. Signal Names

A1 Address Input (x16 Bus Width only)

A2-A23 Address inputs

DQ0-DQ15 Data Inputs/Outputs

DQ16-DQ31

B

(1)

E

G

K Clock

L

R Valid Data Ready

RB

RP

V

PP

W

WORD

V

DD

V

DDQ

V

SS

V

SSQ

NC Not Connected Internally

Data Inputs/Outputs (x32 Bus Width of

M58LW128B only)

Burst Address Advance

Chip Enable

Output Enable

Latch Enable

Ready/Busy

Reset/Power-Down

Program/Erase Enable

Write Enable

Word Organization (M58LW128B only)

Supply Voltage

Input/Output Supply Voltage

Ground

Input/Output Ground

7/65

M58LW128A, M58LW128B

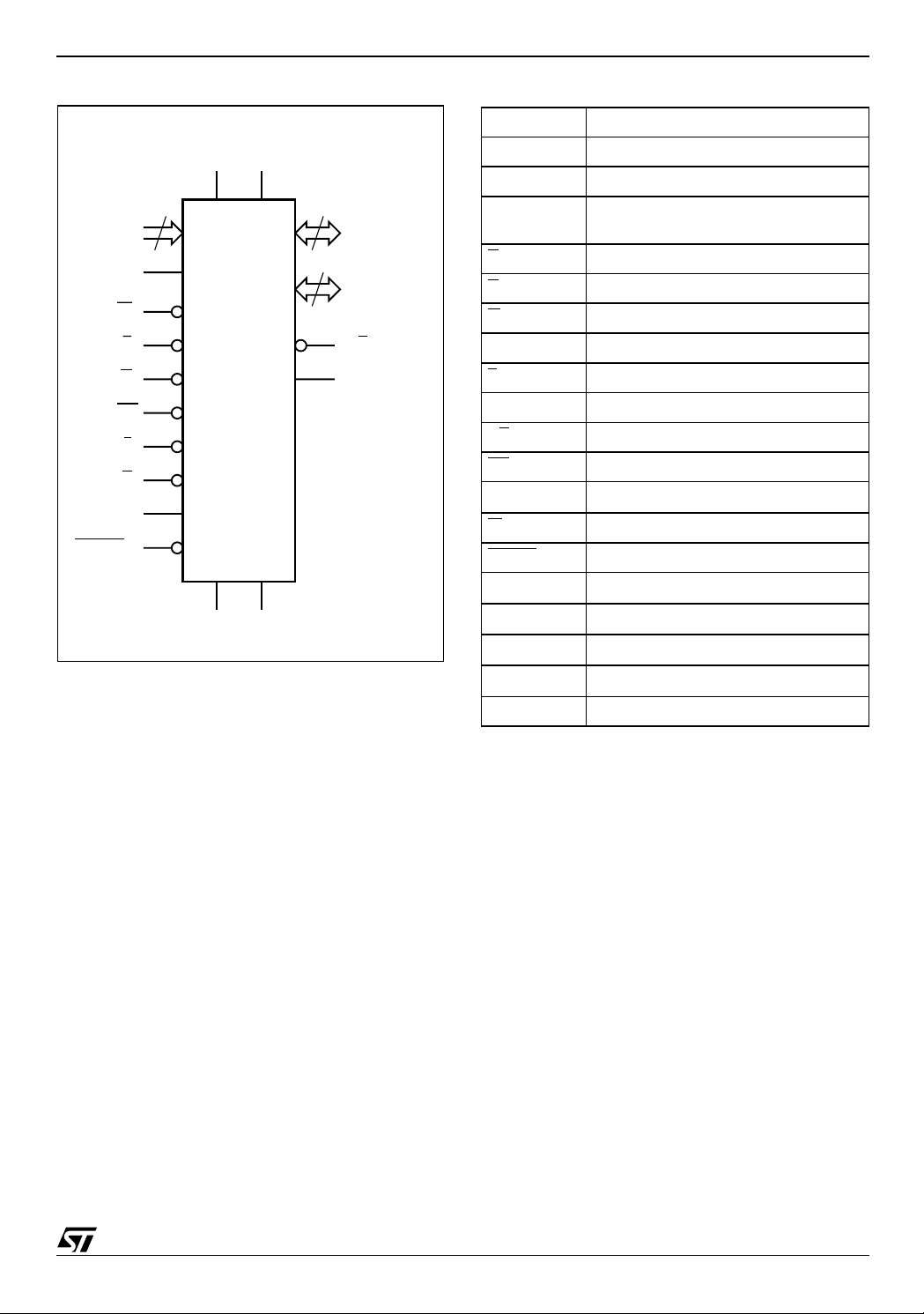

Figure 3. TSOP56 Connections

A22

A21

A20

A19

A18

A17

A16

V

A15

A14

A13

A12

V

A11

A10

V

DD

PP

RP

A9

A8

SS

A7

A6

A5

A4

A3

A2

A1

1

R

E

14

M58LW128A

15

28 29

56

43

42

NC

W

G

RB

DQ15

DQ7

DQ14

DQ6

V

SSQ

DQ13

DQ5

DQ12

DQ4

V

DDQ

V

SS

DQ11

DQ3

DQ10

DQ2

V

DD

DQ9

DQ1

DQ8

DQ0

B

K

A23

L

AI04315

8/65

M58LW128A, M58LW128B

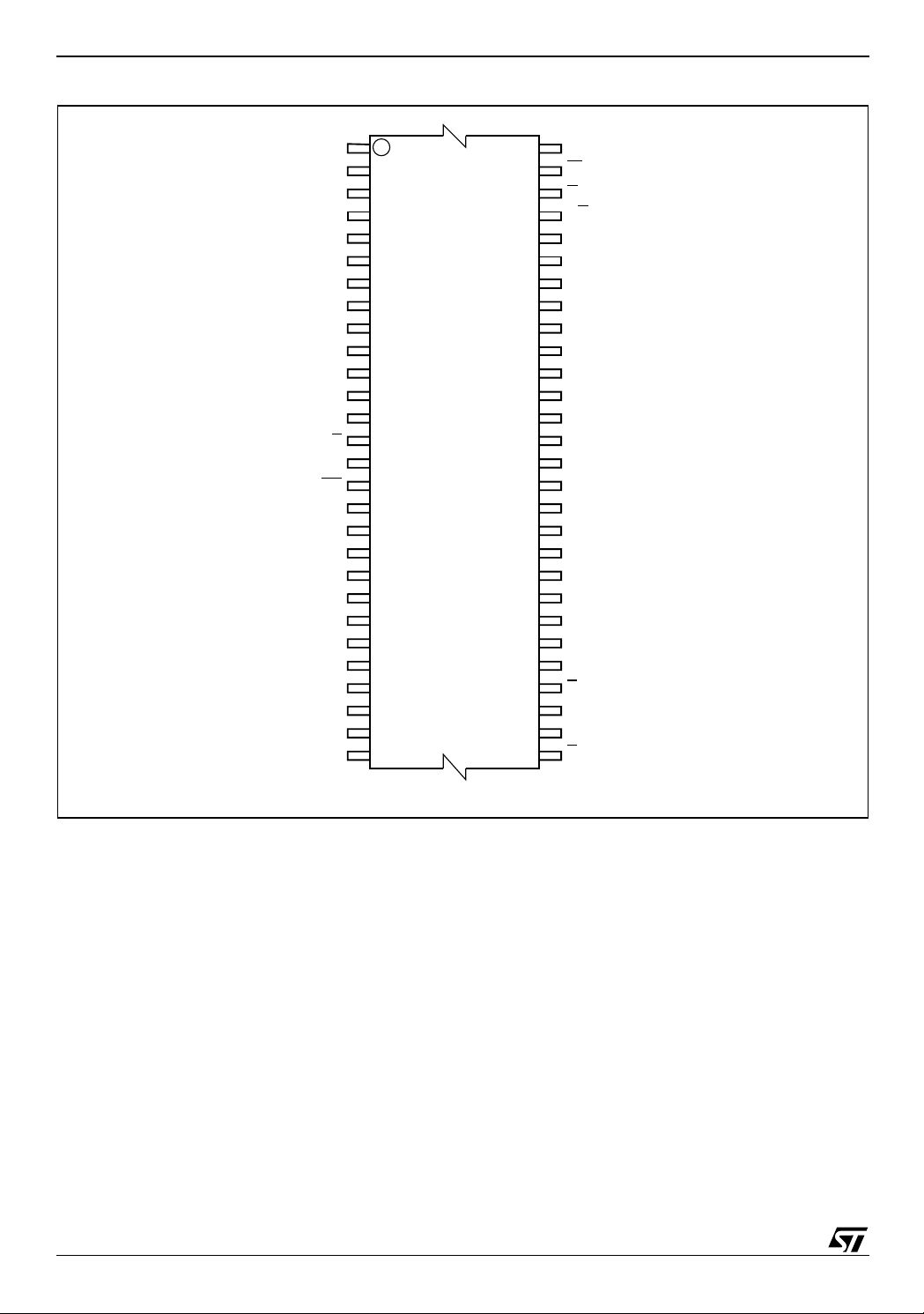

Figure 4. TBGA64 Connections for M58LW128A (Top view through package)

87654321

A

B RA19A2

C

D A16

E

F

G

A1

V

A4 A5

K

A23

DQ0

A6 V

SS

A7A3

A8

A10 A12

A11

DQ10

DQ2B

PP

EA9

RP

DDQ

A13

A14

A15

NC NC

DQ5V

V

DD

NC

NC

NC

NC NC

DQ6

DQ15 RBDQ9DQ8 DQ1 DQ4DQ3

DQ14

A20

A22A18

A21

A17

GDQ12DQ11

W

H

L

NC

V

DD

V

SS

DQ13

V

SSQ

DQ7

NC

AI04316

9/65

M58LW128A, M58LW128B

Figure 5. TBGA80 Connections for M58LW128B (Top view through package)

87654321

A

B RA19A2

C

D NC

E

F

G

A1

A4 A5

DQ24

A8 A22A18

A7

A6A3

DQ25

DQ18

V

SS

A10

A11

DQ27

LDQ17 DQ26 DQ30DQ5DQ3

E

A12A9

V

PP

RP

A13

A14

A15

A23

DQ6WORD

V

DD

A16

A17

NC

DQ28

DQ20 DQ29

W DQ21

A20

DQ22 DQ31DQ19DQ16

A21

NC

DQ23DQ13DQ10

10/65

H

J

K

K DQ15DQ2 DQ12B DQ11 GRB

DQ0

DQ8

DQ1

DQ9 DQ14

V

DD

V

DD

SS

V

SS

DQ4V

V

DDQ

V

V

SSQ

DDQ

V

V

SSQ

DDQ

DQ7

AI04318

Figure 6. Block Addresses

M58LW128A, M58LW128B

M58LW128A, M58LW128B

Word (x16) Bus Width

Address lines A1-A23

7FFFFFh

7F0000h

7EFFFFh

7E0000h

01FFFFh

010000h

00FFFFh

000000h

Note: A l so see Appe ndi x A, Table 28 for a full listing of the Block Addresses

1 Mbit or

64 KWords

1 Mbit or

64 KWords

Total of 128

1 Mbit Blocks

1 Mbit or

64 KWords

1 Mbit or

64 KWords

SIGNAL DESCRIPTIONS

See Figure 2, Logic Diagram and Table 1, Signal

Names, for a brief overview of the signals connected to this device.

Address Inputs (A1-A23). The Address Inputs are used to select the cells to access in the memory array during Bus Read operations either to read or to program data to. During Bus Write operations they control the commands sent to the Command Interface of the internal state m ac hine. Chip Enable must be low when selecting the addresses.

The address inputs are latched on the rising edge

of Chip Enable, Write Enable or Latch Enable,

whichever occurs first in a write operation. The address latch is transparent when Latch Enable is

low, V

. The address is internally latched in a pro-

IL

gram or erase operation.

With a x32 Bus Width, WORD

= VIH, Address Input

A1 is ignored; the Least Significant Word is output

on DQ0-DQ15 and the Most Significant Word is

output on DQ16-DQ31. With a x16 Bus Width,

WORD

on DQ0-DQ15 when A1 is lo w, V

= VIL, the Least Significant Word is ou tput

and the Most

IL,

Significant Word is output on DQ0-DQ15 when A1

is high, V

.

IH

Data Inputs/Outputs (DQ0-DQ31). The Data Inputs/Outputs output the data stored at the selected address during a Bus Read operation, or are used

to input the data during a Program operation. During Bus Write operations they repres ent the commands sent to the Command Interface of the

internal state machine. When used to input data or

write commands they are latched on the rising

edge of Write Enable or Chip Enable, whichever

occurs first.

When Chip Enable and Output Enable are both

low, V

ory array, the Electronic Signature, the Block Protection status, the CFI Information or the contents

of the Status Register. The data bus is high impedance when the chip is deselected, Output E nable

is High, V

Low, V

active the Ready/Busy status is given on DQ7

while DQ0-DQ6 and DQ8-DQ 31 are high impedance.

With a x16 Bus Width, WORD

are not used and are high impedance.

Chip Enable (E

vates the memory control logic, input buffers, decoders and sense amplifiers. Chip Enable, E

V

consumption to the Standby level, I

Output Enable (G

the outputs through the data output buffers during

a read operation. When Output Enable, G

M58LW128B

Double-Word (x32) Bus Width

Address lines A2-A23

(A1 is Don't Care)

3FFFFFh

3F8000h

3F7FFFh

3F0000h

00FFFFh

008000h

007FFFh

000000h

, the data bus outputs data from the mem-

IL

IH,

. When the Program/Erase Controller is

IL

1 Mbit or

32 KDouble-Words

1 Mbit or

32 KDouble-Words

1 Mbit or

32 KDouble-Words

1 Mbit or

32 KDouble-Words

AI06130

or the Reset/Power-Down signal is

= VIL, DQ16-DQ31

). The Chip Enable, E, input acti-

deselects the memory and reduces the power

IH

DD1

.

). The Output Enable, G, gates

, is at V

, at

IH

11/65

M58LW128A, M58LW128B

the outputs are high impedance. Output Enable,

G

, can be used to inhibit the data ou tput during a

burst read operation.

Write Enable (W

). The Write Enable input, W,

controls writing to the Command Interface, Input

Address and Data latches. Both addresses and

data can be latched on the rising edge of Write Enable (also see Latch Enable, L

Reset/Power-Down (RP

).

). The Reset/PowerDown pin can be used to apply a Hardware Reset

to the memory or to temporarily unprotect all

blocks that have been prot e cte d .

A Hardware Reset is achieved by holding Reset/

Power-Down Low, V

, for at least t

IL

Reset/Power-Down is Low, V

, the Status Regis-

IL

PLPH

. When

ter information is cleared and the current is reduced to I

(refer to Table 16, DC

DD2

Characteristics). The device is deselected and

outputs are high impedance. If Reset/PowerDown goes low, V

,during a Block Erase, a Write

IL

to Buffer and Program or a Block Protect/Unprotect the operation is aborted and the data may be

corrupted. In this case the Ready/Bu sy pin stays

low, V

After Reset/Power-Down goes High, V

, for a maximum timing of t

IL

PLPH

+ t

PHRH

, the

IH

.

memory will be ready for Bus Read and Bus Write

operations after t

. Note that Ready/Busy does

RHEL

not fall during a reset, see Ready/Busy Output

section.

During power-up Reset/Power-Down must be held

Low, V

Furthermore it must stay low for t

IL.

VDHPH

after the Supply Voltage inputs become stable.

The device will then be configured in Asynchronous Random Read mode.

See Table 23 and F igure 21, Reset, Power-Down

and Power-up Characteristics, for more details.

Holding RP

at VHH will temporarily unprotect the

protected blocks in the memory. Program and

Erase operations on all blocks will be possible.

In an application, it is recommended to associate

Reset/Power-Down pin, RP

, with the reset sign al

of the microprocessor. Otherwise, if a reset operation occurs while the memory is performing a program or erase operation, the memory may output

the Status Register information instead of being

initialized to the default Asynchronous Random

Read.

Latch Enable (L

). The Bus Interface can be con-

figured to latch the Address Input s on the rising

edge of Latch Enable, L

. In synchronous bus operations the address is latched on the active edge of

the Clock when Latch Enable is Low, V

. Once

IL

latched, the addresses may change without affecting the address used by the memory. When Latch

Enable is Low, V

, the latch is transparent.

IL

Clo c k (K). The Clock, K, is used to synchronize the memory with the external bus during Synchro-

nous Bus Read operations. The Clock can be configured to have an active rising or falling edge. Bus

signals are latched on the active edge of the Clock

during synchronous bus operations. In Synchronous Burst Read m ode the address is latched on

the first active clock edge when Latch Enable is

low, V

, or on the rising edge of Latch Enable,

IL

whichever occurs first.

During Asynchronous Bus operations the Clock is

not used.

Burst Address Advance (B

Advance, B

, controls the advancing of the address

). The Burst Address

by the internal address counter during synchronous bus operations.

Burst Address Advance, B

, is only sampled on the

active clock edge of the Clock when the X- or Y latency time has expired. If Burst Address Advance is Low, V

vances. If Burst Address Advance is High, V

, the internal address counter ad-

IL

IH

, the

internal address counter does not change; the

same data remains on the Data Inputs/Outputs

and Burst Address Advance is not sampled until

the Y-latency expires.

The Burst Address Advance, B

, may be tied to VIL.

Valid Data Ready (R). The Valid Data Ready output, R, is an open drain output that can be used to identify if the memory is ready to output data or not. The Valid Data Ready output is only active during Synchronous Burst Read operat ions when the Burst Length is set to Continuous. The Valid Data Ready output can be configured to be active on the clock edge of the invalid data read cycle or one cycle before. Valid Data Ready Low, VOL, indicates that the data is not, or will not be valid. Valid Data Ready in a high-impedance state indicates that valid data is or will be available.

Unless the Burst Length is set to Cont inuous and

Synchronous Burst Read has been selected, Valid

Data Ready is high-impedance. It may be tied t o

other components with the same Valid Data

Ready signal to create a unique System Ready

signal.

When the system clock frequency is between

33MHz and 50MHz and the Y latency is set to 2,

values of B

sampled on odd clock cycles, starting

from the first read are not considered.

Designers should use an external pull-up resistor

of the correct value to meet the external timing requirements for Valid Data Ready rising. Refer to

Figure 20.

Word Organization (WORD

zatio n inpu t, WORD

, selects the x16 or x32 B us

). The Word Organi-

Width on the M58L W128B. The Word Organization input is not available on the M58LW128A.

When WORD

is Low, VIL, Word-wide x16 Bus

Width is selected; data is read and written to DQ0DQ15; DQ16-DQ31 are at high impedance and A1

12/65

M58LW128A, M58LW128B

is the LSB of the address bus. When WORD is

High, V

, the Double-Word wide x32 Bus Width is

IH

selected and the data is read and written to on

DQ0-DQ31; A2 is the LSB of the address bus and

A1 is don’t care.

Ready/Busy (RB

). The Ready/Busy output, RB,

is an open-drain output that can be used to identify

if the Program/Erase Controller is currently active.

When Ready/Busy is high impedance, the mem ory is ready for any read, program or erase operation. Ready/Busy is Low, V

, during program and

OL

erase operations. When the de vice is busy it will

not accept any additional Program or Erase commands except Program/Erase Suspend. When the

Program/Erase Controller is idle, or suspended,

Ready Busy can float High through a pull-up resistor.

The use of an open-drain output allows the Ready/

Busy pins from several memories to be connected

to a single pull-up resistor. A Low will then indicate

that one, or more, of the memories is busy.

Ready/Busy is not Low during a reset unless the

reset was applied when the Program/Erase Controller was active; Ready/Busy can rise before Reset/Power-Down rises.

Program/Erase Enable (V

Erase Enable input, V

). The Program/

PP

is used to protect all

PP,

blocks, preventing Program and Erase operations

from affecting their data.

When Program/Erase Enable is Low, V

, any pro-

IL

gram or erase operation sent to the Command Interface will cause the V

Status bit (bit3) in the

PP

Status Register to be set. When Program/Erase

Enable is High, V

, program and erase operations

IH

can be performed on unprotected blocks. Program/Erase Enable must be kept High during all

Program, Erase, Block P rotect and Block Unpro-

tect operations, otherwise the operation is not

guaranteed to succeed and data may become corrupt.

V

Supply Voltage. The Supply Voltage, VDD,

DD

is the core power supply. Al l internal c ircuits draw

their current from the V

pin, including the Pro-

DD

gram/Erase Controller.

A 0.1µF capacitor should be connec ted between

the Supply Voltage, V

, and the Ground, VSS, to

DD

decouple the current surges from the power supply. The PCB track widths must be sufficient to

carry the currents required during all operations of

the parts, see Table 16, DC Characteristics, for

maximum current supply requirements.

Input/Output Supply Voltage (V

put/Output Supply Voltage, V

DDQ

). The In-

DDQ

, is the input/output buffer power supply. All input and output pins

and voltage references are powered and measured relative to the Input /Output Suppl y Voltage

pin, V

The Input/Output Supply Volt age, V

ways be equal or less than the V

DDQ

.

, mus t al-

DDQ

Supply Volt-

DD

age, including during Power-Up.

A 0.1µF capacitor should be connec ted between

the Input/Output Supply Voltage, V

Ground, V

from the power supply. If V

, to decouple the current surges

SSQ

and VDD are con-

DDQ

DDQ

, and the

nected together then onl y one decoupling capac itor is required.

Ground (V

). Ground, V

SS

is the reference for

SS,

all core power supply voltages.

Ground (V

). Ground, V

SSQ

is the reference

SSQ,

for input/output voltage measurements. It is essential to connect V

ground

.

SS

and V

to the same

SSQ

13/65

M58LW128A, M58LW128B

BUS OPERATIONS

The bus operations that control the memory are

described in this section, see Tables 2 and 3, Bus

Operations, for a summary. The bus operation is

selected through the Burst Configuration Register;

the bits in this register are described at the end of

this secti on.

On Power-up or after a Hardware Reset the memory defaults to Asynchronous Bus Read and Asynchronous Bus Write, n o other bus operation can

be performed until the Burst Control Register has

been configured.

Synchronous Read operations and Latch Controlled Bus Read operations can only be used to

read the memory array. The Electr onic Sign ature,

CFI or Stat us Register will b e read in asynchro nous mode regardless of the Burst Control Register se tt i n gs.

Typically glitches of less than 5ns on Chip Enable

or Write Enable are ignored by the memory and do

not affect bus operations.

Asynchronous Bus Operation s

For asynchronous bus operations refer to Tabl e 3

together with the text below.

Asynchronous Bus Read. Asynchronous Bus

Read operations read from the memory cells, or

specific registers (Electronic Signature, Status

Register, CFI and Block Prot ection Status) in the

Command Interface. A valid bus operation involves setting the desired address on the Address

Inputs, applying a Low sig nal, V

and Output Enable and keeping Write Enable

High, V

. The Data Inputs/Outputs will output the

IH

value, see Figure 12, Asynchronous Bus Read AC

Waveforms, and Table 17, Asynchronous Bus

Read AC Characteristics, for details of when the

output becomes valid.

Asynchronous Latch Controlled Bus Read.

Asynchronous Latch Controlled Bus Read operations read from the m emory cells. T he address is

latched in the memory before the value is ou tput

on the data bu s, allowing the address to cha nge

during the cycle without affecting the address that

the memo r y uses.

A valid bus operation i nvolves set ting the des ired

address on the Address Inputs, setting Chip Enable and Address Latch Low, V

Write Ena ble Hig h, V

; the address is latched on

IH

the rising edge of Address Latch. Once latched,

the Address Inputs can change. Set Output Enable Low, V

, to read the data on the Data Inputs/

IL

Outputs; see Figure 13, Asynchronous Latch Controlled Bus Read AC Waveforms and Table 18,

Asynchronous Latch Controlled Bus Read AC

Characteristics for details on when the out put becomes valid.

, to Chip Enable

IL

and keeping

IL

Note that, since the Latch Enable input is transparent when set Low, V

, Asynchronous Bus Read

IL

operations can be performed when the memory is

configured for Asynchronous Latch Enable bus

operations by holding Latch Enable Low, V

throughout the bus operation.

Asynchronous Page Read. Asynchronous Page

Read operations are used to read from several addresses within the same memory page. Each

memory page is 8 Words or 4 Double-Words and

has the same A 4-A23, only A1, A2 and A3 may

change.

Valid bus operations are the same as Asynchronous Bus Read operations but with different timings. The first read operation within the page has

identical timings, subsequent reads within the

same page have much sh orter access t i mes. If the

page changes then the normal, longer timings apply again. See Figure 14, Asynchronous Page

Read AC Waveforms and Table 19, Asynchronous Page Read AC Characteristics for details on

when the outputs become valid.

Asynchronous Bus Write. Asynchronous Bus

Write operations write to the Command Interface

in order to send commands to the memory or to

latch addresses and in put data to program. Bus

Write operations are asynchronous, the clock, K,

is don’t care during Bus Write operations.

A valid Asynchronous Bus Write operation begins

by setting the desired address on the A ddress I nputs and setting Latch Enabl e Low, V

. The Ad-

IL

dress Inputs are latched by the Command

Interface on the rising edge of Chip Enable or

Write Enable, whichever occurs first. The Data Inputs/Outputs are la tched by the Comm and Interface on the rising edge of Chip Enable or Write

Enable, whichever occurs first. Output Enable

must remain High, V

, during the whole Asyn-

IH

chronous Bus Write operation. See Figures 15,

and 17, Asynchronous Write AC Wavef orms, and

Tables 20 and 21, Asynchronous Write and Latch

Controlled Write AC Characteristics, for details of

the timing requirements.

Asynchronous Latch Controlled Bus Write.

Asynchronous Latch Controlled Bus W rite operations write to the Command Interface in order to

send commands to the memory or to latch addresses and input data t o p rogram . Bus W r ite operations are asynchronous, the clock , K, is don’t

care during Bus Write operations.

A valid Asynchronous Latch Controlled Bus Write

operation begins by setting the desired address on

the Address Inputs and pulsing Latch Enable Low,

V

. The Address Inputs are latched b y the Com-

IL

mand Interface on the rising edge of Latch Enable,

Chip Enable or Write Enable, whichever occurs

IL

14/65

M58LW128A, M58LW128B

first. The Data Inputs/Outputs are latched by the

Command Interface on the rising edge of Chip Enable or Write Enable, whichever occurs first. Ou tput Enable must remain High, V

, during the

IH

whole Asynchronous Bus Write operation. See

Figures 16 and 18 Asynchronous Latch Controlled

Write AC Waveforms, and Tables 20 and 21,

Asynchronous Write and Latch Controlled Write

AC Characteristics, for details of the timing requirements.

Output Disa bl e . The Data Inputs/Outputs are in the high impedance state when the Output Enable is High.

Standby. When Chip Enable is High, V

IH

, the

puts/Outputs pins are placed in the high impedance state regardless of Output Enable or Write

Enable. The Supply Current is reduced to the

Standby Supply Current, I

During Program or Erase operations the memory

will continue to use the Program/Erase Supply

Current, I

til the operation completes.

Power-Down. The memory is in Power-Down mode when Reset/Power-Down, RP current is reduced to I high impedance, independent of Chip Enable, Output Enable or Write Enable.

memory enters Standby mode and the Data In-

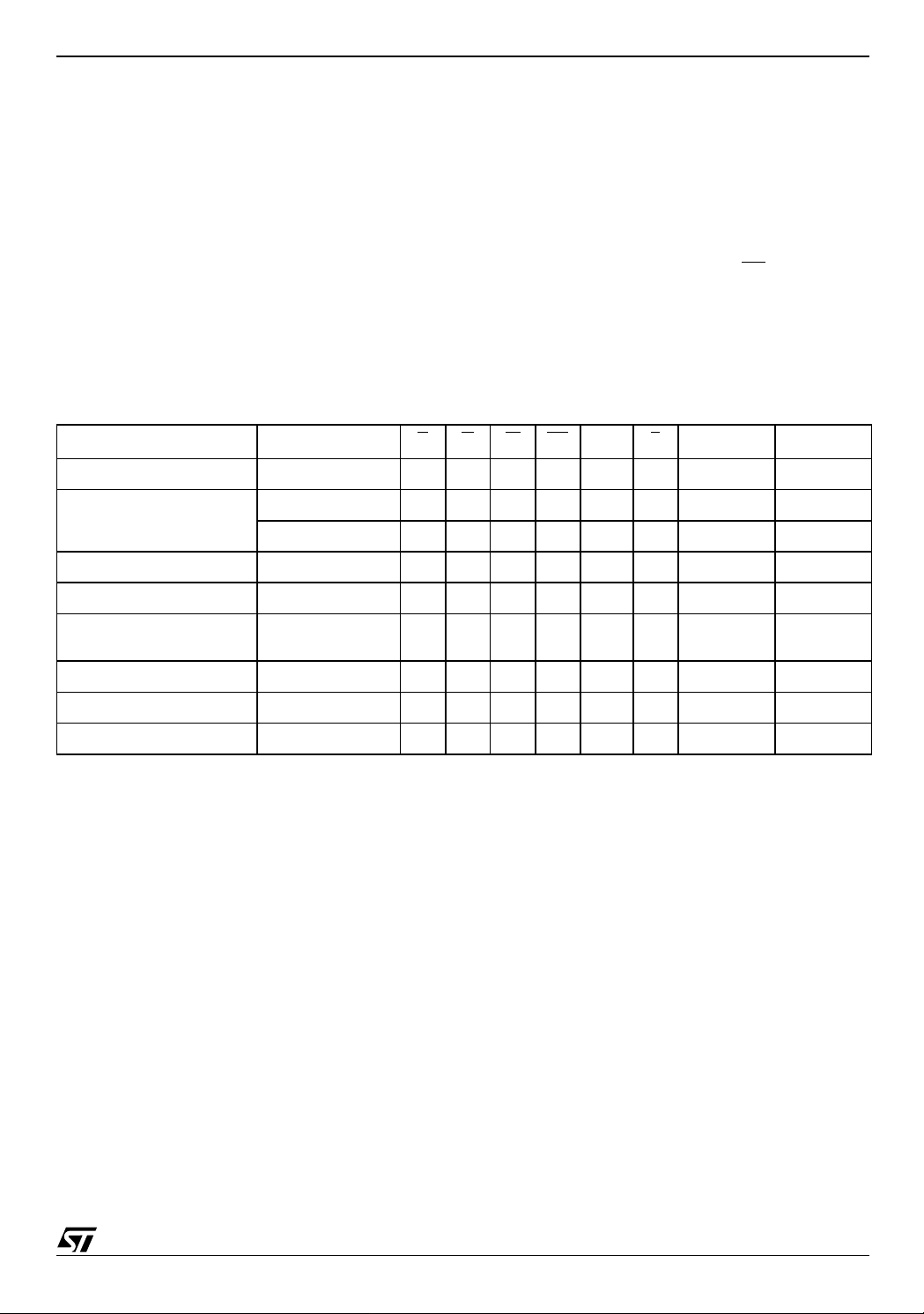

Table 2. Asynchronous Bus Operations

Bus Operation Step E G W RP

Asynchronous Bus Read

Asynchronous Latch

Controlled Bus Read

Asynchronous Page Read

Asynchronous Bus Write

Asynchronous Latch

Controlled Bus Write

Output Disable

Standby

Power-Down X X X

Note: 1. X = Don’t Car e VIL or VIH. High = VIH or VHH.

2. M15 = 1, Bit s M15 and M3 are in the Burst Configura tion Register.

Address Latch

Read

Address Latch

V

ILVILVIH

V

ILVILVIH

V

ILVILVIH

V

ILVILVIH

V

ILVIHVIL

V

ILVIHVIL

V

ILVIHVIH

V

X X High X X X High Z

IH

.

DD1

, for Program or Erase operations un-

DD3

, is Low. The

, and the outputs are

DD2

(2)

M3

High 0 X Address Data Output

High 1

High 1

High 0 X Address Data Output

High X

High X

High X X X High Z

V

IL

L A1-A23 DQ0-DQ31

V

Address High Z

IL

V

IH

V

IL

V

IL

X X X High Z

X Data Output

Address Data Input

Address Data Input

15/65

M58LW128A, M58LW128B

Synchronous Bus Operations

For synchronous bus operat ions refer to Table 3

together with the text below.

Synchronous Burst Read. Synchronous Burst

Read operations are used to read from the memory at specific times synchronized to an external reference clock. The burst type, length and latency

can be configured. The different configurations for

Synchronous Burst Read operations are described in the Burst Configuration Register section.

A valid Synchronous Burst Read operation begins

when the address is set on the Address Inputs,

Write Enable is High, V

Latch Enable are Low, V

, and Chip Enable and

IH

, during the active edge

IL

of the Clock. The address is latched on the first active clock edge when Latch Enable i s low, or on

the rising edge of Latch Enable, whichever occurs

first. The data becomes available for output after

the X-latency specified in the Burst Control Register has expired. The output buffers are activated

by setting Output E nable Low, V

. See Figure 7

IL

for an example of a Synchron ous Burst Read operation.

The Burst Address Advance input and the Y-latency specified in the Burst Control Register determine whether the internal address counter is

advanced on the active edge of the Clock. When

the internal address counter is advanced the Data

Inputs/Outputs change to output the v alue for t he

next address.

In Continuous Burst mode (Burst Length Bit M2-

M0 is set to ‘111’), one Burst Read operation can

access the entire m emory sequentially and wrap

at the last address. The Burst Address Advance,

B

, must be kept low , VIL, for the appropriate number of clock cycles. If Burst Address Advance, B

is pulled High, V

, the Burst Read will be sus-

IH

pended.

In Continuous Burst Mode , if the starting addres s

is not associated with a page (4 Word or 2 Double

Word) boundary the Va lid Data Ready, R, ou tput

goes Low, V

, to indicate that the data will not be

IL

ready in time and additional wait-states are required. The Valid Data Ready output timing (bit

M8) can be changed in the Burst Configuration

Register.

When using the x32 Bus Width certain X-latencies

are not valid and must not be used; s ee Table 5,

Burst Configuration Register.

The Synchronous Burst Read timing diagrams

and AC Characteristics a re described in the AC

and DC Parameters section. See Figures 19, 20

and Table 22.

Synchronous Pipelined Burst Read. Synchronous Burst Read operations can be overlapped to

avoid or reduce the X-latency. Pipelined operations should only be used with Burst Configuration

Register bit M9 = 0 (Y-latency setting).

A valid Synchronous Pipelined Burst Read operation occurs during a Sy nchronous Burs t Read operation when the new address is set on the

Address Inputs and a Low pulse is applied to Latch

Enable. The data for the new address becomes

valid after the X-latency specified in the Burst Configuration Register has expired.

For optimum operation the address should be

latched on the correct clock cycle. Table 4 gives

the clock cycle for each valid X- and Y-latency setting. Only these settings are valid, other settings

must not be used. There is always one Y-Latency

period where the data is not valid. If the address is

latched later than the clock cycle s pecified in Tables 4 then additional cycles where the data is not

valid are inserted. See Figure 8 for an example of

a Synchronous Pipelined Burst Read operation.

Here the X-latency is 8, the Y-latency is 1 and the

burst length is 4; the first address is latched on cycle 1 while the next address is latched on cycle 6,

as shown in Table 4.

Synchronous Pipelined Burst Read operations

should only be performed on Burst Lengths of 4 or

8 with a x16 Bus Width or a Burst Length of 4 with

a x32 Bus Width.

Suspending a Pipelined S ynch ronous B urst Read

operation is not recommended.

,

Synchronous Burst Read Suspend. During a

Synchronous Burst Read operation it is possible to

suspend the operation, freeing the data bus for

other higher priority devices.

A valid Synchronous Burst Read operation is suspended when b oth Output Enable an d Burst Address Advance are H igh, V

Advance going High, V

and the Output Enable going High, V

. The Burst Address

IH

, stops the burst counter

IH

IH

data outputs. The Synchronous Burst Read operation can be resumed by setting Output Enable

Low. See Figure 7 for an example o f a Synchronous Burst Read Suspend operation.

, inhibits the

16/65

M58LW128A, M58LW128B

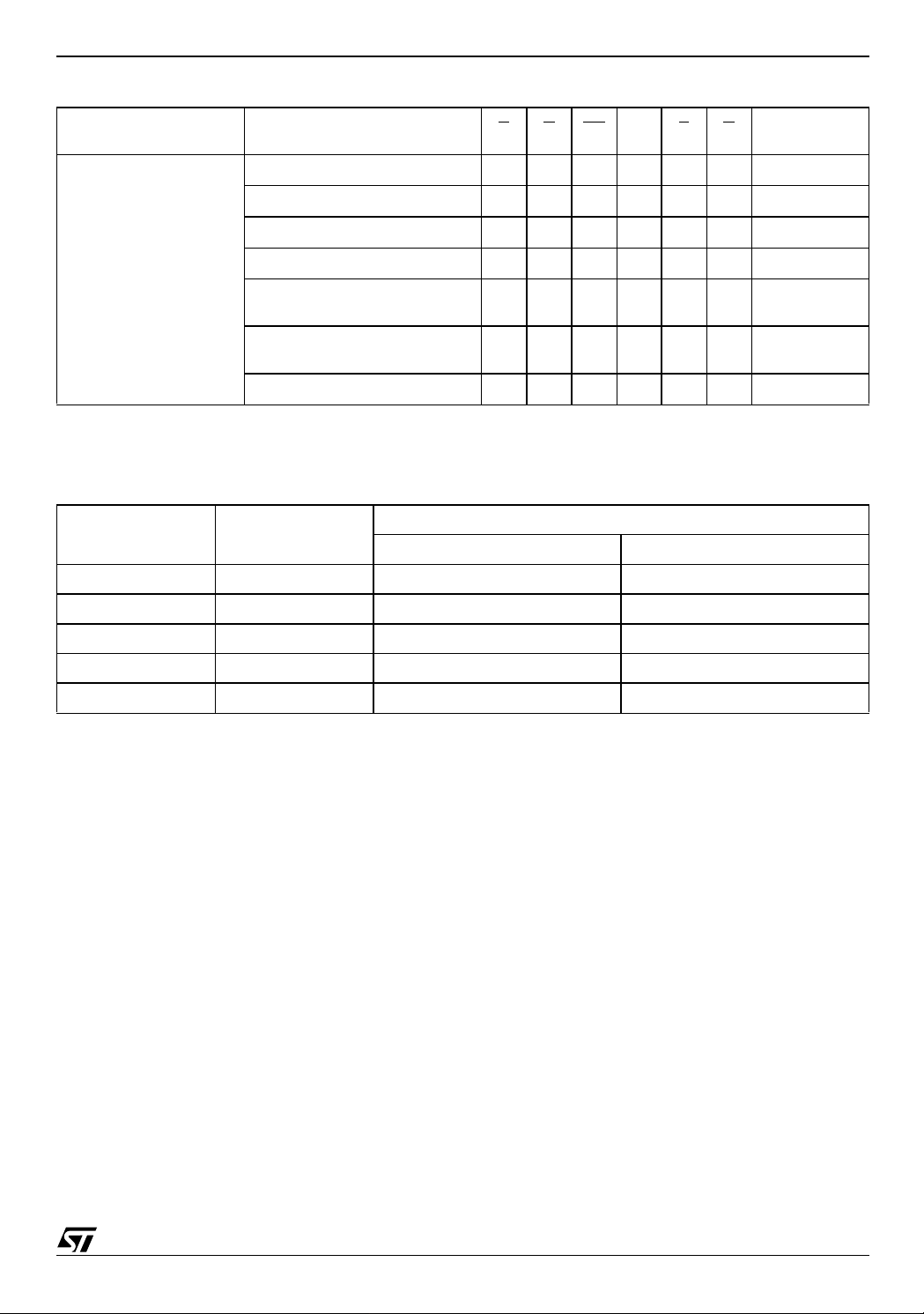

Table 3. Synchronous Burst Read Bus Operation s

Bus Operation Step E G RP

X

VILV

VILV

VILV

VILV

X

V

V

Address Latch

Read (no address advance)

Read (with address advance)

Synchronous Burst Read

Pipelined Synchronous

Burst Read

Read Suspend

Read Resume (no address

advance)

Read Resume (with address

advance)

Read Abort

Note: 1. X = Don’t Care, VIL or VIH.

2. M15 = 0, Bit M 15 i s in the Burs t C onfiguration Register.

3. T = tra nsition, see M6 in the Burst Conf i guration Register for details on the active edge of K.

V

IL

V

IL

V

IL

V

ILVIHVIH

V

IL

V

IL

V

IH

Table 4. Addre s s Lat ch Cycle for Optimum Pipelin ed S ynchronous Burst Read

X-Latency Y-Latency

Burst Length = 4 Burst Length = 8

81 6 10

Address Latch Clock Cycle

K

IH

IH

IH

IH

IH

IH

(3)

L B

V

T

IL

TX

TX

XX

TX

TX

XX

A1-A23

DQ0-DQ31

X Address Input

V

Data Output

IH

V

Data Output

IL

V

IH

V

IH

V

IL

X

High Z

Data Output

Data Output

High Z

91 7 11

12 1 10 14

13 1 11 15

15 2 11 19

17/65

M58LW128A, M58LW128B

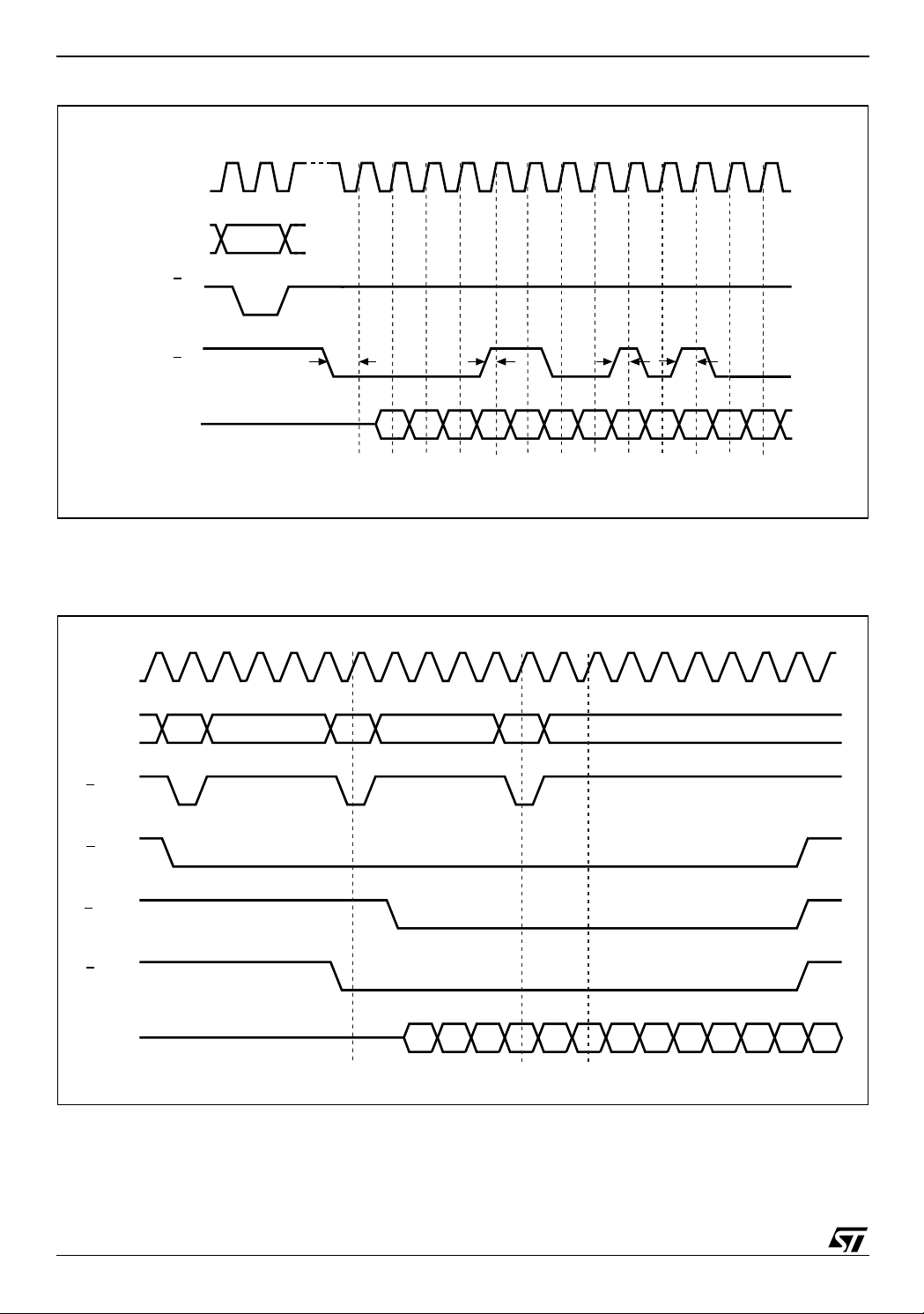

Figure 7. Synchronous B urst Re ad Operation

1

0

K

Address

Inputs

L

B

Data Inputs/

Outputs

Note: I n this exa mple t he Bur st Co nfigur ati on Reg ist er is set with M 2-M 0 = 001 (B urst Lengt h = 4 Wo rds or Doubl e Word s) , M6 = 1 (Valid

Clock Edge = Rising Clock Edge), M7 = 0 or 1 (Burst Type = Interleaved or Sequential), M9 = 0 (Y-Latency = 1), M14-M11 = 0011 (X-

Latency = 8) and M15 = 0 (Rea d Se l ect = Synchronous Burst Read), other bi ts are don’t care.

Q1

X-1

X

tBLKH

Q1

X+1

Q2

tBHKH

tBHKH

Q5Q5Q5Q4Q3 Q7Q6 Q8Q8Q7

tBHKH

AI03454b

Figure 8. Exam pl e Synchronous Pipelined Burst Read Op era ti on

01234567891011121314

K

15

Address

Inputs

L

E

G

B

Data

Inputs/ Outputs

Note: I n this exa mple t he Bur st Co nfigur ati on Reg ist er is set with M 2-M 0 = 001 (B urst Lengt h = 4 Wo rds or Doubl e Word s) , M6 = 1 (Valid

Clock Edge = Rising Clock Edge), M7 = 0 or 1 (Burst Type = Interleaved or Sequential), M9 = 0 (Y-Latency = 1), M14-M11 = 0011 (XLatency = 8) and M15 = 0 (Rea d Se l ect = Synchronous Burst Read), other bi ts are don’t care.

Q1 R1 S1

Q1

Q2 Q3 Q4 NV R1 R2 R3 R4 NV S1 S2

NV= Not Valid

S3

AI03455

18/65

M58LW128A, M58LW128B

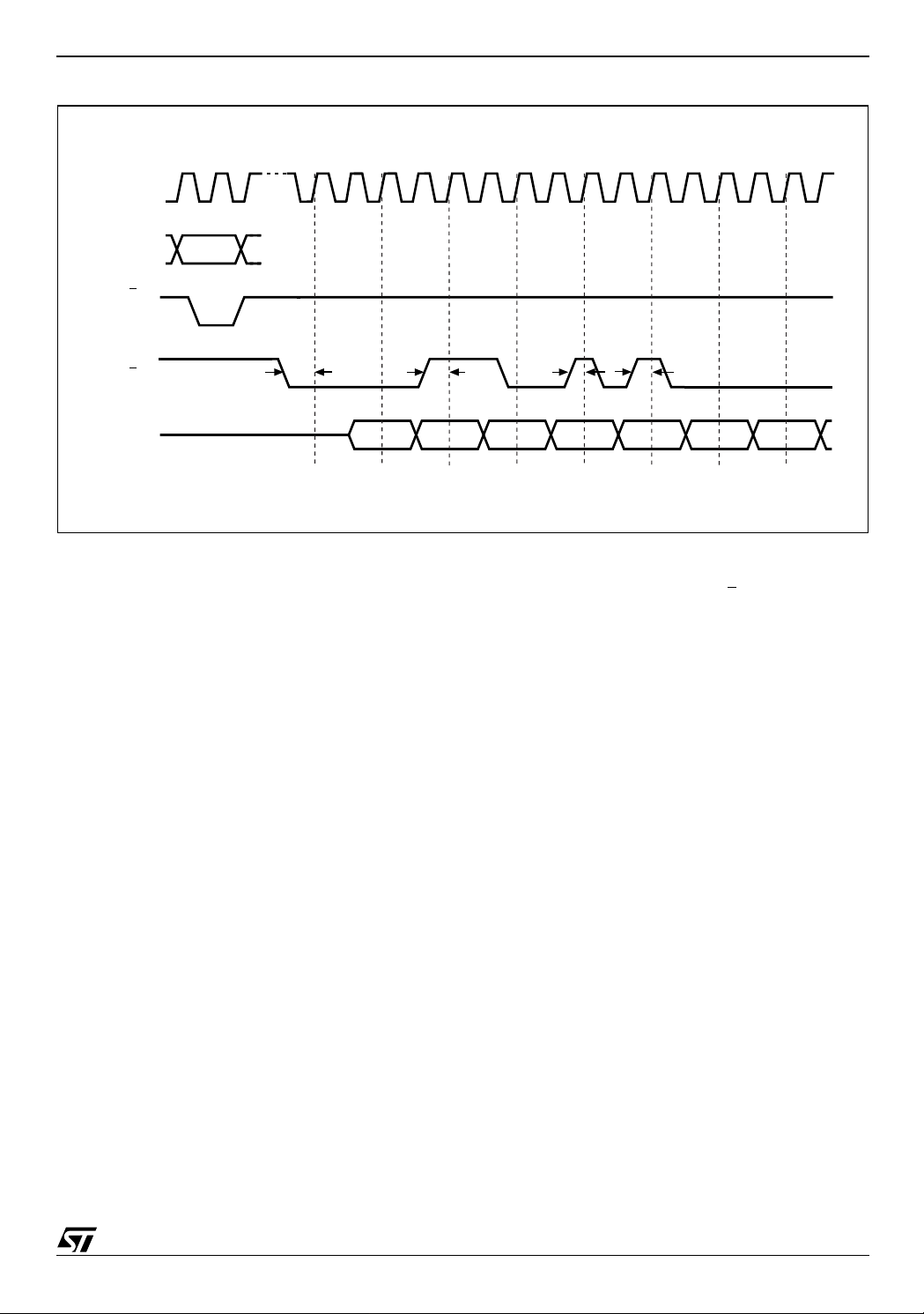

Figure 9. Example Burst Address Advance and Burst Abort operations

1

0

K

Address

Inputs

L

B

Data Inputs/

Outputs

Note: 1. In this exam pl e the Bur st Co nf igurat ion Reg ister is set with M 2-M 0 = 010 (B urst Lengt h = 8 Words ), M 6 = 1 (V alid C loc k Edg e =

Rising Clock Edge), M 7 = 0 or 1 (Burst Type = In te rl eaved or Se quential) , M9 = 1 (Y-Lat ency = 2), M14-M11 = 0011 (X-Latency =

8) and M15 = 0 (Read Select = Sy nchronous Burst Read ), other bits a re don’t care.

2. Whe n t he system clock fre quency is be tween 33MHz and 50MHz and th e Y latenc y i s set to 2, values of B

cycles, starting from t he first read are not conside red.

Q1

X-2

tBLKH

X

Q1 Q2

X+2

tBHKH

X+6X+4 X+12X+10X+8

tBHKH

Q3 Q4 Q4

tBHKH

Q4Q3

AI03457b

sampled on odd clock

19/65

M58LW128A, M58LW128B

Burst Configuration Register

The Burst Configuration Register is used to configure the type of bus access that the memory will

perform.

The Burst Configuration Register is set through

the Command Interface and will retain its information until it is re-configured, the device is reset, or

the device goes into Reset/Power-Down mode.

The Burst Configuration Register bits are described in Table 5. They specify the selection of

the burst length, burst type, burst X and Y latencies and the Read operation.

Read Select Bit (M15). The Read Select bit,

M15, is used to switch between asynchronous and

synchronous Bus Read operations. When the

Read Select bit is set to ’1’, Bus Read operations

are asynchronous; when the Read Select but is

set to ’0’, Bus Read operations are synchronous.

On reset or power-up the Read Sel ect bi t is set

to’1’ for asynchronous accesses.

X-Latency Bits (M14-M11). The X-Latency bits are used during Synchronous Bus Read operations to set the number of clock cycles between the address being latched and the first data becoming available. For correct operation the X-Latency bits can only assume the values in Table 5, Burst Configuration Register. The X -Latency bits should also be sele cted in con junction with Table 8, Burst Performance to ensure valid settings.

Y-Latency Bit (M9). The Y-Latency bit is used

during Synchronous Bus Read operations to set

the number of clock cycles between consecutive

reads. The Y-Latency value depends on both the

X-Latency value and the setting in M9.

When the Y-Latency is 1 the data changes each

clock cycle; when the Y-Latency is 2 the data

changes every seco nd clock cycle. See Tab le 5,

Burst Configuration Register and Table 8, Burst

Performance, for valid co mbinations of the Y-Latency, the X-Latency and the Clock frequency.

Valid Data Ready Bit (M8). The Valid Data Ready bit controls the timing of the Valid Data

Ready output pin, R. When the Valid Data Ready

bit is ’0’ the Valid Data Ready output pin is driven

Low for the active clock edge when invalid data is

output on the bus. When the Valid Data Ready bit

is ’1’ the Valid Data Ready output pin is driven Low

one clock cycle prior to invalid data being output

on the bus.

Burst Type Bit ( M7 ). The Burst Type bit is used to configure the sequence of addresses read as sequential or interleaved. When the Burst Type bit is ’0’ the memory outputs from interleaved addresses; when the Burst Type bit is ’1’ the memory outputs from sequential ad dresses. See Tables 6 and 7, Burst Type Definition, for t he sequence of addresses output from a give n starting a ddress in each mode.

Valid Clock Edge Bit (M6). The Valid Clock Edge bit, M6, is used to configure the active edge of the Clock, K, during Synchronous Burst Read operations. When the Valid Clock Edge bit is ’0’ the falling edge of the Clock is the active edge; when the Valid Clock Edge bit is ’1 ’ the rising edge of the Clock is active.

Latch Enable Bit (M3). The Latch Enable bit is

used to select between Asynchronous Random

Read and Asynchronous La tch Enable Controlled

Read. When the Latch Enable bit is set to ‘0’ Random read is selected; when it is set to ‘1’ Latch Enable Controlled Read is selected. To enable these

Asynchronous Read configuration s M15 must be

set to ‘1’.

Burst Length Bit (M2-M0). The Burst Length bits set the maximum number of Words or DoubleWords that can be ou tput during a Synchronous Burst Read operation before the address wraps.

Table 5, Burst Configuration Register gives the

valid combinations of the Burst Length bits that the

memory accepts; Tables 6 and 7, Burst Type Definition, give the sequence of addresses output

from a given starting address for each length.

M10, M5 an d M4 are reserved for future use.

20/65

Table 5. Burst Configuration Registe r

Address

Bit

17 M15

Mnemonic Bit Name

Read

Select

Reset

Value

1

M58LW128A, M58LW128B

Value Description

0 Synchronous Burst Read x16 or x32

1 Asynchronous Bus Read x16 or x32

Valid Bus

Width

16

to

13

11 M9

10 M8

M14-M11 X-Latency XXXX

Y-Latency

Valid Data

Ready

0010

0011 X- Laten cy = 8 x16 or x32

0100 X- Laten cy = 9 x16 or x32

0101

0110

1001 X-Latency = 12 x16 only

1010 X-Latency = 13 x16 only

1011

1101 X- Laten cy = 15 x16 or x32

Others Reserved, Do Not Use.

X

X

X-Latency = 7, use only with Continuous Burst

Length

X-Latency = 10, use only with Continuous Burst

Length

X-Latency = 11, use only with Continuous Burst

Length

X-Latency = 13, use only with Continuous Burst

Length

When X-Latency < 13, Y-Latency = 1

0

When M14-M11 = 1011 or 1101, Y-Latency = 2

When X-Latency ≤15 but M14-M11≠1011 or

1101, Y-Latency = 2,

1

When M14-M11=1011 or 1101 DO NOT USE.

0 R valid Low during valid Clock edge x16 or x32

1 R valid Low one cycle before valid Clock edge x16 or x32

x16 or x32

x16 only

x16 only

x16 or x32

x16 or x32

x16 or x32

9 M7 Burst Type X

8M6

5M3

4

to

2

M2-M0

Valid Clock

Edge

Latch

Enable

Burst

Length

XXX

0 Interleaved x16 or x32

1 Sequential x16 or x32

0 Falling Clock edge x16 or x32

X

1 Rising Clock edge x16 or x32

0 Random Read x16 or x32

0

1 Latch Enable Controlled Read x16 or x32

100 1 Word or Double-Word x16 or x32

101 2 Words or Double-Words x16 or x32

001 4 Words or Double-Words x16 or x32

010 8 Words x16 only

111 Continuou s x16 or x32

Others Reserved, Do Not Use.

21/65

M58LW128A, M58LW128B

Table 6. Burst Type Definition (x16 Bus Width)

Starting Addres s

Burst Length

2

4

8

(binary)

A3 A2 A1

XX0 0, 1 0, 1

XX1 1, 0 1, 0

X00 0, 1, 2, 3 0, 1, 2, 3

X01 1, 2, 3, 0 1, 0, 3, 2

X10 2, 3, 0, 1 2, 3, 0, 1

X11 3, 0, 1, 2 3, 2, 1, 0

000 0, 1, 2, 3, 4, 5, 6, 7 0, 1, 2, 3, 4, 5, 6, 7

001 1, 2, 3, 4, 5, 6, 7, 0 1, 0, 3, 2, 5, 4, 7, 6

010 2, 3, 4, 5, 6, 7, 0, 1 2, 3, 0, 1, 6, 7, 4, 5

011 3, 4, 5, 6, 7, 0, 1, 2 3, 2, 1, 0, 7, 6, 5, 4

100 4, 5, 6, 7, 0, 1, 2, 3 4, 5, 6, 7, 0, 1, 2, 3

101 5, 6, 7, 0, 1, 2, 3, 4 5, 4, 7, 6, 1, 0, 3, 2

110 6, 7, 0, 1, 2, 3, 4, 5 6, 7, 4, 5, 2, 3, 0, 1

111 7, 0, 1, 2, 3, 4, 5, 6 7, 6, 5, 4, 3, 2, 1, 0

Sequential

(decimal)

Interleaved

(decimal)

Continuous A A, A+1, A+2... Not Valid

Note: X = 0 or 1.

Table 7. Burst Type Definition (x32 Bus Width)

Starting Addres s

Burst Length

2

4

8 Not Valid

Continuous A A, A+1, A+2... Not Valid

Note: X = 0 or 1.

(binary)

A3 A2

X0 0, 1 0, 1

X1 1, 0 1, 0

00 0, 1, 2, 3 0, 1, 2, 3

01 1, 2, 3, 0 1, 0, 3, 2

10 2, 3, 0, 1 2, 3, 0, 1

11 3, 0, 1, 2 3, 2, 1, 0

Sequential

(decimal)

Interleaved

(decimal)

22/65

M58LW128A, M58LW128B

Table 8. Burst Performance

X-Latency Y-Latency Bus Width Clock Frequency Mode

7

continuous only

8

9

7

8

9

10

11

12

13

10

11

12

13

13

15 continuous, length

1

x16, x32

2

1

x16 only

2

2(M9=0) x16, x32

33 MHz

≤

50 MHz

≤

66 MHz

≤

continuous, length

continuous only

continuous, length

continuous only

continuous, length

continuous only

continuous, length

continuous only

23/65

M58LW128A, M58LW128B

COMMAND INTERFACE

All Bus Write operations t o the me mory are in terpreted by the Command Interface. Commands

consist of one or more sequential Bus Write operations. The Commands are summarized in Table

9, Commands. Refer to Table 9 in conjunction with

the text descriptions below.

After Power-Up or a Reset operation the memory

enters Read mode.

Synchronous Read operations and Latch Controlled Bus Read operations can only be used to

read the memory array. The Electr onic Sign ature,

CFI or Status Register will be read in Asynchronous mode regardless of the Burst Control Register settings. Once the memory returns to Read

Memory Array mode the bus will resume the setting in the Burst Configuration Register automatically.

Read Memory A rray Command. The Read Memory Array command returns the memory to Read

mode. One Bus Write cycle is required to issue the

Read Memory Array command and return the

memory to Read mode. Once the command is issued the memory remains in Read mode until another command is issued. From Read mode Bus

Read operations will access the memory array.

While the Program/Erase Controller is executing a

Program, Erase, Bl ock Protect or Blocks Unprotect operation the memory will not accept the Read

Memory Array command until the operation completes.

Read Electronic S ignature C o mmand. The Read

Electronic Signature command is used to read the

Manufacturer Code, the Device Code and the

Block Protection Status. One Bus Write cycle is required to issue the Read Electronic Signature

command. Once the command is issued subsequent Bus Read operations read the Manufacturer

Code, the Device Code or the Block Protection

Status until another command is issued; see Table

10, Read Electronic Signature.

Read Query Command. The Read Query Command is used to read data from the Common Flash Interface (CFI) Memory Area. One Bus Write cycle is required to issue the Read Query Command. Once the command is issued subsequent Bus Read operations read from the Common Flash Interface Memory Area. See Appendix B, Tables 29, 30, 31, 32, 33 and 34 for details on the information contained in the Common Flash Interface (CFI) memory area.

Note that the addresses for the Common Flash Interface Memory Area are A1-A23 for the

M58LW128A and A2-A23 for the M58LW128B, regardless of the Bus Width selected.

Read Statu s Register Command. The Read Status Register command is used to read the Status

Register. One Bus Write cycle is required to issue

the Read Status Register command. Once the

command is issued subsequent Bus Read operations read the Status Register until another command is issued.

The Status Register information is present on the

output data bus (DQ1-DQ 7) when both Chip Enable and Output Enable are low, V

.

IL

See the section on the Status Register and Table

12 for details on the definitions of the Status Register bits

Clear Status Register Command. The Clear Status Register command can be used to reset bits 1,

3, 4 and 5 in the Status Register to ‘0’. One Bus

Write is required to issue the Clear Status Register

command.

The bits in the Status Register are stic ky and do

not automatically return to ‘0’ when a new Write to

Buffer and Program, Erase, Block Protect or Block

Unprotect command is issued. If any error occurs

then it is essential to clear any error bits in the Status Register by issuing the Clear Status Register

command before attempting a new Program,

Erase or Resume command.

Block Erase Command. The Block Erase command can be used to e rase a block. I t sets all of

the bits in the block to ‘1’. All previous data in the

block is lost. If the block is protected then the

Erase operation will abort, the data in the block will

not be changed and the Status Register will output

the error.

Two Bus Write operations are required to issue the

command; the second Bus Write cycle latches the

block address in the internal state machine and

starts the Program/Erase Controller. Once the

command is issued subsequent Bus Read operations read the Status Register. See the section on

the Status Register for details on the definitions of

the Status Register bits.

During the Erase operation the memory will only

accept the Read Status Register command and

the Program/Erase Su spend command. All ot her

commands will be ignored. Typical Erase times

are given in Table 11.

See Appendix C, Figure 27, Block Erase Flowchart and Pseudo Code, for a suggested flowchart

on using the Block Erase command.

Write to Buffer and Program Command. The Write to Buffer and Program comm and is used to program the memory array.

Up to 2 pages of 8 Words (or 4 Double Words) can

be loaded into the Write Buffer and program med

into the memory. The 2 pages are selected by address A4. Each Write Buffer has the same A5 -A23

addresses.

24/65

M58LW128A, M58LW128B

Four successive steps are required to issue the

command.

1. One Bus Write operation is required to set up

the Write to Buffer and Program Comm and. Issue the set up command with the selected

memory Block Address where the program operation should occur (any address in the block

where the values will be programmed can be

used). Any Bus Read operations will start to output the Status Register after the 1st cycle.

2. Us e one Bus Write operation to write the same

block address along with the value N on the

Data Inputs/Output, where N+1 is the number of

Words (x16 Bus Wi dth) or Double Words (x32

Bus Width) to be programmed.

3. Us e N+1 Bus Write operations to load the address and data for each Word or Double Word

into the Write Buffer. See the constraints on the

address combinations listed below. The addresses must have the same A5-A23.

4. Finally, use one Bus Write operation to issue the

final cycle to confirm the command and start the

Program operation.

Invalid address combinations or failing to follow

the correct sequence of Bus Write cycles will set

an error in the Status Register and abort the operation without affecting the data in the memory array. The Status Register should be cleared before

re-issuing the command.

The minimum buffer size f or a program operation

is an 8 Word (or 4 Doub le W ord) page. Inside the

page the 8 Words a re select ed by addres ses A3,

A2 and A1.

For any page, only one Write to Bu ffer and Program Command can be issued inside a previously

erased block. Any further Program operations on

that page must be preceded by an Erase operation

on the respective block.

If the block being program m ed i s prote cted an error will be set in the Status Register and the operation will abort without affecting the data in the

memory array. The block must be unprotected using the Blocks Unprotect command or by using the

Blocks Temporary Unprotect feature of the Reset/

Power-Down pin, RP

.

See Appendix C, Figure 25, Write to Buffer and

Program Flowchart and Pseudo Code, for a suggested flowchart on using the W rite to Buf fer and

Program command.

Program/Erase Suspend Command. The Program/Erase Suspend command is used to pause a

Write to Buffer and Program or Erase operation.

The command will on ly be acc ep t ed du ring a Program or an Erase operation. It can be issued at

any time during an Erase operation but will only be

accepted during a Write to Buffer and Program

command if the Program/Erase Controller is running.

One Bus Write cycle is required to i ssue the P rogram/Erase Suspend command and pause the

Program/Erase Controller. Once the command is

issued it is necessary to poll the Program/Erase

Controller Status bit (bit 7) to find out when the

Program/Erase Controller has paused; no other

commands will be accepted until the Program/

Erase Controller has paused. After the Program/

Erase Controller has paused, the memory will continue to output the Status Register until another

command is issued.

During the polling period between issuing the Program/Erase Suspend command and the Program/

Erase Controller pausing it is possible for the operation to complete. Once the Program/Erase

Controller Status bit (bit 7) i ndicates that the P rogram/Erase Controller is no longer active, the Program Suspend Status bit (bit 2) or the Erase

Suspend Status bit (bit 6) can be used to determine if the operation has completed or is suspended. For timing on the delay between issuing the

Program/Erase Suspend command and the Program/Erase Controller pausing see Table 11.

During Program/Erase Suspend the Read Memory Array, Read Status Register, Read Elect ronic

Signature, Read Query and Program/Erase Resume commands will be accepted by the Command Interface. Additionally, if the suspended

operation was Erase then the W rite to B uffer and

Program, and the Program Suspend commands

will also be ac cepted. W hen a program o peration

is completed inside a Block Erase Suspend the

Read Memory Array command m ust be issued to

reset the device in Read mode, then the Erase Resume command can be issued to complete the

whole sequence. Only the blocks not being erased

may be read or programmed correctly.

See Appendix C, Figure 26 , Program Suspend &

Resume Flowchart and Pseudo Code, and Figure

28, Erase Suspend & Resume Flowchart and

Pseudo Code, for suggested flowcharts on using

the Program/Erase Suspend command .

Program / Erase Resume Command. The Program/Erase Resume com m and c an be used to restart the Program/Erase Controller after a

Program/Erase Suspend operat ion h as paused it.

One Bus Write cycle is required to i ssue the P rogram/Erase Resume command. Once the command is issued subsequ ent Bus Read operations

read the Status Register.

Set Burst Configuration Register Command.

The Set Burst Configuration Register command is

used to write a new value t o the Burst Conf iguration Control Register which defines the burst

length, type, X and Y latencies, Synchronous/

25/65

M58LW128A, M58LW128B

Asynchronous Read mode and the valid Clock

edge configuration.

Two Bus Writ e cycles a re required to i ssue the Set

Burst Configuration Register command. Once the

command is issued the memory returns to Read

mode as if a Read Mem ory Array command had

been issued.

The value for the Burst Configuration Register is

always presented on A2-A17, regardless of the

bus width that is selected. M0 is on A2, M1 on A3,

etc.; the other address bits are ignored.

Block Protect Command. The Block Protect command is used to protec t a block and prevent Program or Erase operations from changing the data in it. Two Bus Write cycles are required to issue the Block Protect command; the second Bus Write cycle latches the block address in the internal state machine and sta rt s the Program/Erase Controller. Once the command is issued subsequent Bus Read operations read the Status Register. See the section on the Status Register for details on the definitions of the Status Register bits.

During the Block Protect operation the memory will

only accept the Read Sta tus Register command.

All other commands will be ignored. Typical Block

Protection times are given in Table 11.

The Block Protection bits are non-volatile, once

set they remain set through Reset and PowerDown/Power-Up. They are cleared by a Blocks

Unprotect command or temporary disabled by

raising the Reset/Power-Down pin to V

HH

and

holding it at that level throughout a Block Erase or

Write to Buffer and Program command.