32 Mbit (2Mb x16, Uniform Block, Burst)

FEATURES SUMMARY

■ WIDE x16 DATA BUS for HIGH BANDWIDTH

■ SUPPLY VOLTAGE

= 2.7 to 3.6V core supply voltage for Pro-

–V

DD

gram, Erase and Read operations

–V

■ SYNCHRONOUS/ASYNCHRONOUS READ

– Synchronous Burst read

– Asynchronous Random Read

– Asynchronous Address Latch Controlled

– Page Read

■ ACCESS TIME

– Synchronous Burst Read up to 56MHz

– Asynchronous Page Mode Read 90/25ns,

– Random Read 90ns, 110ns

■ PROGRAMMING TIME

– 16 Word Write Buffer

– 12µs Word effective programming time

■ 32 UNIFORM 64 KWord MEMORY BLOCKS

■ ENHANCED SECURITY

– Block Protection/ Unprotection

– Smart Protection: irreversible block locking

–V

– 128 bit Protection Register with 64 bit Unique

■ PROGRAM and ERASE SUSPEND

■ COMMON FLASH INTERFACE

■ 100,000 PROGRAM/ERASE CYCLES per

BLOCK

■ ELECTRONIC SIGNATURE

– Manufacturer Code: 0020h

– Device Code M58LW032C : 8822h

= 1.8 to VDD for I/O B u ffers

DDQ

Read

110/25ns

system

signal for Program Erase Enable

PEN

Code in OTP area

M58LW032C

3V Supp l y Fl ash Memory

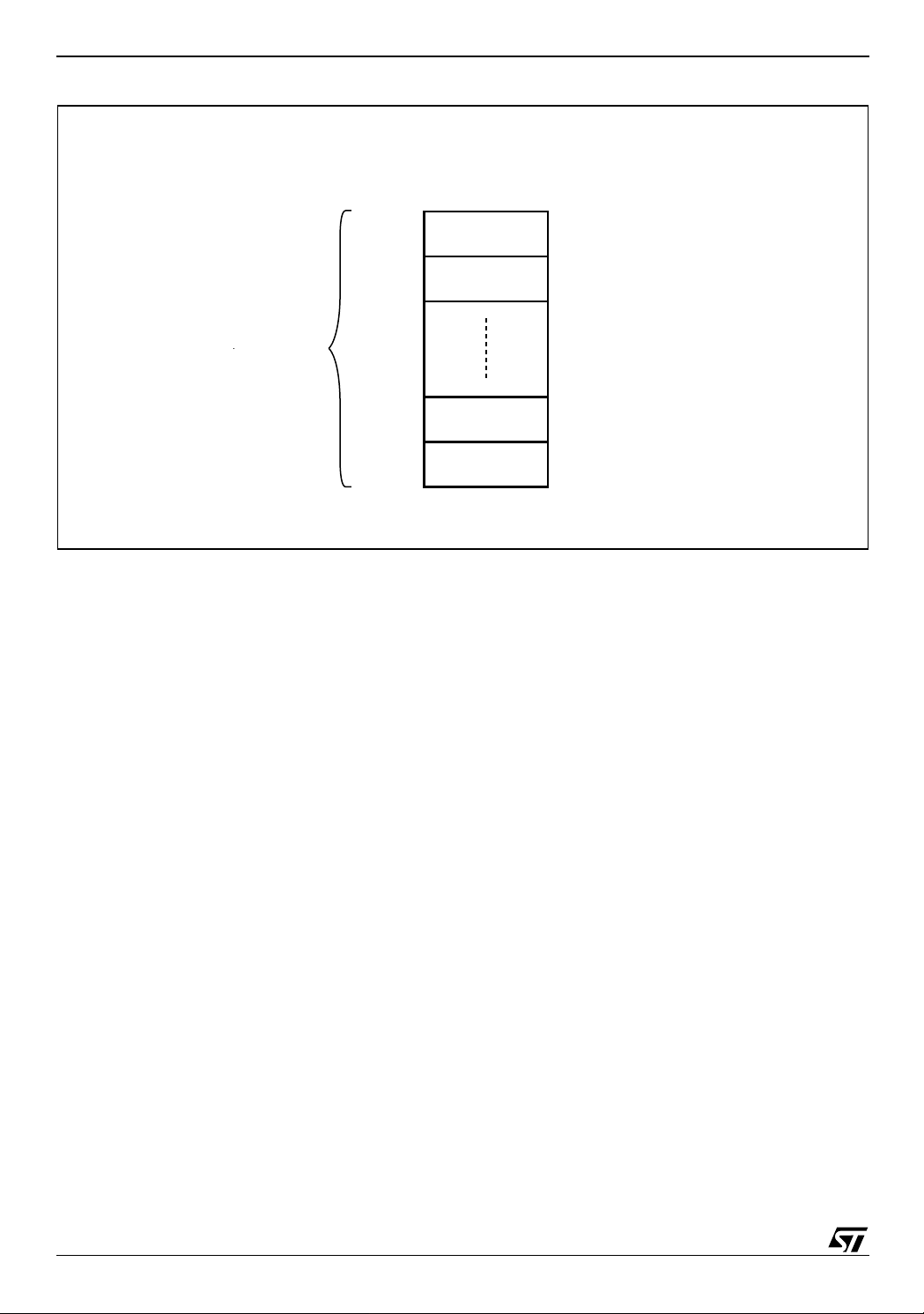

Figure 1. Packages

TSOP56 (N)

14 x 20 mm

TBGA

TBGA64 (ZA)

10 x 13 mm

1/61April 2003

M58LW032C

TABLE OF CONTENTS

SUMMARY DESCRIPTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

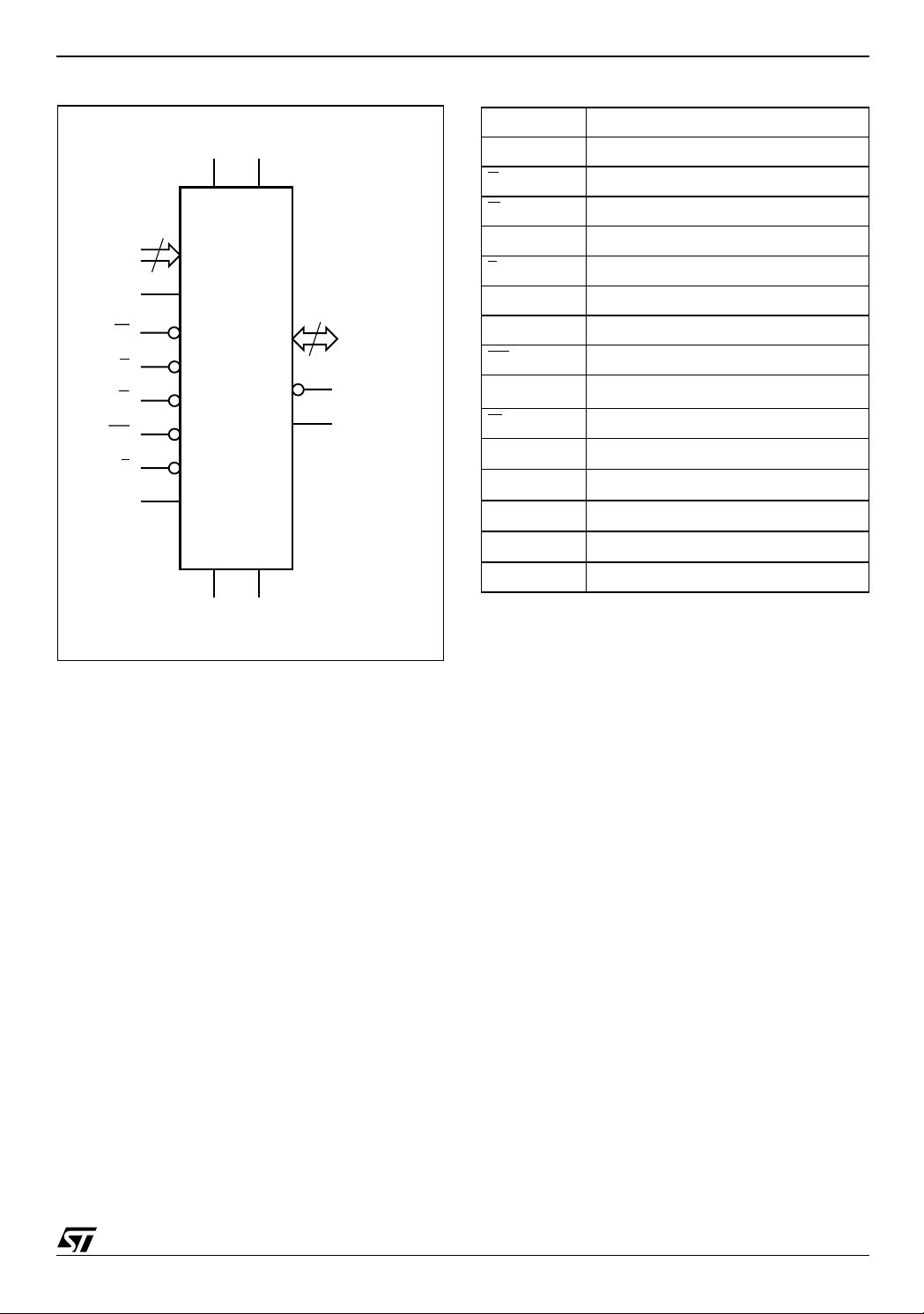

Figure 2. Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Table 1. Signal Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

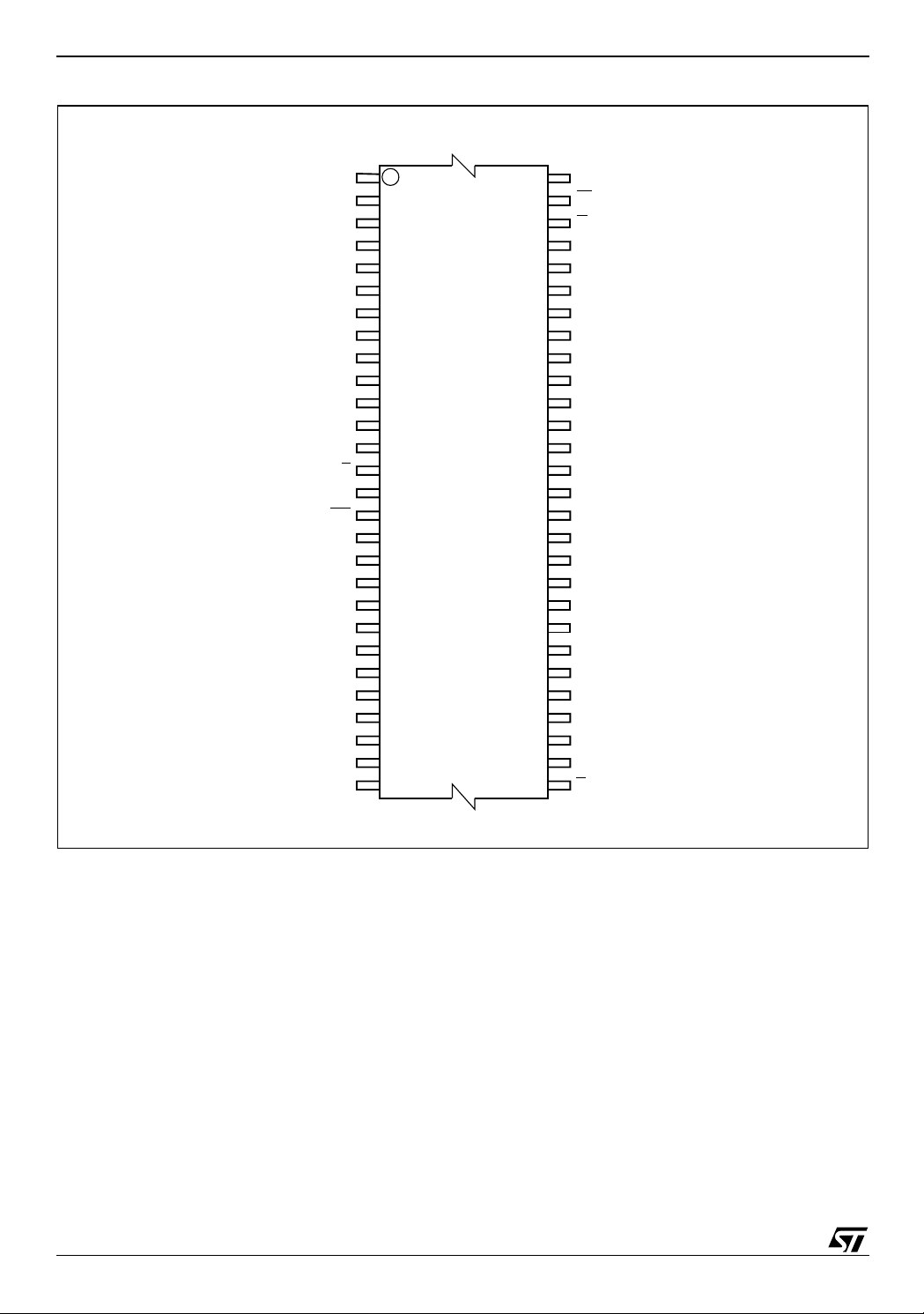

Figure 3. TSOP56 Connections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

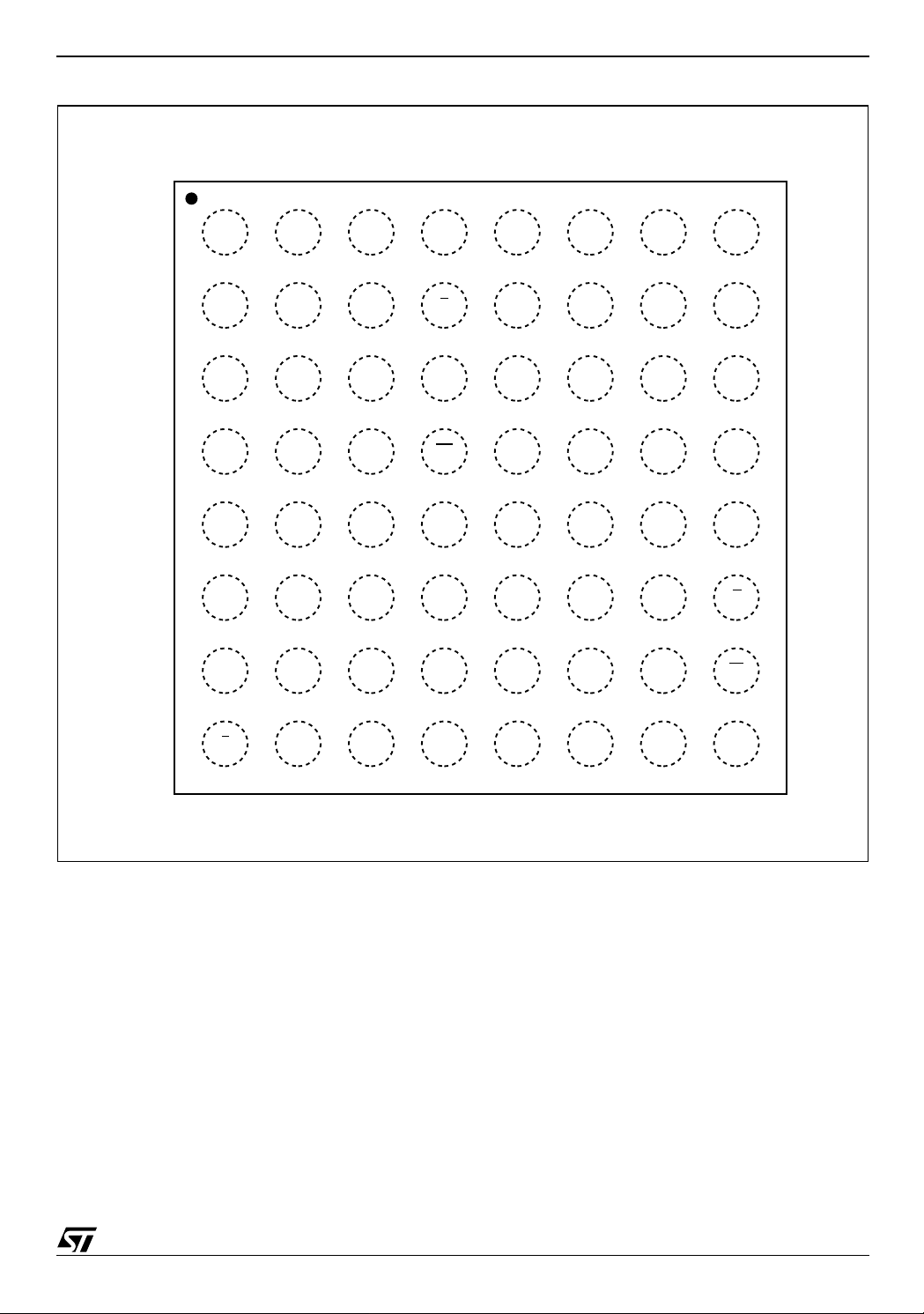

Figure 4. TBGA64 Connections (Top view through package) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 5. Block Addresses. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

SIGNAL DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Address Inputs (A1-A21). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 1

Data Inputs/Outputs (DQ0-DQ15 ). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Chip Enable (E). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Output Enable (G). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Write Enable (W). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Reset/Power-Down (RP). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Latch Enable (L). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Clock (K).. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Valid Data Ready (R). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Status/(Ready/Busy) (STS). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Program/Erase Enable (VPEN). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

V

Supply Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

DD

Supply Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

V

DDQ

V

Ground . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

SS

V

Ground. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

SSQ

BUS OPERATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Address Latch.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Bus Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Bus Write. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Output Disable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Power-Down.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Standby. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Table 2. Bus Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

READ MODES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Asynchronous Read Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

Asynchronous Latch Controlled Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Asynchronous Random Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Asynchronous Page Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Synchronous Read Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

Synchronous Burst Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Single Synchronous Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2/61

M58LW032C

CONFIGURATION REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Read Select Bit (CR15) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

X-Latency Bits (CR13-CR11). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Internal Clock Divider Bit (CR10). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Y-Latency Bit (CR9). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Valid Data Ready Bit (CR8). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 6

Burst Type Bit (CR7). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Valid Clock Edge Bit (CR6). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Burst Length Bit (CR2-CR0).. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 3. Configuration Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 4. Burst Type Definition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

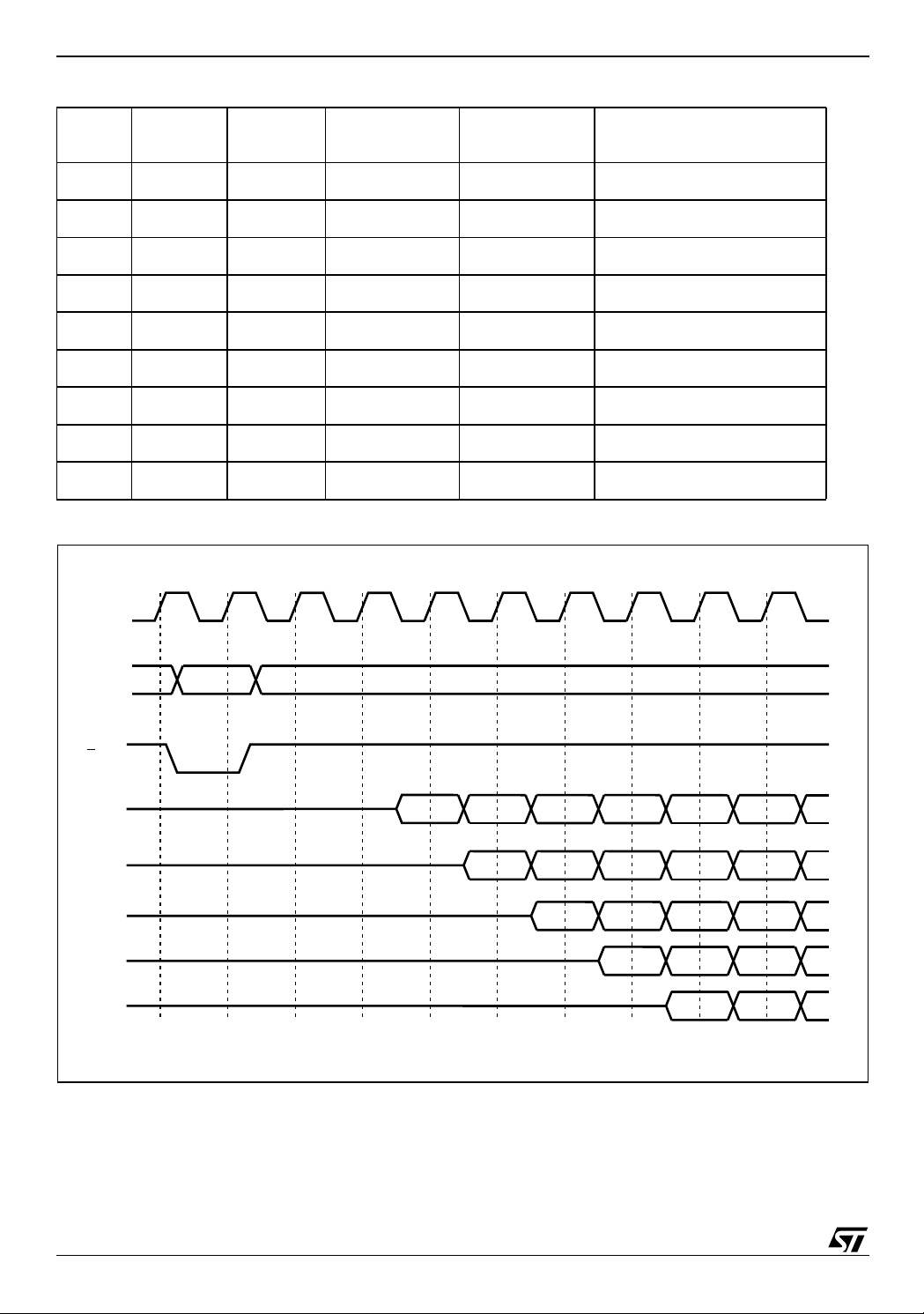

Figure 6. Burst Configuration X-1-1-1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

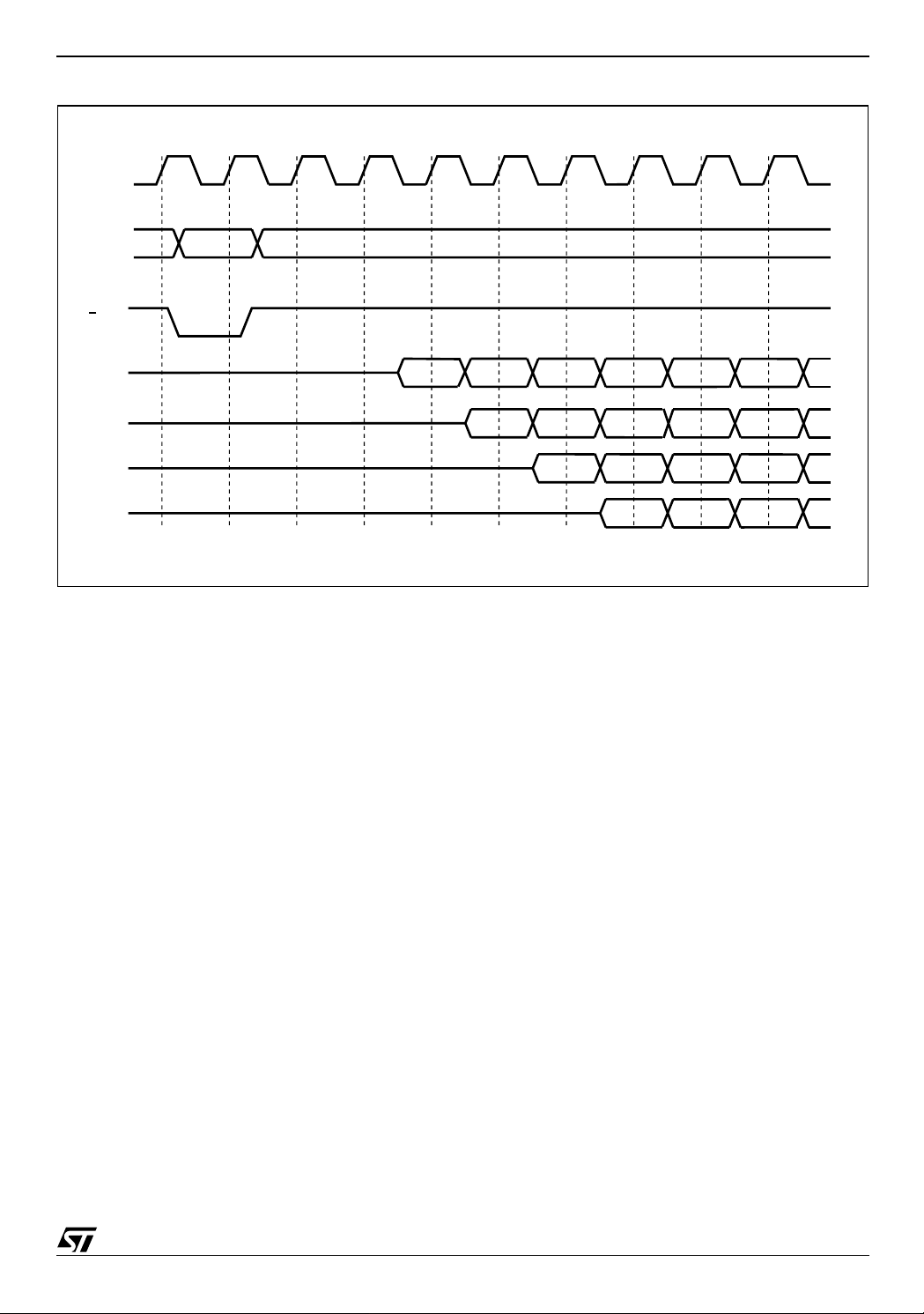

Figure 7. Burst Configuration X-2-2-2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

COMMAND INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Read Memory Array Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

Read Electronic Signature Comma nd . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Read Query Command.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Read Status Register Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

Clear Status Register Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Block Erase Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Word Program Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Write to Buffer and Program Command.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Program/Erase Suspend Comm and . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Program/Erase Resume Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

Set Configuration Register Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Block Protect Command.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Blocks Unprotect Command.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Protection Register Program Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Configure STS Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 2

Table 5. Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 6. Configuration Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 7. Read Electronic Signature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 8. Read Protection Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Figure 8. Protection Register Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 9. Program, Erase Times and Program Erase Endurance Cy cles . . . . . . . . . . . . . . . . . . . 25

STATUS REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Program/Erase Controller Status Bit (SR7). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Erase Suspend Status Bit ( SR6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Erase Status Bit (SR5) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Program Status Bit (SR4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

V

Status Bit (SR3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

PEN

Program Suspend Status Bit (SR2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

Block Protection Status Bit (SR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3/61

M58LW032C

Reserved (SR0). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 10. Status Register Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

MAXIMUM RATING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 11. Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

DC and AC PARAMETERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 12. Operating and AC Measurement Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Figure 9. AC Measurement Input Output Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Figure 10. AC Measurement Load Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 13. Capacitance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 14. DC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Figure 11. Asynchronous Bus Read AC Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 15. Asynchronous Bus Read AC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Figure 12. Asynchronous Latch Controlled Bus Read AC Waveforms . . . . . . . . . . . . . . . . . . . . . 33

Table 16. Asynchronous Latch Controlled Bus Read AC Characteristics. . . . . . . . . . . . . . . . . . . 33

Figure 13. Asynchronous Page Read AC Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Table 17. Asynchronous Page Read AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Figure 14. Asynchronous Write AC Waveform, Write Enable Controlled . . . . . . . . . . . . . . . . . . . 35

Figure 15. Asynchronous Latch Controlled Write AC Waveform, Write Enable Controlled. . . . . . 35

Table 18. Asynchronous Write and Latch Controlled Write AC Characteristics, Write Enable

Controlled.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 16. Asynchronous Write AC Waveforms, Chip Enable Controlled. . . . . . . . . . . . . . . . . . . 37

Figure 17. Asynchronous Latch Controlled Write AC Waveforms, Chip Enable Controlled . . . . . 37

Table 19. Asynchronous Write and Latch Controlled Write AC Characteristics, Chip Enable

Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Figure 18. Synchronous Burst Read AC Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 19. Synchronous Burst Read - Continuous - Valid Data Ready Output. . . . . . . . . . . . . . . 40

Table 20. Synchronous Burst Read AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Figure 20. Reset, Power-Down and Power-up AC Waveform. . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 21. Reset, Power-Down and Power-up AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 41

PACKAGE MECHANICAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Figure 21. TSOP56 - 56 lead Plastic Thin Small Outline, 14 x 20 mm, Package Outline . . . . . . . 42

Table 22. TSOP56 - 56 lead Plastic Thin Small Outline, 14 x 20 mm, Package Mechanical Data 42

Figure 22. TBGA64 10x13mm - 8x8 ball array, 1mm pitch, Package Outline . . . . . . . . . . . . . . . . 43

Table 23. TBGA64 10x13mm - 8x8 ball array, 1mm pitch, Package Mechanical Data. . . . . . . . . 43

PART NUMBERING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 24. Ordering Information Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

APPENDIX A. BLOCK ADDRESS TABLE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 25. Block Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

APPENDIX B. COMMON FLASH INTERFACE - CFI. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 26. Query Structure Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

4/61

M58LW032C

Table 27. CFI - Query Address and Data Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 28. CFI - Device Voltage and Timing Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 29. Device Geometry Definition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 30. Block Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 31. Extended Query information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

APPENDIX C. FLOW CHARTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 23. Write to Buffer and Program Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . 50

Figure 24. Program Suspend & Resume Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . 51

Figure 25. Erase Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 26. Erase Suspend & Resume Flowchart and Pseudo Code. . . . . . . . . . . . . . . . . . . . . . . 53

Figure 27. Block Protect Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Figure 28. Blocks Unprotect Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 29. Protection Register Program Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . 56

Figure 30. Command Interface and Program Erase Controller Flowchart (a). . . . . . . . . . . . . . . . 57

Figure 31. Command Interface and Program Erase Controller Flowchart (b). . . . . . . . . . . . . . . . 58

Figure 32. Command Interface and Program Erase Controller Flowchart (c). . . . . . . . . . . . . . . . 59

REVISION HISTORY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 32. Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

5/61

M58LW032C

SUMMARY DESCRIPTION

M58LW032C is a 32 M bit (2Mb x16) non-volatile

memory that can be read, erased and reprogrammed. These operations can be performed using a single low voltage (2.7V t o 3.6V) core supply.

On power-up the memory defaults to Read mode

with an asynchronous bus where it can be read in

the same way as a non-burst Flash memory.

The memory is divided into 32 blocks of 1Mbit that

can be erased i ndependently so it is poss ible to

preserve valid data while old data is erased. P rogram and Erase commands are written to the

Command Interface of the memory. An on-chip

Program/Erase Controller simplifies the process of

programming or erasing the memory by taking

care of all of the special operations that are required to update the memory contents. The end of

a Program or Erase operation can be detected and

any error conditions identified in the Status Register. The command set required to control the

memory is consistent with JEDEC standards.

The device supports synchronous burst read and

asynchronous read from all blocks of the memory

array; at power-up the device is configured for

asynchronous read. In asynchronous mode an

Address Latch input can be used to latch addresses in Latch Controlled mode. In synchronous burst

mode, data is output on each clock cycle at frequencies of up to 56MHz.

The Write Buffer allows the microprocessor to program from 1 to 16 Words in parallel, both speeding

up the programming and freeing up the microprocessor to perform other work. A Word Program

command is available to program a single Word.

Erase can be suspended in order to perform either

Read or Program in any other block and then resumed. Program ca n be s uspended to Read data

in any other block and then resum ed. Eac h block

can be programmed and erased over 100,000 cycles.

The M58LW032C has several security features to

increase data protection.

■ Block Protection, where each block can be

individually protected against p r ogram or eras e

operations. All blocks are protected during

power-up. The protection of the blocks is nonvolatile; after power-up the protection status of

each block is restored to the state when power

was last removed.

■ Program Erase Enable i nput V

, program or

PEN

erase operations are not possible when the

Program Erase Enable input V

■ Smart Protection, which allows protected blocks

PEN

is low.

to be permanently locked. This feature is not

described in the datasheet for security reasons.

Please contact STMicroelectronics for further

details.

■ 128 bit Protection Regi ster, divided in to two 64

bit segments: the f irst con tains a unique device

number written by ST, the second is user

programmable. The user programmable

segment can be protected.

The Reset/Power-Down pin is used to apply a

Hardware Reset to the memory and to set the device in power-down mode.

The device features an Auto Low Power mode. If

the bus becomes inactive during Asynchronous

Read operations, the device automatically enters

Auto Low Power mode. In this mode the power

consumption is reduced to the Auto Low Power

supply current.

The STS signal is an open drain output that can be

used to identify the Program/Erase Controller status. It can be configured in two modes: Ready/

Busy mode where a static signal indicates the status of the P/E.C, and Status mode where a pulsing

signal indicates the end of a Program or Block

Erase operation. In Status mode it can be used as

a system interrupt signal, useful for saving CPU

time.

The memory is available in TSOP56 (14 x 20 mm)

and TBGA64 (10 x 13mm, 1mm pitch) packages.

6/61

Figure 2. Logi c D iag ram Table 1. Si gn a l Nam es

A1-A21 Address inputs

V

V

DDQ

DD

DQ0-DQ15 Data Inputs/Outputs

M58LW032C

A1-A21

V

PEN

W

E

RP

E

21

16

DQ0-DQ15

M58LW032C

G

STS

R

L

K

V

V

SS

SSQ

AI06208

G

K Clock

L

R Valid Data Ready

STS Status/(Ready/Busy)

RP

V

PEN

W

V

DD

V

DDQ

V

SS

V

SSQ

NC Not Connected Internally

Chip Enable

Output Enable

Latch Enable

Reset/Power-Down

Program/Erase Enable

Write Enable

Supply Voltage

Input/Output Supply Voltage

Ground

Input/Output Ground

7/61

M58LW032C

Figure 3. TSOP56 Connections

V

NC

A21

A20

A19

A18

A17

A16

V

DD

A15

A14

A13

A12

PEN

RP

A11

A10

A9

A8

V

SS

A7

A6

A5

A4

A3

A2

A1

1

R

E

14

M58LW032C

15

28 29

56

43

42

NC

W

G

STS

DQ15

DQ7

DQ14

DQ6

V

SS

DQ13

DQ5

DQ12

DQ4

V

DDQ

V

SSQ

DQ11

DQ3

DQ10

DQ2

V

DD

DQ9

DQ1

DQ8

DQ0

NC

K

NC

L

8/61

AI06209

Figure 4. TBGA64 Connections (Top view through package)

M58LW032C

87654321

A

B RA19A2

C

D A16

E

F

G

A1

V

A4 A5

K

NC

DQ0

NC

A6 V

SS

A7A3

A8

A10 A12

A11

DQ10

DQ2

PEN

EA9

RP

DDQ

A13

A14

A15

NC NC

DQ5V

V

DD

NC

NC

NC

NC

DQ6

A20

DQ15 STSDQ9DQ8 DQ1 DQ4DQ3

NC

DQ14

NCA18

A21

A17

GDQ12DQ11

W

H

L

NC

V

DD

V

SS

DQ13

V

SSQ

DQ7

NC

AI06210b

9/61

M58LW032C

Figure 5. Block Addresses

Word (x16) Bus Width

1FFFFFh

1F0000h

1EFFFFh

1E0000h

Total of 32

1 Mbit Blocks

01FFFFh

010000h

00FFFFh

000000h

Note: Also see Appendix A, T able 25 for a full li st i ng of the Block Addresses.

1 Mbit or

64 KWords

1 Mbit or

64 KWords

1 Mbit or

64 KWords

1 Mbit or

64 KWords

AI06254

10/61

SIGNAL DESCRIPTIONS

See Figure 2, Logic Diagram and Table 11, Signal

Names, for a brief overview of the signals connected to this device.

Address Inputs (A1-A21). The Address Inputs are used to select the cells to access in the memory array during Bus Read operations either to read or to program data to. During Bus Write operations they control the commands sent to the Command Interface of the internal state m ac hine. Chip Enable and Latch Enable must be low when selecting the addresses.

The address inputs are latched on the rising edge

of Chip Enable, Write Enable or Latch Enable,

whichever occurs first in a Write operation. The

address latch is transparent when Latch Enable is

low, V

. The address is internally latched in an

IL

Erase or Program operation. Data Inputs/Outputs (DQ0-DQ15). The Data In-

puts/Outputs output the data stored at the selected

address during a Bus Read operation, or are used

to input the data during a program operation. During Bus Write operations they repres ent the commands sent to the Command Interface of the

internal state machine. When used to input data or

Write commands they are latched on the rising

edge of Write Enable or Chip Enable, whichever

occurs first.

When Chip Enable and Output Enable are both

low, V

, the data bus outputs data from the mem-

IL

ory array, the Electronic Signature, the Block Protection status, the CFI Information or the contents

of the Status Register. The data bus is high impedance when the chip is deselected, Output E nable

is high, V

low, V

or the Reset/Power-Down signal is

IH,

. When the Program/Erase Controller is

IL

active the Ready/Busy status is given on DQ7.

Chip Enable (E

). The Chip Enable, E, input acti-

vates the memory control logic, input buffers, decoders and sense amplifiers. Chip Enable, E

V

deselects the memory and reduces the power

IH

consumption to the Standby level, I

Output Enable (G

). The Output Enable, G, gates

DD1

.

, at

the outputs through the data output buffers during

a read operation. When Output Enable, G

, is at V

IH

the outputs are high impedance. Output Enable,

G

, can be used to inhibit the data ou tput during a

burst read operation.

Write Enable (W

). The Write Enable input, W,

controls writing to the Command Interface, Input

Address and Data latches. Both addresses and

data can be latched on the rising edge of Write Enable (also see Latch Enable, L

Reset/Power-Down (RP

).

). The Reset/PowerDown pin can be used to apply a Hardware Reset

to the me mory.

M58LW032C

A Hardware Reset is achieved by holding Reset/

Power-Down Low, V

Reset/Power-Down is Low, V

ter information is c leared and t he power consumption is reduced to power-down level. The device is

deselected and outputs are high impedance. If Reset/Power-Down goes low, V

Erase, a Write to Buffe r and Program or a Block

Protect/Unprotect the operation is aborted and the

data may be corrupted. In this case the Ready/

Busy pin stays low, V

t

PLPH

+ t

until the completion of the Reset/

PHRH,

Power-Down pulse.

After Reset/Power-Down goes High, V

memory will be ready for Bus Read and Bus Write

operations after t

does not fall during a reset , s ee Rea dy /Busy Ou tput section.

In an application, it is recommended to associate

Reset/Power-Down pin, RP

of the microprocessor. Otherwise, if a reset operation occurs while the memory is performing an

Erase or Program operation, the memory may output the Status Register information inst ead of being initialized to the default Asynchronous

Random Read.

Latch Enable (L

ured to latch the Address Inputs on the rising edge

of Latch Enable, L

the address is latched on the active edge of the

Clock when Latch Enable is Low, V

ing of Latch Enable, whichever occurs first. Once

latched, the addresses may change without affecting the address used by the memory. When Latch

Enable is Low, V

Clo c k (K). The Clock, K, is used to synchronize the memory with the external bus during Synchronous Bus Read operations. The Clock can be configured to have an active rising or falling edge. Bus signals are latched on the active edge of the Clock during synchronous bus operations. In Synchronous Burst Read m ode the address is latched on the first active clock edge when Latch Enable is low, VIL, or on the rising edge of Latch Enable, whichever occurs first.

During asynchronous bus operations the Clock is

not used.

Valid Data Ready (R). The Valid Data Ready output, R, is an open drain output that can be used to identify if the memory is ready to output data or not. The Valid Data Ready output is only active during Synchronous Burst Read operat ions when the Burst Length is set to Continuous. The Valid Data Ready output can be configured to be active on the clock edge of the invalid data read cycle or one cycle before. Valid Data Ready Low, V

, for at least t

IL

, for a ma ximum timin g of

IL

. Note that Ready/Busy

PHQV

, the Status Regis-

IL

,during a Block

IL

PLPH

. When

, the

IH

, with the reset sig nal

). The Bus Interface is config-

. In synchronous bus operations

or on the ris-

IL

, the latch is transparent.

IL

, in-

OL

11/61

M58LW032C

dicates that the data is not, or will not be valid. Valid Data Ready in a high-impedance state indicates

that valid data is or will be available.

Unless Synchronous Burst Read has been selected, Valid Data Ready is high-impedance. It may be

tied to other components with the same Valid Data

Ready signal to create a unique System Ready

signal.

The Valid Data Ready, R, output has an internal

pull-up resistor of approximately 1 MΩ powered

from V

, designers should use an external pull-

DDQ

up resistor of the correct value to meet the external

timing requirements for Valid Data Ready rising.

Refer to Figure 19.

Status/(Ready/Busy) (STS). The STS signal is

an open drain output t hat can be used to id entify

the Program/Erase Controller status. It can be

configured in two modes:

■ Ready/Busy - the pin is Low, V

, during

OL

Program and Erase operations and high

impedance when the memory is ready for any

Read, Program or Erase operation.

■ Status - the pin gives a pulsing signal to indicate

the end of a Program or Block Erase operation.

After power-up or reset the STS pin i s configured

in Ready/Busy mode. T he pin can be co nfigured

for Status mode using the Configure STS command.

When the Program/Erase Controller is idle, or suspended, STS can float High through a pul l-up resistor. The use of an open-drain output allows the

STS pins from several memo ries to be c onnect ed

to a single pull-up resistor (a Low will indicate that

one, or more, of the memories is busy).

STS is not Low during a reset unless the reset was

applied when the Program/Erase controller was

active. Ready/Busy can rise before Reset/PowerDown rises.

Program/Erase Enable (V

Erase Enable input, V

PEN,

). The Program/

PEN

is used to protect all

blocks, preventing Program and Erase operations

from affecting their data.

Program/Erase Enable must be kept High during

all Program/Erase Controller operations, otherwise the operations is not guaranteed to suc ceed

and data may become corrupt.

V

Supply Voltage. VDD provides the power

DD

supply to the internal core of the memory device.

It is the main power supply for all operations

(Read, Program and Erase).

Supply Voltage. V

V

DDQ

provides the power

DDQ

supply to the I/O pins and enables all Outputs to

. V

be powered independently from V

tied to V

or can use a separate supply.

DD

DD

DDQ

can be

It is recommended to power-up and power-down

V

DD

and V

together to avoid any condition that

DDQ

would result in data corruption.

Ground. Ground, V

V

SS

is the reference for

SS,

the core power supply. It must be connected to the

system ground.

V

Ground. V

SSQ

the input/output circuitry driven by V

ground is the reference for

SSQ

DDQ

. V

SSQ

must be connected to VSS.

Note: Each device in a system should have

V

DD

and V

decoupled with a 0.1µF ceramic

DDQ

capacitor close to the pin (high frequency, inherently low inductance ca pacitors should b e

as close as possible to the package). See Figure 10, AC Measurement Load Circuit.

12/61

BUS OPERATIONS

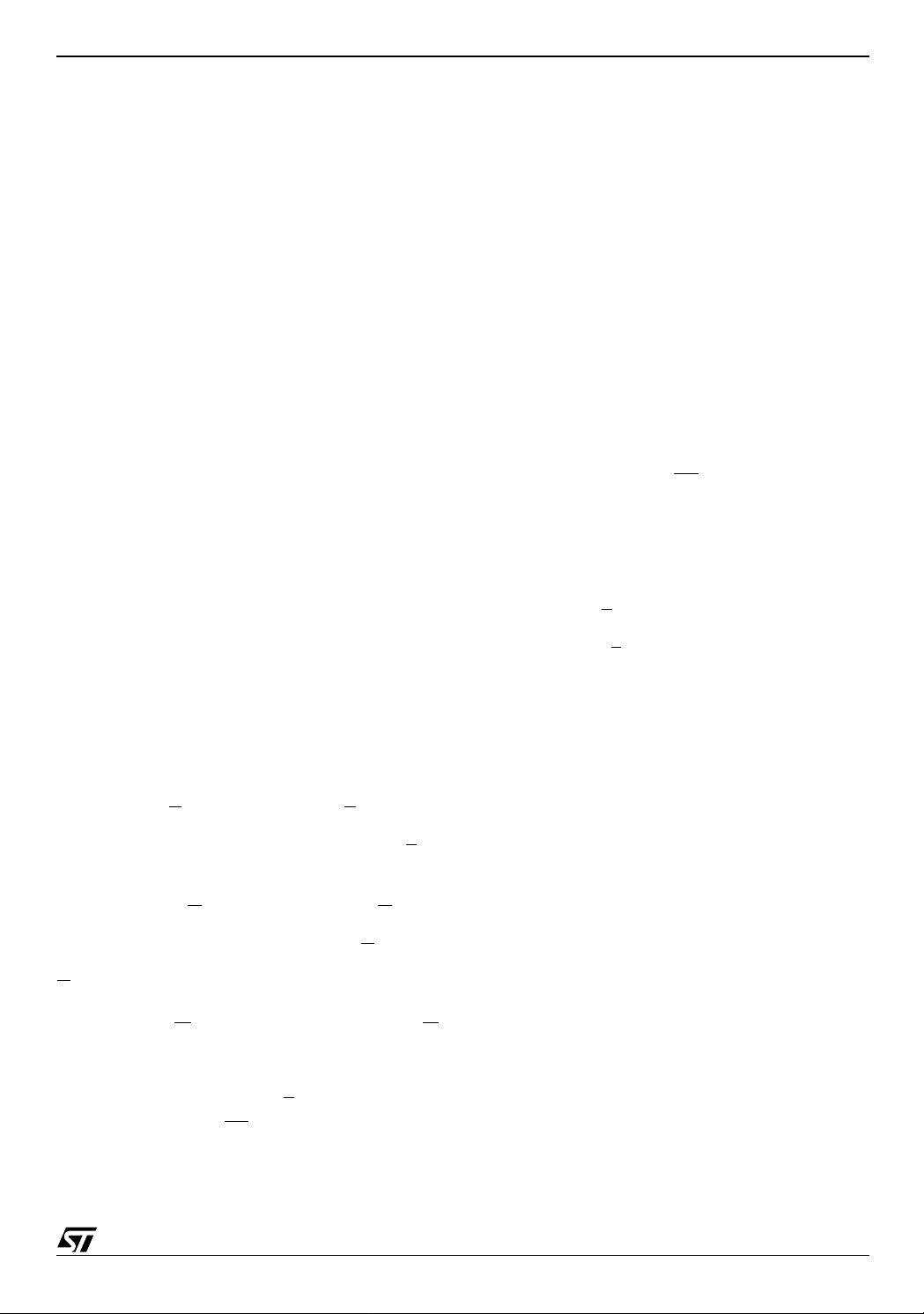

There are six standard bus operations that control

the device. These are Address Latch, B us Read,

Bus Write, Output Disable, Power-Down and

Standby. See Table 2, Bus Operations, for a summary.

Typically glitches of less than 5ns on Chip Enable

or Write Enable are ignored by the memory and do

not affect Bus Write operations.

Address Latch. Address latch operations input valid addresses.

A valid bus operation i nvolves set ting the des ired

address on the Address Inputs, setting Chip Enable and Latch Enable Low, V

Enable High, V

; the address is latched on the ris-

IH

and keeping Write

IL

ing edge of Address Latch. Bus Read. Bus Read operations are used to out-

put the contents of the Memory Array, the Electronic Signature, the Status Register, the Common

Flash Interface and the Block Protection Status.

A valid bus operation i nvolves set ting the des ired

address on the Address Inputs, applying a Low

signal, V

Latch Enable and keeping Write Enable High, V

, to Chip Enable, Output Enable and

IL

IH

The data read depends on the previous command

written to the memory (see Command Interface

section). See Figures 11, 12, 13, 18 and 19 Read

AC Waveforms, and Tables 15, 16, 17 and 20

Read AC Characteristics, for details of when the

output becomes valid.

Bus Write. Bus Write operations write Commands to the memory or latch addresses and input data to be programmed.

M58LW032C

A valid Bus Write operation begin s by setting the

desired address on the Address Inputs and setting

Latch Enable Low, V

latched by the Command Interface on the rising

edge of Chip Enable or Write Enable, whichever

occurs first. The Data Inputs/Outputs are latched

by the Command Interface on the rising edge of

Chip Enable or Write Enable, whichever occurs

first. Output Enable must remain High, V

the Bus Wr ite operation.

See Figures 14, 15, 16 and 17, Write AC Waveforms, and Tables 18 and 19, Write AC Characteristics, for details of the timing requirements.

Output Disa bl e . The The Data Inputs/Outputs are high impedance when the Out put Enable i s at

.

V

IH

Power-Down. The memory is in Power-Down mode when Reset/Power-Down, RP power consumption is reduced to the Power-Down level, I

, and the out puts are high impedance,

DD2

independent of Chip Enable, Output Enable or

Write Enable.

Standby. Stan dby disables most of the inte rnal

.

circuitry, allowing a substantial reduction of the

current consumption. The memory is in standby

when Chip Enable is at V

tion is reduced to the standby level I

outputs are set to high impedance, independently

from the Output Enable or Write Enable inputs.

If Chip Enable switches to V

erase operation, the d ev ice en ters Standby mode

when finished.

. The Address Inputs are

IL

, is Low. The

. The power consump-

IH

during a program or

IH

DD1

, during

IH

and the

Table 2. Bus Operations

Operation E G W RP L A1-A21 DQ0-DQ15

Address Latch

Bus Read

Bus Write

Output Disable

Power-Down X X X

Standby

Note: 1. X = Don’t Care VIL or VIH.

2. Depends on G

V

IL

V

IL

V

IL

V

IL

V

IH

X

V

IL

V

IH

V

IH

XX

V

IH

V

IH

V

IL

V

IH

V

IH

V

IH

V

IH

V

IH

V

IL

V

IH

V

IL

V

IL

V

IL

X X High Z

X X High Z

X X High Z

Address

Address Data Output

Address Data Input

Data Output or Hi-Z

(2)

13/61

M58LW032C

READ MODES

Read operations can be performed in two different

ways depending on the settings in the Configura-

tion Register. If the clock signal is ‘d on’t care’ for

the data output, the read operation is asynchronous; if the data output is synchronized with clock,

the read operation is synchronous.

The read mode and f ormat of the data output are

determined by the Configuration Register. (See

Configuration Register section for details).

On Power-up or after a Hardware Reset the memory defaults to Asynchronous Read mode.

Asynchronous Read Modes

In Asynchronous Read operations the clock signal

is ‘don’t care’. The device outpu ts the dat a corresponding to the address latched, that is the mem ory array, Status Register, Common Flash

Interface, Electronic Signature or Block Protection

Status depending on the comma nd issued. CR15

in the Configuration Register must be set to ‘1’ for

asynchronous operations.

During Asynchronous Read operations, if the bus

is inactive for a time equivalent to t

vice automatically enters Auto Low Power mode.

In this mode the internal supply current is reduced

to the Auto Low Power supply current, I

Data Inputs/Outputs will still output data if a Bus

Read operation is in progress.

Automatic Low Power is only available in Asynchronous Read modes.

Asynchronous Read operations can be performed

in three different ways, Asynchronous Latch Controlled Read, Asynchronous Random Read and

Asynchronous Page Read.

Asynchronous Latch Controlled Read.

In Asynchronous Latch Controlled Read operations read the address is latched in the me mory

before the value is output on the data bus, allowing

the address to change during the cycle without affecting the address that the memory uses.

A valid bus operation i nvolves set ting the des ired

address on the Address Inputs, setting Chip Enable and Latch Enable Low, V

Enable High, V

; the address is latched on the ris-

IH

and keeping Write

IL

ing edge of Address L atch. Once latched, the Address Inputs can change. Set Output Enable Low,

, to read the data on the Data Inputs/Outputs;

V

IL

see Figure 12, Asynchronous Latch Controlled

Read AC Waveforms and Table 16, Asynchronous Latch Controlled Read AC Characteristics for

details on when the output becomes valid.

See Figures 12, Asynchronous Latch Controlled

Read AC Waveforms, and Table 16, Asynchronous Latch Controlled Read AC Characteristics,

for details.

AVQV

, the de-

. The

DD5

Asynchro nous Random R ead. As th e Lat ch En able input is transparent when set Low, V

, Asyn-

IL

chronous Random Read operations can be

performed by holding Latch Enable Low, V

throughout the bus operation.

See Figures 11, Asynchronous Random Read AC

Waveforms, and Table 15, Asynchronous Random Read AC Characteristics, for details.

Asynchro nous Page Read . In Asynchronous

Page Read mode a Page of data is internally read

and stored in a Page Buffer. Each memory page is

4 Words and has th e same A3-A22, only A 1 and

A2 may change.

The first read operation within the Page has the

normal access time (t

), subsequent reads

AVQV

within the same Page have much sho rter access

times (t

). If the Page changes then the nor-

AVQV1

mal, longer timings apply again.

See Figures 13, Asynchronous Page Read AC

Waveforms, and Table 17, Asynchronous Page

Read AC Characteristics, for details.

Synchronous Read Mo de s

In Synchronous Read mode the data output is synchronized with the clock. CR15 in the Configuration Register must be set to ‘0’ for synchronous

operations.

Synchronous Burst Read. In Synchronous

Burst Read mode the data is output in bursts synchronized with the clock. It is possible to perform

burst reads across bank boundaries.

Synchronous Burst Read mode can onl y be used

to read the memory array. For other read operations, such as Read Status Register, Read CFI,

Read Electronic Signature and Block Protection

Status, Single Synchronous Read or Asynchronous Read must be used.

In Synchronous Burst Read mode the flow o f the

data output depends on param eters that are configured in the Configuration Register.

A valid Synchronous Burst Read operation begins

when the address is set on the Address Inputs,

Write Enable is High, V

Latch Enable are Low, V

, and Chip Enable and

IH

, during the active edge

IL

of the Clock. The address is latched on the first active clock edge when Latch Enable i s low, or on

the rising edge of Latch Enable, whichever occurs

first. The data becomes available for output after

the X-latency specified in the Burst Control Register has expired. The output buffers are activated

by setting Output Enable Low, V

. See Figures 6

IL

and 7 for examples o f Synchronous Burst Read

operations.

The number of Words to be out put during a Synchronous Burst Read operation can be configured

as 4 Words, 8 Words or Continuous (Burst Length

IL

14/61

M58LW032C

bits CR2-CR0). In Synchronous Continuous Burst

Read mode one Burst Read operation can access

the entire memory sequ entially. If the starting address is not associated with a page (4 Word)

boundary the Valid Data Ready, R, output goes

Low, V

, to indicate that the data will not be ready

IL

in time and additional wait-states are required. The

Valid Data Ready output timing (bit CR8) can be

changed in the Configuration Register.

The order of the data output can be modified

through the Burst Type bit in the Configuration

Register. The burst sequence can be sequential or

interleaved.

See Table 20, Synchronous Read AC Characteristics and Figure 18 a nd 19, Synchronous Burst

Read AC Waveform for details.

Single Synchronous Read. Single Synchronous Read operations are similar to S ync hronous

Burst Read operations except that only the first

data output after the X latency is valid. Single Synchronous Reads are used to read the Status Register, CFI, Electronic Signature and Block

Protection Status.

15/61

M58LW032C

CONFIGURATION REGISTER

The Configuration Register is used to configure

the type of bus access that the memory will perform. The Configuration Register bits are described in Table 3. They specify the selection of

the burst length, burst type, burst X and Y latencies and the Read operation. See figures 6 and 7

for examples of Synchronous Burst Read configurations.

The Configuration Register is set through the

Command Interface and will retain its information

until it is re-configured, the device is reset, or the

device goes into Reset/Power-Down mode. The

Configuration Register is read using the Read

Electronic Signature Command at address 05h.

Read Select Bit (CR15). The Read Select bit,

CR15, is used to switch between asynchronous

and synchronous Bus Read operations. When the

Read Select bit is set to ’1’, Bus Read operations

are asynchronous; when the Read Select but is

set to ’0’, Bus Read operations are synchronous.

On reset or power-up the Read Select bit is set to

’1’ for asynchronous access.

X-Latency Bits (CR13-CR11). The X-Latency bits are used during Synchronous Bus Read operations to set the number of clock cy cles between the address being latched and the first data becoming available. For correct operation the X-Latency bits can only assume the values in Table 3, Configuration Register.

Internal Clock Divider Bit (CR10). The Internal

Clock Divider Bit is used to divide the internal clock

by two. When CR10 is set to ‘1’ the internal clock

is divided by two, which effectively means that the

X and Y-Latency values are multiplied by two, that

is the number of clock cycles between the address

being latched and the first data becoming available will be twice the value set in CR13-CR11, and

the number of clock cycles between consecutive

reads will be twice the value set in CR9. For example 8-1-1-1 will be come 16-2-2-2. When C R10 is

set to ‘0’ the internal clock runs normally and the X

and Y-Latency values are those set in CR13-CR11

and CR9.

Y-Latency Bit (CR9). The Y-Latency bit is used

during Synchronous Bus Read operations to set

the number of clock cycles between consecutive

reads. The Y-Latency value depends on both the

X-Latency value and the setting in CR9.

When the Y-Latency is 1 the data changes each

clock cycle; when the Y-Latency is 2 the data

changes every seco nd clock cycle. See Tab le 3,

Configuration Register for valid combinations of

the Y-Latency, the X-Latency and the Clock frequency.

Valid Data Ready Bit (CR8). The Valid Data Ready bit controls the timing of the Valid Data Ready output pin, R. When the Valid Data Ready bit is ’0’ the Valid Data Ready output pin is driven Low for the active clock edge when invalid data is output on the bus. When the Valid Data Ready bit is ’1’ the Valid Data Ready output pin is driven Low one clock cycle prior to invalid data being output on the bus.

Burst Type Bit (CR7). The Burst Type bit is used to configure the sequence of addresses read as sequential or interleaved. When the Burst Type bit is ’0’ the memory outputs from interleaved addresses; when the Burst Type bit is ’1’ the memory outputs from sequential addresses. See Tables 4, Burst Type Definition, for the sequence of addresses output from a given starting address in each mode.

Valid Clock Edge Bit (CR6). The Valid Clock Edge bit, CR6, is used to configure the active edge of the Clock, K, during Synchronous Burst Read operations. When the Valid Clock Edge bit is ’0’ the falling edge of the Clock is the active edge; when the Valid Clock Edge bit is ’1’ the rising edge of the Clock is active.

Burst Length Bit (CR2-CR0). The Burst Length bits set the maximum number of Words that can be output during a Synchronous Burst Read operation.

Table 3, Configuration Register gives the valid

combinations of the Burst Length bits that the

memory accepts; Tables 4, Burst Type Definition,

give the sequence of addresses output from a given starting address for each length.

CR5 CR4 and CR3 are reserved for future use.

16/61

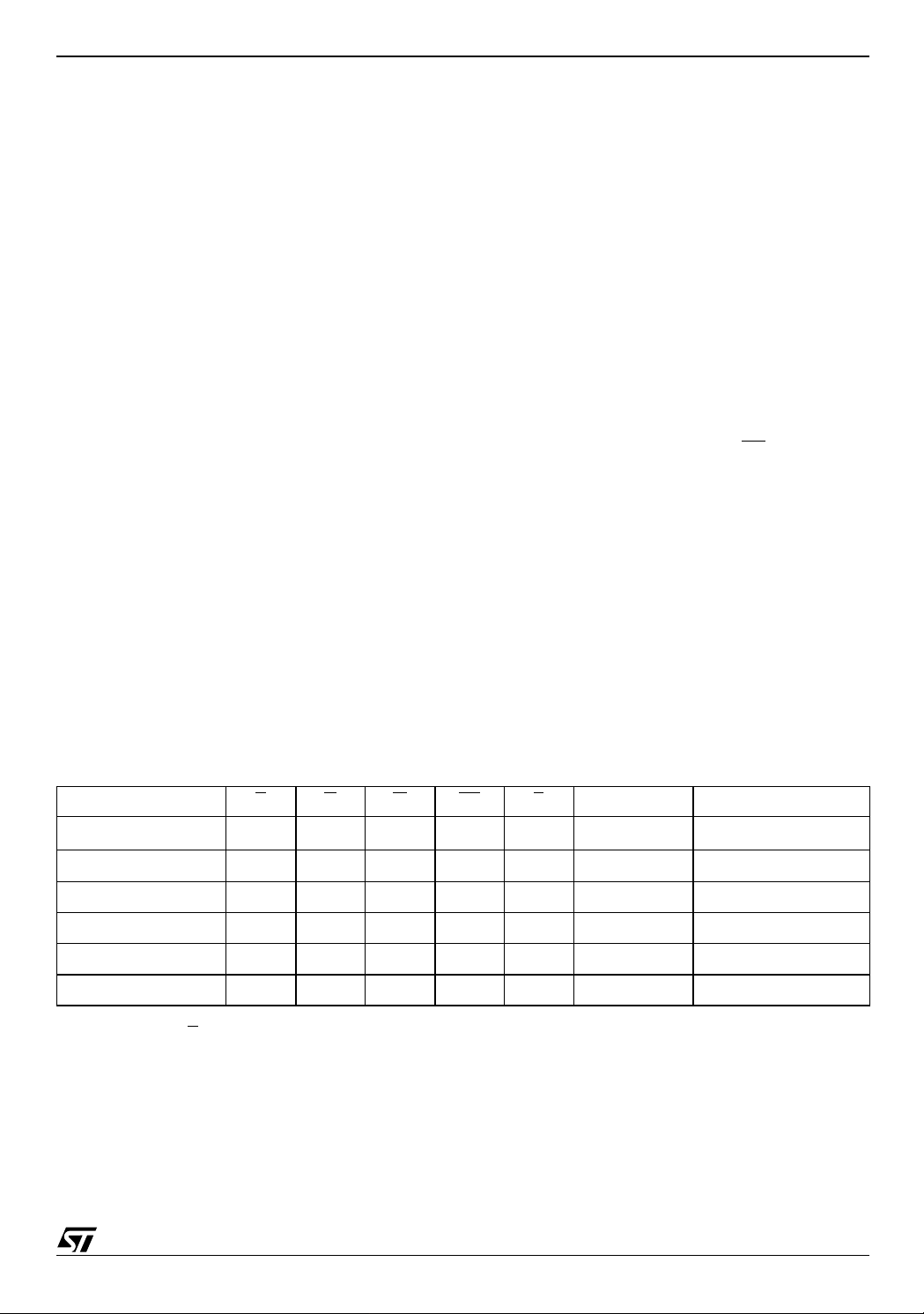

Table 3. Configuration Register

Address

Bit

Mnemonic Bit Name

16 CR15 Read Select 1

15 CR14 Reserved

Reset

Value

Value Description

0 Synchronous Burst Read

1 Asynchronous Bus Read (default at power-up)

001 Reserved

010

X-Latency = 4, 4-1-1-1 (use only with Y-Latency = 1)

M58LW032C

(1)

14

to

12

CR13-CR11

X-Latency

(2)

XXX

011

100

101

X-Latency = 5, 5-1-1-1, 5-2-2-2

X-Latency = 6, 6-1-1-1, 6-2-2-2

X-Latency = 7, 7-1-1-1, 7-2-2-2

110 X-Latency = 8, 8-1-1-1, 8-2-2-2

X and Y-Latencies remains as set in CR13-CR11 and

11 CR10

Internal

Clock Divider

X

0

CR9

1 Divides internal clock, X and Y-Latencies multiplied by 2

10 CR9

9CR8

Y-Latency

Valid Data

Ready

(3)

X

X

0 Y-Latency = 1

1 Y-Latency = 2

0 R valid Low during valid Clock edge

1 R valid Low one cycle before valid Clock edge

0 Interleaved

8 CR7 Burst Type X

1 Sequential

7CR6

Valid Clock

Edge

X

0 Falling Clock edge

1 Rising Clock edge

6 to 4 CR5-CR3 Reserved

3

to

CR2-CR0 Burst Length XXX

1

Note: 1. 4 - 2 - 2 - 2 (represents X-Y-Y-Y) is not allowed.

2. X latencies can be calculated as: (t

is the clock period).

3. Y latencies can be calculated as: t

4. t

SYSTEM MARGIN

is the time m argin requir ed for the calculation.

AVQV

KHQV

– t

LLKH

+ t

SYSTEM MARGIN

001 4 Words

010 8 Words

111 Continuous

+ t

) + t

QVKH

SYSTEM MARGIN

+ t

QVKH

< Y t

K.

< (X - 1) t

is an integer number from 4 to 8 and t

K. (X

K

17/61

M58LW032C

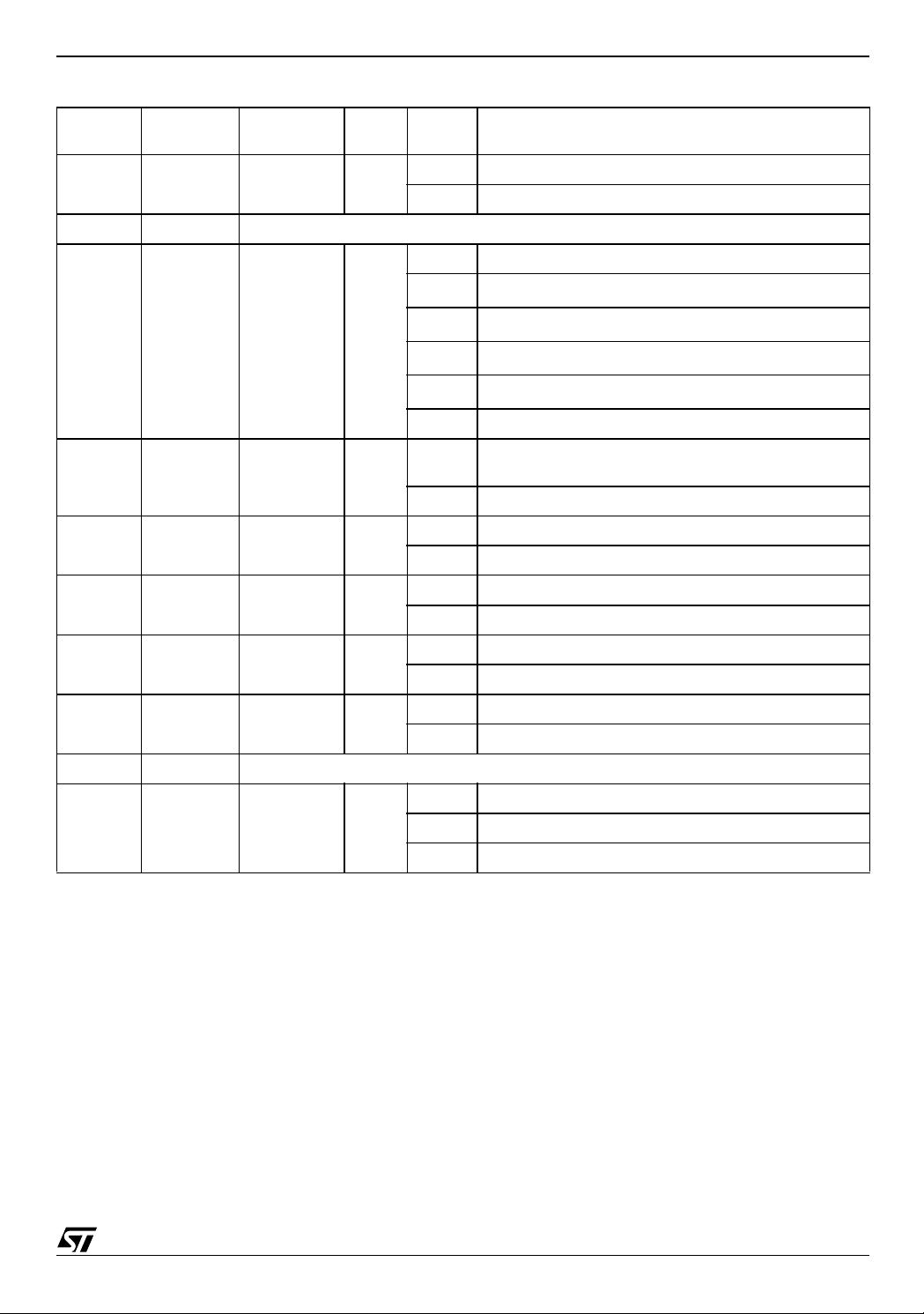

Tabl e 4. Burst Type Definit ion

Starting

Addressx4Sequentialx4Interleaved

x8

Sequential

x8

Interleaved

Continuous

0 0-1-2-3 0-1-2-3 0-1-2-3-4-5-6-7 0-1-2-3-4-5-6-7 0-1-2-3-4-5-6-7-8-9-10..

1 1-2-3-0 1-0-3-2 1-2-3-4-5-6-7-0 1-0-3-2-5-4-7-6 1-2-3-4-5-6-7-8-9-10-11..

2 2-3-0-1 2-3-0-1 2-3-4-5-6-7-0-1 2-3-0-1-6-7-4-5 2-3-4-5-6-7-8-9-10-11-12..

3 3-0-1-2 3-2-1-0 3-4-5-6-7-0-1-2 3-2-1-0-7-6-5-4 3-4-5-6-7-8-9-10-11-12-13..

4 – – 4-5-6-7-0-1-2-3 4-5-6-7-0-1-2-3 4-5-6-7-8-9-10-11-2-13-14..

5 – – 5-6-7-0-1-2-3-4 5-4-7-6-1-0-3-2 5-6-7-8-9-10-11-12-13-14..

6 – – 6-7-0-1-2-3-4-5 6-7-4-5-2-3-0-1 6-7-8-9-10-11-12-13-14-15..

7 – – 7-0-1-2-3-4-5-6 7-6-5-4-3-2-1-0 7-8-9-10-11-12-13-14-15-16..

8 – – – – 8-9-10-11-12-13-14-15-16-17..

Figure 6. Burst Configuration X-1-1-1

0123456789

K

ADD VALID

L

DQ

DQ

DQ

DQ

DQ

4-1-1-1

5-1-1-1

6-1-1-1

7-1-1-1

8-1-1-1

VALID

VALID

VALID

VALIDVALIDVALIDVALID

VALIDVALIDVALID

VALID

VALIDVALIDVALIDVALID

VALID

VALID

VALID

VALIDVALID

AI05512

18/61

Figure 7. Burst Configuration X-2-2-2

0123456789

K

M58LW032C

ADD

L

DQ

DQ

DQ

DQ

5-2-2-2

6-2-2-2

7-2-2-2

8-2-2-2

VALID

NV

NV=NOT VALID

VALID

NV

NV

VALID

NV

VALID

NV

VALID

NV

VALID

NV

VALID

VALID

NV

VALID

NVNV

AI05513

19/61

Loading...

Loading...