2 Mbit (256Kb x8, Boot Block) Single Supply Flash Memory

5V ± 10% SUPPLYVOLTAGEfor PROGRAM,

ERASEand READOPERATIONS

FASTACCESSTIME: 70ns

FASTPROGRAMMING TIME: 10µs typical

PROGRAM/ERASECONTROLLER(P/E.C.)

– ProgramByte-by-Byte

– Status Register bits

MEMORYBLOCKS

– Boot Block (Topor Bottomlocation)

– Parameterand Mainblocks

BLOCK, MULTI-BLOCKand CHIP ERASE

MULTI-BLOCKPROTECTION/TEMPORARY

UNPROTECTIONMODES

ERASESUSPEND and RESUMEMODES

– Read and Program anotherBlock during

Erase Suspend

LOW POWER CONSUMPTION

– Stand-byand Automatic Stand-by

100,000 PROGRAM/ERASECYCLESper

BLOCK

20 YEARSDATARETENTION

– Defectivitybelow 1ppm/year

ELECTRONICSIGNATURE

– ManufacturerCode: 20h

– Device Code, M29F002T:B0h

– Device Code, M29F002NT:B0h

– Device Code, M29F002B:34h

DESCRIPTION

The M29F002 is a non-volatile memory that may

beerasedelectricallyat theblock or chipleveland

programmed in-system on a Byte-by-Byte basis

usingonlyasingle5VV

Eraseoperations thenecessaryhigh voltages are

generatedinternally. The device can also be programmedin standardprogrammers.

Thearraymatrixorganisationallowseach blockto

be erased and reprogrammed without affecting

otherblocks. Blockscan be protectedagainst programing and erase on programming equipment,

and temporarily unprotected to make changes in

the application. Each block can be programmed

and erased over 100,000 cycles.

supply.ForProgramand

CC

M29F002T, M29F002NT

M29F002B

32

1

PDIP32 (P)

TSOP32 (N)

8 x 20mm

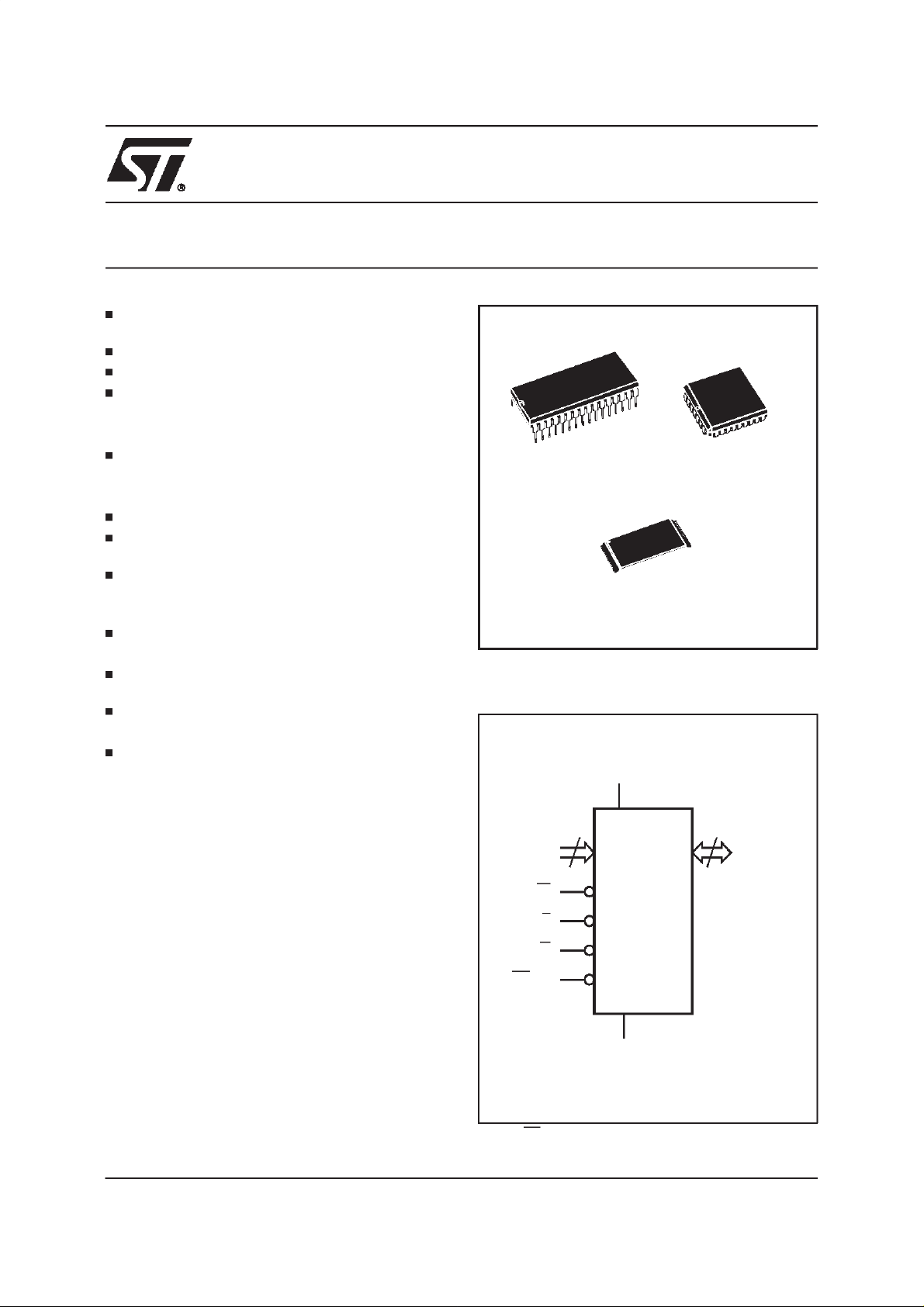

Figure1. LogicDiagram

V

CC

18

A0-A17

W

E

G

(*) RPNC

Note: * RPNC function is not available for theM29F002NT

M29F002T

M29F002B

M29F002NT

V

SS

PLCC32 (K)

8

DQ0-DQ7

AI02078C

July 1998 1/29

M29F002T, M29F002NT, M29F002B

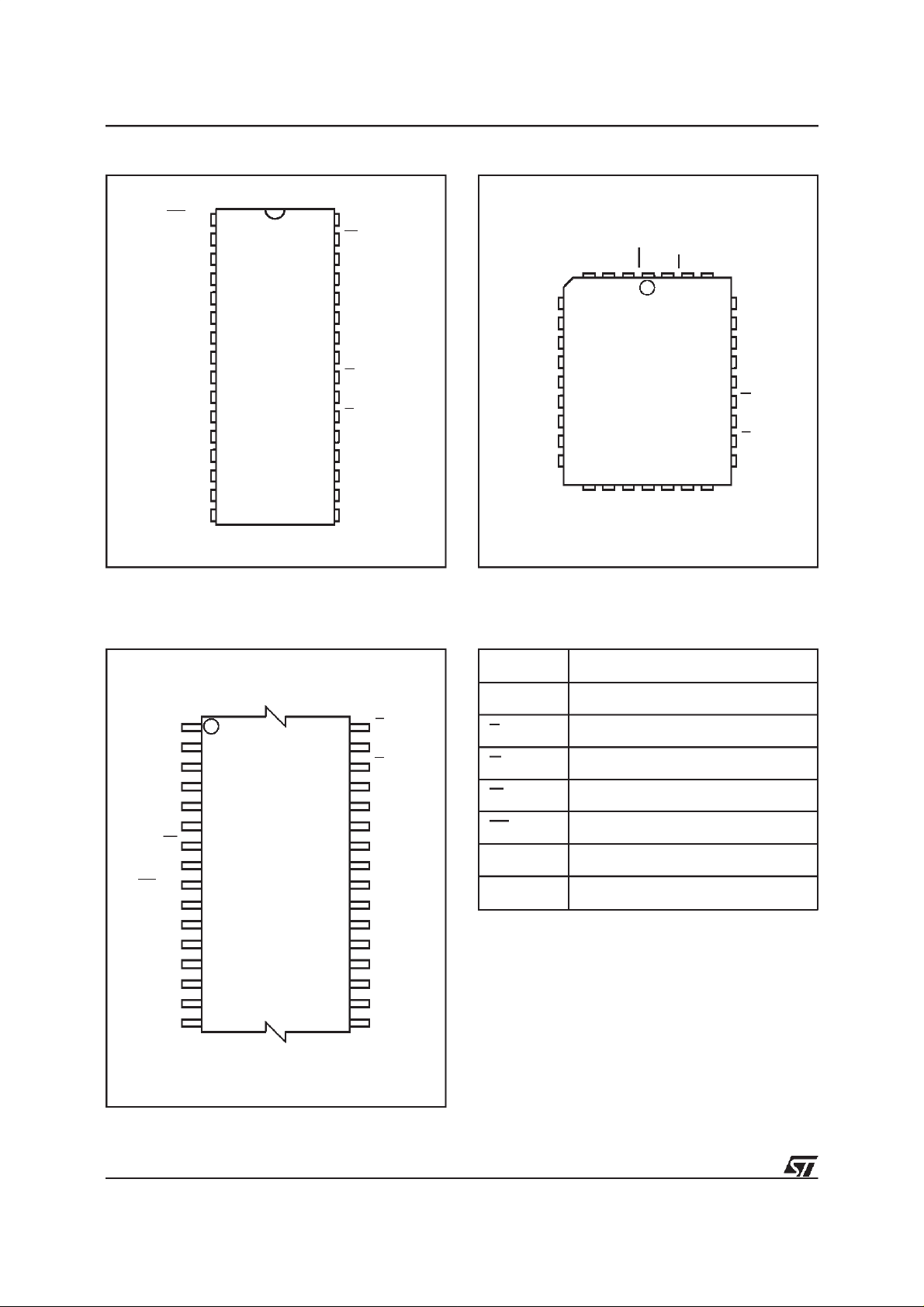

Figure2A. DIPPin Connections

(*) RPNC V

Note: Pin 1 is notconnected forthe M29F002NT

A15

A12

A7

A6

A5

A4

A3

A2

A1

A0

DQ0

DQ2

SS

1

2

3

4

5

6

7

M29F002T

8

M29F002B

9

M29F002NT

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

AI02080C

WA16

A17

A14

A13

A8

A9

A11

G

A10

E

DQ7

DQ6

DQ5DQ1

DQ4

DQ3V

CC

Figure2B. LCC Pin Connections

CC

RPNC

V

32

DQ3

DQ4

W

DQ5

A7

A6

A5

A4

A3

A2

A1

A0

DQ0

9

A12

A15

M29F002T

M29F002B

DQ1

DQ2

A16

1

17

SS

V

A17

25

DQ6

A14

A13

A8

A9

A11

G

A10

E

DQ7

AI02079C

Figure2C. TSOPPin Connections

A11 G

A9

A8

A13

A14

A17

V

CC

RPNC

A16

A15

A12

A7

A6

A5

A4 A3

1

W

8

M29F002T

M29F002B

9

16 17

32

25

24

AI02361B

A10

E

DQ7

DQ6

DQ5

DQ4

DQ3

V

SS

DQ2

DQ1

DQ0

A0

A1

A2

Table 1. Signal Names

A0-A17 Address Inputs

DQ0-DQ7 Data Input/Outputs, Command Inputs

E Chip Enable

G Output Enable

W Write Enable

RPNC

V

CC

V

SS

(*)

Reset / Block TemporaryUnprotect

Supply Voltage

Ground

DESCRIPTION(cont’d)

Instructionsfor Read/Reset, Auto Select for read-

ing the Electronic Signature or Block Protection

status,Programming,Blockand Chip Erase,Erase

Suspend and Resume are written to thedevice in

cyclesofcommandstoa CommandInterfaceusing

standardmicroprocessorwritetimings.The device

isoffered in PLCC32,PDIP32andTSOP32(8 x20

mm)packages.

2/29

M29F002T, M29F002NT, M29F002B

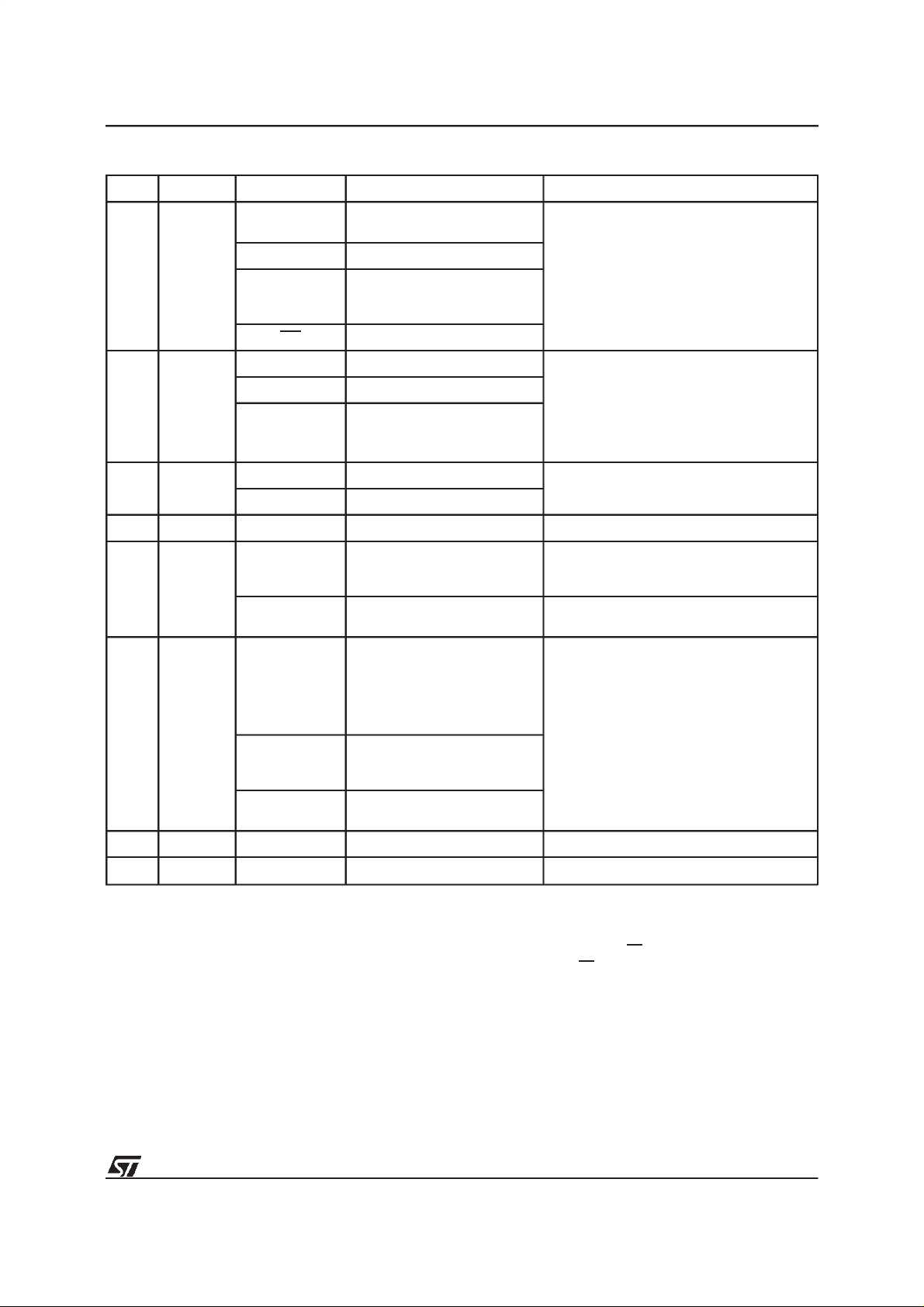

Table2. Absolute Maximum Ratings

Symbol Parameter Value Unit

T

A

T

BIAS

T

STG

(2)

V

IO

V

CC

V

(A9, E, G, RPNC)

Notes: 1. Except for therating ”Operating Temperature Range”, stressesabove those listedin theTable ”AbsoluteMaximum Ratings”

may cause permanent damage to thedevice. These are stress ratings only and operation of the device at these or any other

conditions above those indicated in the Operatingsections of this specification is not implied.Exposure to Absolute Maximum

Rating conditions for extended periods may affectdevice reliability.Refer also tothe STMicroelectronics SURE Programand other

relevant quality documents.

2. Minimum Voltagemay undershoot to–2V during transitionand for less than 20ns.

3. Depends on range.

Ambient Operating Temperature

Temperature Under Bias –50 to 125 °C

Storage Temperature –65 to 150 °C

Input or Output Voltages –0.6to 7 V

Supply Voltage –0.6to 7 V

(2)

A9, E, G, RPNC Voltage –0.6to 13.5 V

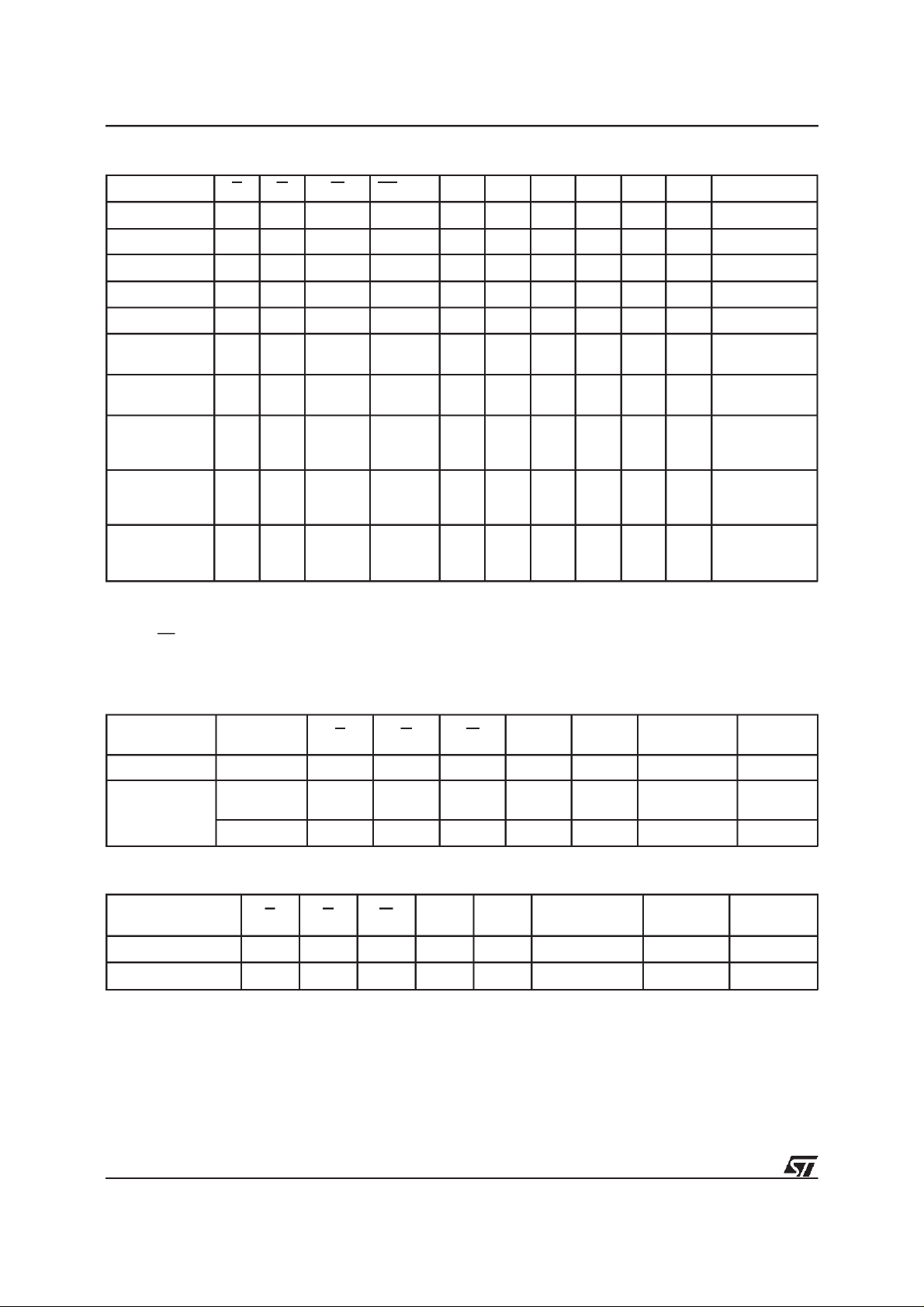

Organisation

The M29F002 is organised as 256K x 8. Memory

control is provided by Chip Enable E, OutputEnable G and WriteEnableW inputs.

A Reset/Block Temporary Unprotection RPNC

(NOTavailable on M29F002NT)tri-levelinput providesa hardwareresetwhenpulledLow,andwhen

held High (at V

) temporarily unprotectsblocks

ID

previously protected allowing them to be programed and erased. Erase and Program operations

are controlled by an internal Program/Erase Controller(P/E.C.).StatusRegisterdataoutputon DQ7

providesa Data Pollingsignal, and DQ6 and DQ2

provide Togglesignals to indicate the state of the

P/E.Coperations.

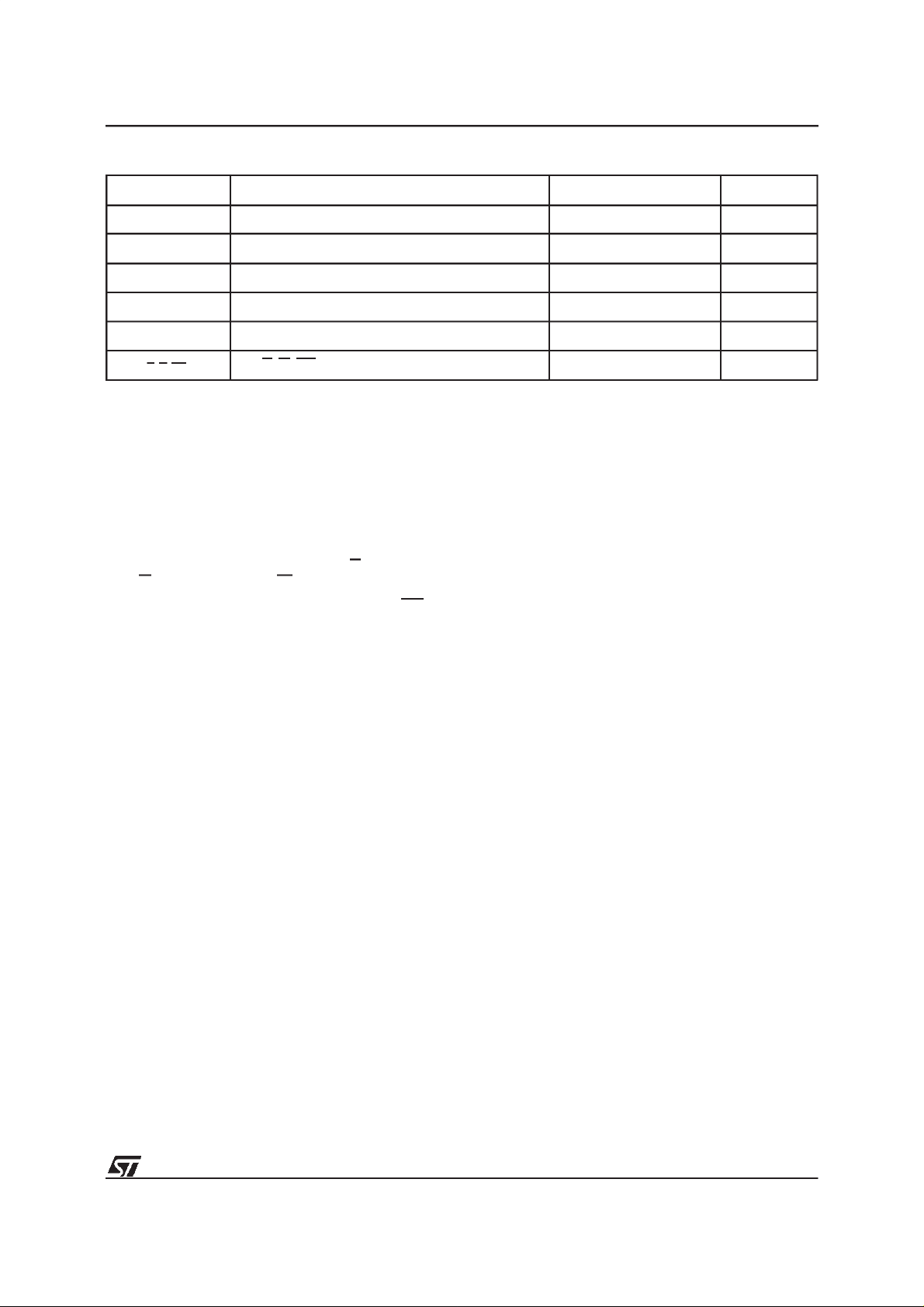

MemoryBlocks

Thedevices feature asymmetricallyblocked architecture providing system memory integration.The

M29F002hasan arrayof 7 blocks, one BootBlock

of 16 KBytes,two Parameter Blocks of 8 KBytes,

oneMainBlockof 32KBytesandthreeMainBlocks

of 64 KBytes.

Thememory map isshownin Figure3. Eachblock

can be erased separately, any combination of

blockscan be specifiedfor multi-blockerase or the

entire chip may be erased. The Erase operations

aremanagedautomaticallybytheP/E.C.Theblock

eraseoperationcan besuspendedin orderto read

(1)

(3)

–40 to 125 °C

from or program to any block not being ersased,

andthenresumed.Block protection providesadditional data security. Each block can be separately

protectedorunprotectedagainstProgramorErase

on programming equipment. All previously protectedblockscanbetemporarilyunprotectedin the

application.

Bus Operations

The following operations can be performed using

theappropriatebus cycles:Read(Array,Electronic

Signature, Block Protection Status), Write command, Output Disable,Standby,Reset, Block Protection, Unprotection, Protection Verify,

Unprotection Verify and Block Temporary Unprotection.See Tables4 and 5.

Command Interface

Instructions,made up of commands written in cycles,can be givento the Program/EraseController

through a Command Interface (C.I.). For added

dataprotection,program or erase execution starts

after4 or6 cycles.The first,second,fourthandfifth

cycles are used to input Coded cycles to the C.I.

This Coded sequence is the same for all Program/Erase Controller instructions. The ’Command’itself and its confirmation,when applicable,

are given on the third, fourth or sixth cycles. Any

incorrectcommand or any impropercommandsequencewill resetthe deviceto Read Array mode.

3/29

M29F002T, M29F002NT, M29F002B

Figure3. MemoryMap and Block AddressTable

3FFFFh

3C000h

3BFFFh

3A000h

39FFFh

38000h

37FFFh

30000h

2FFFFh

20000h

1FFFFh

10000h

0FFFFh

00000h

M29F002T, M29F002NT

16K BOOT BLOCK

8K PARAMETER BLOCK

8K PARAMETER BLOCK

32K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

3FFFFh

30000h

2FFFFh

20000h

1FFFFh

10000h

0FFFFh

08000h

07FFFh

06000h

05FFFh

04000h

03FFFh

00000h

M29F002B

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

32K MAIN BLOCK

8K PARAMETER BLOCK

8K PARAMETER BLOCK

16K BOOT BLOCK

Table 3A. M29F002T,M29F002NTBlock Address Table

Address Range A17 A16 A15 A14 A13

00000h-0FFFFh 0 0 X X X

10000h-1FFFFh 0 1 X X X

20000h-2FFFFh 1 0 X X X

AI02081C

30000h-37FFFh 1 1 0 X X

38000h-39FFFh 11100

3A000h-3BFFFh 11101

3C000h-3FFFFh 1111X

Table 3B. M29F002B Block Address Table

Address Range A17 A16 A15 A14 A13

00000h-03FFFh 0000X

04000h-05FFFh 00010

06000h-07FFFh 00011

08000h-0FFFFh 0 0 1 X X

10000h-1FFFFh 0 1 X X X

20000h-2FFFFh 1 0 X X X

30000h-3FFFFh 1 1 X X X

4/29

M29F002T, M29F002NT, M29F002B

Instructions

Seven instructions are defined to perform Read

Array,AutoSelect(to readthe ElectronicSignature

or BlockProtectionStatus),Program,Block Erase,

Chip Erase, Erase Suspend and Erase Resume.

The internal P/E.C. automatically handles all timing and verification of the Program and Erase

operations.The Status Register Data Polling, Toggle, Error bits may be read at any time, during

programming or erase, to monitor the progressof

the operation.

Instructionsare composedof up to sixcycles.The

first two cycles input a Coded sequence to the

CommandInterfacewhich iscommontoall instructions (see Table 8). The third cycle inputs the

instruction set-up command. Subsequent cycles

outputthe addressed data,ElectronicSignatureor

Block Protection Status for Read operations. In

orderto giveadditionaldataprotection,the instructionsfor Programand Blockor Chip Erase require

furthercommandinputs.ForaPrograminstruction,

the fourth command cycle inputs theaddressand

data to be programmed.For an Erase instruction

(Block or Chip), the fourth and fifth cycles input a

furtherCoded sequence before the Eraseconfirm

commandon thesixth cycle. Erasure of a memory

blockmaybesuspended,inordertoreaddatafrom

anotherblock or to programdata in anotherblock,

and then resumed.

When power is first applied or if V

V

, the command interface is reset to Read

LKO

falls below

CC

Array.

SIGNALDESCRIPTIONS

See Figure 1 and Table1.

AddressInputs (A0-A17).The addressinputs for

thememoryarrayarelatchedduringa write operation on the falling edge of Chip Enable E or Write

EnableW. When A9 is raised to V

, eithera Read

ID

ElectronicSignatureManufacturerorDeviceCode,

BlockProtectionStatus or a WriteBlock Protection

or BlockUnprotectionisenableddependingonthe

combinationof levels on A0,A1, A6,A12and A15.

DataInput/Outputs(DQ0-DQ7). Theinput is data

to be programmed in the memory array or a command to be written to the C.I. Both are latched on

the rising edge of Chip Enable E or Write Enable

W. Theoutput is data from the Memory Array, the

Electronic Signature Manufacturer or Device

codes, the Block Protection Status or the Status

registerData Polling bit DQ7, the ToggleBits DQ6

and DQ2, the Errorbit DQ5 or the EraseTimerbit

DQ3. Outputs are valid when Chip Enable E and

Output Enable G are active. The output is high

impedance when the chip is deselected or the

outputs are disabled and when RPNC is at a Low

level.

Chip Enable (E). The Chip Enable input activates

the memory control logic, input buffers, decoders

andsenseamplifiers.E Highdeselectsthememory

andreducesthepower consumptiontothestandby

level. E can also be used to control writing to the

commandregister and to the memory array,while

Wremainsat a low level.TheChip Enablemustbe

forcedto V

duringthe Block Unprotectionopera-

ID

tion.

OutputEnable (G). TheOutput Enable gates the

outputs through the data buffers during a read

operation. When G is High the outputs are High

impedance. G must be forced to V

level during

ID

BlockProtectionand Unprotection operations.

WriteEnable(W). This inputcontrols writingto the

CommandRegisterand Addressand Datalatches.

Reset/BlockTemporaryUnprotect/No Connect

Input (RPNC). The RPNC (not available for the

M29F002NT) input provides hardware reset and

protected block(s) temporary unprotection functions. In read or write mode, the RPNC pin can be

left open (Not Connected) or heldat V

thememory isacheived by pulling RPNC to V

. Reset of

IH

for

IL

atleast 500ns.When thereset pulseis given,if the

memory is in Read or Standby modes, it will be

availablefornewoperationsin 50nsafter the rising

edge of RPNC. If the memory is in Erase, Erase

Suspend or Program modes the reset will take

10µs.Ahardwareresetduringan EraseorProgram

operationwill corrupt the data being programmed

or the sector(s) being erased.

Temporary block unprotectionis made by holding

RPNCat V

. Inthisconditionpreviouslyprotected

ID

blockscan be programmed or erased. The transition of RPNC from V

500ns.When RPNCis returnedfrom V

to VIDmust slower than

IH

to VIHall

ID

blocks temporarily unprotected will be again protected.

Supply Voltage. The power supply for all

V

CC

operations(Read, Programand Erase).

Ground. VSSis the reference for all voltage

V

SS

measurements.

DEVICEOPERATIONS

SeeTables4, 5 and 6.

Read. Read operations are used to output the

contents of the Memory Array, the ElectronicSignature,the StatusRegisteror the BlockProtection

Status.Both Chip Enable E and Output Enable G

must be low in order to read the output of the

memory.

5/29

M29F002T, M29F002NT, M29F002B

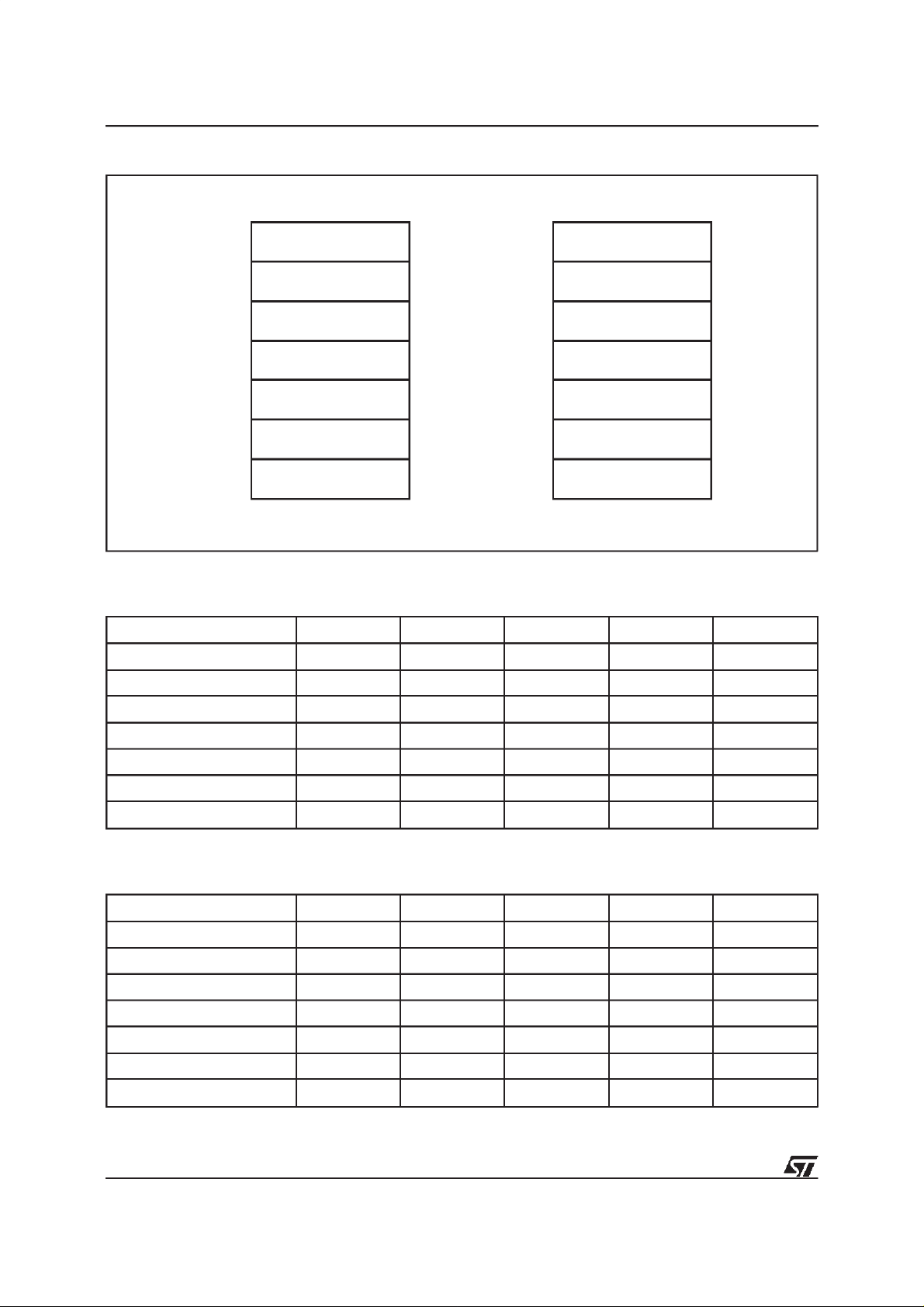

Table4. User Bus Operations

(1)

Operation E G W RPNC

Read Byte V

Write Byte V

Output Disable V

Standby V

(6)

Reset

Block

Protection

Blocks

Unprotection

(2,4)

(4)

V

V

V

IL

V

IL

IH

V

IL

IH

XXV

IH

V

IL

IH

V

IL

V

IH

XX X VILXXXXXX Hi-Z

VIDVILPulse VIH/NC

IL

VIDVILPulse VIH/NC

ID

Block

Protection

(2,4)

Verify

V

V

IL

V

IL

IH

Block

Unprotection

(2,4)

Verify

V

IL

V

IL

IH

V

Block

Temporary

Unprotection

Notes: 1. X = VILor V

2. Block Address must be given on A13-A17 bits.

3. See Table6.

4. Operation performed onprogramming equipment.

5. RPNC can be heldat V

6. Not Availableon M29F002NT.

XX X VIDXXXXXX X

(6)

IH

or left open (Not Connected).

IH

VIH/NC

VIH/NC

VIH/NC

/NC

IH

VIH/NC

VIH/NC

(6)

A0 A1 A6 A9 A12 A15 DQ0-DQ7

(5)

A0 A1 A6 A9 A12 A15 Data Output

(5)

A0 A1 A6 A9 A12 A15 Data Input

(5)

XXXXXX Hi-Z

(5)

XXXXXX Hi-Z

(5)

XXXVIDXX X

(5)

XXXVIDV

(5)

V

V

IL

(5)

V

IL

V

IH

IL

V

V

IH

IH

V

ID

V

ID

V

IH

IH

A12 A15

A12 A15

Block Protect

Block Protect

X

Status

Status

(3)

(3)

Table5. Read ElectronicSignature (followingAS instructionor with A9 = VID)

Code Device E G W A0 A1

Manufact. Code V

M29F002T

Device Code

M29F002NT

M29F002B V

IL

V

IL

IL

V

IL

V

IL

VIL V

V

IH

V

IH

IH

V

V

V

IL

IH

IH

V

IL

V

IL

V

IL

Addresses

Don’t Care 20h

Don’t Care B0h

Don’t Care 34h

Table6. Read Block Protectionwith AS Instruction

Code E G W A0 A1 A13 - A17

Protected Block V

Unprotected Block V

IL

IL

V

IL

V

IL

V

IH

V

IH

V

IL

V

IL

V

IH

V

IH

Block Address Don’t Care 01h

Block Address Don’t Care 00h

Addresses

Other

Other

DQ0 - DQ7

DQ0 - DQ7

6/29

M29F002T, M29F002NT, M29F002B

Write.Writeoperationsareused to giveInstruction

Commandsto the memoryor to latch input data to

beprogrammed.Awrite operationisinitiatedwhen

Chip Enable E is Low and Write Enable W is Low

with OutputEnableG High.Addressesare latched

onthe fallingedgeof W or E whicheveroccurslast.

Commandsand InputDataarelatchedontherising

edge of W or E whichever occurs first.

OutputDisable.The dataoutputsare highimpedancewhen the Output EnableG is High with Write

EnableW High.

Standby. The memory is in standby when Chip

EnableE is Highand the P/E.C.is idle. The power

consumption is reduced to the standby level and

the outputs are high impedance, independent of

the Output Enable G or WriteEnable W inputs.

Automatic Standby. After 150ns of bus inactivity

and whenCMOS levels are driving the addresses,

the chip automatically enters a pseudo-standby

modewhere consumptionis reducedto the CMOS

standbyvalue, while outputsstill drive the bus.

Electronic Signature. Two codes identifying the

manufacturerand the devicecan be read fromthe

memory. These codes allow programming equipment or applications to automatically match their

interface to the characteristics of the M29F002.

The Electronic Signature is output by a Read operationwhenthe voltageappliedto A9isat V

and

ID

addressinput A1is Low.Themanufacturercodeis

output when the Address input A0 is Lowand the

devicecodewhen thisinput isHigh.OtherAddress

inputs are ignored.

TheElectronic Signaturecanalso be read, without

raisingA9to V

, bygivingthe memorythe Instruc-

ID

tionAS.

Block Protection. Each block can be separately

protected against Program or Erase on programming equipment. Block protection provides additional data security, as it disables all program or

erase operations. This mode is activated when

bothA9 and G are raisedto V

and an addressin

ID

theblock is applied on A13-A17.TheBlockProtection algorithm is shownin Figure 14. Block protectionis initiatedon theedge of Wfallingto V

after a delay of 100µs, the edge of W rising to V

. Then

IL

IH

ends the protection operations. Block protection

verify is achieved by bringing G, E, A0 and A6 to

and A1 to VIH, while W is at VIHand A9 at VID.

V

IL

Undertheseconditions,readingthedataoutputwill

yield 01h if the block defined by the inputs on

A13-A17 is protected. Any attempt to program or

erase a protected block will be ignored by the

device.

Block Temporary Unprotection. This feature is

available on M29F002T and M29F002B only. Any

previouslyprotected block can be temporarily unprotected in order to change stored data. The

temporaryunprotectionmodeisactivatedby bringing RPNC to V

. Duringthe temporary unprotec-

ID

tion mode the previously protected blocks are

unprotected.Ablock can be selectedand data can

be modified by executing the Erase or Program

instructionwiththe RPNCsignal held atV

RPNC is returned to V

, all the previously pro-

IH

. When

ID

tectedblocksare again protected.

Block Unprotection. All protected blocks can be

unprotected on programming equipment to allow

updating of bit contents. All blocks must first be

protectedbefore theunprotectionoperation.Block

unprotectionis activatedwhen A9, G and E are at

V

and A12, A15 at VIH. The Block Unprotection

ID

algorithm is shown in Figure 15. Unprotection is

initiatedbythe edgeof W fallingto V

.Afteradelay

IL

of 10ms, the unprotection operation is ended by

rising W to V

bringing G and E to V

A1 are at V

. Unprotectionverify is achieved by

IH

and A9 remains at VID. In these

IH

while A0 is at VIL, A6 and

IL

conditions,reading the output data will yield 00hif

the block defined by the inputsA13-A17has been

succesfullyunprotected.Eachblockmustbe separately verified by giving its address in order to

ensurethat it has been unprotected.

INSTRUCTIONSAND COMMANDS

The Command Interface latches commands written to the memory. Instructionsare made up from

one or more commandsto performRead Memory

Array,ReadElectronicSignature,Read Block Protection,Program, Block Erase, Chip Erase, Erase

Suspend and Erase Resume. Commands are

madeof addressand datasequences.

Table7. Commands

Hex Code Command

00h Invalid/Reserved

10h Chip Erase Confirm

20h Reserved

30h Block Erase Resume/Confirm

80h Set-up Erase

90h

A0h Program

B0h Erase Suspend

F0h Read Array/Reset

Read Electronic Signature/

Block Protection Status

7/29

M29F002T, M29F002NT, M29F002B

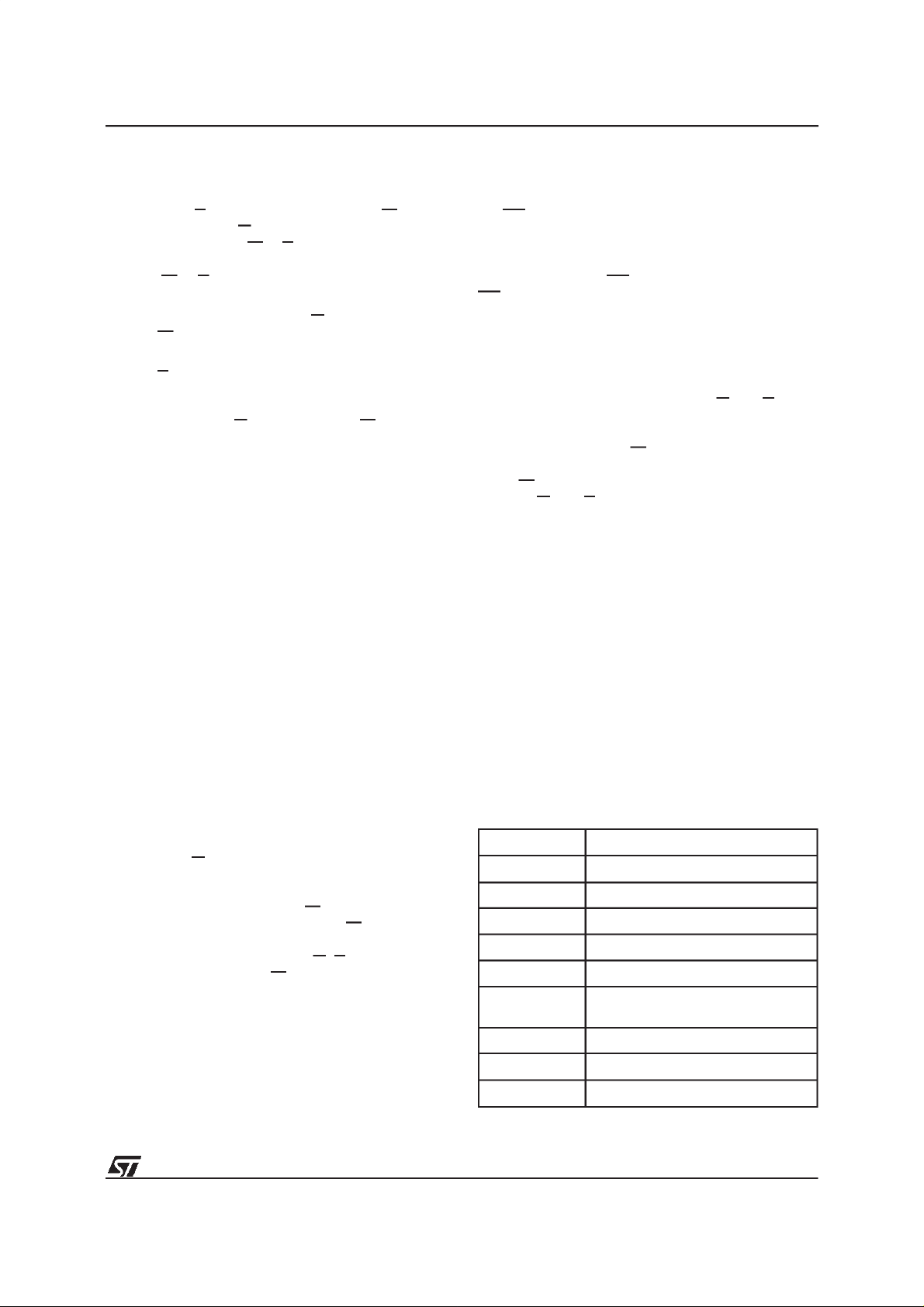

Table8. Instructions

(1)

Mne. Instr. Cyc. 1st Cyc. 2nd Cyc. 3rd Cyc. 4th Cyc. 5th Cyc. 6th Cyc. 7th Cyc.

RD

AS

Memory Array

(4)

AutoSelect 3+

Read/Reset

(2,4)

PG Program 4

BE BlockErase 6

(3,7)

Addr.

1+

Data F0h

(3,7)

Addr.

3+

Data AAh 55h F0h

(3,7)

Addr.

Data AAh 55h 90h

(3,7)

Addr.

Data AAh 55h A0h

(3,7)

Addr.

X

Read Memory Array until a new write cycle isinitiated.

555h AAAh 555h

Read Memory Array until a new write

cycle is initiated.

555h AAAh 555h Read Electronic Signature or Block

Protection Status until a new write cycle

is initiated. See Note 5 and 6.

555h AAAh 555h

Program

Address

Program

Read Data Polling or Toggle

Bit until Program completes.

Data

555h AAAh 555h 555h AAAh

Block

Address

Additional

Block

Data AAh 55h 80h AAh 55h 30h 30h

(3,7)

CE ChipErase 6

Addr.

555h AAAh 555h 555h AAAh 555h

Note 9

Data AAh 55h 80h AAh 55h 10h

(3,7)

ES

Notes: 1. Commands not interpreted in this table will default to read array mode.

Suspend

Erase

ER

Resume

2. Await of t

before starting any new operation (see Table14 and Figure 9).

3. X = Don’t Care.

4. The first cycles of the RD or AS instructions are followed by read operations.Any number of readcycles can occur after

the command cycles.

5. Signature Address bits A0,A1 at V

Device code.

6. Block Protection Address: A0 at V

7. For Coded cycles address inputs A12-A17are don’t care.

8. Optional, additional Blocks addresses must be entered within the erasetimeout delay after last writeentry,

timeout status can be verified through DQ3 value (see EraseTimerBit DQ3 description).

When full command is entered, read Data Polling or Togglebit until Erase is completed or suspended.

9. Read Data Polling, Togglebits or RB until Erase completes.

10.During Erase Suspend, Read and Data Programfunctions are allowed in blocks not being erased.

is necessary after a Read/Reset commandif the memory was in an Erase or Program mode

PLYH

Erase

(10)

Addr.

1

Data B0h

Addr.

1

Data 30h

IL

,A1atVIHand A13-A17 within the Block will output the Block Protection status.

IL

(3,7)

will output Manufacturer code (20h). Address bits A0 at VIHandA1 at VILwill output

X

Read until Togglestops, then read all the data needed from

any Block(s) not being erased then Resume Erase.

X

Read Data Polling or ToggleBits until Erase completesor

Erase is suspended another time

(8)

Theinstructionsrequirefrom 1 to6 cycles,the first

or first three of which are alwayswrite operations

usedtoinitiatetheinstruction.Theyarefollowedby

either further write cycles to confirmthe first commandor executethe commandimmediately.Command sequencing must be followed exactly. Any

invalid combination of commands will reset the

device to Read Array. The increased number of

cycleshas been chosen to assure maximum data

security. Instructions are initialised by two initial

Coded cycles which unlock the Command Interface.Inaddition,for Erase,instructionconfirmation

is again precededby the two Coded cycles.

8/29

StatusRegisterBits

P/E.C.statusis indicatedduring executionby Data

Polling on DQ7, detection of Toggle on DQ6 and

DQ2, or Erroron DQ5 and Erase Timer DQ3 bits.

Any read attempt during Program or Erase commandexecutionwill automaticallyoutputthesefive

StatusRegisterbits. TheP/E.C. automaticallysets

bits DQ2, DQ3, DQ5, DQ6 and DQ7. Other bits

(DQ0, DQ1 and DQ4) are reservedfor future use

and should be masked. See Tables9 and 10.

M29F002T, M29F002NT, M29F002B

Table 9. Status Register Bits

DQ Name Logic Level Definition Note

’1’

Data

7

Polling

’0’ Erase On-going

DQ

DQ Program On-going

Erase Complete or erase

block in Erase Suspend

Program Complete or data

of non erase block during

Erase Suspend

Indicates the P/E.C. status, check during

Program or Erase, and on completion

before checking bits DQ5 for Program or

Erase Success.

6 ToggleBit

5 Error Bit

4 Reserved

Erase

3

Time Bit

2 ToggleBit

’-1-0-1-0-1-0-1-’ Erase or Program On-going Successive reads outputcomplementary

DQ Program Complete

’-1-1-1-1-1-1-1-’

’1’ Program or Erase Error

’0’ Program or Erase On-going

’1’ Erase TimeoutPeriod Expired

’0’

’-1-0-1-0-1-0-1-’

1

DQ

Erase Complete or Erase

Suspend on currently

addressed block

Erase TimeoutPeriod

On-going

Chip Erase, Erase or Erase

Suspend on the currently

addressed block.

Erase Error due to the

currently addressed block

(when DQ5 = ’1’).

Program on-going, Erase

on-going on another block or

Erase Complete

Erase Suspend read on

non Erase Suspend block

data on DQ6 while Programming or Erase

operations are on-going. DQ6 remains at

constant level when P/E.C. operations are

completed or Erase Suspend is

acknowledged.

This bitis setto ’1’in the case of

Programming or Erase failure.

P/E.C. Erase operation has started. Only

possible command entry is Erase Suspend

(ES).

An additionalblock to be erased in parallel

can be entered to the P/E.C.

Indicates the erase status and allows to

identify the erased block

1 Reserved

0 Reserved

Notes: Logic level ’1’is High, ’0’ is Low.-0-1-0-0-0-1-1-1-0- represent bit value in successive Read operations.

Data Polling Bit (DQ7). WhenProgramming op-

erations are in progress, this bit outputs the complement of the bit being programmed on DQ7.

DuringEraseoperation,it outputsa ’0’.After completionof the operation, DQ7 will output the bit last

programmed or a ’1’after erasing. Data Polling is

valid and only effective during P/E.C. operation,

that is after the fourth W pulse for programmingor

after the sixth W pulse for erase. It must be performedat theaddress being programmed or at an

address within the block being erased. If all the

blocksselectedforerasureare protected,DQ7will

beset to ’0’for about 100µs,and thenreturnto the

previousaddressedmemory data value.

9/29

M29F002T, M29F002NT, M29F002B

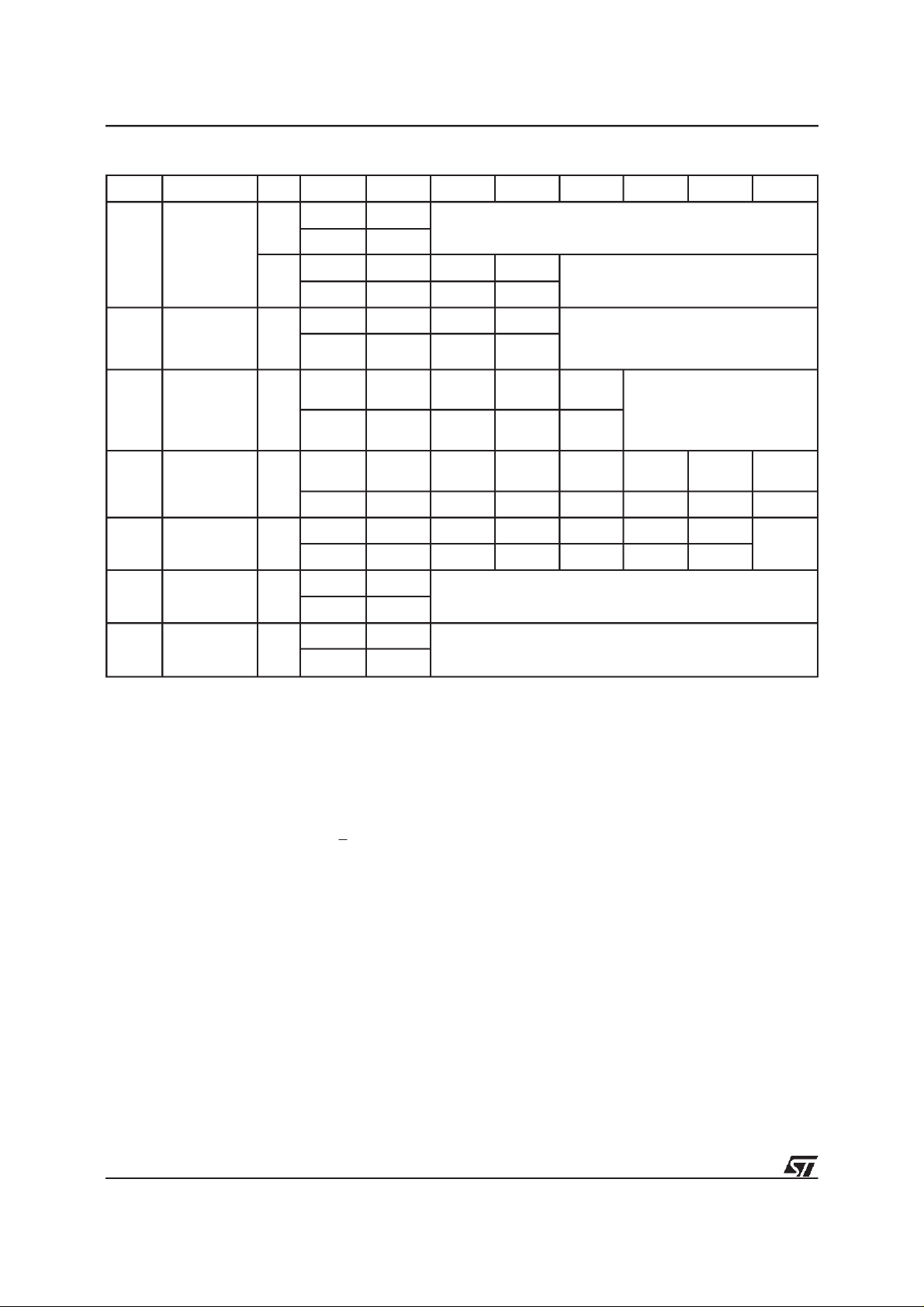

Table10. Polling and Toggle Bits

Mode DQ7 DQ6 DQ2

Program DQ7 Toggle 1

Erase 0 Toggle Note 1

Erase Suspend Read

(in EraseSuspend

block)

Erase Suspend Read

(outside Erase Suspend

block)

Erase Suspend Program DQ7 Toggle N/A

Note: 1. Toggle if the address is within a block being erased.

’1’ if the address is within a block not being erased.

1 1 Toggle

DQ7 DQ6 DQ2

See Figure 11 for the Data Polling flowchart and

Figure10 for theData Pollingwaveforms.DQ7 will

also flag the Erase Suspend mode by switching

from ’0’ to ’1’ at thestart of the Erase Suspend. In

order to monitor DQ7 in the EraseSuspend mode

an address within a block being erased must be

provided.For a Read Operationin EraseSuspend

mode, DQ7 will output ’1’if the read is attempted

onablockbeingerasedandthedatavalueonother

blocks. During Program operation in Erase SuspendMode, DQ7 will have the same behaviouras

in the normal program execution outside of the

suspendmode.

ToggleBit (DQ6). WhenProgrammingor Erasing

operationsare in progress,successiveattemptsto

readDQ6willoutputcomplementarydata.DQ6will

toggle followingtoggling of either G, or E when G

is low. The operation is completed when two successivereadsyield thesameoutputdata.Thenext

readwilloutputthe bitlastprogrammedora’1’after

erasing. The toggle bit DQ6 is valid only during

P/E.C. operations,thatis after the fourth W pulse

for programming or after the sixth W pulse for

Erase. If the blocks selected for erasure are protected, DQ6 will toggle for about 100µs and then

returnback toRead. DQ6will besetto ’1’if aRead

operationisattemptedonanEraseSuspendblock.

When erase is suspendedDQ6 will toggle during

programmingoperations in a blockdifferent to the

blockin EraseSuspend.EitherE or Gtogglingwill

causeDQ6 to toggle. SeeFigure 12 forToggleBit

flowchartand Figure 13 for ToggleBit waveforms.

Toggle Bit (DQ2). This toggle bit, together with

DQ6, can be used to determine the device status

duringthe Eraseoperations.It can also beusedto

identify the block being erased. During Erase or

Erase Suspenda read from a blockbeing erased

will cause DQ2 to toggle. A read from a blocknot

being erased will set DQ2 to ’1’during erase and

to DQ2 during Erase Suspend.During Chip Erase

a read operation will cause DQ2 to toggle as all

blocks are being erased. DQ2 will be set to ’1’

duringprogram operationand when erase is complete. After erase completion and if the error bit

DQ5 is set to ’1’, DQ2 will toggle if the faulty block

is addressed.

ErrorBit (DQ5). This bit is set to ’1’by the P/E.C.

when there is a failure of programming, block

erase, or chiperase that results in invalid data in

thememoryblock.In caseofanerrorin blockerase

or program,the block in which theerror occured or

to which the programmed data belongs, must be

discarded. The DQ5 failurecondition will also appearif a usertries to programa’1’ toa locationthat

ispreviouslyprogrammedto ’0’.OtherBlocksmay

stillbeused.Theerrorbit resetsafteraRead/Reset

(RD)instruction. In case of successof Program or

Erase,the error bit will be set to ’0’.

Erase Timer Bit (DQ3). Thisbit is set to ’0’ by the

P/E.C. when the last block Erase command has

been entered to the Command Interface and it is

awaiting the Erase start. When the erase timeout

periodis finished,after50µsto 120µs,DQ3returns

to ’1’.

Coded Cycles

Thetwo Coded cyclesunlockthe CommandInterface.Theyare followed by an input commandor a

confirmationcommand.The Coded cycles consist

ofwriting the dataAAh ataddress555hduringthe

first cycle. During the second cycle the Coded

cycles consist of writing the data 55h at address

AAAh.The addresslinesA0 to A11are valid,other

address lines are ’don’t care’. The Coded cycles

happenonfirstandsecondcyclesof thecommand

writeor on thefourth and fifthcycles.

Instructions

SeeTable 8.

Read/Reset (RD) Instruction. The Read/Reset

instruction consists of one write cycle giving the

commandF0h.It canbe optionallyprecededbythe

twoCodedcycles.Subsequentreadoperationswill

read the memory array addressed and output the

data read. A wait stateof 10µs is necessaryafter

Read/Reset prior to any valid read if the memory

was in an Erase mode when the RD instruction is

given.

10/29

M29F002T, M29F002NT, M29F002B

Table11. AC MeasurementConditions

High Speed Standard

Input Rise and Fall Times

Input Pulse Voltages 0 to 3V 0.45V to 2.4V

Input and Output Timing Ref. Voltages 1.5V 0.8V and 2V

≤

10ns

≤

10ns

Figure4. AC TestingInput Output Waveform

High Speed

3V

1.5V

0V

Standard

2.4V

0.45V

Table12. Capacitance

Symbol Parameter TestCondition Min Max Unit

C

IN

C

OUT

Note: 1. Sampled only, not 100% tested.

Input Capacitance VIN=0V 6 pF

Output Capacitance V

(1)

(TA=25°C, f = 1 MHz)

2.0V

0.8V

AI01275B

Figure5. AC TestingLoad Circuit

1.3V

1N914

3.3kΩ

DEVICE

UNDER

TEST

C

L

CL= 30pF for High Speed

CL= 100pF for Standard

CLincludes JIG capacitance

=0V 12 pF

OUT

OUT

AI01276B

Auto Select (AS) Instruction. This instruction

uses the two Coded cycles followed by one write

cyclegiving the command90h to address555h for

commandset-up. Asubsequentread willoutputthe

manufacturer code and the device code or the

block protection status dependingon the levels of

A0and A1. The manufacturercode,20h,is output

when the addresses lines A0 and A1 are Low,the

devicecodeis outputwhenA0isHigh withA1 Low.

The AS instructionalso allows accessto theblock

protectionstatus.AftergivingtheASinstruction,A0

is set to V

with A1 at VIH, while A13-A17 define

IL

the address of the block to be verified. A read in

these conditions will output a 01h if the block is

protectedand a 00h if the block is not protected.

Program (PG) Instruction. This instruction uses

four write cycles. The Program command A0h is

writtento address555h on the third cycle after two

Codedcycles. A fourth write operation latches the

Addresson the fallingedge of W orE and the Data

to be written on the rising edge and starts the

P/E.C.Readoperationsoutput the StatusRegister

bits after the programming has started. Memory

programmingis made only by writing’0’in place of

’1’.StatusbitsDQ6andDQ7determineif programmingison-goingandDQ5 allowsverificationofany

possible error. Programming at an address not in

blocks being erased is also possible during erase

suspend. In this case, DQ2 will toggle at the addressbeing programmed.

11/29

M29F002T, M29F002NT, M29F002B

Table13. DC Characteristics

=0 to 70°C or –40 to 85°C; VCC=5V±10%)

(T

A

Symbol Parameter Test Condition Min Max Unit

(2)

I

LI

I

I

LR1

I

LR2

I

CC1

I

CC2

I

CC3

I

CC4

Input Leakage Current 0V ≤ VIN≤ V

Output Leakage Current 0V ≤ V

LO

RPNC Leakage Current High RPNC = V

RPNC Leakage Current Low RPNC = V

Supply Current (Read) TTL Byte E = VIL,G=VIH, f = 6MHz 20 mA

Supply Current (Standby) TTL E = V

Supply Current (Standby) CMOS E = V

(1)

Supply Current (Program or Erase)

Byte program, Block or

Chip Erase in progress

CC

≤ V

OUT

CC

CC

SS

IH

0.2V 100

±

CC

–0.2 –10 µA

±1 µA

±1 µA

±1 µA

1mA

20 mA

A

µ

V

V

V

V

V

I

V

LKO

Note: 1. Sampled only, not 100% tested.

Input Low Voltage –0.5 0.8 V

IL

Input High Voltage 2 VCC+ 0.5 V

IH

Output Low Voltage IOL= 5.8mA 0.45 V

OL

Output High Voltage TTL IOH= –2.5mA 2.4 V

OH

Output High VoltageCMOS I

A9, E, G, RPNC High Voltage 11.5 12.5 V

ID

A9, E, G, RPNC High Current A9, E, G or RPNC = V

ID

Supply Voltage(Erase and

Program lock-out)

2. Except RPNC.

Block Erase (BE) Instruction. This instruction

uses a minimum of six write cycles. The Erase

Set-upcommand80his writtento address555hon

third cycle after the two Coded cycles. The Block

EraseConfirmcommand30his similarlywrittenon

the sixth cycle after another two Coded cycles.

During the input of the second command an address within the block to be erased is given and

latched into the memory. Additional block Erase

Confirm commands and block addresses can be

written subsequently to erase other blocksin parallel, without further Coded cycles. The erase will

start after the erase timeout period (see Erase

TimerBit DQ3description).Thus,additionalErase

Confirmcommandsfor otherblocks mustbe given

withinthisdelay. Theinputof anew EraseConfirm

commandwillrestartthetimeoutperiod.Thestatus

of the internal timer can be monitored throughthe

level of DQ3, if DQ3 is ’0’ the Block Erase Commandhas beengiven and the timeoutis running,if

DQ3 is ’1’, the timeout has expired andthe P/E.C.

= –100µAV

OH

ID

–0.4V V

CC

100

3.2 4.2 V

is erasing the Block(s). If the second command

givenis notan eraseconfirmor if theCodedcycles

arewrong,the instructionaborts,and thedevice is

resetto Read Array. It is not necessaryto program

the block with 00h as the P/E.C. will do thisautomaticallybeforetoerasingtoFFh.Readoperations

after the sixth rising edge of W or E output the

statusregister status bits.

Duringtheexecutionof theeraseby theP/E.C.,the

memoryaccepts onlythe EraseSuspend ES and

Read/ResetRD instructions. Data Polling bit DQ7

returns’0’ while the erasureis inprogress and ’1’

when it has completed. The Toggle bit DQ2 and

DQ6 toggle during the erase operation. They stop

when erase is completed. After completion the

StatusRegisterbitDQ5returns’1’iftherehasbeen

an erase failure. In sucha situation, the Toggle bit

DQ2 can be used to determine which block is not

correctly erased. In the case of erase failure, a

Read/ResetRDinstructionis necessaryin orderto

resetthe P/E.C.

A

µ

12/29

Table14. Read AC Characteristics

=0 to 70°C or –40 to 85°C)

(T

A

Symbol Alt Parameter Test Condition

t

t

t

ELQX

AVAV

AVQV

(1)

Address Validto

t

RC

Next Address Valid

Address Validto

t

ACC

Output Valid

Chip Enable Low to

t

LZ

Output Transition

E=V

E=V

G=V

,G=V

IL

,G=V

IL

IL

M29F002T, M29F002NT, M29F002B

M29F002T / M29F002NT / M29F002B

-70 -90 -120

V

=5V±10% VCC=5V±10% VCC=5V±10%

CC

Standard

Interface

Standard

Interface

Standard

Interface

Min Max Min Max Min Max

70 90 120 ns

IL

IL

70 90 120 ns

000ns

Unit

(2)

t

ELQV

(1)

t

GLQX

(2)

t

GLQV

t

EHQX

(1)

t

EHQZ

t

GHQX

(1)

t

GHQZ

t

AXQX

(1,3)

t

PLEL

t

t

Notes: 1. Sampled only,not 100% tested.

t

PHEL

PLPX

2. G maybe delayed by up to t

3. To be considered only if the Reset pulse is given while the memory is in Erase mode.

Chip Enable Low to

t

CE

Output Valid

Output Enable Low

t

OLZ

to Output Transition

Output Enable Low

t

OE

to Output Valid

Chip Enable High to

t

OH

Output Transition

Chip Enable High to

t

HZ

Output Hi-Z

Output Enable High

t

OH

to Output Transition

Output Enable High

t

DF

to Output Hi-Z

Address Transition

t

OH

to Output Transition

RPNC Low to Read

READY

Mode

RPNC High to Chip

t

RSP

Enable Low

t

RPNC Pulse Width 500 500 500 ns

RP

ELQV-tGLQV

G=V

IL

000ns

000ns

000ns

000ns

IL

G=V

G=V

E=V

E=V

E=V

E=V

E=V

,G=V

IL

IL

IL

IL

IL

IL

IL

50 50 50 ns

afterthe falling edge of E without increasing t

70 90 120 ns

30 35 50 ns

20 20 30 ns

20 20 30 ns

10 10 10

.

ELQV

µ

s

13/29

M29F002T, M29F002NT, M29F002B

Figure 6. ReadMode AC Waveforms

tEHQZ

tGHQX

AI02082

tGHQZ

VALID

tAVAV

VALID

A0-A17

tAVQV tAXQX

tELQV

tGLQV

tGLQX

tELQX tEHQX

E

G

DQ0-DQ7

OUTPUT ENABLE DATA VALID

ADDRESS VALID

AND CHIP ENABLE

WriteEnable (W) = High

Note:

14/29

Table15. Write AC Characteristics,WriteEnable Controlled

=0 to 70°C or –40 to 85°C)

(T

A

M29F002T / M29F002NT / M29F002B

-70 -90 -120

Symbol Alt Parameter

Address Validto Next Address

t

AVAV

t

ELWL

t

WLWH

t

DVWH

t

WHDX

t

WC

Valid

Chip Enable Low to WriteEnable

t

CS

Low

Write Enable Low to Write Enable

t

WP

High

t

Input Validto Write Enable High 30 45 50 ns

DS

Write Enable High to Input

t

DH

Transition

=5V±10% VCC=5V±10% VCC=5V±10%

V

CC

Standard

Interface

Min Max Min Max Min Max

70 90 120 ns

000ns

35 45 50 ns

000ns

M29F002T, M29F002NT, M29F002B

Unit

Standard

Interface

Standard

Interface

Write Enable High to Chip Enable

(1,2)

t

CH

High

Write Enable High to Write Enable

t

WPH

Low

t

Address Validto Write Enable Low 5 5 5 ns

AS

Write Enable Low to Address

t

AH

Transition

Output Enable High to Write

Enable Low

t

VCSVCC

t

OEH

t

VIDR

t

RP

High to Chip Enable Low 50 50 50

Write Enable High to Output

Enable Low

RPNC Rise Time to V

ID

RPNC Pulse Width 500 500 500 ns

t

WHEH

t

WHWL

t

AVWL

t

WLAX

t

GHWL

t

VCHEL

t

WHGL

t

PHPHH

t

PLPX

Notes: 1. Sample only, not 100% tested.

2. This timing is for TemporaryBlock Unprotection operation.

ChipErase(CE)Instruction.Thisinstructionuses

six write cycles. The Erase Set-up command 80h

is written to address555h on the third cycle after

the two Coded cycles. The Chip Erase Confirm

command10h is similarlywrittenon thesixthcycle

after another two Coded cycles. If the second

command given is not an erase confirm or if the

Codedcyclesare wrong,theinstructionabortsand

thedeviceisresettoReadArray.Itisnotnecessary

000ns

20 20 20 ns

45 45 50 ns

000ns

s

µ

000ns

500 500 500 ns

toprogramthearray with00h firstastheP/E.C.will

automaticallydothisbeforeerasingittoFFh.Read

operations after the sixth rising edge of W or E

output the Status Register bits. During the executionof theeraseby the P/E.C.,DataPollingbit DQ7

returns’0’, then ’1’ on completion. The Toggle bits

DQ2 and DQ6 toggle during erase operation and

stopwheneraseis completed.Aftercompletionthe

StatusRegisterbitDQ5returns’1’iftherehasbeen

an Erase Failure.

15/29

M29F002T, M29F002NT, M29F002B

Figure7. WriteAC Waveforms,W Controlled

tAVAV

A0-A17

tAVWL

E

tELWL

G

W

DQ0-DQ7

V

CC

tVCHEL

Note: Address are latched on the falling edge of W, Datais latched on the rising edge of W.

VALID

tWLAX

tWLWHtGHWL

tDVWH

VALID

tWHEH

tWHGL

tWHWL

tWHDX

AI02083

Erase Suspend (ES) Instruction. The Block

Eraseoperationmay besuspendedbythisinstruction which consists of writing the command B0h

withoutany specificaddress. No Coded cyclesare

required. It permits reading of data from another

block and programming in anotherblock while an

erase operation is in progress. Erase suspend is

accepted only during the Block Erase instruction

execution. Writing this command during Erase

timeout will, in addition to suspending the erase,

terminate the timeout. The Toggle bit DQ6 stops

togglingwhentheP/E.C.is suspended.The Toggle

bitswill stoptogglingbetween0.1µsand 15µsafter

the Erase Suspend (ES) command has been written. The device will then automatically be set to

Read Memory Array mode. When erase is suspended, a Read from blocks being erased will

output DQ2 togglingand DQ6 at ’1’. A Read from

a blocknot beingerasedreturnsvalid data.During

suspension the memory will respond only to the

Erase Resume ER and the Program PG instructions. A Program operation can be initiatedduring

erase suspend in one of the blocks not being

erased. It willresult in both DQ2and DQ6 toggling

whenthedatais beingprogrammed.ARead/Reset

16/29

commandwill definitivelyabort erasure and result

in invalid data in the blocksbeing erased.

EraseResume(ER)Instruction. IfanErase Suspend instruction was previously executed, the

erase operation may be resumed by giving the

command 30h, at any address, and without any

Codedcycles.

POWERSUPPLY

PowerUp

ThememoryCommandInterfaceis reset onpower

uptoRead Array.EitherE or Wmust be tiedto V

IH

during Power Up to allow maximum security and

thepossibilityto writea commandonthefirst rising

edge of E and W. Any write cycle initiation is

blockedwhen Vcc is below V

LKO

.

SupplyRails

Normalprecautionsmust be takenfor supply voltage decoupling; each device in a system should

havethe V

close to the V

widths should be sufficient to carry the V

raildecoupledwith a 0.1µF capacitor

CC

and VSSpins. The PCB trace

CC

CC

pro-

gramand erasecurrents required.

Table16. Write AC Characteristics,Chip Enable Controlled

=0 to 70°C or –40 to 85°C)

(T

A

M29F002T / M29F002NT / M29F002B

-70 -90 -120

Symbol Alt Parameter

Address Valid to Next Address

t

AVAV

t

WLEL

t

ELEH

t

DVEH

t

EHDX

t

WC

Valid

Write Enable Low to Chip

t

WS

Enable Low

Chip Enable Low to Chip

t

CP

Enable High

t

Input Validto Chip EnableHigh 30 45 50 ns

DS

Chip Enable High to Input

t

DH

Transition

=5V±10% VCC=5V±10% VCC=5V±10%

V

CC

Standard

Interface

Min Max Min Max Min Max

70 90 120 ns

000ns

35 45 50 ns

555ns

M29F002T, M29F002NT, M29F002B

Unit

Standard

Interface

Standard

Interface

Chip Enable High to Write

(1,2)

t

t

CPH

t

t

t

VCS

t

OEH

t

VIDR

t

WH

Enable High

Chip Enable High to Chip

Enable Low

Address Valid to Chip Enable

AS

Low

Chip Enable Low to Address

AH

Transition

Output Enable High Chip

Enable Low

VCCHigh to Write Enable Low 50 50 50 µs

Chip Enable High to Output

Enable Low

RPNC Rise TIme to V

RPNC Pulse Width 500 500 500 ns

RP

t

EHWH

t

EHEL

t

AVEL

t

ELAX

t

GHEL

t

VCHWL

t

EHGL

t

PHPHH

t

PLPX

Notes: 1. Sample only, not 100% tested.

2. This timing is for TemporaryBlock Unprotection operation.

000ns

20 20 20 ns

000ns

45 45 50 ns

000ns

000ns

ID

500 500 500 ns

17/29

M29F002T, M29F002NT, M29F002B

Figure8. WriteAC Waveforms,E Controlled

tAVAV

A0-A17

tAVEL

W

tWLEL

G

E

DQ0-DQ7

V

CC

tVCHWL

Note: Address are latched onthe falling edge of E, Data is latchedon the rising edge of E.

VALID

tELAX

tELEHtGHEL

tDVEH

VALID

tEHWH

tEHGL

tEHEL

tEHDX

AI02084

Figure9. Readand WriteAC Characteristics,RP Related

E

tPHEL

RPNC

18/29

tPLPX

tPLEL

tPHPHH

AI02085

M29F002T, M29F002NT, M29F002B

Table17. Data Polling and Toggle Bit AC Characteristics

(TA=0 to 70°C or –40 to 85°C)

M29F002T / M29F002NT / M29F002B

Sym-

bol

Alt Parameter

Write Enable High to DQ7 Valid

t

WHQ7V

(Program, W Controlled)

Write Enable High to DQ7 Valid

(Chip Erase, W Controlled)

Chip Enable High to DQ7 Valid

t

EHQ7V

(Program, E Controlled)

Chip Enable High to DQ7 Valid

(Chip Erase, E Controlled)

t

Q7VQV

Q7 Validto Output Valid (Data

Polling)

Write Enable High to Output

t

WHQV

Valid(Program)

Write Enable High to Output

Valid(Chip Erase)

Chip Enable High to Output

t

EHQV

Valid(Program)

Chip Enable High to Output

Valid(Chip Erase)

Note: 1. All other timings are defined in Read AC Characteristics table.

-70 -90 -120

=5V±10% VCC=5V±10% VCC=5V±10%

V

CC

Standard

Interface

Min Max Min Max Min Max

10 2400 10 2400 10 2400

1.0 30 1.0 30 1.0 30 sec

10 2400 10 2400 10 2400 µs

1.0 30 1.0 30 1.0 30 sec

30 35 50 ns

10 2400 10 2400 10 2400

1.0 30 1.0 30 1.0 30 sec

10 2400 10 2400 10 2400 µs

1.0 30 1.0 30 1.0 30 sec

(1)

Standard

Interface

Standard

Interface

Unit

µ

µ

s

s

19/29

M29F002T, M29F002NT, M29F002B

Figure10. DataPolling DQ7 AC Waveforms

AI02086

ARRAY

READ CYCLE

DATA OUTPUT VALID

ADDRESS (WITHIN BLOCKS)

tAVQV

tELQV

tEHQ7V

tGLQV

VALID

DQ7

tWHQ7V

VALID

tQ7VQV

IGNORE

DATA POLLING (LAST) CYCLE MEMORY

READ CYCLES

DATA POLLING

20/29

A0-A17

PROGRAM

OR ERASE

CYCLE OF

LAST WRITE

E

G

W

DQ7

DQ0-DQ6

INSTRUCTION

M29F002T, M29F002NT, M29F002B

Figure 11. Data Polling Flowchart

START

READ DQ5 &

at VALID ADDRESS

NO

READ DQ7

DQ7

DQ7

YES

=

DATA

NO

DQ5

=1

YES

DQ7

YES

=

DATA

NO

FAIL PASS

Figure 12. Data Toggle Flowchart

START

READ

DQ2, DQ5 & DQ6

DQ6

YES

YES

DQ6

YES

NO

NO

DQ2,

=

TOGGLE

NO

DQ5

=1

READ DQ2, DQ6

DQ2,

=

TOGGLE

FAIL PASS

AI01369

AI01873

Table 18. Program, Erase Times and Program, Erase Endurance Cycles

= 0 to 70°C)

(T

A

M29F002T / M29F002NT / M29F002B

Parameter

Min Typ

Typical after

100k W/E Cycles

Chip Erase (Preprogrammed) 0.7 0.9 sec

Chip Erase 2.4 2.5 sec

Boot Block Erase 0.6 sec

Parameter Block Erase 0.5 sec

Main Block (32Kb) Erase 0.9 sec

Main Block (64Kb) Erase 1.0 sec

Chip Program (Byte) 3.2 3.2 sec

Byte Program 11 11

Program/Erase Cycles (perBlock) 100,000 cycles

Unit

s

µ

21/29

M29F002T, M29F002NT, M29F002B

Figure13. DataToggle DQ6, DQ2AC Waveforms

AI02087

VALID

tEHQV

tAVQV

tELQV

tGLQV

VALID

tWHQV

STOP TOGGLE

VALID

IGNORE

READ CYCLE

MEMORY ARRAY

READ CYCLE

DATA TOGGLE

22/29

A0-A17

DATA

TOGGLE

READ CYCLE

OF ERASE

PROGRAM

CYCLE OF

LAST WRITE

E

G

W

DQ6,DQ2

DQ0-DQ1,DQ3-DQ5,DQ7

INSTRUCTION

All other timings are as a normal Readcycle.

Note:

Figure 14. Block Protection Flowchart

M29F002T, M29F002NT, M29F002B

Set-up

Protect

Verify

VERIFY BLOCK

A0, A6 = VIL;A1=VIH;A9=VID

A13-A17 IDENTIFY BLOCK

START

BLOCK

on A13-A17

W=V

n=0

G, A9 = VID,

E=V

Wait 4µs

W=V

Wait 100µs

W=V

E, G = V

ADDRESS

IH

IL

IL

IH

IH

PROTECTION

E=V

IL

Wait 4µs

G=V

IL

Wait 60ns

VERIFY

DATA

=

01h

A9 = V

PASS

BLOCK

NO

YES

IH

PROTECT STATUS

++n

=25

A9 = V

FAIL

NO

YES

IH

AI02088B

23/29

M29F002T, M29F002NT, M29F002B

Figure15. AllBlocks UnprotectingFlowchart

E, A0 = VIL; A1, A6 = VIH;A9=V

A13-A17 IDENTIFY BLOCK

START

PROTECT

ALL BLOCKS

n=0

W=V

IH

E, G, A9 = V

A12, A15 = V

Wait 4µs

W=V

IL

Wait 10ms

W=V

IH

E, G = V

Set-up

ID

IH

Unprotect

IH

ID

Verify

NEXT

BLOCK

Wait 4µs

G=V

IL

Wait 60ns

BLOCK

VERIFY

PROTECT STATUS

YESNO

DATA

=

00h

++n

NO

= 1000

YES

A9 = V

IH

FAIL PASS

LAST

BLK.

A9 = V

NO

YES

IH

AI02089C

24/29

ORDERING INFORMATION SCHEME

Example: M29F002T -70 X K 1 TR

M29F002T, M29F002NT, M29F002B

Operating Voltage

F5V

Array Matrix

T TopBoot

B Bottom Boot

NT TopBoot

without

RPNC function

Speed

-70 70ns

-90 90ns

-120 120ns

Power Supplies

blank V

XV

CC

CC

±

±

10%

5%

Package

P PDIP32

K PLCC32

N TSOP32

(8 x 20 mm)

Option

TR Tape & Reel

Packing

Temp. Range

1 0 to 70°C

6 –40 to 85°C

Devicesare shipped from the factory with the memory contenterased (to FFh).

Fora list ofavailableoptions(Speed,Package,etc...)or for furtherinformationon anyaspect of thisdevice,

pleasecontactthe STMicroelectronicsSales Officenearest to you.

25/29

M29F002T, M29F002NT, M29F002B

PDIP32 - 32 pin Plastic DIP, 600 mils width

Symb

Typ Min Max Typ Min Max

A – 5.08 – 0.200

A1 0.38 – 0.015 –

A2 3.56 4.06 0.140 0.160

B 0.38 0.51 0.015 0.020

B1 1.52 – – 0.060 – –

C 0.20 0.30 0.008 0.012

D 41.78 42.04 1.645 1.655

D2 38.10 – – 1.500 – –

E 15.24 – – 0.600 – –

E1 13.59 13.84 0.535 0.545

e1 2.54 – – 0.100 – –

eA 15.24 – – 0.600 – –

eB 15.24 17.78 0.600 0.700

L 3.18 3.43 0.125 0.135

S 1.78 2.03 0.070 0.080

α 0° 10° 0° 10°

N32 32

mm inches

Drawing is not to scale.

26/29

B1 B e1

D2

D

S

N

1

A2A1A

E1 E

L

α

C

eA

eB

PDIP

M29F002T, M29F002NT, M29F002B

PLCC32 - 32 lead Plastic LeadedChip Carrier,rectangular

Symb

Typ Min Max Typ Min Max

A 2.54 3.56 0.100 0.140

A1 1.52 2.41 0.060 0.095

A2 – 0.38 – 0.015

B 0.33 0.53 0.013 0.021

B1 0.66 0.81 0.026 0.032

D 12.32 12.57 0.485 0.495

D1 11.35 11.56 0.447 0.455

D2 9.91 10.92 0.390 0.430

E 14.86 15.11 0.585 0.595

E1 13.89 14.10 0.547 0.555

E2 12.45 13.46 0.490 0.530

e 1.27 – – 0.050 – –

F 0.00 0.25 0.000 0.010

R 0.89 – – 0.035 – –

N32 32

Nd 7 7

Ne 9 9

CP 0.10 0.004

mm inches

D

D1

1N

Ne E1 E

Nd

PLCC

Drawing is not to scale.

R

F

0.51 (.020)

1.14 (.045)

D2/E2

A1

A2

B1

e

B

A

CP

27/29

M29F002T, M29F002NT, M29F002B

TSOP32 - 32 lead Plastic Thin Small Outline, 8 x 20mm

Symb

Typ Min Max Typ Min Max

A 1.20 0.047

A1 0.05 0.15 0.002 0.007

A2 0.95 1.05 0.037 0.041

B 0.15 0.27 0.006 0.011

C 0.10 0.21 0.004 0.008

D 19.80 20.20 0.780 0.795

D1 18.30 18.50 0.720 0.728

E 7.90 8.10 0.311 0.319

e 0.50 - - 0.020 - -

L 0.50 0.70 0.020 0.028

α

N32 32

CP 0.10 0.004

mm inches

0

°

5

°

0

°

5

°

Drawing is not to scale.

1N

E

N/2

D1

D

DIE

TSOP-a

A2

e

B

A

CP

C

LA1 α

28/29

M29F002T, M29F002NT, M29F002B

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences

ofuse ofsuch information nor for any infringement of patents or otherrightsof third parties which may result from itsuse. No license is granted

by implicationor otherwise under any patent or patent rights of STMicroelectronics. Specificationsmentioned in this publication are subject to

change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not

authorized for use as critical componentsin lifesupport devices or systems without express writtenapproval of STMicroelectronics.

The STlogo is a registeredtrademark of STMicroelectronics.

1998 STMicroelectronics - All Rights Reserved

Australia - Brazil - Canada- China- France- Germany - Italy - Japan - Korea - Malaysia - Malta- Mexico - Morocco - The Netherlands -

Singapore - Spain - Sweden- Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

STMicroelectronics GROUP OF COMPANIES

29/29

Loading...

Loading...