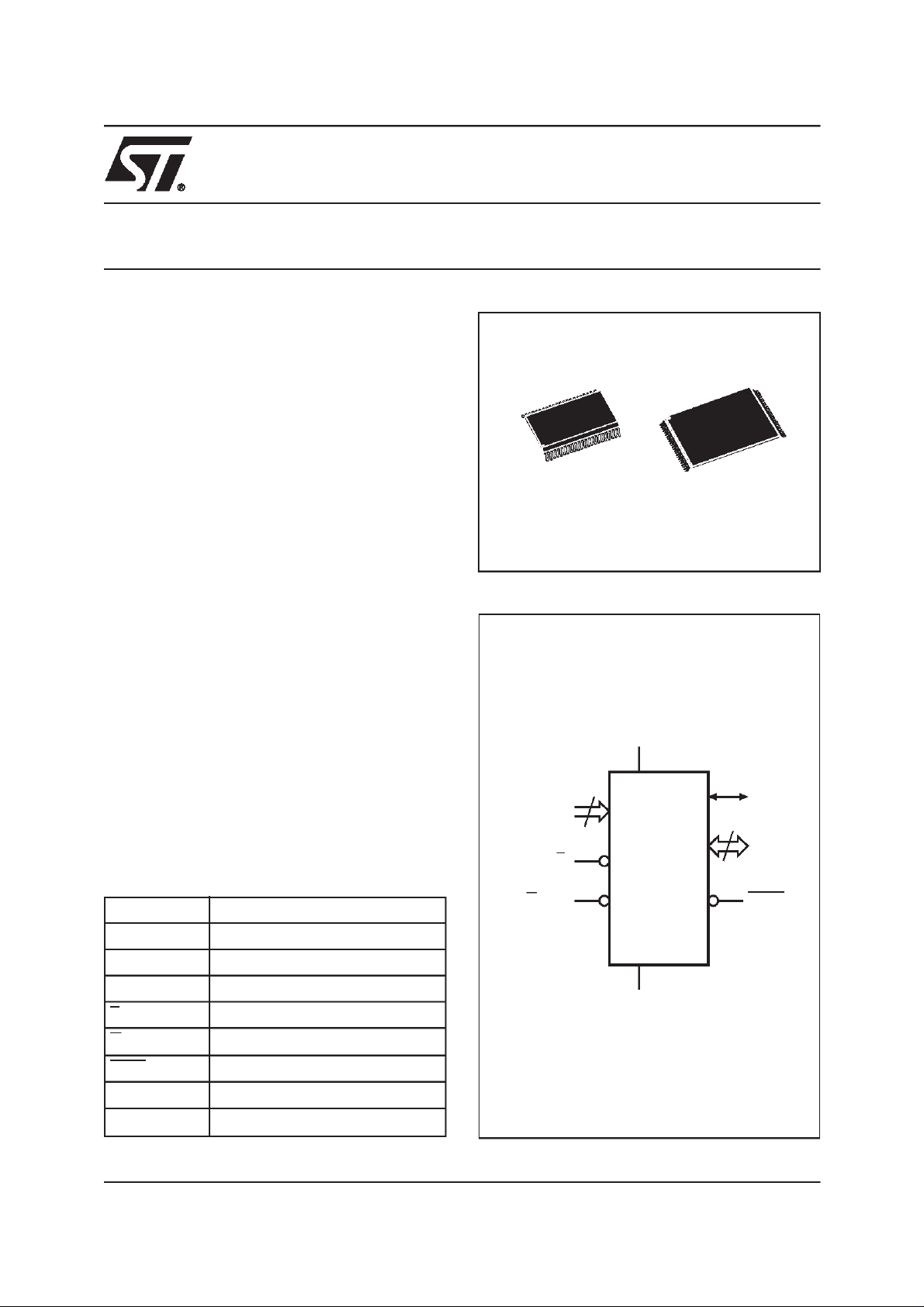

32 Mbit (4Mb x8 or 2Mb x16) OTP EPROM

■ 5V ± 10% SUPPLY VOLTAGE in READ

OPERATION

■ FAST ACCESS TIME: 80ns

■ BYTE-WIDE or WORD-WIDE

CONFIGURABLE

■ 32 MbitMASK ROM REPLACEMENT

■ LOW POWER CONSUMPTION

– Active Current70mA at 8MHz

– Stand-by Current 100mA

■ PROGRAMMING VOLTAGE: 12V ± 0.25V

■ PROGRAMMING TIME: 100µs/byte

(typical)(PRESTO III Algorithm)

■ ELECTRONIC SIGNATURE:

– Manufacturer Code0020h

– Device Code: 0032h

M27C320

PRELIMINARY DATA

44

1

SO44 (M) TSOP48 (N)

12 x20 mm

Figure 1. Logic Diagram

DESCRIPTION

The M27C320 is a 32 Mbit EPROM offered in the

OTP range (one time programmable). It is ideally

suited for microprocessor systems requiring large

data or program storage. It is organised as either

4 MWords of 8 bit or 2 MWords of 16 bit. The pinout is compatible with the 32 Mbit Mask ROM.

The M27C320 is offered in TSOP48 (12 x 20mm)

and SO44 packages.

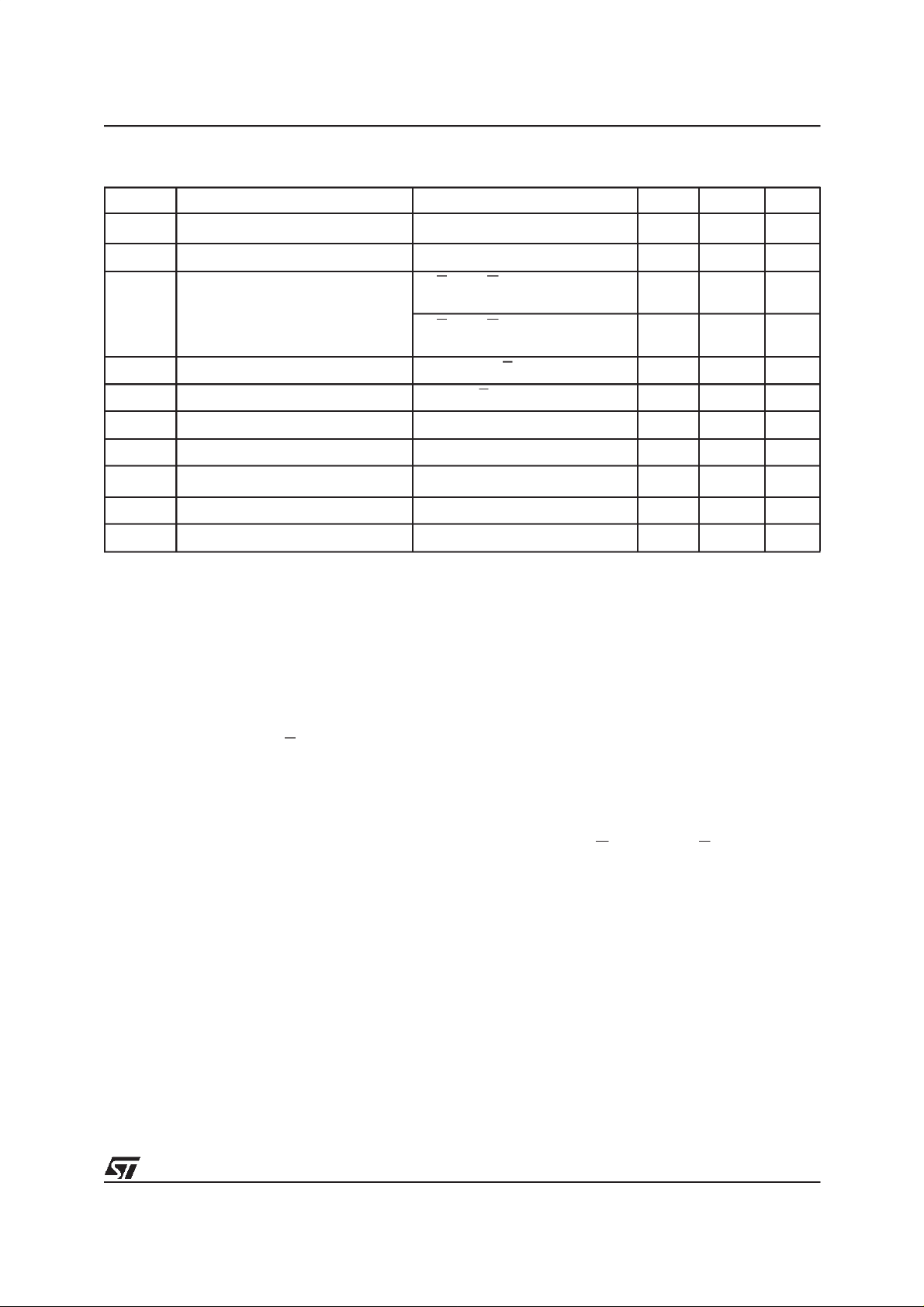

Table 1. Signal Names

A0-A20 Address Inputs

Q0-Q7 Data Outputs

Q8-Q14 Data Outputs

Q15A–1 Data Output / Address Input

E Chip Enable

GV

PP

BYTE Byte-Wide Select

V

CC

V

SS

Output Enable / Program Supply

Supply Voltage

Ground

A0-A20

GV

PP

V

CC

21

Q15A–1

15

Q0-Q14

E

M27C320

BYTE

V

SS

AI02152

September 1998

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

1/15

M27C320

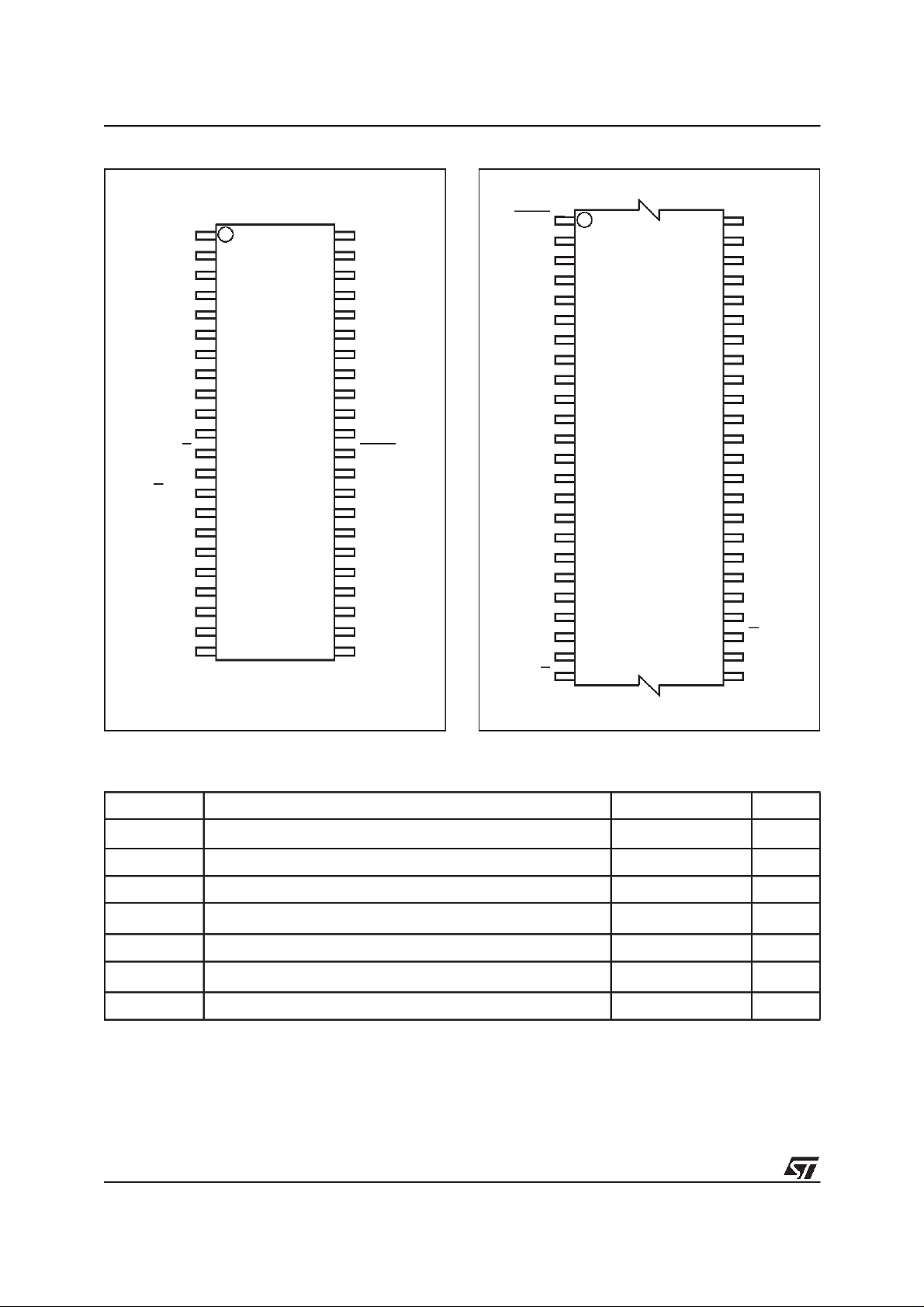

Figure 2A. SO Pin Connections

NC A20

1

2

A7

A6

A5

A4

A3

A2

A1

A0

3

4

5

6

7

8

9

10

11

12

M27C320

E

13

14

15

16

A17 A8

V

SS

GV

PP

Q0

Q8

17Q1

Q9

18

19

Q10

Q3

20

21

Q11

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

2322

AI02153

A19A18

A9

A10

A11

A12

A13

A14

A15

A16

BYTE

V

SS

Q15A–1

Q7

Q14

Q6

Q13

Q5Q2

Q12

Q4

V

CC

Figure 2B. TSOP Pin Connections

BYTE

A16

A15

A14

A13

A12

A10

A9

A8

A19

V

SS

A20

A18

A17

A7

A6

A5

A4

A2

A1

A0

1

12

M27C320

13

24 25

E

48

37

36

AI02154

V

SS

V

SS

Q15A–1

Q7

Q14

Q6

Q13A11

Q5

Q12

Q4

V

CC

V

CC

V

SS

Q11

Q3

Q10

Q2

Q9

Q1

Q8A3

Q0

GV

PP

V

SS

V

SS

Warning: NC = Not Connected.

Table 2. Absolute Maximum Ratings

Symbol Parameter Value Unit

T

A

T

BIAS

T

STG

(2)

V

IO

V

CC

(2)

V

A9

V

PP

Note: 1. Except for the rating ”Operating Temperature Range”, stresses above those listedin the Table ”Absolute Maximum Ratings” may

2/15

cause permanent damage to the device. These are stress ratings only and operation of the device atthese or any other conditions

above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periodsmay affect device reliability. Referalso to theSTMicroelectronics SUREProgram and other relevant quality documents.

2. Minimum DC voltage on Input or Output is –0.5V with possible undershoot to –2.0V for a period less than 20ns. Maximum DC

voltage on Output is V

3. Depends on range.

Ambient Operating Temperature

Temperature Under Bias –50 to 125 °C

Storage Temperature –65 to 150 °C

Input or Output Voltage (except A9) –2 to 7 V

Supply Voltage –2 to 7 V

A9 Voltage –2 to 13.5 V

Program Supply Voltage –2 to 14 V

+0.5V with possible overshoot to VCC+2V for a period less than 20ns.

CC

(1)

(3)

–40 to 125 °C

Table 3. Operating Modes

Mode E GV

Read Word-wide

Read Byte-wide Upper V

Read Byte-wide Lower

Output Disable

Program

Program Inhibit

Standby

Electronic Signature

Note: X = VIHor VIL,VID= 12V ± 0.5V.

V

V

V

V

Pulse V

IL

V

IH

V

IH

V

PP

IL

IL

IL

IL

IL

V

IL

V

IL

V

IL

V

IH

PP

V

PP

X X X Hi-Z Hi-Z Hi-Z

V

IL

BYTE A9 Q0-Q7 Q8-Q14 Q15A–1

V

IH

V

IL

V

IL

X X Hi-Z Hi-Z Hi-Z

V

IH

V

IH

V

IH

X Data Out Data Out Data Out

X Data Out Hi-Z V

X Data Out Hi-Z

X Data In Data In Data In

X Hi-Z Hi-Z Hi-Z

V

ID

Codes Codes Code

Table 4. Electronic Signature

Identifier A0 Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0 Hex Data

Manufacturer’s Code

Device Code V

Note: Outputs Q8-Q15 are set to ’0’.

V

IL

IH

00100000 20h

00110010 32h

M27C320

IH

V

IL

DEVICE OPERATION

The operatingmodes ofthe M27C320 are listed in

the OperatingModes Table.A single power supply

is required in the read mode. All inputs are TTL

compatible except for VPPand 12V on A9 for the

Electronic Signature.

Read Mode

The M27C320 has two organisations, Word-wide

and Byte-wide.The organisationis selected by the

signal level ontheBYTE pin. WhenBYTE is at V

IH

the Word-wide organisation is selected and the

Q15A–1 pin is used for Q15 Data Output. When

the BYTE pin is at VILthe Byte-wide organisation

is selected andthe Q15A–1 pin is used for the Address Input A–1. When the memory is logically regarded as 16 bit wide, but read in the Byte-wide

organisation, then with A–1 at VILthe lower 8 bits

of the 16 bit data are selected and with A–1at V

IH

the upper 8 bits of the 16 bit data are selected.

The M27C320 has two control functions, both of

which must be logically active in order to obtain

data at the outputs. In addition the Word-wide or

Byte-wide organisation must be selected.

Chip Enable (E) is thepower control andshould be

used fordevice selection.Output Enable (G) is the

output control and should be used to gate data to

the output pins independent of device selection.

Assuming that the addresses are stable, the address access time (t

from E to output (t

ELQV

output after a delay of t

) is equal to the delay

AVQV

). Data is available at the

from the falling edge

GLQV

of G, assuming that E has been low and the addresseshave beenstable for atleast t

AVQV-tGLQV

Standby Mode

The M27C320 has standby mode which reduces

the supply current from 50mA to 100µA. The

M27C320 is placedin the standby modeby applying aCMOS high signal to the Einput. Whenin the

standby mode, the outputs are in a high impedance state, independent of the G input.

.

3/15

M27C320

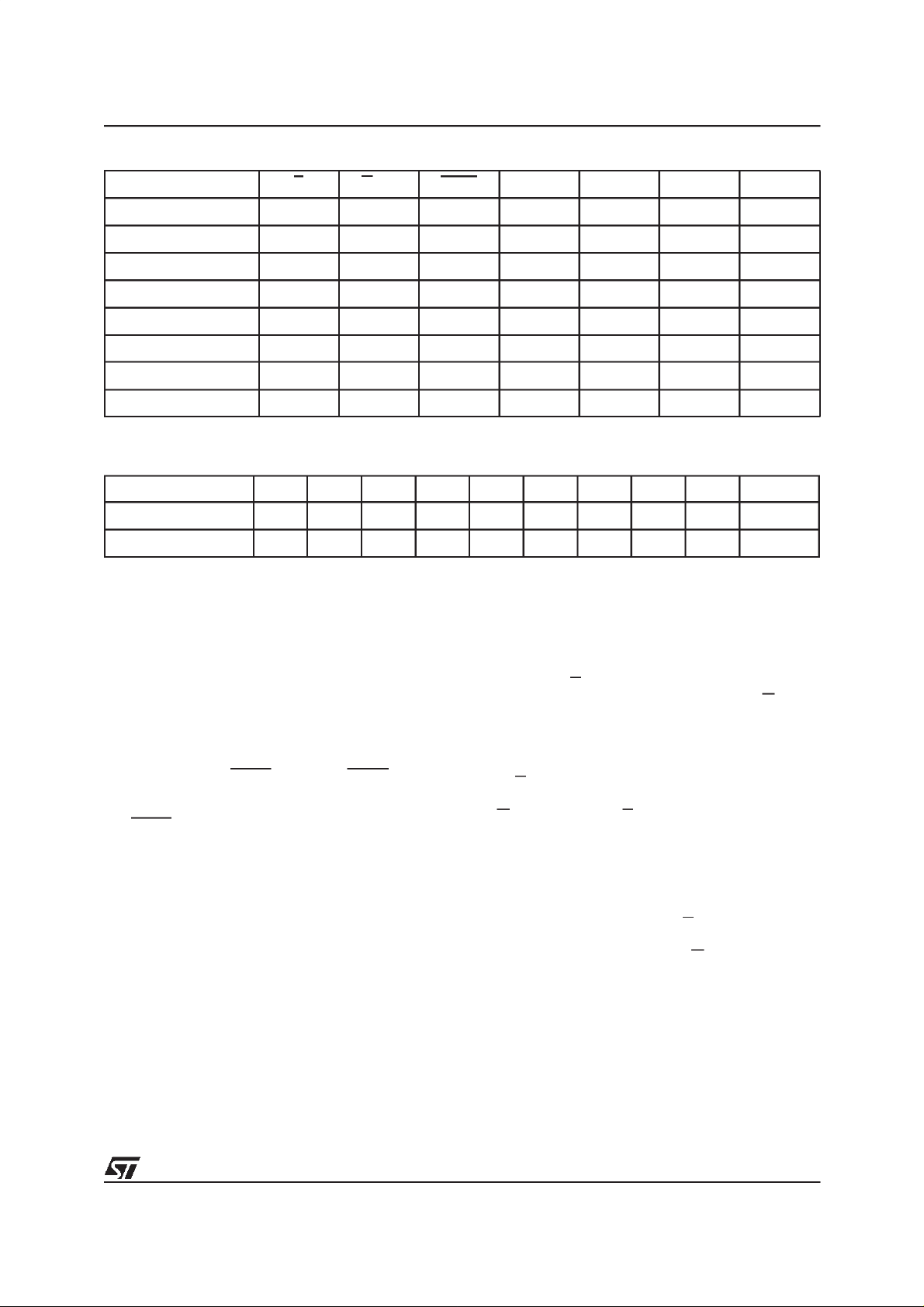

Table 5. AC Measurement Conditions

High Speed Standard

Input Rise and Fall Times ≤ 10ns ≤ 20ns

Input Pulse Voltages 0 to 3V 0.4V to 2.4V

Input and Output Timing Ref. Voltages 1.5V 0.8V and 2V

Figure 3. Testing Input Output Waveform

High Speed

3V

1.5V

0V

Standard

2.4V

0.4V

Table 6. Capacitance

(1)

(TA=25°C, f = 1 MHz)

2.0V

0.8V

AI01822

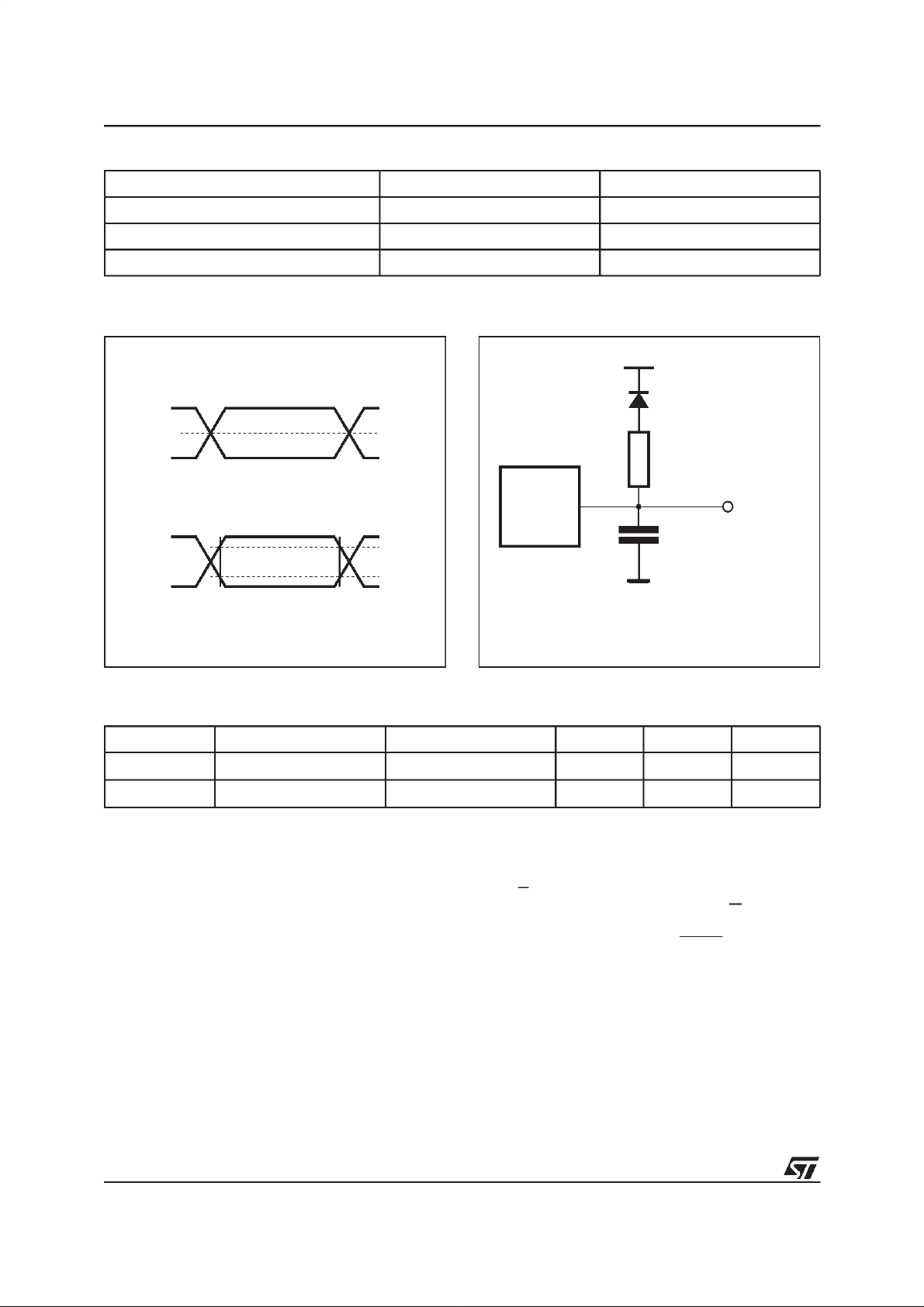

Figure 4. AC Testing Load Circuit

1.3V

1N914

3.3kΩ

DEVICE

UNDER

TEST

C

L

CL= 30pF for High Speed

CL= 100pF for Standard

CLincludes JIG capacitance

Symbol Parameter Test Condition Min Max Unit

V

C

IN

C

OUT

Note: 1. Sampled only,not 100% tested.

Input Capacitance

Output Capacitance V

=0V

IN

=0V 12 pF

OUT

10 pF

OUT

AI01823B

Two Line Output Control

Because EPROMs are usually used in larger

memory arrays, this product features a 2 line control function which accommodates the use of multiple memory connection. The two line control

function allows:

a. the lowest possible memory power dissipation,

b. complete assurance that output bus contention

will not occur.

4/15

For the most efficient use of these two control

lines, Eshould be decoded and used astheprimary device selecting function, while G should be

made a common connection to all devices in the

array and connected to the READ line from the

system control bus. This ensures that all deselected memory devices are in their low power standby

mode and that the output pins are only active

when data is required from a particular memory

device.

M27C320

Table 7. Read Mode DC Characteristics

(1)

(TA= 0 to 70 °C; VCC=5V±10%)

Symbol Parameter Test Condition Min Max Unit

I

I

I

CC

I

CC

I

CC

I

V

V

IH

V

V

Note: 1. VCCmust be applied simultaneously with or before VPPand removed simultaneously or after VPP.

Input Leakage Current

LI

Output Leakage Current

LO

Supply Current

1

Supply Current (Standby) TTL

2

Supply Current (Standby) CMOS

Program Current

PP

Input Low Voltage –0.3 0.8 V

IL

(2)

Input High Voltage 2

Output Low Voltage

OL

Output High Voltage TTL

OH

2. Maximum DC voltage on Output is V

CC

+0.5V.

E=V

E=V

0V ≤ V

IL

IL

0V ≤ V

,G=VIL,I

,G=VIL,I

E>VCC– 0.2V

I

IN

OUT

f = 8MHz

f = 5MHz

E=V

V

PP=VCC

I

= 2.1mA

OL

=–400µA

OH

≤ V

≤ V

IH

OUT

OUT

CC

CC

= 0mA,

= 0mA,

2.4 V

±1 µA

±10 µA

70 mA

50 mA

1mA

100 µA

10 µA

V

+1

CC

0.4 V

V

System Considerations

The power switching characteristics of Advanced

CMOS EPROMs require carefull decoupliing of

the suppliesto the devices. The supply current I

CC

has three segments of importance to the system

designer: the standby current, the active current

and the transient peaks that are produced by the

falling and rising edges of E.

The magnitude of the transient current peaks is

dependant on the capacititive and inductive loading of the device outputs. The associatedtransient

voltage peaks can be supressed by complying

with the two line output control and byproperly selected decoupling capacitors. It is recommended

that a 0.1µF ceramic capacitor is used on every

device between VCCand VSS. This should be a

high frequency type of low inherent inductance

and should be placed as close as possible to the

device. In addition, a 4.7µF electrolytic capacitor

should be used between VCCand VSSfor every

eight devices. This capacitor should be mounted

near the power supply connection point. The purpose of this capacitor is to overcome the voltage

drop caused by the inductive effects of PCB traces.

Programming

When delivered, allbits of the M27C320 arein the

’1’ state. Data is introduced by selectively programming ’0’s into the desired bit locations. Although only ’0’s will be programmed, both ’1’s and

’0’s can be present in the data word. The

M27C320 is in the programming mode when V

PP

input is at 12.5V, G is at VIHand Eis pulsedto VIL.

The data to be programmed isapplied to 16 bitsin

parallel to the data outputpins. Thelevels required

for the address and data inputs are TTL. VCCis

specified to be 6.25V ± 0.25V.

5/15

Loading...

Loading...