1/4June 2002

IP Library: High PSRR, Low power,

80mA Low Dropout Volt age Regulator

■

ANALOG BASEBAND REGUL AT OR

■

VERY LOW DROPOUT VOLTAGE : 50mV

■

HIGH PSRR : 60dB

■

LOW QUIESCENT CURRENT : 130µA

■

LOW OU TPU T VOLTAGE NOISE

■

NO CURRENT IN POWER DOWN MODE

■

SHORT CIRCUIT PROTECTION

■

SMALL DECOUPLING CERAMIC CAPACITOR

TYPICAL APPLICATIONS

– Cellular and Cordless phones suppli ed by 1 cell

Lithium-ion battery / 3 cells Ni-MH or Ni-Cd

battery.

– PDA (Personal Digital Assistant), Smart phone.

– Portable equipm ent.

– Supply for Analog and Mixe d-signal devices f or

cellular phone.

APPLICATION NOTE

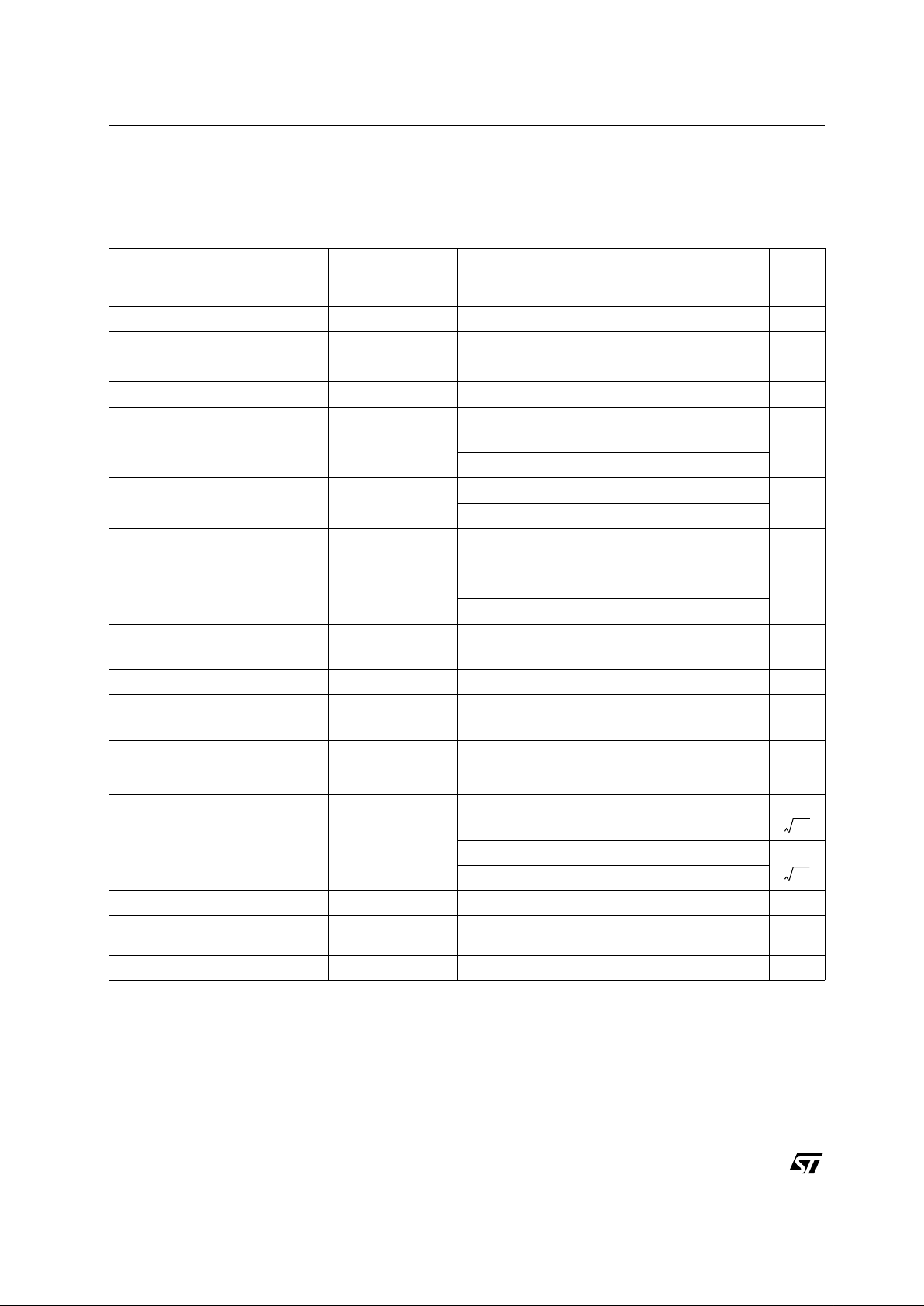

An external capacitor (C

OUT

= 1µF) with an

equivalent serial resistance (ESR) in the range

0.02 to 0.6Ω is used for regulator stability.

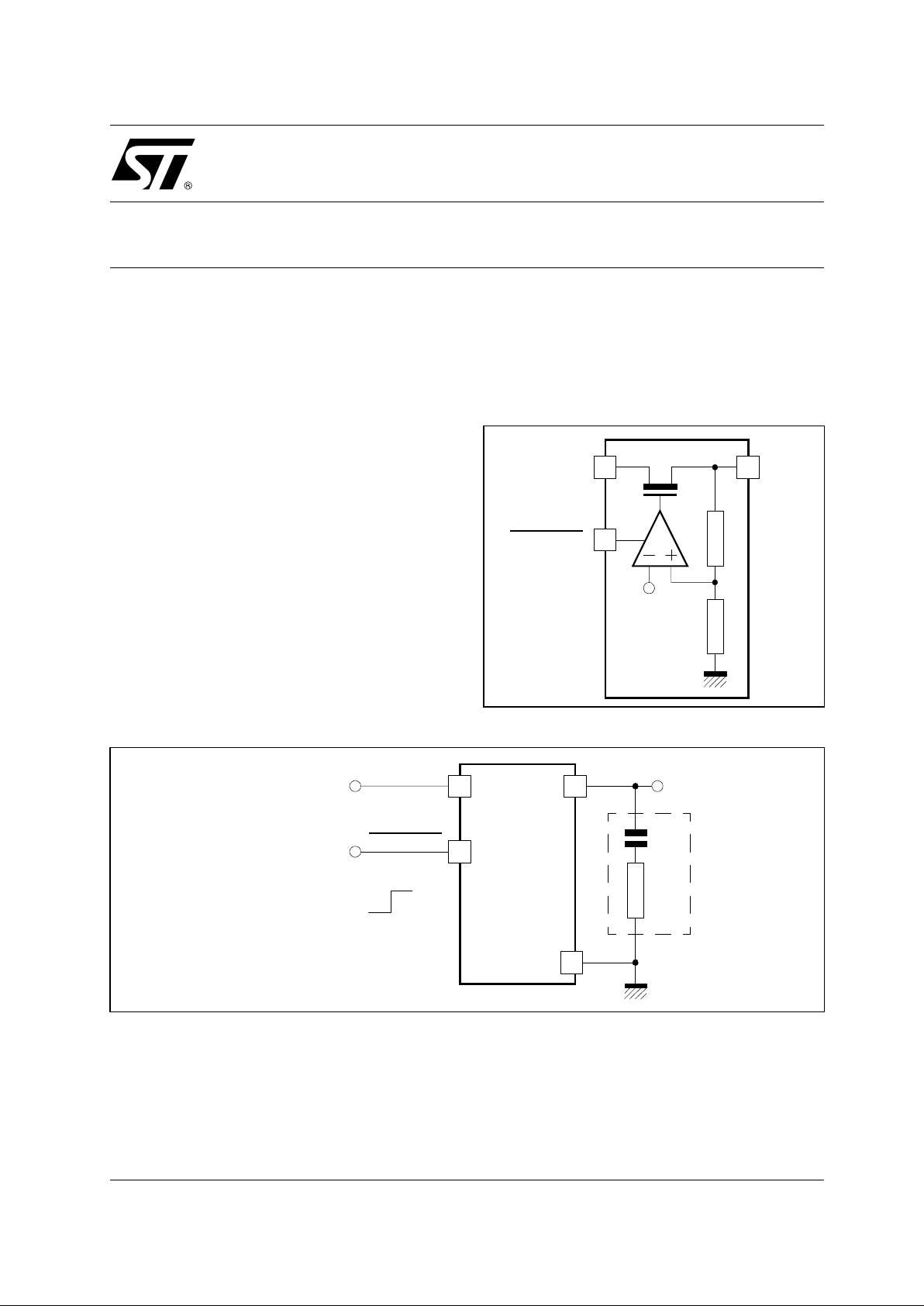

Figure 1 :

Block Diagram

?

V

REF

?

?

LDO_51

OUTIN

PWRDWN

Figure 2 :

Typical Application Circuit

1µF

ESR

V

OUT

C

OUT

?

?

OUT

GND

?

?

V

IN

IN

Power Dow n Mode

OFF

ON

LDO_51

PWRDWN

LDO_51

This is advance information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

PRODUCT PREVIEW

LDO_51

2/4

ELECTRICAL CHARACTERISTICS

3V < V

IN

< 5.5V, -55°C < TA < +125°C, V

REF

= 2.8V, 0.8µF < C

OUT

< 1.2µF, 20mΩ < ESR < 0. 6Ω.

100µA < I

LOAD

< 80mA.

Typical case :

V

IN

= 4V, T = 25°C, I

OUT

= 40mA.

Notes: 1. Above characteristics are given for 3V minimum input operating range voltage, but regulator is

operational with 2.7V minimum input voltage.

2. All parameters are guaranteed with 170mV Dropout voltage.

Parameter Symbol Test Condition Min Typ Max Unit

Input Voltage Range (Note 1) V

IN

3 5,5 V

Output Voltage V

OUT

2,8 V

Output Voltage Accuracy -3 3 %

Output current I

OUT

0,1 80 mA

P

MOS

Output Resistance R

ON

0,5 Ω

Dropout Voltage ∆V

DO

∆V

OUT

= 50mV,

I

LOAD

= 80mA

50 mV

(Note 2) 170

Quiescent current I

Q

I

LOAD

= 100µA3050µA

I

LOAD

= 80mA 130 170

Power down mode

quiescent current

I

QPDM

Power down active 100 nA

Power Supply Rejection Ratio PSRR f < 10KHz 50 60 dB

f < 100KHz 40 50

Line Regulation Lir I

LOAD

= 80mA,

V

IN

= 3V to 5.1V

36mV

Load Regulation Ldr 30 45 mV

Line Transient Lirt ∆VIN = 300mV

t

RISE

= t

FALL

= 10µs

1mV

Load Transient Ldtr 10% to 90%

and 90% to 10%

of 80mA in 10µs

1mV

Output Noise Voltage en 100Hz 1,5

1KHz 550

100KHz 300

Output decoupling Capacitor C

OUT

1 µF

Settling time From power down to

active mode

25 µs

Short Circuit Current Limit I

SHORT

180 230 300 mA

µV

Hz

----------- -

nV

Hz

----------- -

Loading...

Loading...