Page 1

Octal Low-Side Driver for resistive and inductive loads with

serial/parallel input control, output protection and diagnostic

■

OUTPUTS CURRENT CAPABILITY UP TO

500mA, R

■

PARALLEL CONTROL INPUTS FOR

OUTPUTS 1 AND 2

■

SPI CONTROL FOR OUTPUTS 1 TO 8

■

RESET FUNCTION WITH RESET SIGNAL AT

NRES PIN OR UNDERVOLTAGE AT V

■

- INTRINSIC OUTPU T VOLTAG E C LA MPING

AT TYP. 50V

■

OVERCURRENT SHUTDOWN AT OUTPUTS

3 TO 8

■

SHORT CIRCUIT CURRENT LIMITATION

AND SELECTIVE THERMAL SHUTDOWN AT

OUTPUTS 1 AND 2

■

OUTPUT STATUS DATA AVAILABLE ON THE SPI

= 2.2Ω AT TJ = 25°C

ON

CC

L9826

SO20 (16+2+2)

ORDERING NUMBER: L9826

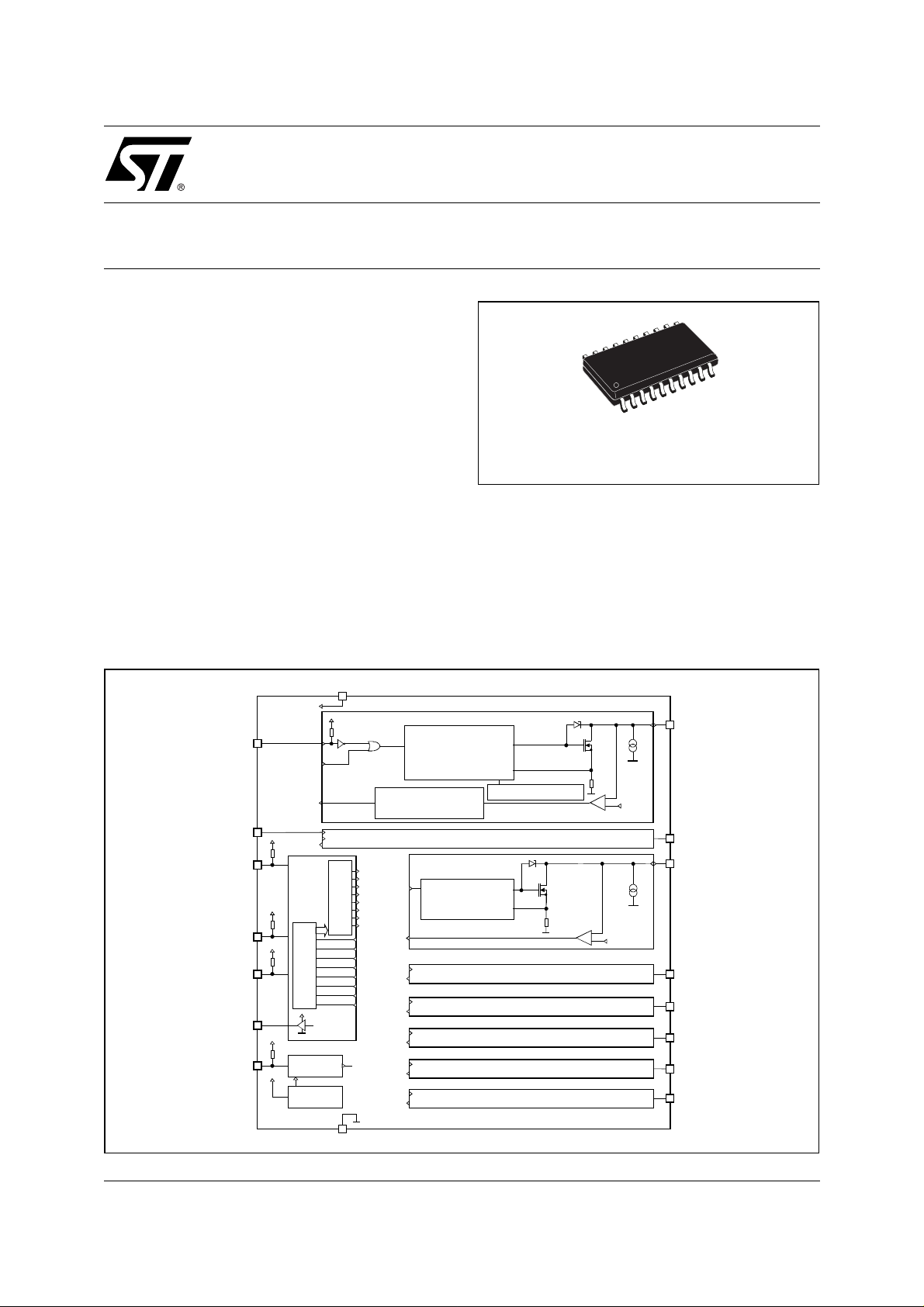

DESCRIPTION

The L9826 is a Octal Low-Side Driver Circuit, dedicated

for automotive applications. Output voltage clamping is

provided for flyback current recirculation, when inductive loads are driven. Chip Select and Serial Peripheral

Interface for outputs control and diagnostic data transfer. Parallel Control inputs for two outputs.

BLOCK DIAGRAM

NON1

NON2

NCS

CLK

SDI

SDO

nRES

V

CC

V

CC

V

CC

V

CC

V

CC

Q1

Diag1

Q2

Diag2

SPI

Interface

Shift Register

V

CC

Reset

Undervoltage

RESET

V

CC

V

CC

1

3

S

2

Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

Output Latc h

Diag1

Diag2

Diag3

Diag4

Diag5

Diag6

Diag7

Diag8

Reset

Latch / Driver

Fault Latch

S

Q3

Diag3

Q4

Diag4

Q5

Diag5

Q6

Diag6

Q7

Diag7

Q8

Diag8

R

Overtemperature Detection

Latch / Driver

+

-

V

DG

R

+

-

V

DG

I

OL

CH1

CH2

I

OL

CH3

CH4

CH5

CH6

CH7

CH8

OUT1

OUT2

OUT3

OUT4

OUT5

OUT6

OUT7

OUT8

October 2002

GND

1/12

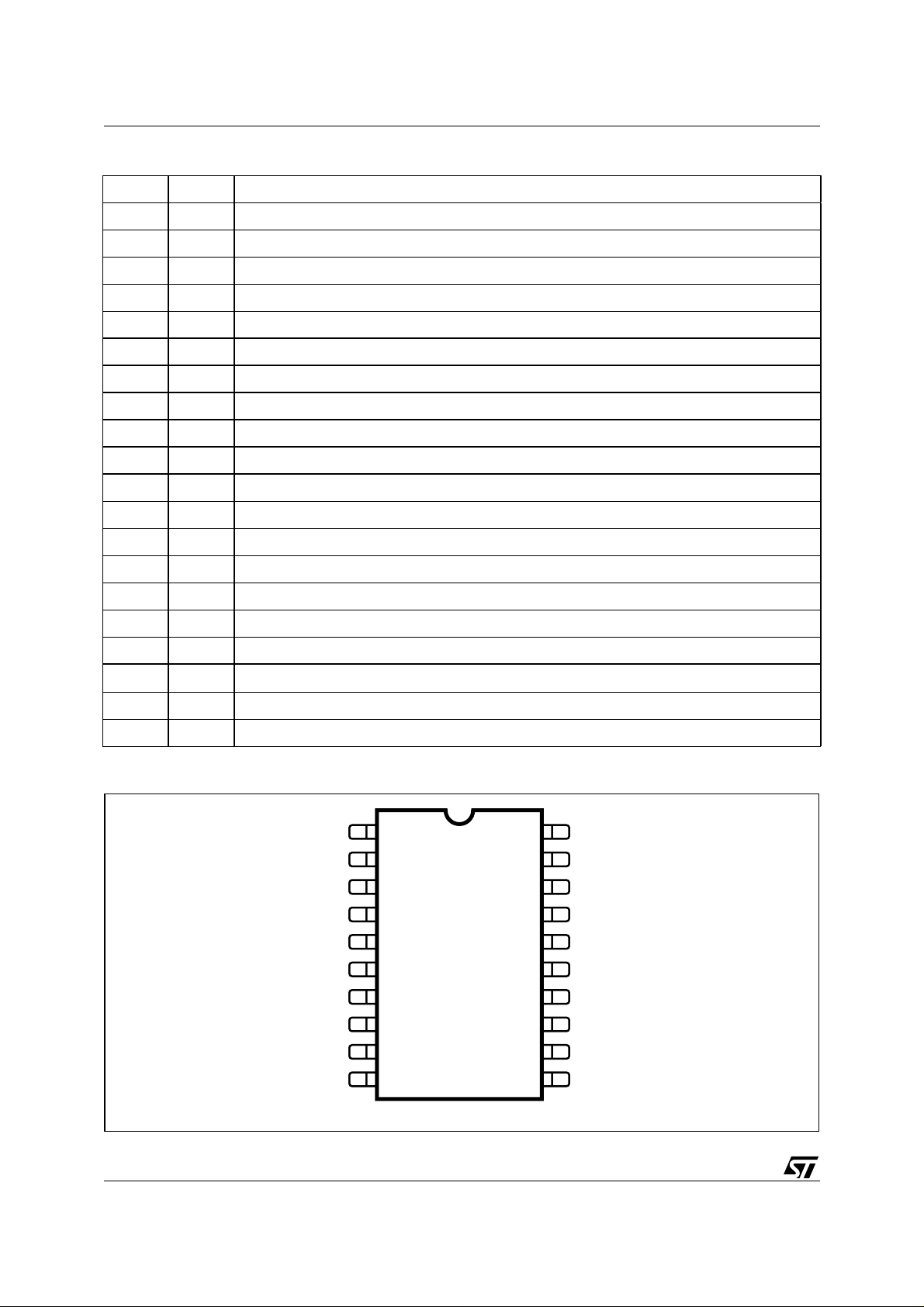

Page 2

L9826

PIN FUNCTION

N° Pin Description

1 Out 6 output 6

2 Out 1 output 1

3 nRes asynchronous nRes

4 NCS chip select (active low)

5 GND device ground

6 GND device ground

7 NON1 control input 1

8 SDO serial data output

9 Out 8 output 8

10 Out 3 output 3

11 Out 5 output 5

12 Out 2 output 2

13 SDI serial data input

14 CLK serial clock

15 GND device ground

16 GND device ground

17 NON2 control input 2

18 V

19 Out 7 output 7

20 Out 4 output 4

PIN CONNECTIONS

CC

supply voltage

(Top view)

OUT6

OUT1

nRES

NCS

GND

GND

NON1

20

2

3

4

5

6

7

19

18

17

16

15

14

OUT41

OUT7

Vcc

NON2

GND

GND

CLK

2/12

SDO

OUT8 OUT2

OUT3 OUT5

8

9

10

PINCON_L9826

13

12

11

SDI

Page 3

L9826

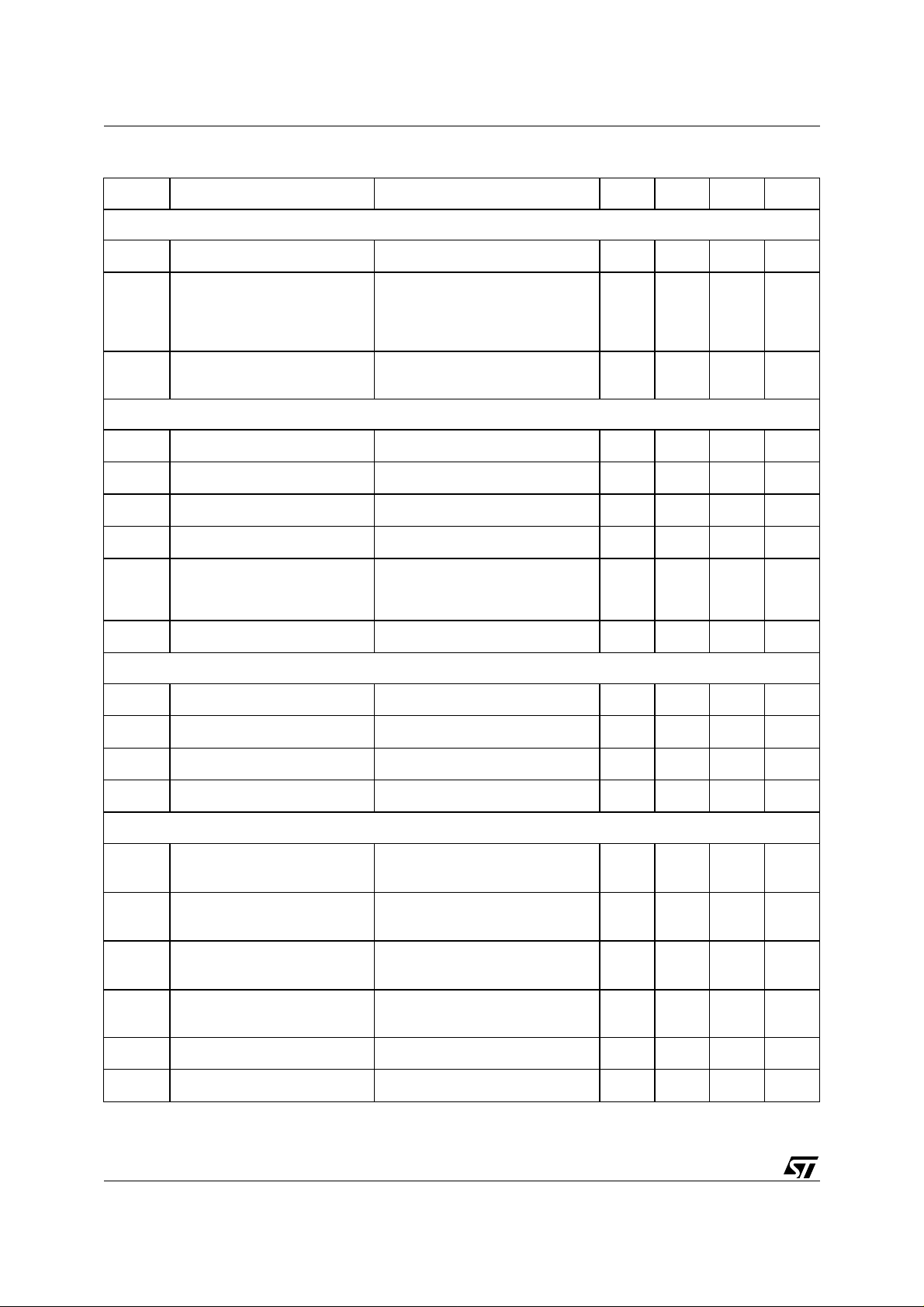

ABSOLUTE MAXIMUM RATINGS

For voltages and currents applied externally to the device

Symbol Parameter Test Condition Min. Typ. Max. Unit

CC

Supply voltage

-0.3 7 V

V

Inputs and data lines

(NONx, NCS, CLK, SDI, nRes)

V

Voltage

IN

-0.3 7 V

(NONx, NCS, CLK, SDI, nRes)

I

IN

Protection diodes current

1)

T ≤ 1ms -20 20 mA

Outputs (Out1 ... Out8)

V

OUTc

I

OUT

E

OUTcl

Notes: 1. All inputs are protected against ES D according to MIL 883C; tested with HBM at 2KV. It cor responds to a dissipated energy E £

Continuous output voltage -1,0 45 V

Output current

Output clamp energy I

0,2mJ.

2. Transient pulses in accordance to D IN40839 part 1, 3 and ISO 7637 P art 1, 3.

2)

≤ 250mA 10 mJ

OUT

-2 1,0 A

For currents determined within the device:

Symbol Parameter Test Condition Min. Typ. Max. Unit

Outputs (Out1 ... Out8)

I

OUT

Output current (Out1 ... Out8) 1,0 A

∑

I

OUTi

Total average-current all outputs

3)

2.0 A

i = 1-8

3. When op eratin g t he dev ic e with sh ort c ircui t at more t han 2 out puts at t he sam e tim e, dama ge d ue to elec tric al ov erstre ss may

occur.

THERMAL DATA

Symbol Parameter Test Condition Min. Typ. Max. Unit

Thermal shutdown

T

Thermal resistance

R

thjA-one

R

thjA-all

R

thj-pin

Thermal shutdown threshold 150 165 °C

JSC

Single output (junction ambient) 90 °C/W

All outputs (junction ambient) 75 °C/W

Junction to Pin 18 °C/W

3/12

Page 4

L9826

ELECTRICAL CHARACTERISTCS

(4.5V ≤ VCC ≤ 5,5V; -40°C ≤ TJ ≤ 150°C; unless otherwise specified)

Symbol Parameter Test Condition Min. Typ. Max. Unit

Supply voltage

I

ccSTB

I

ccOPM

Standby current without load (nRes = Low) 70 µA

Operating mode I

OUT1 ... 8

= 500mA

5mA

SPI - CLK = 3MHz

NCS = LOW

SDO no load

∆I

CC

during reverse output

∆I

CC

I

= -2A 100 mA

out

current

Inputs

(NONx. NCS, CLK, SDI, nRes)

V

V

V

R

Low level -0.3

INL

High level

INH

Hysteresis voltage 0.85 V

hyst

Input current VIN = V

I

IN

Pullup resistance

IN

CC

0.7·V

CC

-10 10 µA

50 250 kΩ

0.2·V

CC

VCC+0,3

(NONx, NCS, CLK, SDI)

Pulldown resistance (nRes)

V

V

C

Input capacitance 10 pF

IN

Serial data outputs

V

SDOH

V

SDOL

I

SDOL

C

High output level I

Low output level I

Tristate leakage current

Output capacitance f

SDO

Outputs OUT 1 ... 8

I

OUTL1 - 8

I

OUTL1 - 8

I

OUTL1 - 8

V

R

DSon

C

Leakage current OUTx = OFF; V

Leakage current OUTx = OFF; V

Leakage current OUTx = OFF; V

Output clamp voltage

clp

On resistance OUT 1 ... 8 I

Output capacitance V

OUT

= -4mA

SDO

= 3,2mA 0.4 V

SDO

NCS = high; 0V ≤ V

= 300kHz 10 pF

SDO

V

= 5V

CC

V

= 5V

CC

V

= 1V

CC

1mA ≤ I

≤ I

clp

outp

OUTx

OUTx

OUTx

; I

test

≤ V

SDO

= 25V;

= 16V;

= 16V;

= 10mA

CC

with

VCC -0.4

-10 10 µA

100 µA

100 µA

10 µA

45 62 V

correlation

= 500mA; Tj = +150°C 3.0 Ω

OUT

= 16V; f = 1MHz 300 pF

OUT

V

4/12

Page 5

L9826

ELECTRICAL CHARACTERISTCS

(continued)

Symbol Parameter Test Condition Min. Typ. Max. Unit

Outputs short circuit protection

I

SBC

I

t

SCB

Overcurrent shutoff threshold OUT3 ... OUT8 0.45 1.1 A

Short circuit current limitation OUT1; OUT2 0.5 1,0 A

LIM

Delay shutdown for output 3 ... 8; I

OUT

≤ 1/2 I

SCB

0.2 3,0 12 µs

Diagnostics

V

I

Diagnostic threshold voltage 0.32·V

DG

Open load detection sink

OL

V

= V

out

DG

0.4·V

CC

C

C

20 100 µA

current

t

Diagnostic detection filter time

df

15 50 µs

for output 1 & 2 on each

diagnostic condition

Outputs timing

t

don1

Turn ON delay of OUT 1 and 2 NON

NCS = 50% to V

= 50% to V

1, 2

OUT

= 0,9·V

OUT

= 0,9·V

bat

bat

5µs

V

t

don2

t

dU

dU

dU

dU

Turn ON delay of OUT 3 to 8 NCS = 50% to V

Turn OFF delay of OUT 1 to 8 NCS = 50% to V

doff

Turn ON voltage slew-rate For output 3 to 8; 90% to 30% of

on1/dt

Turn ON voltage slew-rate For output 1 and 2; 90% to 30% of

on2/dt

Turn OFF voltage slew-rate For output 1 to 8; 30% to 90% of

off1/dt

Turn OFF voltage slew-rate For output 1 to 8; 30% to 80% of

off2/dt

Serial diagnostic link

f

t

t

pcld

Clock frequency 50% duty cycle 3 MHz

clk

Minimum time CLK = HIGH 160 ns

clh

Minimum time CLK = LOW 160 ns

t

cll

Propagation delay

CLK to data at SDO valid

t

csdv

NCS = LOW to data at SDO

active

NON

V

V

V

V

= 50% to V

1, 2

; RL = 500Ω; V

bat

; RL = 500Ω; V

bat

; RL = 500Ω; V

bat

; RL = 500Ω; V

bat

(Load capacitor at SDO = 100pF)

4,9V ≤ VCC ≤ 5,1V 100 ns

OUT

OUT

= 0,9·V

= 0,1·V

OUT

= 16V

bat

= 16V

bat

= 16V

bat

= 0.9 · V

bat

bat

bat

= 0,1·V

10 µs

10 µs

bat

0.7 3.5 V/µs

2 10 V/µs

2 10 V/µs

2 15 V/µs

clp

100 ns

t

sclch

CLK low before NCS low Setup time CLK to NCS change H/L 100 ns

5/12

Page 6

L9826

ELECTRICAL CHARACTERISTCS

Symbol Parameter Test Condition Min. Typ. Max. Unit

t

hclcl

t

t

hcld

t

sclcl

t

hclch

t

pchdz

CLK change L/H after NCS =

low

SDI input setup time CLK change H/L after SDI data

scld

SDI input hold time

CLK low before NCS high 150 ns

CLK high after NCS high 150 ns

NCS L/H to output data float 100 ns

NCS pulse filter time Multiple of 8 CLK cycles inside

(continued)

valid

SDI data hold after CLK change H/L

NCS period

100 ns

20 ns

20 n s

FUNCTIONAL DESCRIPTION

General

The L9826 integrated circuit features 8 power low-side-driver outputs. Data is transmitted to the device using

the Serial Peripheral Interface, SPI protocol. Outputs 1 and 2 can be controlled parallel or serial. The power

outputs features voltage clamping function for flyback current recirculation and are protected against short circuit to Vbat.

The diagnostics recognizes two outputs fault conditions: 1) over curr ent for outpu ts 3 to 8 , over current and thermal overload for outputs 1 and 2 in switch-on co ndition and 2) open load or short to GND in switch- off condition

for all outputs. The outputs status can be read out via the serial interface.

The chip internal reset is a OR function of the external nRes signal and internall y gener ated underv oltage nRes

signal.

Output Stages Control

Each output is controlled with its latch and with common reset line, which enables all eight outputs. Outputs 1

and 2 can be controlled also by its NON1, NON2 inputs. It allows PWM control independently on the SPI. These

inputs features internal pull-up resistors to assure that the outputs are switched off, when the inputs are open.

The control data are transmitted via the SDI input, the timing of the serial interface is shown in Fig. 1.

The device is selected with low NCS signal and the input data are transferred into the 8 bit shift register at every

falling CLK edge. The rising edge of the NCS latches the new data from the shift register to the drivers.

6/12

Page 7

L9826

Figure 1. Timing of the Serial Interface.

NCS

tsclch thclcl tclh tcll tsclcl thclch

CLK

tcsdv tpcld tpchdz

SDO

SDI

The SPI register data are transfer red to the output l atch at r ising N CS edge. The digital filter between NCS and

the output latch ensures that the data are transferred only after 8 CLK cycles or multiple of 8 CLK cycles since

the last NCS falling edge. The NCS changes only at low CLK.

Outputs Control Tables :

Outputs 1, 2: Outputs 3 to 8:

not defined D8 D1

tscld

thcld

D8 D7 D1

NON1, 2 1001

SPI-bit 1, 2 0011 SPI-bit 3 ... 8 0 1

Output 1, 2 off on on on Output 3 ... 8 off on

Figure 2. Out put C on t rol regi st er s tructure

MSB LSB

Q2 Q4 Q6 Q8 Q1 Q3 Q5 Q7

Control-bit output 7

Control-bit output 5

Control-bit output 3

Control-bit output 1

Control-bit output 8

Control-bit output 6

Control-bit output 4

Control-bit output 2

7/12

Page 8

L9826

Power outputs characteristics

for flyback current, outputs short circuit protection and diagnostics

For output currents flowing into the circuit the output vol tages are limited. The ty pical value of this vo ltage is 50V.

This function allows that the flyback current of a inducti ve load r ecircul ates into the circui t; the flyback energy is

absorbed in the chip.

Output short circuit protection for outputs 3 to 8 (dedicated for loads without inrush current): when the output

current exceeds the short circuit threshold, the corresponding output overload latch is set and the output is

switched off immediately.

Output short circuit protection for outputs 1 and 2 (dedicated for loads with inrush current, as lamps): when the

load current would exceed the short circuit limit value, the corresponding output goes in a current regulation

mode. The output current is determined by the output characteristics and the output voltage depends on the

load resistance. In this mode high power is dissipated in the output transis tor and its temperatur e increases rapidly. When the power transistor temperatur e exceeds the thermal shutdow n threshold, the ov erload latch is set

and the corresponding output switched off.

For the load diagnostic in output off condition each output features a diagnostic current sink, typ 60µA.

Diagnostics

The output voltage at all outputs is compared with the diagnostic threshold, typ 0,38 · V

.

CC

Outputs 1 and 2 features dedicated fault latches. The output status signal is filtered and latched. The fault latches are cleared dur ing NCS low. The latch stores the status bi t, so the first reading after the er ror occ urred might

be wrong. The second reading is right.

Diagnostic Table for outputs 1 and 2 in parallel controlled mode:

Output 1, 2 Output-voltage Status-bit Output-mode

off > DG-threshold high correct operation

off < DG-threshold low fault condition 2)

on < DG-threshold high correct operation

on > DG-threshold low fault condition 1)

Fault condition 1) "output short circuit to Vbat" : the output was switched on and the voltage at the output exceeds the diagnostics threshold. The output operates in current regulation mode or has been switched off due

to thermal shutdown. The status bit is low.

Fault condition 2) "open load" or "output short circuit to GND" : the output is switched off and the voltage at the

output drops below the diagnostics threshold, because the load current is lower than the output diagnostic current source, the load is interrupted. The diagnostic bit is low.

For outputs 3 to 8 the output status signals, are fed directly to the SPI register.

Diagnostic Table for outputs 1 to 8 in SPI controlled mode:

Output 1 ... 8 Output-voltage Status-bit Output-mode

off > DG-threshold high correct operation

off < DG-threshold low fault condition 2)

on < DG-threshold low correct operation

on > DG-threshold high fault condition 1)

8/12

Page 9

L9826

The fault condition 1) "output short circuit to Vbat" : the output was switched on and the voltage at the output

exceeded the diagnostics threshold due to overcurrent, the output overload latch was set and the output has

been switched off. The diagnostic bit is high.

Fault condition 2) "open load" or "output short circuit to GND" is the same as of outputs 1 and 2.

At the falling edge of NCS the output status data are transferred to the shift register. When NSC is low, data bits

contained in the shift register are transferred to SDO output et every rising CLK edge.

Figure 3. The Pulse Diagram to Read the Outputs Status Register

NCS

CLK

SDO

SDI

MSB LSB654321

MSB LSB654321

Figure 4. The Structure of the Outputs Status Register

MSB LSB

Diag2Diag4Diag6Diag8Diag1Diag3Diag5Diag7

Diagnostic-bit output 7

Diagnostic-bit output 5

Diagnostic-bit output 3

Diagnostic-bit output 1

Diagnostic-bit output 8

Diagnostic-bit output 6

Diagnostic-bit output 4

Diagnostic-bit output 2

9/12

Page 10

L9826

APPLICATION INF ORMATION

The typical application diagram is shown in Fig. 5.

Figure 5. Typical Application Circuit Diagram for the L9826 Circuit.

µP

V

CC

V

CC

V

CC

NON1

NON2

NCS

CLK

SDI

SDO

nRES

V

CC

V

CC

V

CC

V

CC

V

CC

Q1

Diag1

Q2

Diag2

SPI

Shift Register

V

CC

Reset

Undervoltage

RESE T

Interface

1

3

S

2

Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

Output Latch

Diag

Diag

Diag

Diag4

Diag

Diag

Diag

Diag8

Reset

Fault Latch

Q3

Diag

3

1

2

3

Q4

5

Diag

4

6

7

Q5

Diag

5

Q6

Diag

6

Q7

Diag7

Q8

Diag8

Latch / Driver

S

Latch / Driver

R

Overtemperature Detection

R

+

V

-

DG

CH

CH2

+

-

V

CH3

DG

CH4

CH5

CH6

CH7

CH8

L9826

GND

SDI

SDO

CLOCK

NCS2 ... 7

NRES

I

OL

1

I

OL

VOLTAGE

REGULATOR

OUT1

OUT2

OUT3

OUT4

OUT5

OUT6

OUT7

OUT8

R, L loads

V

BAT

L9826

For higher current driving capability two outputs of the same kind can be paralleled. In this case the maximum

flyback energy should not exceed the limit value for single output.

The immunity of the circuit with respect to the transients at the output is verified during the characterization for

Test Pulses 1, 2 and 3a, 3b, DIN40839 or ISO7637 part 3. The Test Pulses are coupled to the outputs with

200pF series capacitor. All outputs withstand testpulses without damage.

The correct function of the c ircuit with t he Test Pulses coupled to the outputs is verified during the characterization for the typical application with R = 30

Ω

to 100Ω, L= 0 to 600mH loads. The Test Pulses are coupled to the

outputs with 200pF series capacitor.

10/12

Page 11

L9826

DIM.

MIN. TYP. MAX. MIN. TYP. MAX.

A 2.35 2.65 0.093 0.104

A1 0.1 0.3 0.004 0.012

B 0.33 0.51 0.013 0.020

C 0.23 0.32 0.009 0.013

D 12.6 13 0.496 0.512

E 7.4 7.6 0.291 0.299

e 1.27 0.050

H 10 10.65 0.394 0.419

h 0.25 0.75 0.010 0.030

L 0.4 1.27 0.016 0.050

K 0˚ (min .)8˚ (max.)

mm inch

OUTLINE AND

MECHANICAL DATA

SO20

B

e

D

1120

110

L

h x 45˚

A

K

A1

C

H

E

SO20MEC

11/12

Page 12

L9826

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences

of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted

by implic ation or oth erwise under any patent or patent rights of STMicroel ectronics. S pecificati ons mentioned in this publicati on are subje ct

to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not

authorized for use as critical components in life support devices or systems wi t hout express written approval of STMicroelectro nics.

The ST logo is a registered trademark of STMicroelectronics

2002 STMi croelectr oni cs - All Rights Reserved

Australia - Brazil - Canada - China - F i nland - Franc e - Germany - Hong Kong - India - Israel - Ita l y - Japan -Mal aysia - Malta - Morocco -

Singap ore - Spain - Sw eden - Switze rl and - United K i ngdom - United States.

STMicroelectronics GROUP OF COMPANIES

http://www.s t. com

12/12

Loading...

Loading...