SGS Thomson Microelectronics L6918ADTR, L6918D Datasheet

5 BIT PROGRAMMABLE MULTIPHASE CONTROLLER

■

OUTPUT CURRENT IN EXCESS OF 100A

■

ULTRA FAST LOAD TRANSIEN T RESP ONSE

■

REMOTE SENSE BUFFER

■

INTEGRATED 2A GATE DRIVERS

■

5 BIT VID VOLTAGE POSITI ONING, VRM 9.0

■

0.6% INTERNAL REFERENCE ACCURACY

■

DIGITAL 2048 STEP SOFT-START

■

OVP & OCP PROTECTIONS

■

Rdson or Rsense CURRENT SENSING

■

1200KHz EFFECTIVE SWITCHING

FREQUENCY, EXTERNALLY AD JUSTABLE

■

POWER GOOD OUTPUT AND INHIBIT

■

PACKAGE: SO28

APPLICATIONS

■

HIGH DENSITY DC-DC FOR SERVERS AND

WORKSTATIONS

■

SUPPLY FOR HIGH CURRENT

MICROPROCESSORS

■

DISTRIBUTED POWER

L6918 L6918A

SO28

ORDERING NUMBERS: L6918D, L6918AD

L6918DTR, L6918ADTR

DESCRIPTION

L6918A is a master devi ce that it has to be combined

with the L6918,slave, realizing a 4-phases topology,

interleaved. The device kit is specifically designed to

provide a high performance/high densit y DC/DC conversion for high current microprocessors and distributed power. Each device implements a dual-phase

step-down controller with a 180° phas e-shift between

each phase.

A precise 5-bit DAC allows adjusting the output voltage from 1.100V to 1.850V with 25mV binary steps.

The high peak current gate drives affords to have

high system switching frequency, typically of

1200KHz, and higher by external adjustement.

The device kit assure a fast protection against OVP,

UVP and OCP. An internal crowbar, by turning on the

low side mosfets, elimi nates the ne ed of external protection. In case of over-current, the system works in

Constant Current mode.

PIN CONNECTIONS

LGATE1

1

VCCDR

2

PHASE1

3

UGATE1

4

BOOT1

5

VCC

6

SGND

7

COMP

8

FB

9

VPROG_OUT

SYNC_OUT

SLAVE_OK

October 2002

ISEN1

PGNDS1

10

11

12

13

14

L6918A

PGND

28

27

26

25

24

23

22

21

Master)

(

20

19

18

17

16

15

LGATE2

PHASE2

UGATE2

BOOT2

PGOOD

VID4

VID3

VID2

VID1

VID0

OSC / INH / FAULT

ISEN2

PGNDS2

LGATE1

1

VCCDR

2

PHASE1

3

UGATE1

4

BOOT1

5

VCC

6

SGND

7

COMP

8

FB

VSEN

FBR

FBG

ISEN1

PGNDS1

L6918

9

10

11

12

13

14

28

27

26

25

24

23

22

21

(Slave)

20

19

18

17

16

15

PGND

LGATE2

PHASE2

UGATE2

BOOT2

PGOOD

VPROG_IN

SYNC_IN

SLAVE_OK

SYNC / ADJ

SYNC_OUT

OSC / INH / FAULT

ISEN2

PGNDS2

1/35

L6918 L6918A

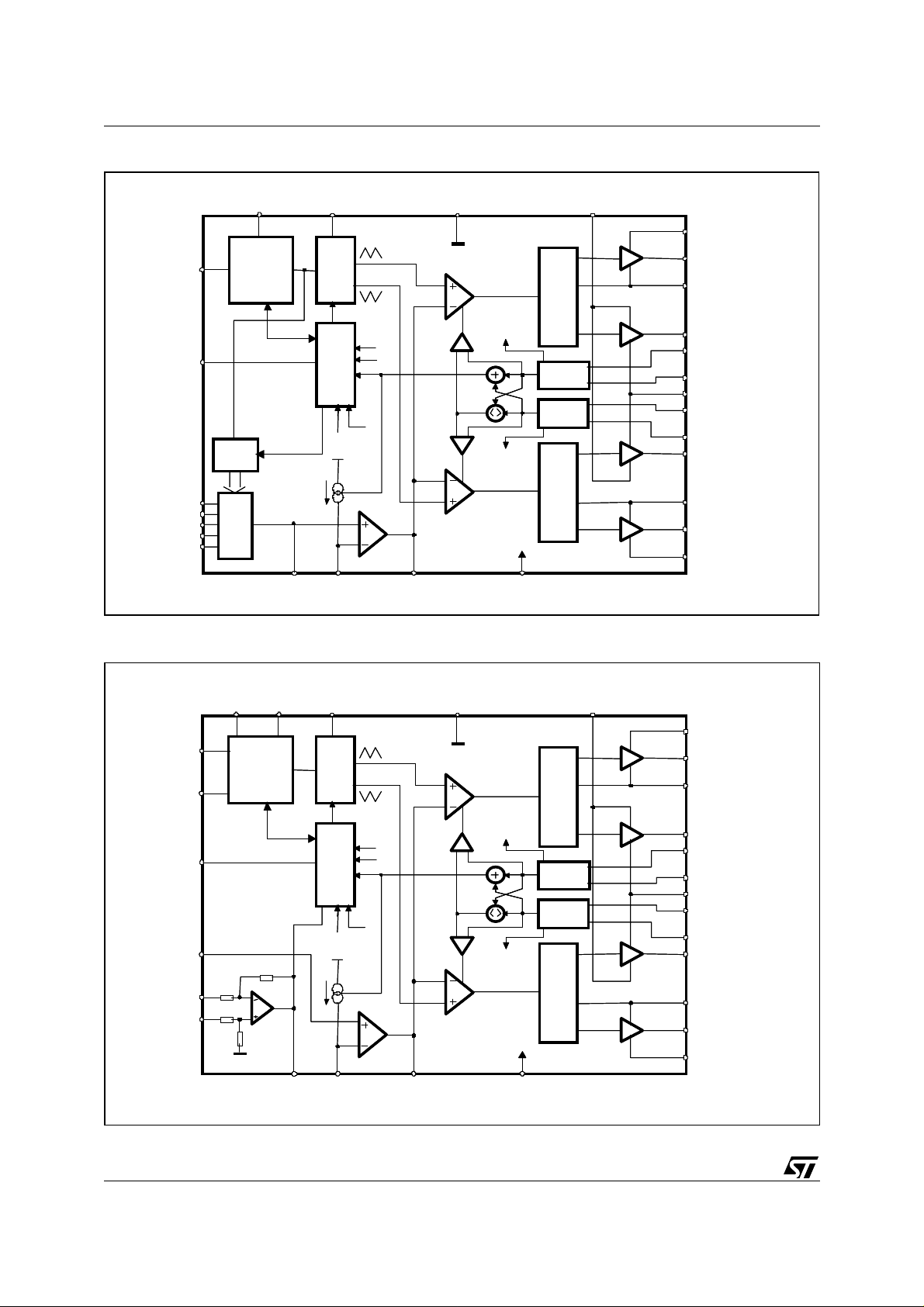

L6918A (MASTER) DEVICE BLOCK DIAGRAM

SYNC_ OU T

SLAVE_OK

SLAVE_OK

PGOOD

PGOOD

VID4

VID4

VID3

VID3

VID2

VID2

VID1

VID1

VID0

VID0

SYNC_ OU T

CIRCUITRY

CIRCUITRY

DIGITAL

DIGITAL

SOFT- START

SOFT- S TAR T

DAC

DAC

SYNC H.

SYNC H.

ROSC / INH SGND VCCDR

ROSC / INH SGND VCCDR

2 PHASE

2 PHASE

OSCILLATOR

OSCILLATOR

VCC

VCC

VCCDR

VCCDR

LOGIC AND

LOGIC AND

PROTECTIONS

PROTECTIONS

CH2 OCP

CH2 OCP

CH1 OCP

CH1 OCP

I

I

FB

FB

ERROR

ERROR

AMPLIFIER

AMPLIFIER

TO TAL

TO TAL

CURRENT

CURRENT

PWM1

PWM1

CURRENT

CURRENT

PWM2

PWM2

BOOT1

BOOT1

HS

HS

LOGIC PWM

LOGIC PW M

LOGIC PW M

ADAPT IVE AN TI

ADAPTI VE AN TI

Vcc

Vcc

ADAPTI VE AN TI

CROS S CO NDU CT I ON

CROS S CO NDU CT I ON

CROS S CO NDU CT I ON

CURRENT

CURRENT

CURRENT

READING

READIN G

READIN G

CURRENT

CURRENT

CURRENT

READING

READING

READING

LOGIC PW M

LOGIC PW M

LOGIC PW M

ADAPTI VE ANTI

ADAPTI VE ANTI

ADAPTI VE ANTI

CROS S CONDU CT ION

CROS S CONDU CT ION

CROS S CONDU CT ION

LS

LS

HS

HS

LS

LS

CH1

CH1

OCP

OCP

CURRENT

CURRENT

COR RECTIO N

COR RECTIO N

AVG

AVG

CH2

CH2

OCP

OCP

CURRENT

CURRENT

COR RECTIO N

COR RECTIO N

VccCOMPFBVSEN

VccCOMPFBVSEN

UGATE1

UGATE1

PHAS E1

PHAS E1

LGATE1

LGATE1

ISEN1

ISEN1

PGNDS1

PGNDS1

PGND

PGND

PGNDS2

PGNDS2

ISEN2

ISEN2

LGATE2

LGATE2

PHAS E2

PHAS E2

UGATE2

UGATE2

BOOT2

BOOT2

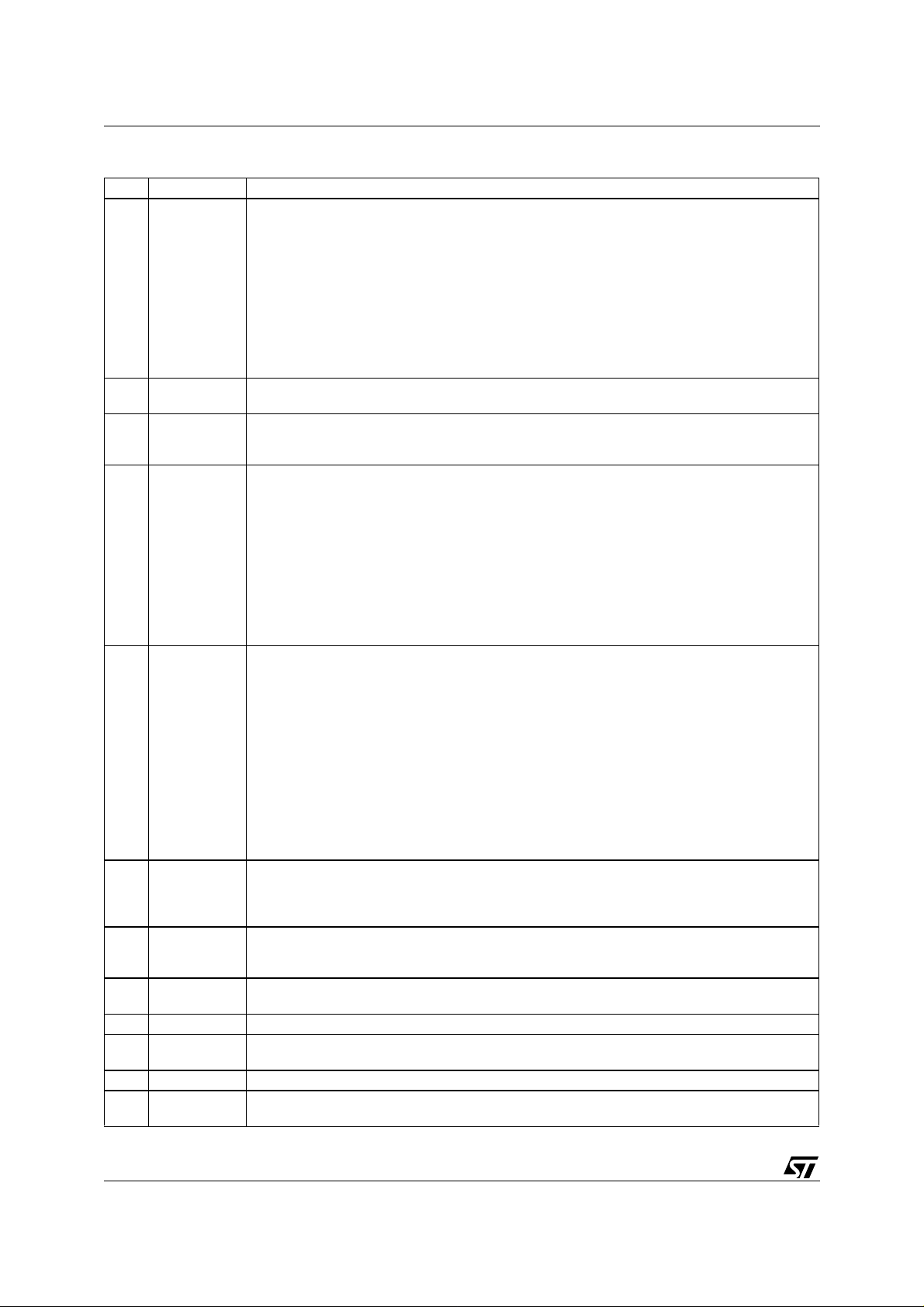

L6918 (SLAVE) DEVICE BLOCK DIAGRAM

CIRCUITRY

CIRCUITRY

10k

10k

10k

10k

10k

10k

SYNC_O UT

SYNC_O UT

SYNCH.

SYNCH.

10k

10k

REMOTE

REMOTE

BUF FER

BUF FER

R O SC / IN H SG N D V C C DR

R O SC / IN H SG N D V C C DR

2 PHASE

2 PHASE

OSCILLATOR

OSCILLATOR

VCC

VCC

VCC DR

VCC DR

LOGIC AND

LOGIC AND

PROTECTIONS

PROTECTIONS

CH2 OCP

CH2 OCP

CH1 OCP

CH1 OCP

I

I

FB

FB

ERROR

ERROR

AMPLIFIER

AMPLIFIER

VSEN

VSEN

VSEN

VSEN

SYNC_IN

SYNC_IN

SLAVE_OK

SLAVE_OK

PGOOD

PGOOD

VPROG_IN

VPROG_IN

FBG

FBG

FBR

FBR

SLAVE / ADJ

SLAVE / ADJ

TO TAL

TO TAL

CURRENT

CURRENT

PWM1

PWM1

CURRENT

CURRENT

PWM2

PWM2

BOOT1

BOOT1

HS

HS

LOGIC PW M

LOGIC PW M

LOGIC PW M

ADAPTI VE AN TI

ADAPTI VE AN TI

Vcc

Vcc

ADAPTI VE AN TI

CROSS CONDUCTION

CROSS CONDUCTION

CROSS CONDUCTION

CURRENT

CURRENT

CURRENT

READING

READING

READING

CURRENT

CURRENT

CURRENT

READING

READING

READING

LOGIC PW M

LOGIC PW M

LOGIC PW M

ADAPTI VE ANTI

ADAPTI VE ANTI

ADAPTI VE ANTI

CROSS CONDUCTION

CROSS CONDUCTION

CROSS CONDUCTION

LS

LS

HS

HS

LS

LS

CH1

CH1

OCP

OCP

CURRENT

CURRENT

CORRECTION

CORRECTION

AVG

AVG

CH2

CH2

OCP

OCP

CURRENT

CURRENT

CORRECTION

CORRECTION

VccCOMPFB

VccCOMPFB

UGATE1

UGATE1

PHAS E1

PHAS E1

LGATE1

LGATE1

ISEN1

ISEN1

PGNDS1

PGNDS1

PGND

PGND

PGNDS2

PGNDS2

ISEN2

ISEN2

LGATE2

LGATE2

PHAS E2

PHAS E2

UGATE2

UGATE2

BOOT2

BOOT2

2/35

L6918 L6918A

g

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

Vcc, V

CCDR

V

BOOT-VPHASE

V

UGATE1-VPHASE1

V

UGATE2-VPHASE2

V

PHASEx

THERMAL DATA

Symbol Parameter Value Unit

R

th j-amb

T

T

storage

P

max

T

MAX

Thermal Resistance Junction to Ambient 60 °

Maximum junction temperature 150 °

Storage temperature range -40 to 150 °

Junction Temperature Range 0 to 125 °

j

Max power dissipation at Tamb=25°C

To PGND 15 V

Boot Voltage 15 V

15 V

LGATE1, PHASE1, LGATE2, PHASE2 to PGND -0.3 to Vcc+0.3 V

VID0 to VID4 -0.3 to 5 V

All other pins to PGND -0.3 to 7 V

Sustainable Peak Voltage t<20nS @ 600kHz 26 V

2W

C / W

C

C

C

L6918A (MASTER) PIN FUNCTION

N. Name Description

1 LGATE1 Channel 1 low side gate driver output.

2 VCCDR LS Mosfet driver supply. 5V or 12V buses can be used.

3 PHASE1 This pin is connecte d to the Source of the u pper mos fet and provides the retur n pa th for the

high side driver of channel 1.

4 UGATE1 Channel 1 high side gate driver output.

5 BOOT1 Channel 1 bootst rap capacitor pin. This pin supplies the high side driver. Connect through a

capacitor to the PHASE1 pin and through a diode to Vcc (cathode vs. boot).

6 VCC Device supply voltage. The operative supply voltage is 12V.

7 GND All the internal references are referred to this pin. Connect it to the PCB signal ground.

8 COMP This pin is connected to the error amp lifier output and is used to compensate the control

feedback loop.

9 FB This pin is connected t o the error amplifier inverting input and is u sed to compensate the

voltage control feedback loop.

A current proportional to the sum of the current sensed in both channel is sourced from this pin

(50µA at full load, 70µA at th e Over Cur rent threshold ). Connectin

this pin and VSEN pin allows programming the droop effect.

10 VPROG_OUT Reference voltage output used for voltage regulation.

This pin must be connected together with the slave device VPROG_IN pin.

Filter to SGND with 1nF capacitor (a total 30nF distributed capacitance is allowed).

11 SYNC_OUT Synchronizati on output s ignal. From this pin exits a sq uare - 50% duty cycle - 5Vpp –90 deg

phase shifted wave clock signal that the Slave device PLL locks to.

Connect this pin to the Slave SYNC_IN pin.

12 SLAVE_OK Open-drain inpu t/output used for star t-up and to manage prote ctions as shown in the timing

diagram. Intern ally pulle d-up. Connect tog ether with othe r IC’s SLAVE_OK pin. Filter with 1nF

capacitor vs. SGND.

a resistor RFB between

3/35

L6918 L6918A

L6918A (MASTER) PIN FUNCTION

(continued)

N. Name Description

13 ISEN1 Channe l 1 current sense pin. The output current may be sensed across a sense resistor or

across the low-side m osfet RdsON. Th is pin ha s to be co nnect ed to the low-side mosfet drain

or to the se nse resist or through a resisto r Rg in o rder to pr ogram the cur rent inter vention for

each phase at 140% as follow:

35µAR

⋅

I

OCPx

--------------------------=

R

sense

g

Where 35µA is th e current offset infor mation relative to the Over Cur rent condition (off set at

OC threshold minus offset at zero load).The net connecting the pin to the sense point must be

routed as close as possible to the PGNDS1 net in order t o couple in common mode a ny

picked-up noise.

14 PGNDS1

Channel 1 Power Ground sense pin . The net co nnecting th e pin to th e sense poin t must be rou ted as

close as possible to the ISEN1 net in order to couple in common mode any picked-up noise.

15 PG NDS2 Channe l 2 Power Ground sense pin. The net connecting the pin to the se nse point must be

routed as clo se as poss ible to the ISEN 2 ne t in o rder to cou ple in comm on m ode any picked-

up noise.

16 ISEN2 Channe l 2 current sense pin. The output current may be sensed across a sense resistor or

across the low-s ide mos fet Rds

This pin has to be connecte d to the low-side mosfet drain

ON.

or to the se nse resist or through a resisto r Rg in o rder to pr ogram the cur rent inter vention for

each phase at 140% as follow:

35µAR

⋅

I

OCPx

--------------------------=

R

sense

g

Where 35µA is the current offset info rmation relative to the Over Current co ndition (offset at

OC threshold minus offset at zero load).

The net c onnecting the pin to the sense point mu st be routed as cl ose as possible to the

PGNDS2 net in order to couple in common mode any picked-up noise.

17 OSC/INH

FAULT

Oscillator switching fre quency pin. Conn ecting an external re sistor from this pin to GND, the

external frequency is increased according to the equation:

f

S

300KHz

14.82 10

-----------------------------+=

R

OSC

6

⋅

KΩ()

Connecting a resistor from this pin to Vcc (12V), the switching frequency is reduced according

to the equation:

f

S

300KHz

12.91 10

-----------------------------+=

R

OSC

7

⋅

KΩ()

If the pin is not connected, the switching frequency is 300KHz.

Forcing the pin to a voltage lower than 0.8V, the dev ice stop operation and enter the inhibit

state; all mosfets are turned OFF.

18

to

22

VID0-4 Voltage Identif icatio n pin s. These inpu t are inte r nally pulle d-up and TTL comp atible. They are

used to pro gram the output voltage as specified in Ta ble 1 and to set the over voltage and

power good thresholds.

Connect to GND to program a ‘0’ while leave floating to program a ‘1’.

23 PGOOD Th is pin is an op en collector outpu t and is pulled low if the output voltage is not within the

above specified thresholds. It must be connected with the Slave’s PGOOD pin.

If not used may be left floating.

24 BO OT2 Channel 2 bootstrap capac itor pin. This pin supplies the hig h side driver. Connect through a

capacitor to the PHASE2 pin and through a diode to Vcc (cathode vs. boot).

25 UGATE2 Channel 2 high side gate driver output.

26 PHASE2 This pin is connected to the source of the upper mosfet and provides the return path for the

high side driver of channel 2.

27 LGATE2 Channel 2 low side gate driver output.

28 PGND

Power ground pin. Thi s pin is common t o both s ections and it mus t be con nected th rough t he closest

path to the low side mosfets source pins in order to reduce the noise injection into the device.

4/35

L6918 L6918A

g

L6918 (SLAVE) PIN FUNCTION

N. Name Description

1 LGATE1 Channel 1 low side gate driver output.

2 VCCDR LS Mosfet driver supply. 5V or 12V buses can be used.

3 PHASE1 This pin is connect ed to the Source of the upper mosfet and provides the ret urn path for the

4 UGATE1 Channel 1 high side gate driver output.

5 BOOT1 Cha nnel 1 bootst rap capacitor pin . This pin s upplies the high s ide driver. Connect throug h a

6 VCC Device supply voltage. The operative supply voltage is 12V.

7 GND All the internal references are referred to this pin. Connect it to the PCB signal ground.

8 COMP This pin is connected to the error amplifier output and is used to compensate the control

9 FB This pin is connected to th e error amplifier inverting i nput and is used to compensate the

10 VSEN Con necte d to the ou tput voltage it is able to manag e Over & Under- voltage cond itions and the

11 FBR Remote sense buffer non-inverting input. It has to be connected to the positive side of the load

12 FBG Remote sense buffer inverting inpu t. It has to be con necte d to the nega tive side of the loa d to

13 ISEN1 Cha nnel 1 current sense pin. The output curren t may be sensed across a s ense resistor or

high side driver of channel 1.

capacitor to the PHASE1 pin and through a diode to Vcc (cathode vs. boot).

feedback loop.

voltage control feedback loop.

A current proportional to the sum of the current sensed in both channel is sourced from this pin

(50µA at full load, 70µA at the Over Current threshold). Connectin

a resistor RFB between this

pin and VSEN pin allows programming the droop effect.

PGOOD signal. It is internally connected with the output of the Remote Sense Buffer for

Remote Sense of the regulated voltage.

If no Remote Se nse is implemented, connec t it directly to the regulated voltage in ord er to

manage OVP, UVP and PGOOD.

to perform a remote sense.

If no remote sense is implemente d, conne ct direct ly to the output voltage (in this case connect

also the VSEN pin directly to the output regulated voltage).

perform a remote sense.

Pull-down to ground if no remote sense is implemented.

across the low-side mosfet Rds

This pin has to be connected to the low-side mosfet drain or

ON.

to the sense resistor through a resistor Rg in order to program the current intervention for each

phase at 140% as follow:

35µAR

⋅

I

OCPx

--------------------------=

R

g

sense

Where 35µA is the current offset information rela tive to the Over Current condition (offset at

OC threshold minus offset at zero load).

The net connecting the pin to the sense point must be routed as close a s possible to the

PGNDS1 net in order to couple in common mode any picked-up noise.

14 PGNDS1 Channel 1 Power Ground sense pin. The net connec ting the pin to the sense point must be

routed as close as possible to the ISEN1 net in order to couple in common mode any picked-up

noise.

15 PGNDS2 Channel 2 Power Ground sense pin. The net connec ting the pin to the sense point must be

routed as close as possible to the ISEN2 net in order to couple in common mode any picked-up

noise.

5/35

L6918 L6918A

g

g

L6918 (SLAVE) PIN FUNCTION

(continued)

N. Name Description

16 ISEN2 Cha nnel 2 current sense pin. The output curren t may be sensed across a s ense resistor or

across the low-side mosfet Rds

This pin has to be connected to the low-side mosfet drain or

ON.

to the sense resistor through a resistor Rg in order to program the current intervention for each

phase at 140% as follow:

35 µAR

⋅

I

OCPx

--------------------------=

R

g

sense

Where 35µA is the current offset information rela tive to the Over Current condition (offset at

OC threshold minus offset at zero load).

The net connecting the pin to the sense point must be routed as close a s possible to the

PGNDS2 net in order to couple in common mode any picked-up noise.

17 OSC/INH

FAULT

Oscillator switching frequen cy pin. Connecting an external resisto r from this pin to GND, the

external frequency is increased according to the equation:

f

S

300KHz

14.82 10

-----------------------------+=

R

OSC

6

⋅

KΩ()

Connecting a resist or from this pin to Vcc (12V ), the switching freq uenc y is reduce d according

to the equation:

f

S

300KHz

12.91 10

-----------------------------+=

R

OSC

7

⋅

KΩ()

If the pin is not connected, the switching frequency is 300KHz.

Forcing the pin to a voltage lower th an 0.8V, the device stops operation and enters the inhibit

state; all mosfets are turned OFF.

The pin is forced high when an over voltage is detected. This condition is latched; to recover it

is necessary turn off and on VCC.

18 SYNC_OUT Output synchronization signal.

while no si

nal exits when the device works as an adjustable.

A 60° phase shift si

nal exits when the device works as a Slave

19 SYNC / ADJ Slave or Adjustable operation.

Connecting this pin to GND the device becomes an adjustable two-phase controll er using an

external reference for its regulation. No soft start is implemented in this condition, so it must be

performed with exter nal circuitr y. The device switches using its intern al oscillator a ccording to

the frequency set by R

OSC

.

Leaving this pin floating, the device works as a Slave two-phase controller. It uses the

reference sourced from the master device and an internal PLL locks the synchronization signal

sourced from the master device.

20 SLAVE_OK

Open-drain output used for start-up and to manage protections as shown in the timing diagram. Internally

pulled-up. Connect together with other IC’s SLAVE_OK pin. Filter with 1nF capacitor vs. SGND.

21 SYN C_IN

Synchronization input sign al locked during the s la ve operation . Connect to the master SYNC_OUT pin.

22 VPROG_IN Reference voltage input used for voltage regulation.

This pin must be connected together with the other’s slave (if present) to the VPROG_OUT pin

of the master device.

Filter to SGND with 1nF capacitor (a total 30nF distributed capacitance is allowed).

If the device works as an Adjustable (SYNC/ADJ to GND), this is the reference used for the regulation.

23 PGOOD This pin is an open collector ou tput and is pulled low if the output voltage is not with in the

above specified thresholds. It must be connected with the master’s PGOOD pin.

If not used may be left floating.

6/35

L6918 L6918A

j

L6918 (SLAVE) PIN FUNCTION

(continued)

N. Name Description

24 BOOT2 Channel 2 bootstrap ca pacitor pin. Th is pin supplie s the high side d river. Connect through a

capacitor to the PHASE2 pin and through a diode to Vcc (cathode vs. boot).

25 UGATE2 Channel 2 high side gate driver output.

26 PHASE2 This pin is connected to the Source of the upper mosfet and provides the retur n path for the

high side driver of channel 2.

27 LGATE2 Channel 2 low side gate driver output.

28 PGND

Po w er ground pin. This pin is common to both sections and it must be connected through the closest

path to the low side mosfets source pins in order to reduce the noise injection into the device.

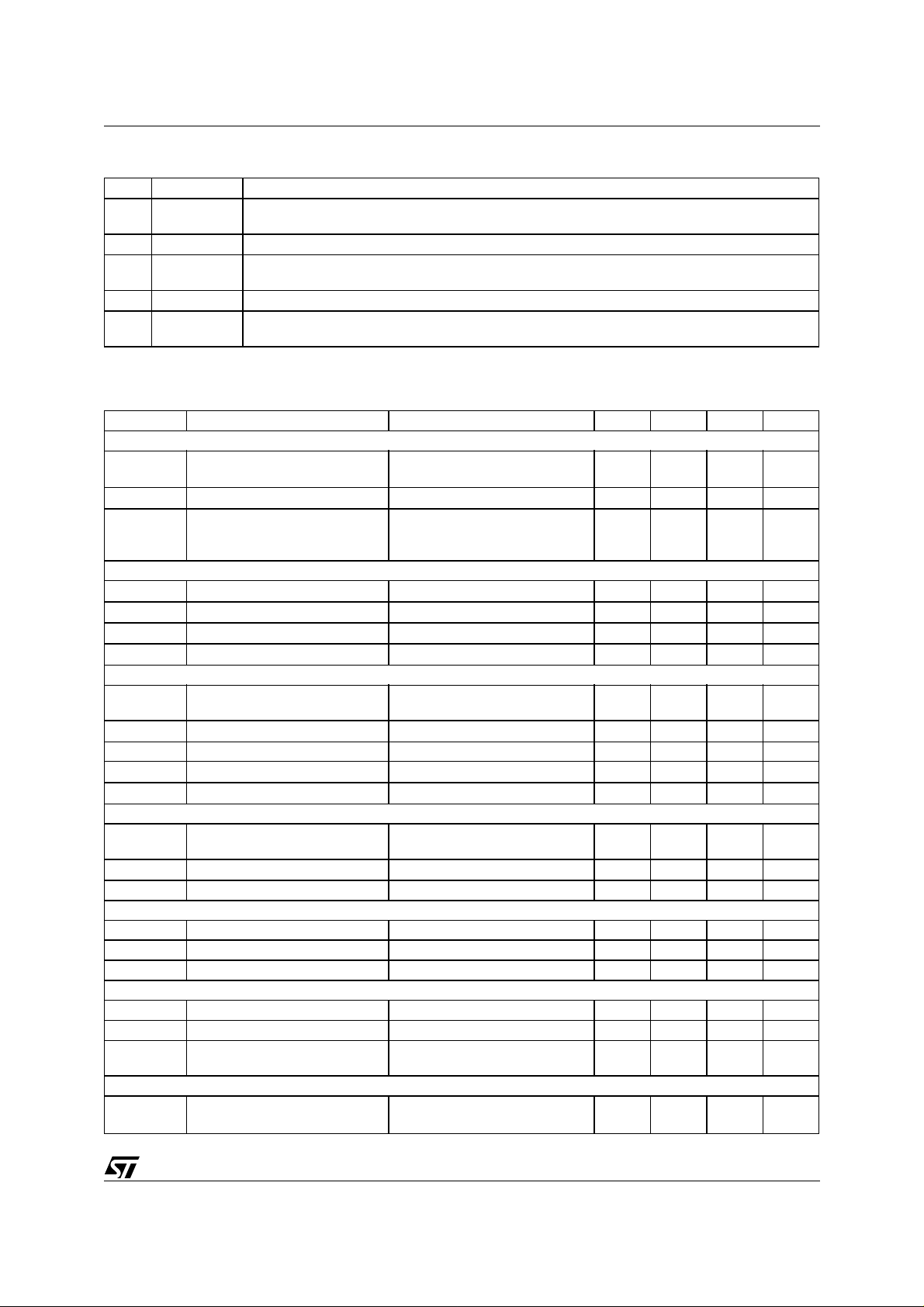

ELECTRICAL CHARACTERISTCS

(Vcc=12V±10%, TJ=0°C to 70°C unless otherwise specified)

Symbol Parameter Test Condition Min. Typ. Max. Unit

Vcc SUPPLY CURRENT

I

CC

I

CCDR

I

BOOTx

Vcc supply current HGATEx and LGATEx open

V

V

supply current LGATEx open; V

CCDR

CCDR=VBOOT

=12V

=12V 2 3 4 mA

CCDR

Boot supply current HGATEx open; PHASEx to

PGND

V

CC=VBOOT

=12V

POWER-ON

Turn-On V

Turn-Off V

Turn-On V

Turn-Off V

threshold VCC Rising; V

CC

threshold VCC Falling; V

CC

Threshold V

CCDR

Threshold V

CCDR

CCDR

CCDR

=5V 7.8 9 10.2 V

CCDR

=5V 6.5 7.5 8.5 V

CCDR

Rising; VCC=12V 4.2 4.4 4.6 V

Falling; VCC=12V 4.0 4.2 4.4 V

OSCILLATOR AND INHIBIT

f

OSC

f

OSC,Rosc

∆

Vosc

d

MAX

INH Inhibit threshold I

Initial Accuracy OSC = OPEN

Total Accuracy

OSC = OPEN; T

to GND=74k

R

T

=0°C to 125°C

Ω 450 500 550 kHz

Ramp Amplitude 2 V

Maximum duty cycle OSC = OPEN 45 50 - %

=5mA 0.8 0.85 0.9 V

SINK

REFERENCE AND DAC only for L6918A (MASTER)

V

PROG_OUT

Reference Voltage

VID0 to VID4 see Table1 -0.6 - 0.6 %

Accuracy

I

DAC

VID pull-up Current VIDx = GND 4 5 6 µ

VID pull-up Voltage VIDx = OPEN 3.1 - 3.4 V

ERROR AMPLIFIER

DC Gain 80 dB

SR Slew-Rate COMP=10pF 15

Offset -7 7 mV

DIFFERENTIAL AMPLIFIER (REMOTE BUFFER) only for L6918 (SLAVE)

DC Gain 1V/V

CMRR Common Mode Rejection Ratio 40 dB

Input Offset FBR=1.100V to1.850V;

FBG=GND

DIFFERENTIAL CURRENT SENSING

I

,

ISEN1

I

ISEN2

Bias Current I

= 0% 45 50 55 µ

LOAD

7.5 10 12.5 mA

0.5 1 1.5 mA

278

270

300 322

330

-12 12 mV

kHz

kHz

A

V/µS

A

7/35

L6918 L6918A

ELECTRICAL CHARACTERISTCS

(continued)

(Vcc=12V±10%, TJ=0°C to 70°C unless otherwise specified)

Symbol Parameter Test Condition Min. Typ. Max. Unit

I

PGNDSx

I

ISEN1

I

ISEN2

I

FB

GATE DRIVERS

t

RISE HGATE

I

HGATEx

R

HGATEx

t

RISE LGATE

I

LGATEx

R

LGATEx

PROTECTIONS

PGOOD Upper Threshold

PGOOD Lower Threshold

OVP Over Voltage Threshold

UVP Under Voltage Trip

V

PGOOD

Bias Current 45 50 55 µ

,

Bias Current at

80 85 90 µ

Over Current Threshold

Active Droop Current I

High Side

Rise Time

High Side

= 0 0 1 µ

LOAD

I

= 100% 47.5 50 52.5 µ

LOAD

V

BOOTx-VPHASEx

C

V

to PHASEx=3.3nF

HGATEx

BOOTx-VPHASEx

=10V;

15 30 nS

=10V 2 A

Source Current

High Side

V

BOOTx-VPHASEx

=12V; 1.5 2 2.5 Ω

Sink Resistance

Low Side

Rise Time

Low Side

V

=10V;

CCDR

C

V

to PGNDx=5.6nF

LGATEx

=10V 1.8 A

CCDR

30 55 nS

Source Current

Low Side

V

=12V 0.7 1.1 1.5 Ω

CCDR

Sink Resistance

V

Rising 109 112 115 %

/ VPROG_IN)

(V

SEN

/ VPROG_IN)

(V

SEN

/ VPROG_IN)

(V

SEN

/ VPROG_IN)

(V

SEN

PGOOD Voltage Low I

SEN

V

Falling 87 90 93 %

SEN

V

Rising 114 117 120 %

SEN

V

Falling 55 60 65 %

SEN

= -4mA 0.3 0.4 0.5 V

PGOOD

A

A

A

A

Table 1. VID Settings (only for L6918A)

VID4 VID3 VID2 VID1 VID0

00000

00001

00010

00011

00100

00101

00110

00111

01000

01001

01010

01011

01100

01101

01110

01111

8/35

Voltage (V)

Output

1.850

1.825

1.800

1.775

1.750

1.725

1.700

1.675

1.650

1.625

1.600

1.575

1.550

1.525

1.500

1.475

VID4 VID3 VID2 VID1 VID0

10000

10001

10010

10011

10100

10101

10110

10111

11000

11001

11010

11011

11100

11101

11110

11111

Output

Voltage (V)

1.450

1.425

1.400

1.375

1.350

1.325

1.300

1.275

1.250

1.225

1.200

1.175

1.150

1.125

1.100

Shutdown

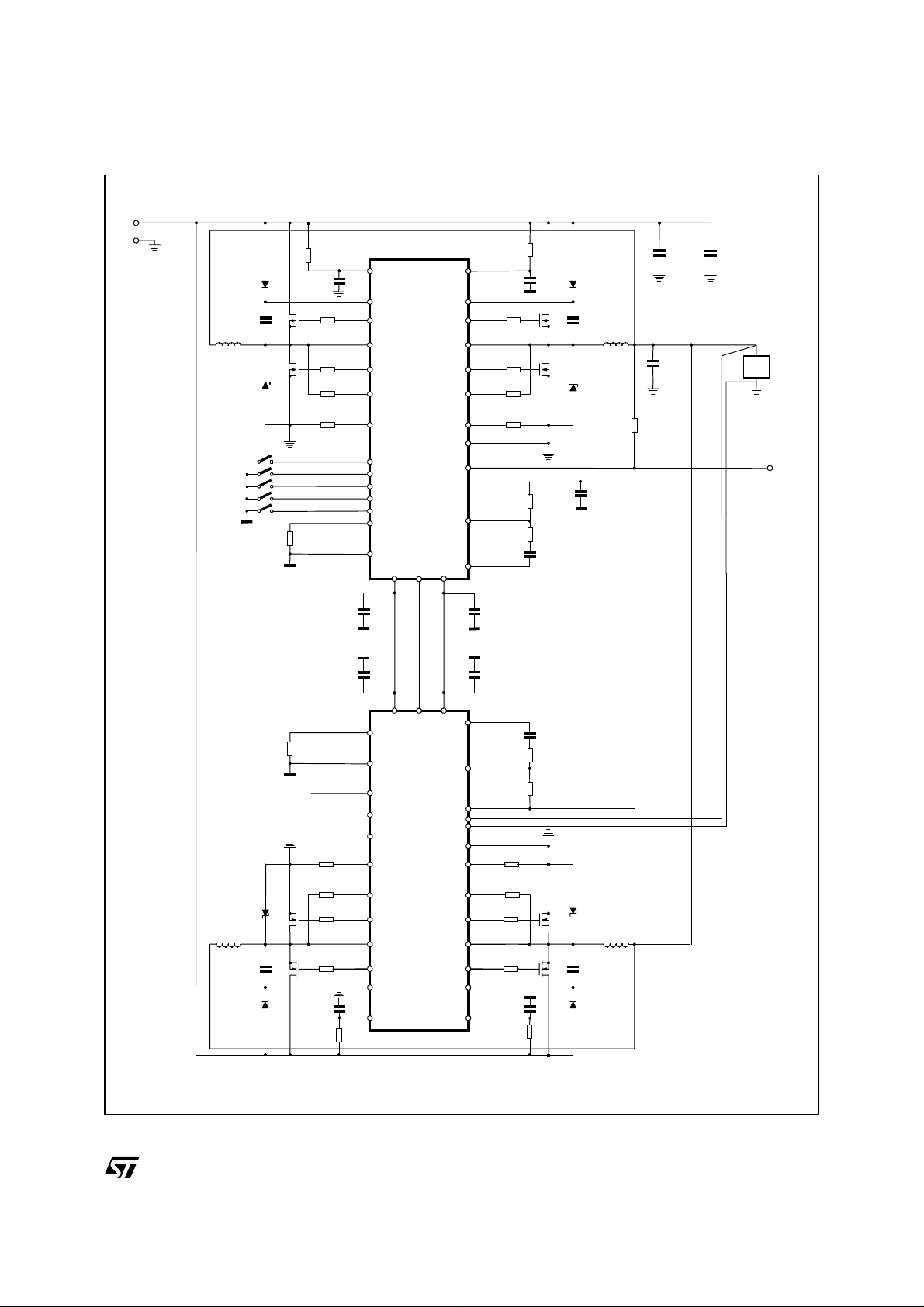

FOUR PHASE REFERENCE SCHEMATICS

g

Vin

NDin

VCCDR

2

HS1

L1

LS1

S4

S3

S2

S1

S0

UGATE1

PHASE1

LGATE1

Rg

PGNDS1

Rg

OSC / INH

BOOT1

ISEN1

VID4

VID3

VID2

VID1

VID0

SGND

VPROG_OUT

5

4

3

1

13

14

L6918A

Master

22

21

20

19

18

17

7

10

L6918 L6918A

C

VCC

6

BOOT2

24

25

26

27

16

15

28

23

11

12

SYNC_OUT

SLAVE OK

9

8

UGATE2

PHASE2

LGATE2

ISEN2

PGNDS2

PGND

PGOOD

FB

COMP

HS2

LS2

L2

Rg

Rg

R

FB

R

F

C

F

IN

C

OUT

CPU

PGOOD

SYNC_IN

VPROG_IN

SGND

ISEN1

22 21 20

17

7

23

18

19

14

L6918

13

1

3

4

5

2

Slave

OSC / INH

R2

To Slave’s

PGOOD

PGOOD

SYNC_OUT

SYNC/ADJ

Rg

PGNDS1

R

LS3

LGATE1

L3

HS3

PHASE1

UGATE1

BOOT1

VCCDR

SLAVE_OK

8

9

10

11

12

28

15

16

27

26

25

24

6

COMP

FB

VSEN

FBR

FBG

PGND

PGNDS2

ISEN2

LGATE2

PHASE2

UGATE2

BOOT2

VCC

C

F

R

F

R

F

Rg

Rg

LS4

HS4

L4

9/35

L6918 L6918A

V

R

R

DEVICES DESCRIPTION

The devices are integrated cir cui t realized i n BCD technology. They prov ide, in kit, a complete control logic and

protections sets for a high performance four-phases step-down DC-DC converter optimized for microprocessor s

supply and High Density DC-DC converters. They are designed to drive N-Channel mosfets in an interleaved

four-phase synchronous-rec tified buck topology. Each controller provi des a 180 deg phase shift betw een its two

phases and a 90deg phase-shifted syn chronizatio n signal is passed from the mas ter to the slave c ontroller that

locks the signal through a PLL. The resulting four-phases converter synchronized together results in a 90 deg

phase shift on each phase, al lowing a consistent reductio n of the input ca pacitors ripple cur rent, minimizing al so

the size and the power losses. The output voltage of the converter can be precisely regulated, programming the

master's VID pins, from 1.100V to 1.850V with 25mV binary steps. The reference for the regulation is passed

from the master device to the slave device through apposite pin likewise the synchronization signal. Each device

provides an average cur rent- mode control with fast tr ansient response. They inc lude a 300kHz free-running oscillator externally adjustable up to 600kHz, realized in order to multiply by 4 times the equivalent system frequency. The error amplifier features a 15MHz gain-bandwidth product and 10V/

converter bandwidth for fast transient performances. Current information is read in all the devices across the

lower mosfets R

or across a sense resistor in fully differential mode. The current information corrects the

DSON

PWM output in order to equalize the av erage current carried the two phases of each device. Cur rent sharing

between the two phases of each device is then limited at ±10% over static and dynamic conditions. Current

sharing between devices is assured by the droop function. The device protects against over-current, with an

OCP threshold for each phase, ent eri ng in constant cur rent mode. S ince the cur rent is read across the low s ide

mosfets, the constant current keeps c onstant the bot tom of the inductors current triangular waveform. When an

under voltage is detected the Slave device latches. The Slave device also perform an over voltage protection

that disable immediately both devices turning ON the lower driver and driving high the FAULT pin. Over Load

condition are transmitted from the Slave device(s) to the master through the SLAVE_OK line.

µ

s slew rate that permits high

MASTER - SLAVE INTERACTIONS

Figure 1. Four P has e connectio n wi th L6 918 family

ID 9.0

L6918A

L6918

Master and slave devices are connected together in order to realize four-phase high performance step-down

DC/DC converter. Four-phase c onver ter is implemented using L6918A master and one L6918 slave devices as

shown in figure 1.

A communication bus is implemented among all the controllers involved in the regulation. This bus consists in

the following lines:

Reference (VPROG_IN / VPROG_OUT pins):

–

The devices share the reference for the regulation. The reference is programmed through the master

device VID pins. It exits from the master through the VPROG_OUT pin and enters the slave device

through the VPROG_IN pin(s). Filter externally with at least 1nF capacitor.

MASTER CONTROLLE

SYNC_OUT

VPROG_OUT

SLAVE_OK

PGOOD PGOOD

OSC

Unidirectional line.

SYNC_IN

VPROG_IN

SLAVE_OK

OSC

SYNC_OUT

SLAVE CONTROLLE

10/35

L6918 L6918A

Clock Signal (SYNC_IN / SYNC_OUT pins):

–

A synchronization signal exits from the Master device through the SYNC_OUT pin with 90 deg phaseshift and enters the Slave device through the SYNC_IN pin. The Slave device locks that signal

through an internal PLL for its regulation. An auxiliary synchronizat ion signal exits from the Slave

through the SYNC_OUT.

SLAVE_OK Bus (SLAVE_OK pins):

–

Bi-directional line.

While the supply voltages are increasing, this line is hold to GND by all the devices. The Slave device

sets this line free (internally 5V pulled-up) when i t is ready for the Soft-Start. After that this line is

freed, the Master device starts the Soft Start (for further details about Soft-Start, see the relevant section).

During normal operation , the line is pulled low by the S lave d evice if an Over / Under v oltage i s detected (See relevant section).

– PGOOD pins:

PGOOD pins are connected together and pulled-up. During Soft-Start, the master device hold down

this line while during normal regulation the slave device de-assert the line if PGOOD has been lost.

Connections between the devices are shown in figure 1.

OSCILLATOR

The devices have been designed in order to operate on each phase at the same switching frequency of the internal oscillator. So, input and output resulting frequencies are four times bigger.

The oscillator is present in all the devices. Since the Master oscillator sets the main frequency for the regul ation,

the Slave oscillator gives an offset to the Slave's PLL. In this way the PLL is able to lock the synchronization

signal that enters from its SYNC_IN pin; it is able to recover up to ±15% offset in the sync hronization signal frequency. It is then necessary to program the switching frequency for all the devices involved in the multi-phase

conversion as follow.

The switching frequency is internally fixed to 300kHz. The internal oscillator generates the triangular waveform

for the PWM charging and discharging with a constant c urrent an internal capacit or. The current deliver ed to the

oscillator is typically 25

µ

A (Fsw = 300KHz) and may be varied using an external resistor (R

tween OSC pin and GND or Vcc. Since the OSC pin is maintained at fixed voltage (typ. 1.235V), the frequency

is varied proportional ly to the current sunk (forced) fr om (into) the pin consider ing the in ternal gain of 12K Hz/

In particular connecting it to GND the frequency is increased (current is sunk from the pin), while connecting

ROSC to Vcc=12V the frequency is reduced (current is forced into the pin), according to the following relationships:

Unidirectional line.

) connected be-

OSC

µ

A.

R

OSC

R

OSC

Note that forcing a 25

1.237

vs. GND:

vs. 12V:

µ

A current into this pin, the device stops switching because no current is delivered to the

fS300kHz

f

300kHz

S

----------------------------- 12

KΩ()

R

OSC

12 1.237–

----------------------------- 12

R

KΩ()

OSC

KHz

------------ 300KHz

µA

KHz

------------ 300KHz

µA

14.82 10

-----------------------------+=⋅+=

R

OSC

12.918 10

--------------------------------–=⋅+=

R

OSC

6

⋅

KΩ()

7

⋅

KΩ()

oscillator.

Figure 2 shows the frequency variation vs . the oscillator resistor ROSC considering the above repor ted relation-

ships.

11/35

Loading...

Loading...