■

SIGNAL PROCESSING

– PR4 signal equalization and loops

– 8th order optimized low pass filter with program-

mable cut-off frequency and boost

– single flash 6-bit ADC

– 5-TAP programmable/self-adaptive digital FIR

for signal equalization

– Programmable/self-adaptive Offset and MR

Head Asymmetry compensation for signal

equalization

– Timing and Gain loops f or optimu m da ta recov-

ery

– Encoder scheme:

– Rate 304/338 with Local ECC (16/17 without

Local ECC)

– Detector scheme:

– Media Noise TerminatorTM Detector

– Optional Local ECC Post Processing scheme

– 8-bit NRZ interface to disk controller

– Thermal Asperity detection/compensation and

Erasure Flag

■

WRITE

– 2 level Write Precomp for Non Linear Transition

Shift compensation

– Asynchronous and Synchronous Direct Write

for disk/head characterization

■

SERVO

– Digital Synchronous Servo with data rates up to

75MHz (8x Ovsersampling)

– Internal Burst and Grey Code detection

– Repeatable Run Out Support

L6363

PRML READ/WRITE CHANNEL

PRODUCT PREVIEW

TQFP100

ORDERING NUMBER: L6363

■

CHANNEL QUALITY MONITOR

– Fast read parameters optimization for minimum

BER

– Advanced Disk Surface Defect Scan

■

QUALITY AND RELIABILITY

– BIST for analog front-end and digital back-end

– Iddq and I/O pins mapping

■

POWER SUPPLY AND CONTROL

– 2.5V Analog and 1.8V Digital supply; 1.8V to

3.3V supply for I/O pins

– Advanced Power Management features

DESCRIPTION

L6363 is a 0.18µm CMOS PRML R/W channel supporting data rates up to 750Mb/sec with Servo Demodulation, Clock Synthesis, Channel Quality

Monitor for channel optimization and Disk Surface

Defect Scan capability

June 2001

This is preliminary information on a new product now in development. Details are subject to change without notice.

1/4

L6363

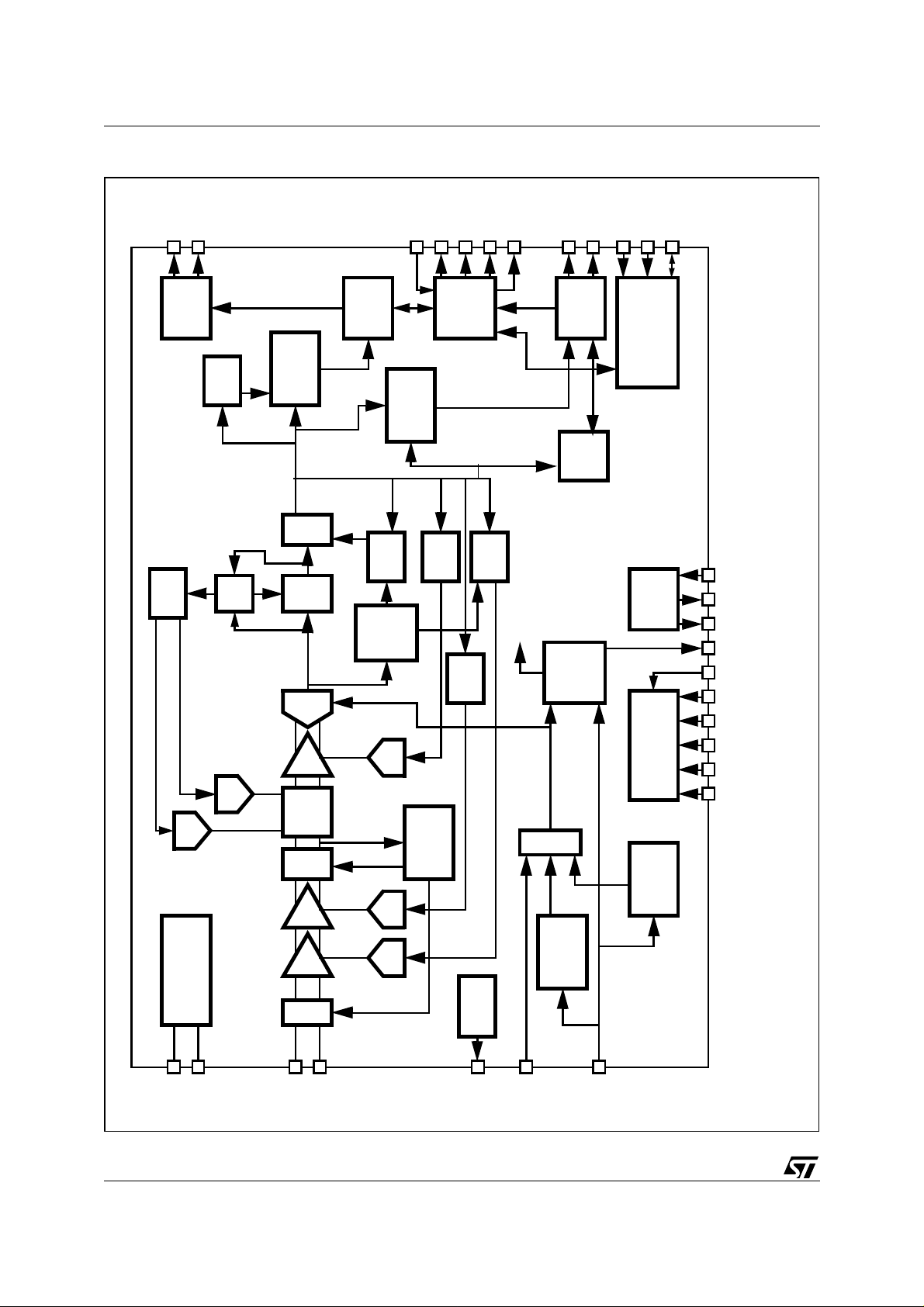

Figure 1. Block Diagram

WOP

WOM

WCLK

NRZ[7:0]

SBD*

ER_FLAG

TA_O UT

SVOCLK

SVO[1:0]

SCLK

SDEN

SDATA

Write

Precomp

Data

Low

Detector

SRC

FIR

ADC

Pass

Filter

SMD

LPFCA

BDAC

FCA

FDAC

ECC

Servo

Loop

Timing

Zero

Phase

& Gain

Restart

Encoder

Decoder

Interface

Detector

Gain

Loop

Offset

Control

Detection &

Thermal Asp.

Loop

Loop

Asymm.

Servo

Interface

Interface

Burst

Servo

Demod.

TI-[5:0]

Test

Block

Digital

Clock

Generator

Control Block

MUX

TESTBUS[7:0]

TBUSCLK

RRCLK

MODE[1 :0]

RESET*

PWD

RG

WG

SG

2/4

Data Freq.

Synthesizer

MDAC

VGA OFFMRA HPF

Analog Test Point

DIAG1

DIAG0

Zin

Ctrl

INP

INM

GDAC ODAC

Bandgap

IREF

Servo Freq.

Synthesizer

EXTCLK

REFCLK

Loading...

Loading...