L6246

12V VOICE COIL MOTOR DRIVER

12V (±10%) OPERATION

3A MAXIMUMCURRENT CAPABILITY

0.3ΩMAXIMUM ON RESISTANCE OF EACH

POWER DMOS AT A JUNCTION TEMPERATAUREOF25°C

CLASS ABPOWER AMPLIFIERS

LOGICAND POWERSUPPLYMONITOR

POWERONRESET

PARKING FUNCTION WITH SELECTABLE

RETRACT VOLTAGE AND DYNAMIC BRAKE

BEFOREPARKING

ENABLEFUNCTION

GATE DRIVER FOR EXTERNAL BLOCKING

N-MOSFET

OVERTEMPERATUREPROTECTION

OVERTEMPERATUREWARNING OUTPUT

PQFP44PACKAGE

DESCRIPTION

The voice coil driver L6246 is a linear power amplifier designed to drive single phase bipolar DC

motors for hard disk drive applications. The device contains a selectable transconductanceloop,

which allows high precision for head positioning.

The power stage is composedof 2 power amplifiers, in AB class, with 4 DMOSs, with Rdson of

0.5Ω (Sink+Source)maximum, in a H-bridge con-

MULTIPOWER BCD TECHNOLOGY

PQFP44(10x10)

figuration. Drive voltage for the upper DMOS

FETs is provided by a charge pump circuit to ensure low Rdson.

Automaticbrake and parking of the head actuator

is performed by logic or when a failure condition

is detectedby power supply monitors.An external

resistor programs the parking voltage that enables the head retract. In addition, a 5V stable

output is provided for the external usage, and a

gate driver circuit enables an external power supply isolation N-MOSFET.

This device is built in BCD II technologyallowing

dense digital circuitry to be combined with high

power bipolar power devices and is assembled in

PQFP44.

February 1998

1/12

L6246

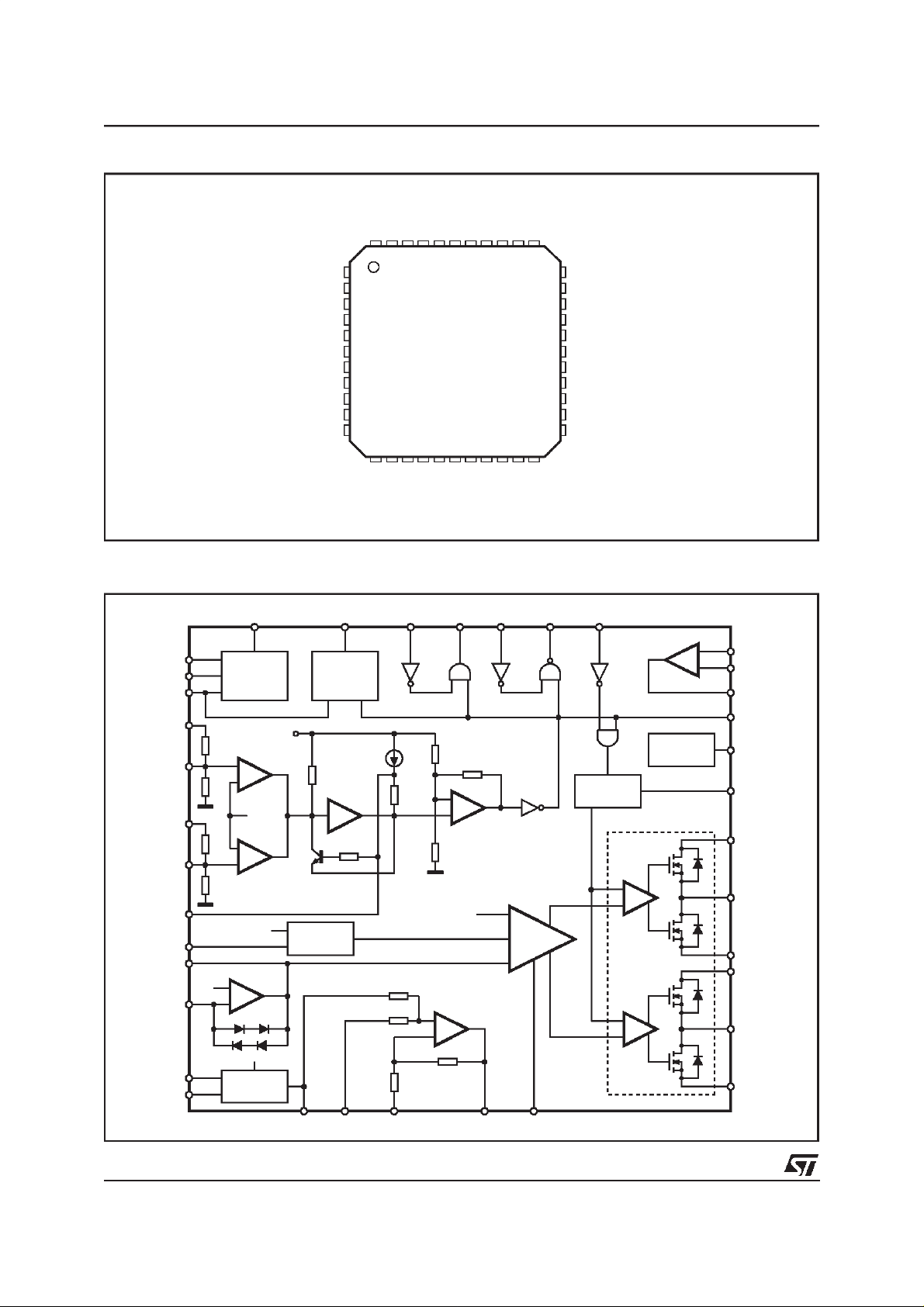

PIN CONNECTION (Top view)

BLOCK DIAGRAM

C1

C2

VCP

V

CC

+12

FILTER CAP

V

DD

+5

FILTER CAP

T_CAP

RPARK

ERR_OUT

V

CC/2

ERR-

+5V REF

+5V REF_GND

N.C.

FILTER_CAP

BRAKE DELAY

-THERMAL SD

SENSE-IN+

SENSE-IN-

GND

ERR-OUT

ERR-

SENSE-OUT

N.C.

CP_GND GATE DRIVE

CHARGE

PUMP

GATE

DRIVER

+5

+

-

10K

REF1

-

10K

+

REF1

PARKING

ERROR

AMPL.

+

-

REF1

REF. VOLT.

GENERATOR

SENSE

V

CC/2

_IN+

GND

OUT-

VIN-

VIN+

-SPINDLE

START

10K

CC

V

C2

VCPC1VCCOUT+

171118 19 20 21 22

DDVCC

-AE_W_GATE

MOTOR START

MOTOR

START

V

-W_GATE

CC/2

V

30K

25K

+

GATE DRIVE

44 43 42 41 3940 38 37 36 35 34

1

2

3

4

5

6

7

8

9

10

12 13 14 15 16

VIN_OUT

4µA

-

20K

V

SENSE

AMPLIFIER

+

CC/2

VPARK

-

SENSE

_IN-

SENSE_

OUT

-POR

GND

CPGND

T_CAP

+5V REF

W_GATE

VBEMF

N.C.

33

ENABLE

32

31

-SPINDLE START

30

VCM PARK

29

-W_GATE

28

RPARK

27

VBEMF

26

+12SETPT

+5SETPT

25

24

+5V REF_GND

N.C.

23

D95IN241B

-AE

+

-

VCM

PARK

INPUT

AMPLIFIER

BRAKE

CIRCUIT

POWER AMPLIFIERS

VINVIN+

VIN_OUT

-POR

THERMAL -THERMAL SD

BRAKE DELAY

V

CC

+

-

OUT+

GND

V

CC

+

-

OUT-

GND

D95IN242B

2/12

L6246

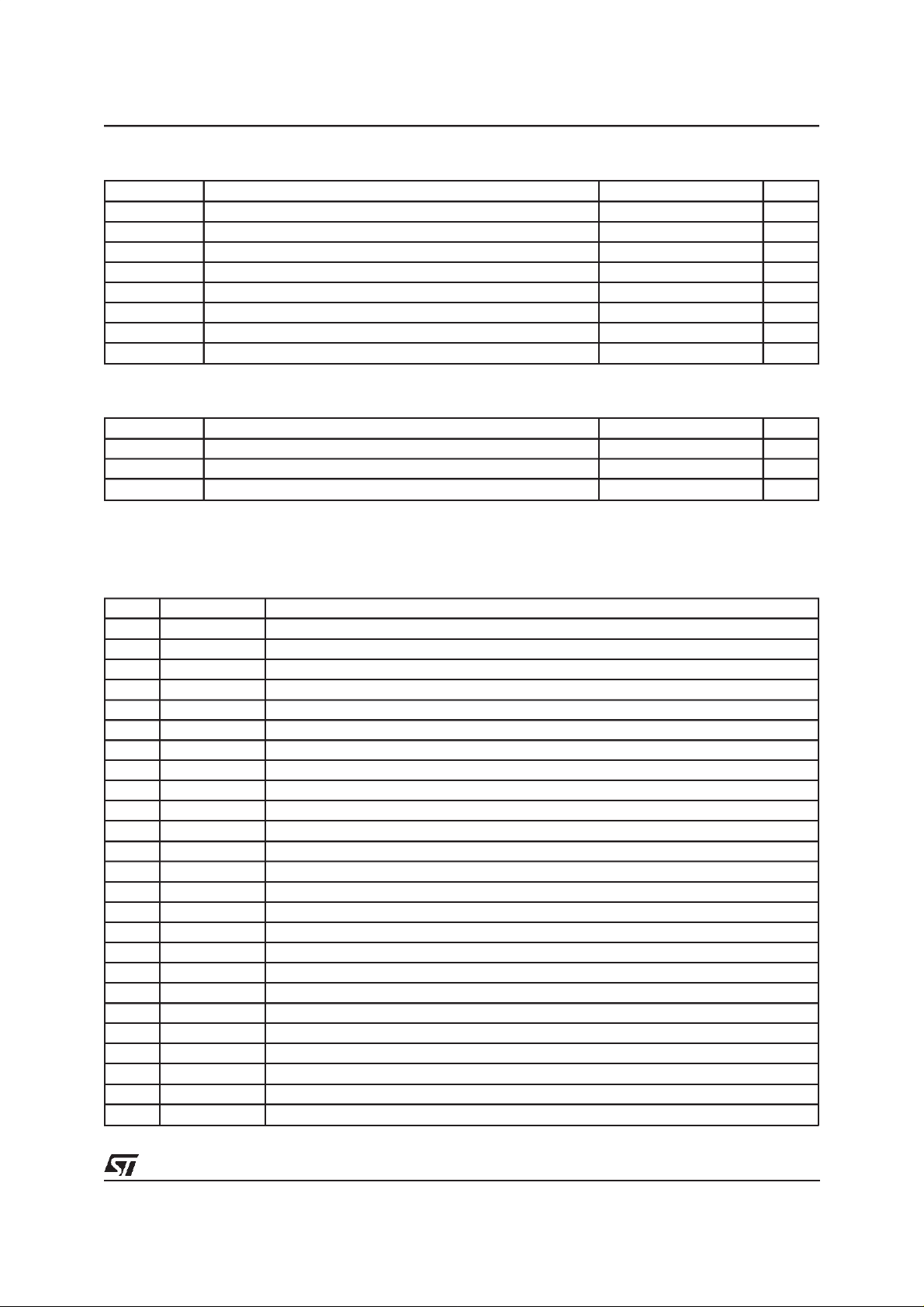

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

pow. max.

V

digital max.

V

in max.

V

in min.

I

peak

I

dc

P

tot

T

op

THERMAL DATA

Symbol Parameter Value Unit

R

th j-case

R

th j-amb

R

th j-amb

(*) Standard boardconstruction: single layer (1S 0P); size 100mm long by 100mm wide.

(**) The board constructionincludes: a 6 layer board (2S 4P,with power planes ≅80%); size 136mm longby 99mm wide; package location

near middle pointof lenght and onethird of width.

Maximum supply voltage 15 V

Maximum supply voltage 7 V

Maximum input voltage V

±0.3 V

digital

Minimum input voltage GND - 0.3 V

Peak sink/source output current 3 A

DC sink/source output current 1.7 A

Maximum total power dissipation ≅1.7 W

Operative temperature range 0 to 80 °C

Thermal resistance junction to case ≅20 °C/W

Thermalresistancejunction toambientmountedon standard PCB(*) ≅66 °C/W

Thermal resistance junction to ambient mounted on PCB (**) ≅35 °C/W

PIN FUNCTIONS

Pin Name Description

1 N.C. Not Connected.

2 Filter_cap Filter capacitor for 10V internal regulator. The capacitor is optional.

3 Brake Delay Voice Coil Motor brake delay capacitor.

4 -Thermal SD Pre Thermal Shut Down indication Output.

5 Sense_in+ Non invertingInput of Sense Amplifier.

6 Sense_in- Inverting Input of Sense Amplifier.

7 Gnd Ground.

8 Err_out Error Amplifier Output.

9 Err- InvertingInput of Error Amplifier.

10 Sense_out Output of Sense Amplifier.

11 N.C. Not Connected.

12 Vin_out Output of Input Amplifier.

13 Vin- Inverting Input of Input Amplifier.

14 Vin+ Non invertingInput of Input Amplifier.

15 +Vcc/2 Half Supply Voltage reference.

16 +Motor start Motor start Output to Spindle Controller.

17 -AE_W_Gate Write Gate Output to AE.

18 +Vdd +5V Supply.

19 +Vcc +12V Supply.

20 -POR Power On Reset. Low willsignal thefailureof thelogic supply or 12V supply

21 +5V Ref +5V Reference Output from the Voltage Reference Regulator.

22 T_cap Power On Reset Timing Capacitor. The capacitor sets the POR delay.

23 N.C. Not Connected.

24 +5V Ref Gnd Ground for VoltageReference Generator.

25 +5Setpt +5V Monitor Set Point and filtering

3/12

L6246

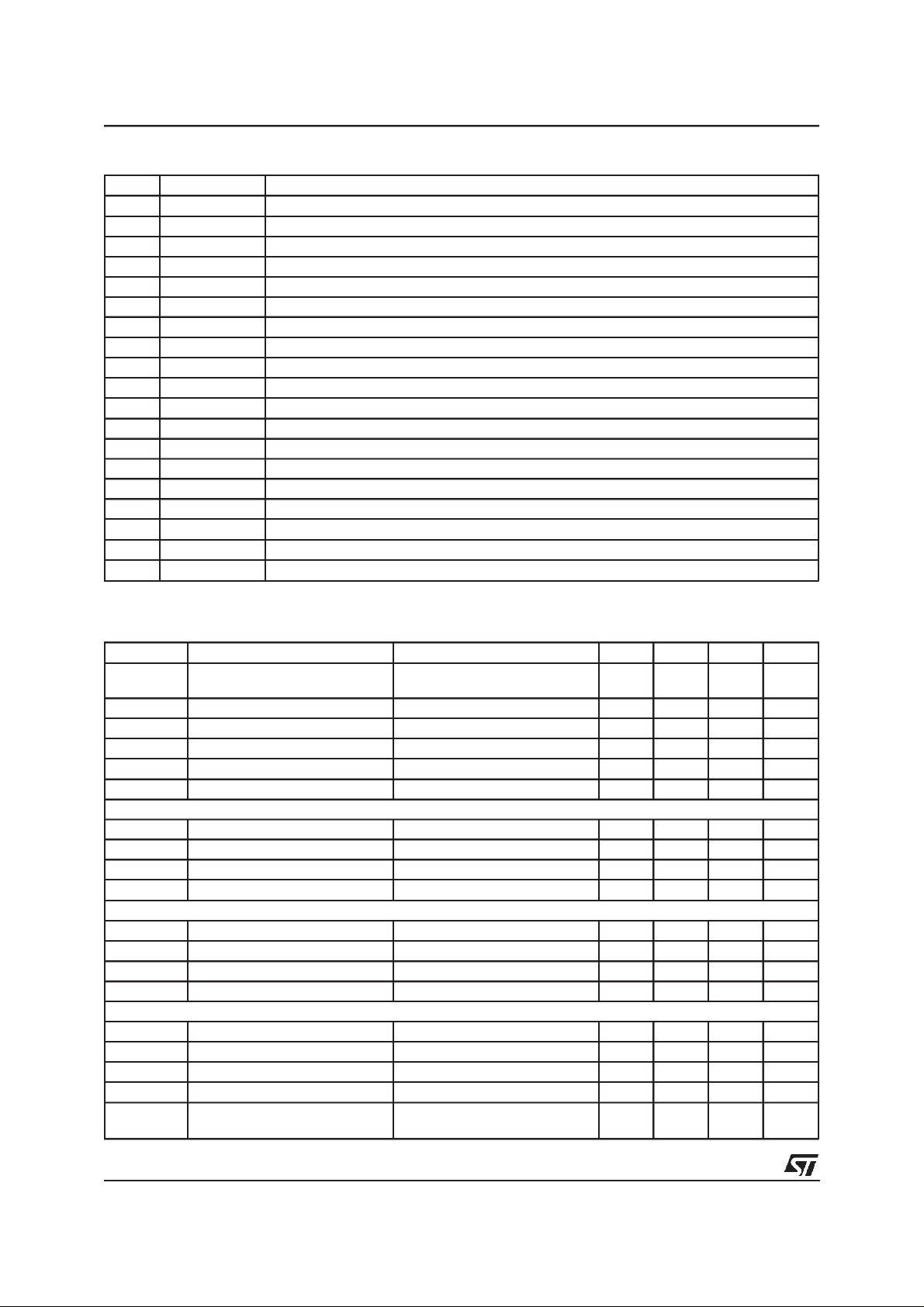

PIN FUNCTIONS (continued)

Pin Name Description

26 +12Setpt +12V Monitor Set Point and filtering

27 Vbemf Input BEMF from spindle motor for parking circuit.

28 Rpark Resistor for setting the park voltage.

29 -W_Gate Write Gate Input.

30 +VCM park External input for parking. High will activate the park procedure.

31 -Spindle_start Spindle Start input.

32 +Enable Input. logic low will disable only the IC.

33 N.C. Not Connected.

34 Cpgnd Charge Pump Ground.

35 Gnd Ground.

36 Out+ Power Amplifier Output.

37 Vcc +12V Power Supply.

38 C1 Charge Pump Oscillator Output.

39 C2 Input for external Charge Pump Capacitor.

40 Vcp Output for Charge Pump Storage Capacitor.

41 Vcc +12V Power Supply.

42 Out- Power Amplifier Output.

43 Gnd Ground.

44 Gate Drive Gate Drive for External Isolation N-MOSFETS.

ELECTRICALCHARACTERISTICS (Tj=25°C,Vdd= 5V, Vcc= 12V; unless otherwise specified.)

Symbol Parameter Test Condition Min. Typ. Max. Unit

Vcc Analog/Power supply voltage

range

Vdd Digital supplyvoltage range 4.5 5 5.5 V

Idd Digital supply quiescent current Output ENABLED 5 mA

Idd Digital supply quiescent current Output DISABLED 5 mA

Icc Power supply quiescent current Output ENABLED 20 mA

Icc Power supply quiescent current Output DISABLED 10 mA

THERMAL SHUT DOWN DATA

T

h_SD

T

h_SD_H

T

h_Warn

Shut down Temperature 135 160 °C

Shut down hysteresys 25 °C

Pre Shut down alarm 115 140 °C

Pre Shut down alarm hysteresys 15 °C

EXTERNAL N-MOSFET GATE DRIVER

Vll Low level voltage 500 mV

Vhl High level voltage Vcc+4 V

Isink Current sinking capability 4 mA

Isource Current source capability 0.5 mA

POWER ON RESET AND GATE SPECIFICATION

V

dd_und_th

V

cc_und_th

POR

POR

_delay

V

dd_POR_T_R

Digital undervoltage threshold 3.8 4.1 4.45 V

Power undervoltage threshold 8.5 9.25 10.0 V

POR timeout Cpor = 1µF 375 500 625 ms

_to

Time delay forPOR Active 1

Power supply POR thereshold

Resistance

10.8 12 13.2 V

10 K

s

µ

Ω

4/12

ELECTRICALCHARACTERISTICS (continued)

Symbol Parameter Test Condition Min. Typ. Max. Unit

V

CC_POR_T_R

Logic supply POR thereshold

Resistance

I

_POR_O

POR output current drive 4 mA

LOGIC INTERFACE VOLTAGE LEVEL (All digital inputs are CMOS compatible)

Voh CMOS high level output voltage Iout = 1.0mA 4.10 V

Vol CMOS low level output voltage Iout = 1.0mA 0.40 V

Vih TTL high level input voltage 2 V

Vil TTL low level input voltage 0.80 V

5V REFERENCE GENERATOR

Vref Voltage reference at Power On 4.75 5.00 5.25 V

Drift Drift from Power On -2 +2 %

loref Current output 10 mA

INPUT AMPLIFIER

Vi Input voltage range Vref (-) Vref (+) V

Vcm Input common mode voltage

range

Vds Input differentialvoltage swing -5 +5 V

Vos Input offset voltage -5 +5 mV

Ib Input Bias current -500 +500 nA

Gv Open Loop voltage Gain 80 dB

SR Output slew rate 0.6 V/µs

GBW Gain bandwidth product 1 MHz

PSRR Power supply rejection ratio 80 dB

Vo Output voltage swing 9 V

ERROR AMPLIFIER

Vi Input voltage range V

Vos Input offset voltage -5 +5 mV

Ib Input Bias current -500 +500 nA

Gv Open Loop voltage Gain 80 dB

SR Output slew rate 0.6 V/µs

GBW Gain bandwidth product 1 MHz

PSRR Power supply rejection ratio 80 dB

Vo Output voltage swing V

SENSE AMPLIFIER

Vi Input voltage range Gnd Vcc V

Vos Input offset voltage -6 +6 mV

Ii Input sink and source current -1.5 +1.5 mA

PSRR Power supply rejection ratio 50 dB

Gv Vloltage gain 9.9 10 10.1 V/V

Rin Differential input resistance 3 KΩ

GBW Gain bandwidth product 1 MHz

Vli Linear differential input voltage

Gv = 10(V/V) -0.35 +0.55 V

range

CMRR Common mode rejection ratio 56 dB

10 K

0 5.00 V

CC

-0.5

CC

-2Vbe

/2

/2

VCC/2

+0.5

VCC/2

+2Vbe

L6246

Ω

V

V

5/12

L6246

ELECTRICALCHARACTERISTICS (continued)

Symbol Parameter Test Condition Min. Typ. Max. Unit

POWER AMPLIFIER

Rdson DMOS on resistance at 25°C 0.3 Ω

Gdv Differential voltage gain 32 V/V

Iol Output current leakage 500 µA

SR Output slew rate 0.4 V/µs

Tsr Saturation recovery time 5 µs

GBW Gain bandwidth product 100 KHz

RETRACT

Vr Max. retract voltage Vcc shorted to GND 300 mV

Vr Max. retract voltage Vcc Normal 1 V

CHARGE PUMP

Cs Storage capacitor 1 µF

Vs Storage voltage Vcc +4 V

Cp Pump capacitor 0.2 µF

RETRACT TRUTH TABLE

Input Input Output Output

-Retract +Enable Bridge Enable +Retract

Brake and Retract 0 X 0 1

Run 1110

Disable 1000

BLOCK DESCRIPTION

POWERAMPLIFIERS

The two power amplifiers are connected in bridge

configurationworking in AB class.

SENSEAMPLIFIER

The open loop gain and bandwith of this amplifier

are similar to the sense amplifier.

The negative input and the output of the error amplifier are accessible externally in order to have

the current loop compensationuser configurable.

The dynamic of the output is limited at +/- 2Vbe to

have a faster responseof the outputvoltage.

This stage senses the voltage drop across the

Rsense.

The input stage is supplied by the charge pump

voltage to have an high dynamic, while the other

sections of the amplifier are supplied by the voltage of 10.5V internally regulated to have an high

power supply rejection (this voltage,suppliesalso

the error amplifier, the input amplifier and the operational amplifier which generatesthe Vcc/2 volt-

INPUTAMPLIFIER

The inputs and the output pins are externally ac-

cessible to have the possibility to configure the

transconductance gain of the current control loop

selectingthe voltagegain of this amplifier.

The open loop gain and bandwith of this amplifier

are similar to the sense amplifier.

age).

The open loop gain is around 80dB and the bandwith is more than 1MHz.

The voltage gain is fixedinternallyat 10 V/V.

ERRORAMPLIFIER

This is the stage which compares the input volt-

age and the sense voltage, generatingthe control

voltage for the power section.

REFERENCE VOLTAGEGENERATOR

This block generates the two reference voltage

Vcc/2 and +5VREF.

The Vcc/2 voltage is used as reference by the

currentcontrolloop.

The +5VREF is a very stable voltage generator

that can be used as reference voltage of an exter-

nal DAC.

6/12

L6246

POWERSUPPLYMONITOR

This circuit monitors the logic supply (5V) and the

power supply (12V) and activates the power on

reset output (POR) and the VCM PARK circuit.

After both logic and power supply reach their

nominal value a timing capacitor (T_CAP) has to

be charge before the POR output change from

low to high level.

POR delay=

where:

C ⋅ V

I

C is the capacitor value connected at pin

T_CAP

V is delta voltage that capacitor have to be

charged(2.3V)

I is the costant current charging the capacitor

(4µA typ.)

At the two input pins, +12 FILTER CAP and + 5

FILTER CAP, can be connected two capacitors

for filtering the noise on the power supply, avoiding in this case undesired commutations of the

POR signal becauseof some fast negative spikes

on theline.

BRAKEAND PARKINGCIRCUITS

The voice coil driver is switched into the parking

condition through the VCM PARK input or when

the POR signal is low. In such condition immediately the output stage turns on the two lower

DMOS of the power bridge to activatethe BRAKE

of the voice coil motor.

After a delay generated by the capacitor at the

BRAKE DELAY pin, only one of the two lower

DMOS stays on while the opposite half bridge is

tristated.

BRAKEdelay=

where:

C ⋅ V

I

C is the capacitor value connected at pin

BRAKEDELAY

V is delta voltage that capacitor have to be

charged(3V)

I is the costant current charging the capacitor

(5µA typ.)

The parking voltage is then supplied by the

PARKINGcircuit connected to the output that has

been tristated.

The value of such a voltage is set by connecting

an external resistor between the RPARK pin and

ground.

Vbandgap⋅

=

V

r

Rpark

10

4

where:

Vr is the retract voltagefor parkingthe heads

Vbandgap is the internal bandgap reference

voltageof 1.4V

Rpark is value of the resistor connected at

RPARKpin

The parking circuit takes the power supply from

the spindle driver through the VBEMF pin, so that

in case of power fail the retract of the heads is

possible using the rectified BEMF voltage coming

from the spindle motor.

CHARGEPUMP

The charge pump circuit is usedas a means of al-

most doubling the power supply voltage (12V) in

order to drive the upper DMOS of the power

bridge.

The energy stored in the in the capacitor connected at VCP pin is also used to drive the gate

of the externalN-MOSFET.

GATE DRIVER

This circuit provide the voltage driving the gate of

the external isolation N-MOSFET, and it is controlledby thePOR signal.

THERMAL

The thermal protection circuit has two threshold,

the first if the pre shut down alarm that activates

the THERMAL SD signal and the second is the

shut down temperature that tristates the output

stage when the junction temperature increases

over thislevel.

APPLICATIONINFORMATION

Example of calculation of the error amplifier compansation for the stability of the current control

loop. As can be seen from the draw of the current

control loop circuit of the next page, the voltage

across the load is:

#1

CPW ⋅ACERR ⋅(ACINP ⋅

=A

V

L

V

=Rs⋅I

sense

L

VL=(ZL+ Rs)⋅ I

L

CENSE ⋅

-A

V

IN

V

sense

where AC... is the closed loop gain of Power, Error, Sense and Input Amplifier.

Changing in the #1 the transfer function between

the load currentand the V

is:

IN

#2

I

L

V

IN

=

ZL+ RS+ A

A

CPW

CPW

⋅

A

⋅ A

CERR

CERR

⋅

A

⋅ A

CINP

CSENSE

⋅ R

S

)

7/12

L6246

TypicalApplicationCircuit

V

CTL

V

REF

V

CC/2

10.5V

INT.REG.

1K

10K

10K

10K

10K

AE WGATE

MOTOR START

THERMAL SHTD

POR

(*)

Rs 0.2

OUT_ SENSE_IN- SENSE_IN+ OUT+

SENSE_OUT

ERR_OUT

1M1K

VIN_OUT

FILTER_CAP

42 6 5 36

10

8

1K

100nF

9

ERR-

12

VIN-

13

VIN+

14

V

CC/2

15

CPGND

34

GND

7,35,43

17

16

4

20 32 ENABLE

2

FILTER CAPACITORS TO BESET IN APPLICATION

VOICE COIL

MOTOR

LL RL

L6246

PQFP44

V

DD

100nF

10nF

V

18

DD

C1 C2

38 39

V

CC

19

V

CC

41

V

CC

37

44

27

40

28

21

24

26

25

22

3

30 VCM PARK

31 SPINDLE START

29 W GATE

GATE DRV

V

BEMF

V

CP

R

PARK

5V

REF

5V

GND

REF

12S

EPT

5S

SEPT

12S

EPT

5S

SEPT

D95IN268

22µF 100nF

1µF

51K

1µF

1µF

V

CC

S

P322

G

D

FROM

100nF

5V

REF

(*)

(*)

GND

SPINDLE

DRIVER

Current Control Loop Circuit

V

+ 10V

CC/2

SENSE

20K

V

2K

SENSE

2K

RB

VIN

RB

20K

RA

-

+

SENSE

AMPL.

V

CC/2

RA

-

+

INPUT

AMPL.

V

V

CC/2

- (RA-RB) VIN

CC/2

V

+ (RA/RB)(ZC/RC) VIN-10 (ZC/R1) V

CC/2

ERROR

AMPL.

V

CC/2

+

-

R1

R2

C

R3

1.1K

V

RC (=R1)

VL=32 ( (ZC/RC) VIN - 10 (ZC/R1) V

=A

D95IN269B

SENSE

TO

SENSE

Z

CC/2

AMPLIFIER

17.5K

C

+

-+

POWER

AMPL.

+-

LL

R

S

LOAD

VL

)

SENSE

RL

POWER

AMPL.

CPW*ACERR(ACIMP * VIN-ACSENSE*VSENSE

16.5K

)

-

+

1.1K

V

CC/2

8/12

L6246

If Now We Define:

#3

Aloop = A

CPW

⋅ A

CERR

⋅ A

CSENSE

⋅

RS+ Z

R

S

L

we obtain:

#4

Aloop⋅

I

L

=

V

IN

A

CINP

A

CSENSE

1+ Aloo p

1

⋅

R

S

Atlowfrequencyis:

Aloop = 32 ⋅

if R2 = 1M, R1 = 1K, R

R2

⋅ 10 ⋅

R1

S

=0.2, RL=7

(R

R

S

S

+ ZL)

then Aloop = 8889 = 80dB.

Being Aloop very high we can simplify the #4 in

this way:

I

A

L

V

IN

=

CINP

A

CSENSE

1

⋅

R

S

=

1

10 ⋅

0.2

1

=

2

and its pole is at frequency

1

2π L

(RS+ R

so around 1KHz if L = 1.2mH.

So considering:

Ax |

dB

= Aloop |dBA

dB

+ACSENSE |dB+

CERR

R

S

RS+ R

|dBA

dB

L

CPW

|

we have these Bode diagrams:

ACPW

30dB 130KHz

ACSENSE

20dB

)

L

210KHz

For the stability we have to study the stability of

Aloop, that as we can see from the #3 is a multiplication,so in dB is a sum:

Aloop |

+

dB

R

=ACPW |dB+ACERR |dB+ACSENSE |

dB

R

S

dB

+

Z

S

L

So we can take in consideration the BODE diagrams of the each operational amplifier, with particular attentionto the Error amplifier.

1)The Power amplifier is actually composed by

two operational amplifiers in the way to have

a gain of +16 and -16 (in voltage) respectevely,for a totalof 32 = 30dB.

The point at -3dB is around 130KHz.

2)The Sense amplifier has a gain of 20dB with

the point at -3dB around 210KHz.

3)The load introduce an attenuationof:

R

S

20log

RS+ R

= -31dBwith RS = 0.2 and RL =7

L

-31dB

LOAD

AX

19dB

1K 10K 100K

D95IN270A

As can be easily see the bandwith is narrow and

the gain is low. It is possible to increase both

choosing an appropriatecompensation of the Error amplifier.

The total bandwith should be, of course, at least a

decade lower of the 130KHz to avoid instability

problem. The bandwith guaranteed by the Error

amplifier has a Gmax of 80dB and a gain of 0dB

at 1MHz approximately, the real is some dB more

with a largerbandwith.

9/12

L6246

ERROR AMPL.

120

100

80

60

40

20

D95IN271

Using the compensation network of the draw of

pag.8, we have a error amplifier transfer function

of:

GAIN

(dB)

OPEN LOOP GAIN

1 10 100 1M 10M

1K 10K 100K

As can be seen the choice of the pole influence

overall in fixing the gain at high frequency.

The gain at high frequency must be choosen in

order to not create instability problem, because

more higher is this gain and lower is the second

pole that we have at high frequency.

If this pole is taken close to the other that we

have already seen at 130KHz and 210KHz, instabilityproblemscan arise.

Adding together AX |

dB

and A

CERR|dB

we ob-

taine the Aloop:

ACERR

(dB)

COMPENSATION AT 3Hz

60

40

20

AX(dB)

COMPENSATION AT 100Hz

V

V

so:

Gmax (DC) =

ZC

O

=−

R1

I

R2

R1

R2

=−

R1

= 1000= 60dB

with R1 = 1MΩand R2 = 1K

zero =

pole =

Note: Fpole is lower thanFzero

1

2 π R3C

1

2 π(R3 + R2) C

1+scR3

⋅

1 + sc (R3 + R2)

Ω

The best choice is to cancel the pole of the load

(at around 1KHz) with the zero of the compensation.

ACERR (dB)

120

100

80

60

40

20

D95IN272

X

CLOSED

LOOP

ACERR

1 10 100 1M 10M

1K 10K 100K

X

X

DIFFERENTS

POLES

EXAMPLES

19

A

(dB)

LOOP

79

60

40

20

D95IN273

10 100 1K 10K 100K 1M 10M

IS STABLE

IS NOT STABLE

So the choice of the compensation network must

be done in order to fix at thebeginning the Gmax

of the error amplifier dependingon the ratio

R2

R1

.

To calculate the R3 and C values satisfying the

followingsystem:

2 π R3C

1

=

R

2 π L

+ R

L

1

sense

Erroramplifierzeroequal to load pole

1

2 π(R3 + R2)C

AdmissibleBandwith

=

Gloop

=

130KHz

10

=

8912

=

1.5Hz

This example is for crossing the 0dB one decade

before the first pole of the Power Amplifier

(130KHz),startingwitha Gloop max of 79dB.

10/12

PQFP44 (10x10) PACKAGE MECHANICAL DATA

L6246

DIM.

mm inch

MIN. TYP. MAX. MIN. TYP. MAX.

A 2.45 0.096

A1 0.25 0.010

A2 1.95 2.00 2.10 0.077 0.079 0.083

B 0.30 0.45 0.012 0.018

c 0.13 0.23 0.005 0.009

D 12.95 13.20 13.45 0.51 0.52 0.53

D1 9.90 10.00 10.10 0.390 0.394 0.398

D3 8.00 0.315

e 0.80 0.031

E 12.95 13.20 13.45 0.510 0.520 0.530

E1 9.90 10.00 10.10 0.390 0.394 0.398

E3 8.00 0.315

L 0.65 0.80 0.95 0.026 0.031 0.037

L1 1.60 0.063

K0

(min.), 7°(max.)

°

D

D1

33

34

B

44

1

e

23

11

PQFP44

22

L1

E

L

E3D3E1

12

0.10mm

.004

Seating Plane

K

A1

A

A2

B

C

11/12

L6246

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the

consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No

license is granted by implicationor otherwise under any patentor patent rights of SGS-THOMSON Microelectronics. Specificationmentioned

in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGSTHOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express

written approval ofSGS-THOMSON Microelectronics.

1998 SGS-THOMSON Microelectronics – Printed in Italy– All Rights Reserved

SGS-THOMSON Microelectronics GROUPOF COMPANIES

Australia - Brazil - Canada - China - France- Germany - Italy- Japan - Korea - Malaysia - Malta - Morocco - TheNetherlands -

Singapore - Spain - Sweden - Switzerland- Taiwan - Thailand - UnitedKingdom - U.S.A.

12/12

Loading...

Loading...