ISB35000 SERIES

HCMOS ST RU CTU RED AR RAY

PRELIMINARY DATA

FEATURES

0.5 micron triple layer metal HCMOS process

featuring retrograde well technology, low

resistance salicided active areas, polysilicide

gates and thin metal oxide.

3.3 V optimized trans ist or with 5 V I/O inter fac e

capability

2 - input NAND delay of 0.210 ns (typ) with

fanout = 2.

Broad I/O functionality including LVCMOS,

LVTTL, GTL, PE CL, and LVDS.

High drive I/O; c apability of sink ing up to 48 m A

with slew rate cont rol, current spike suppression

and impedance matching.

Metallised generators to support SPRAM and

DPRAM, plus an extensive embedded function

library.

Combines Standard Cell Features with Sea of

Gates time to market.

T ab le 1. Pro d u ct rang e

Internal

Device Name

Total Sites

1

Estimated

Gates

2

Fully independent power and ground

configurations for inputs, core and outputs.

Programmable I/O ring capability up to 1000

pads.

Output buffers capable of driving ISA, EISA,

PCI, MCA, and SCSI interface levels.

Active pull up and pull down devices.

Buskeeper I/O funct ions .

Oscillators for wide frequency spectrum.

Broad range of 400 SSI cells.

300 element macrofunction library.

Design For Test includes LSSD macro library

option and IEEE 1149.1 JTAG Boundary Scan

architecture built in.

Cadence and Mentor bas ed design s ystem with

interfaces from multiple workstations.

Broad ceramic and plastic package range.

Latchup trigger current +/- 500 mA.

ESD protection +/- 4000 volts.

Total Usable

Gates

3

Maximum

Device Pads

4

Maximum

I/O

5

ISB35083 124,416 82,944 58,060 188 172

ISB35130 194,400 129,600 90,720 232 216

ISB35166 249,696 166,464 116,524 260 244

ISB35208 311,904 207,936 145,555 288 272

ISB35279 418,176 278,784 195,148 332 316

ISB35389 584,064 389,376 253,094 388 372

ISB35484 726,624 484,416 314,870 432 416

ISB35666 998,784 665,856 399,513 504 488

ISB35832 1,247,616 831,744 499,046 560 544

Notes : 1. Internal sites is based on the number of placement sites available to the route and place software

2. A factor of 1.5 is used to derive the gate complexity from the total available sites . This number is in Nand2 equivalents

3. Factors of 70%, 65%, and 60% have been used to calculate the routing efficiency. This number may vary depending on the

design.

4. 16 corner pads are dedicated to internal and external power supplies. I/O pads may be configured for additional power.

5. Maximum I/O = total device pads minus power pads.

May 1994

1/15

ISB35000 SERIES

GENERAL DESCRIPTION

The ISB35000 array series uses a high performance, low voltage, triple level metal, HCMOS 0.5

micron process to achieve sub-nanosecond internal speeds while of fering very low power dissipation

and high noise immunity. The potential total gate

count ranges above 1 million equivalent usable

gates. The array operates over a Vdd voltage range

of 2.7 to 3.6 volts.

The I/O count for this array family ranges to over

600 signals and 1000 pins dependent upon the

package technology utilized. A Sea of I/O approach

has been followed to give a solution to today’s

problems of drive levels and specialized interface

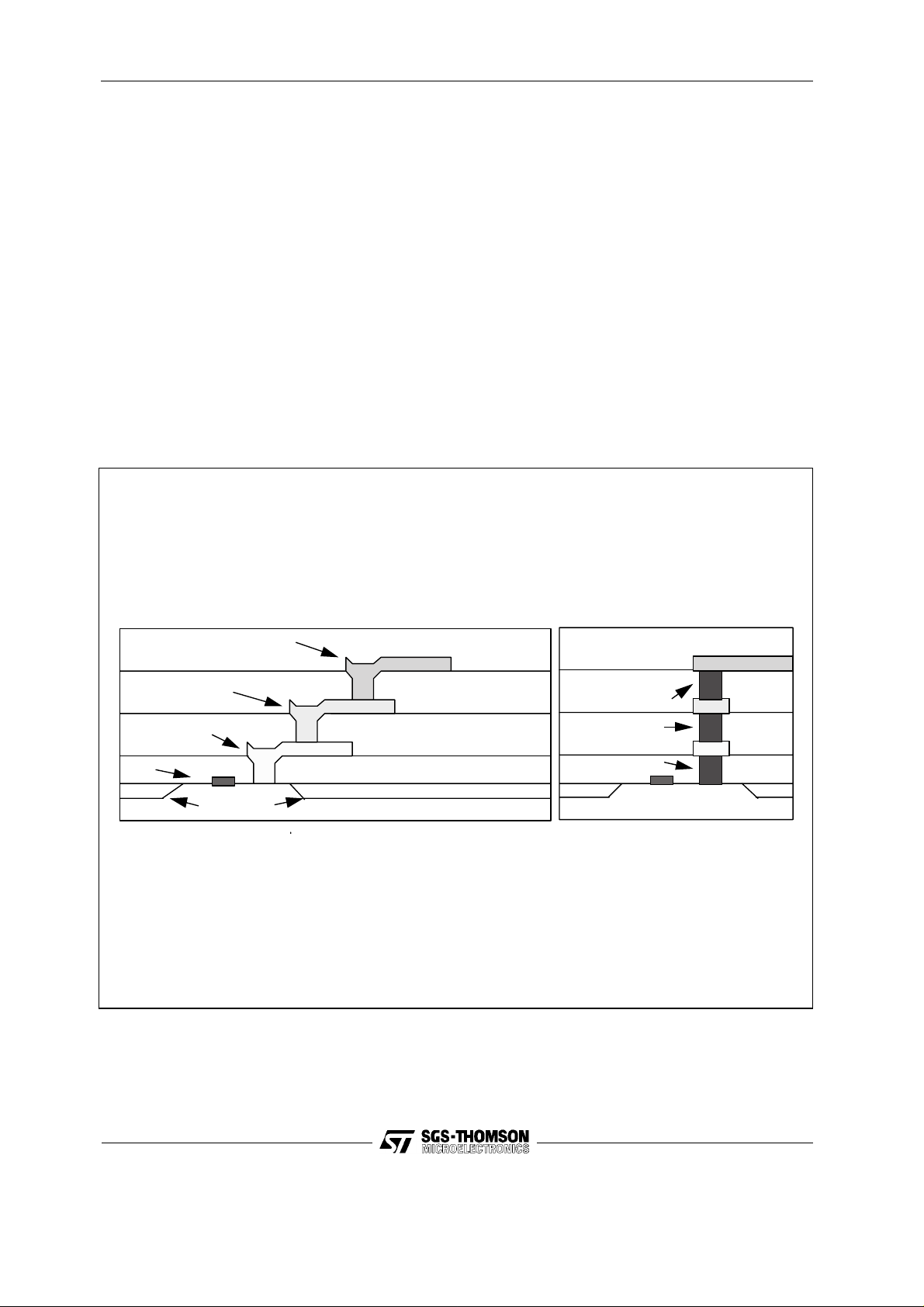

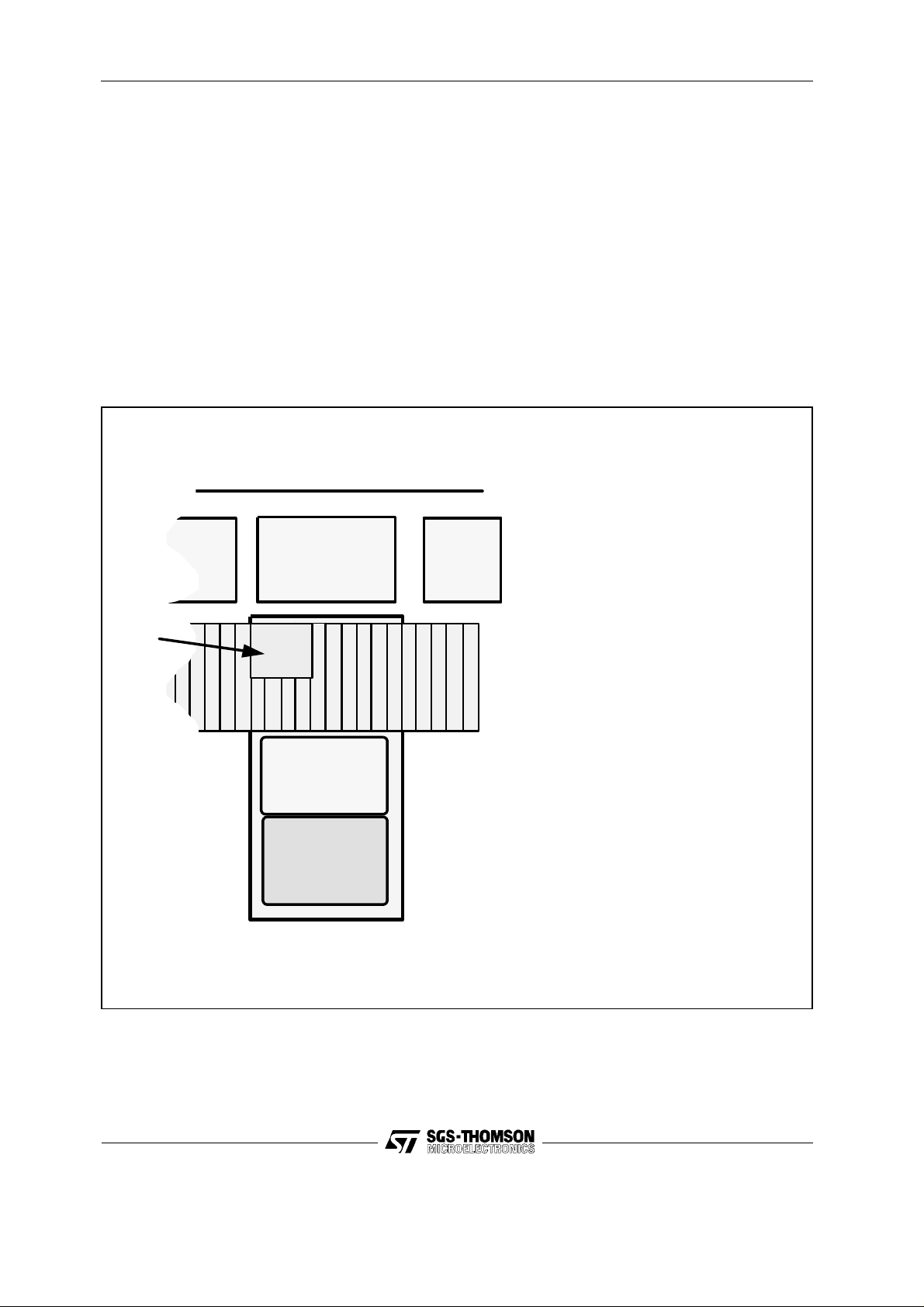

Figure 1. Advantages of stacked contacts and vias

standards. The ar ray does not utilize a set bond pad

spacing but allows for pad spacings from 80 microns upwards.

The I/O can be configured for c ircuit s ranging fr om

low voltage CMOS and TTL to 200 mHz plus low

swing differential circuits. Standards like GTL,

SCSI-2, 3.3 Volt PCI, CTI, and a limited set of 5.0

Volt interfaces are currently being addressed. A

specialized set of impedance matched transmission line driver LVTTL type circuits are also available with 25, 35, 45, and 55 Ohm output

impedance. These buffers sacrifice direct current

capabilities for matching positiv e and negative voltage and current waveforms.

CONVENTIONAL VIA LAYOUT STACKED VIA LAYOUT

2nd

VIA

1st

VIA

METAL 2

METAL 1

GATE 1st DIELECTRIC

SUBSTRATEISOLATION

- STACKABLE CONTACTS + VIAs ALLOW MUCH HIGHER DENSITY (AREA SAVINGS UP TO 20% FOR R.L.)

- SIMPLIFIED ROUTING AND DESIGN RULE CHECKING

METAL 3

3rd DIELECTRIC

2nd DIELECTRICCONTACT

CONTACT/VIA

PLUGS

ISB35_VA

2/15

ISB35000 SERIES

TECHNOLO G Y OVERVIEW

The design of ISB35000 internal cell is a proprietary

design variation of the CONTINUOUS ARRAY architecture previously used in ISB12000, 18000,

and 24000 array families. This proprietary (patent

pending) configuration has been named THE DOUBLE BUFFE R CE LL. T his c onfigur ation pr ovides a

core that is completely filled with potently active

transistors. Surrounding the core are configurational specialized transistors forming a Sea of I/O

giving a high degree of flexibility to the system

designer. The ISB35000 supports the routing of

signals over unused transistors as needed. Three

levels of metal are utilized, intracell and intercell

wiring are limited to first metal with second and t hird

metal levels dedicated to interconnect wiring and

power distribution.

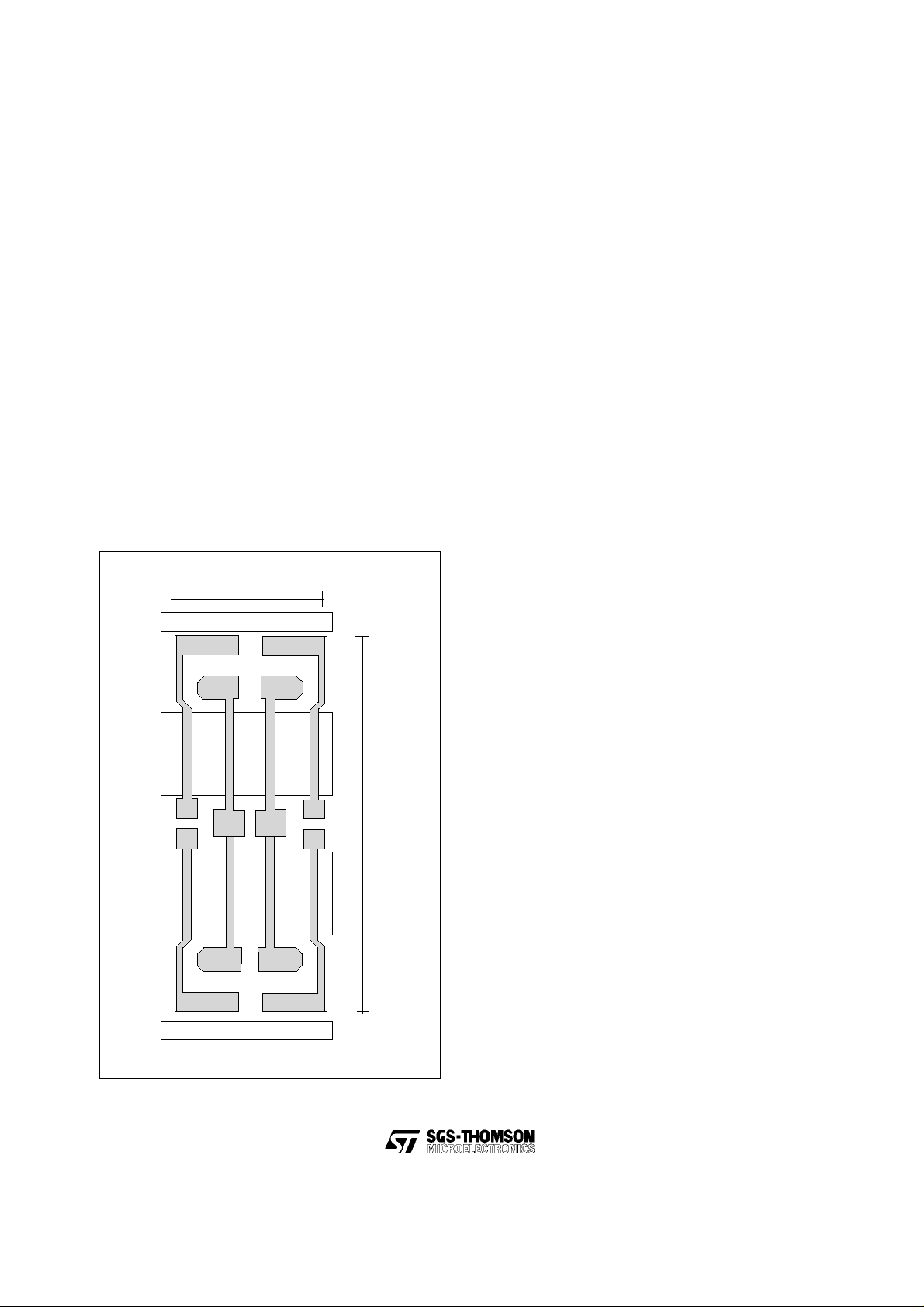

The basic cell is m ade up of four N and four P ty pe

transistors that are vertically arranged. The centre

two pairs of transistor have common polysilicon

Figure 2. Internal Core Cell

10 µm

30 µm

ISB35_PA

gates, while the outer two pairs have separate

gates for the polysilicon transistors. The cell was

configured to allow extremely high density macro

design for internal macro cell counts over one

million gates while enabling paralleling of transistors to allow high drive capability and the sym metry

of the rise and fall of macro outputs hence the

DOUBLE BUFFER name. Each cell has twelve

horizontal wiring channels on first m etal, four v ertical wiring channels on second metal and a further

twelve channels on third metal. The HCMO S5 process technology allows for adjacent vias and

stacked via1, via2 with or without silicon contacts.

The transistor width utilized by the DOUBLE BUF FER cell is very small as compared to previous

technologies. Even though the basic cell consists

of eight transistors adjacent macros share transistors across the cell borders allowing high density

usage of the resources.

Macros are constructed using resources from one

half cell to tens of cells dependent upon the complexity of the function. The transistors within and

between cells are placed adjacent to each other

sharing source and drain regions. All isolation is

achieved by cutting off adjacent source drain regions with turned off transist ors .

A further feature of the Double Buffer cell that helps

allow it to obtain very high density usage is the

proprietary (patent pending) method of localized

power distribution. A major feature of the HCMOS 5

process is salicided active areas. This results in

source drain areas that are of one to two ohms

resistance as opposed to the hundreds or thousands of ohms of source drain resistance in previous technologies. This very low resistance is one

reason that very low transistor widths could be

utilized in the cell design since driv e is not lost due

to source drain resistance. This use of low width

transistors results in lower capacitance loading of

the gates due to the smaller areas utilized. Low

resistance, low capacitance, and small gates results in low power usage for inv erters as com pared

to previous ISB technologies. This reduction in

power allows the use of salicided active stripes for

power distribution replacing the first level metal

buses used in previous technologies. This removal

of the metal one power buses simplified macro

layout allowing additional wiring res ources to be left

for the router allowing a higher density usage of the

array than would be achievable with previous

power distribution techniques. One other gain in the

performance of the array and its usability for the

customer was derived from the use of the salicided

3/15

ISB35000 SERIES

active power distribution. Since the pow er dist ribution serves as the well ties the inherent capacitance

of the reversed biased well junctions is closely

coupled into the power dist ribution and funct ions as

localized decoupling capacitance helping to keep

high frequency noise from being coupled from one

macro to the other through the power distribution.

The salicided active local distribution of the DOUBLE BUF FER cell is supplied its power by a screen

grid of power bused on bot h second and third met al.

The second metal buses run every nine cells and

are two wiring tracks wide. Vss and Vdd is interleaved every other bus. The third level buses run

every thirty six tracks and are three trac ks wide. This

grid is sufficient to power all but the largest arrays

though the use of custom structured cores or gate

counts above 500,000 usable cells along with high

clock rates m ay result in the need for supplem ental

power. The overall die power distribution is broken

down into a minimum of three Vdd and three Vss

distributions. Optionally other distributions for specialized I/O may be inserted. The standard distributions are Internal Vdd and Vs s, s erving the int ernal

cells and the prebuffer sections of the I/O, External

Vdd and Vss serving the output transistor s only, and

Receiver Vdd and Vss serving the firs t stages of the

receiver cells. Optional distributions for 5.0V interface, GTL, CTL, and other standar ds can be utilized

as necessary.

LIBRARY

The following section details the elements which

make up the ISB35000 Series librar y . The elements

are organised into three categories:

1. Macrocell library with Input, Output, Bidirectional

Buffers including JTAG macrocells and Core

cells.

2. Macrofunctions

3. Module generators

4. Embedded Functions

I/O BUFFERS

ISB35000 technology does not utilize a standard

type I/O cell but is a leader in the emerging Sea of

I/O approach to handling the chip interface problem.

This approach star ts at t he bond pad area of the I/O

where the pad size and pitch is not determined until

the customers choice of pack aging, signal interface

standards and I/O count is considered. Wire bond

pad spacings for 80 micron centres are available

where large signal counts are most important.

Pad spacing can be increased incrementally. It is

expected that most designs will use 100 or 120

micron spacings. It is also possible to use different

spacings for different width output sections when

needed within the same device.

Along with the variable bond pad spacing the I/O

output transistor section does not have a fixed

width. Previous technologies utilized a design approach where the desired full function buffer was

designed for a maximum current taking one pad

location with the usual current in the range of twenty

four milliamps. T he approach followed in ISB35000

is to have identical twenty m ic ron wide output transistor slices stepped around the die. Each slice

contains one set of protect ion diodes to the external

power rails and eight P and eight N transistors. T he

transistors are specifically laid out and selectively

non salicided for ESD protection and latch up prevention. These slices are paralleled to meet the

current needs of the user, for example, to c onstruc t

a 24mA sink and 12mA source LVTTL buffer, a

number of slices would be us ed. T he next group of

devices that makes up the I/ O circuit s is again a 20

u wide slice of specialized transistors that are utilized to form the slew rate c ontrol sections of the I/ O.

Each of these slices has circuits to control the

switching of up two sections of P and N output

transistors. These sections are of course created

from the output transis tor slic e above the slew r ate

section and can be connected as desired by the

designer. Many configurations of circuits can be

created to supply the des ired r esults wit h s lew r ate

slices paralleled with multiple output sections. A

further function of the scan circuits is current spike

suppression during switching of the I/O trans istors .

The logic utiliz ed causes the conduct ing transis tors

to turn off before the opposing set of transistors turn

on.

Inside the slew rate sections the next slices of

specialized designed components step on a 40

micron wide pattern. The first of these 40 micron

wide sections is utilized for predriver circuits ; these

include specialized built in test func tions for the I/O .

The predriver of course interfaces the core signals

controlling tristate and switching functions with the

slew rate and output transistor sections but it also

allows all Output Buffers to be driven high, low or

put into trist ate regardless of the stat e of the internal

logic greatly simplifying parametric testing of the

part and also assisting customers who wish to use

this feature during board testing. Note that all output

4/15

ISB35000 SERIES

buffers can be tristated by this function including

buffers that normally do not tristate. This test function also turns off all pull up or down devices and

shuts down all differential receivers and converts

them into standard CMOS receivers. Inside the

predriver is a section of specializ ed transistors used

to create the receiver functions. This section includes specialized non salicide protection resistor

diodes to further protect the gates of the receiver

devices from E SD and latch up. Also present in this

section are devices that can be utilized to form

various parameteriseable pull up, pull down and

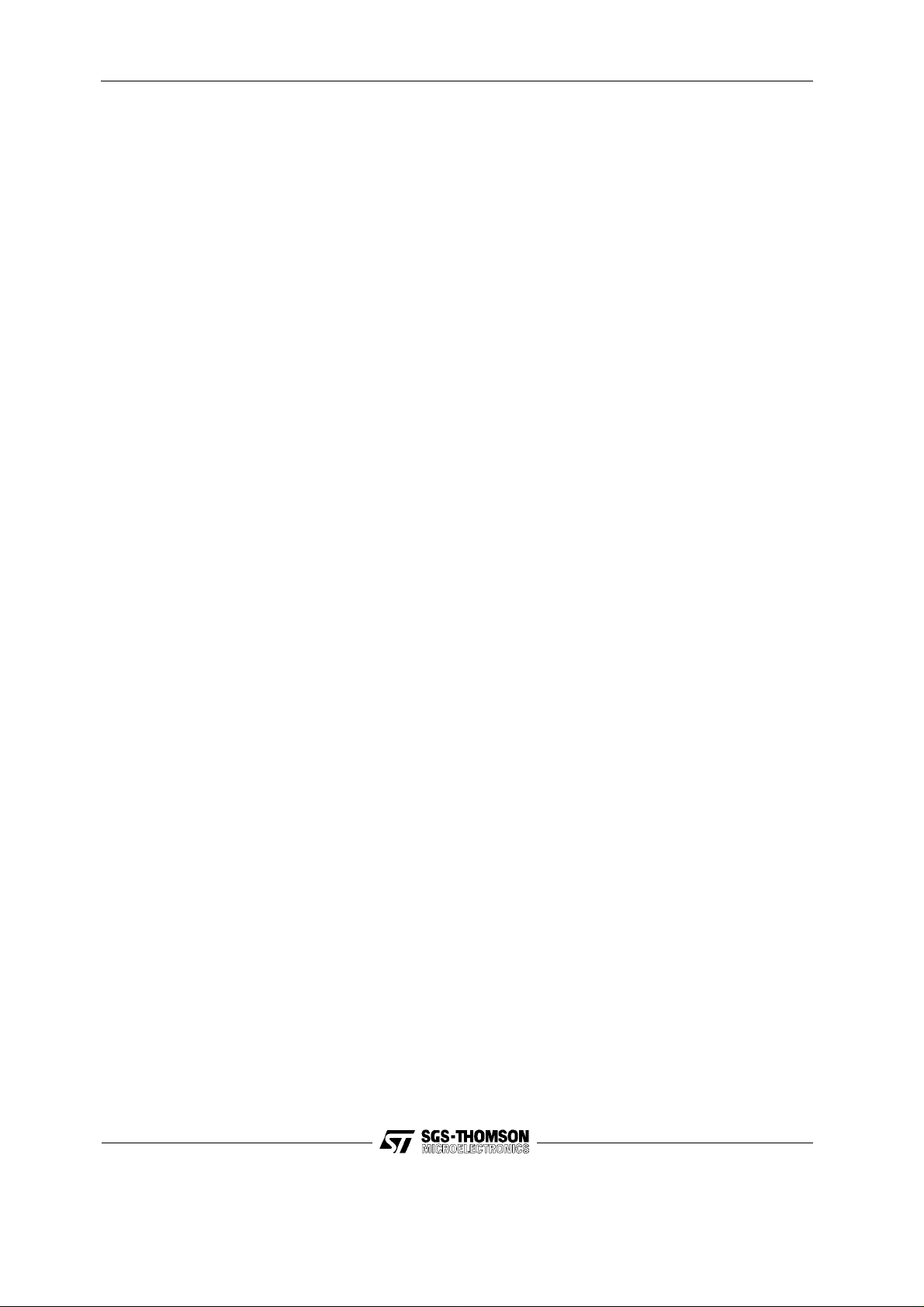

Figure 3. IS B35000 I/O Technology

Edge of Die

Guardring

Programmable

Pitch Bond

Pad

buskeeper funct ions. A full set of standard receivers

with pull up and pull down dev ices is pres ent in the

library. The technologies supported mat ch the output buffer capabilities and include, LVCMOS,

LVTTL, GTL, CTL, Differential, etc. and a five volt

interface capability. The last section of devices t hat

make up the I/O ring is a set of custom designed

(for com pact ness) scan lat ches and s upport ing c ircuits that can be utilized to form various types of

scan circuits conforming to the standard that the

customer is utilizing in his systems. These circuits

can be combined with internal transis tors if needed.

4mA

selected

Segmented

Output

River of Drive

Transistors

Input &

Control

SlewRate

Tristate

Buskeeper

Level Shifter

JTAG

Die Core

ISB35_PB

5/15

Loading...

Loading...