)

FEATURES

Standard INMOS link protocol

10 or 20 Mbits/sec operating speed

Communicates with transputers

IMS C011

Link adaptor

Converts between serial link and parallel bus

Converts between serial link and parallel device

Two modes of parallel operation:

Mode 1: Peripheral interface

Eight bitparallel input interface

Eight bitparallel output interface

Full handshake on input and output

Mode 2: Bus interface

Tristatebidirectional bus interface

Memory mapped registers

Interrupt capability

Single +5V 5% power supply

TTL and CMOS compatibility

120mW power dissipation

28 pin 0.6” plastic package

28 pin SOJ package

28 pin LCCC package

Extended temperature version available

System

Services

Link

System

Services

Mode 1

Input

Interface

Output

Interface

Interrupt

Control

Register

Select

8

8

APPLICATIONS

Programmable I/O for transputer

Connecting microprocessors to transputers

High speed links between microprocessors

Inter-family microprocessor interfacing

Interconnecting different speed links

Link

Mode 2

Data and

Status

Registers

8

July 1995

42 1412 08

1/30

Contents

1 Introduction 3......................................................

2 Pin designations 4..................................................

3 System services 5..................................................

3.1 Power 5.....................................................................

3.2 CapMinus 5.................................................................

3.3 ClockIn 5....................................................................

3.4 SeparateIQ 6................................................................

3.5 Reset 7.....................................................................

4 Links 9.............................................................

5 Mode 1 parallel interface 12...........................................

5.1 Input port 12..................................................................

5.2 Output port 13................................................................

6 Mode 2 parallel interface 14...........................................

6.1 D0–7 14......................................................................

6.2 notCS 14.....................................................................

6.3 RnotW 14....................................................................

6.4 RS0–1 14....................................................................

6.5 InputInt 17....................................................................

6.6 OutputInt 18..................................................................

6.7 Data read 18..................................................................

6.8 Data write 18.................................................................

7 Electrical specifications 19...........................................

7.1 DC electrical characteristics 19..................................................

7.2 Equivalent circuits 20..........................................................

7.3 AC timingcharacteristics 21....................................................

7.4 Power rating 23...............................................................

8 Package details 24...................................................

8.1 Package pinouts 24............................................................

8.2 28-pin plastic DIL package dimensions 25........................................

8.3 28-pin SOJ package dimensions 26..............................................

8.4 28-pin LCCC package dimensions 27............................................

8.5 Thermal specification 28.......................................................

9 Ordering 29..........................................................

/30

2

1 Introduction

The INMOScommunicationlink is a highspeedsystem interconnectwhich providesfull duplex communication between members of the transputer family, according to the INMOS serial link protocol. The

IMS C011, a member of thisfamily, provides for full duplex transputer link communication with standard

microprocessor and sub-system architectures, by converting bi-directional serial link data into parallel

data streams.

Alltransputerproductswhichuse communicationlinks, regardless ofdevicetype,supportastandardcommunications frequency of 10 Mbits/sec; most products also support 20 Mbits/sec. Products of different

typeorperformancecan,therefore,beinterconnecteddirectlyandfuturesystemswillbeabletocommunicate directly with those of today.The IMS C011link will run ateither thestandard speedof 10 Mbits/sec

or at thehigherspeed of 20 Mbits/sec.Data reception is asynchronous,allowing communication to be independent of clock phase.

The link adaptor can be operated in one oftwo modes.In Mode 1the IMSC011converts between alink

and two independent fully handshaken byte-wide interfaces, oneinput and one output.It can be used by

a peripheral device to communicate with a transputer,a peripheral processor or another link adaptor, or

it can provide programmable input and output pins for a transputer. Two IMS C011 devices in this mode

can be connected back to back via the parallel ports and used as a frequency changer betweendifferent

speed links.

InMode 2 theIMS C011providesan interfacebetweenanINMOSseriallinkandamicroprocessorsystem

bus. Status and data registers for both input and output ports can be accessed across the byte-wide

bi-directional interface. Twointerrupt outputs are provided, one to indicate input data available and one

for output buffer empty.

VDD

GND

CapMinus

ClockIn

Reset

SeparateIQ

LinkOut

LinkIn

VDD

GND

CapMinus

ClockIn

Reset

SeparateIQ

LinkSpeed

LinkOut

LinkIn

Input

System

Services

Link

Figure 1.1 IMS C011 Mode 1 block diagram

System

Services

Link

Interface

Output

Interface

Interrupt

Control

Register

Select

Data and

Status

Registers

8

8

8

I0–7

IAck

IValid

Q0–7

Qack

QValid

InputInt

OutputInt

RS0

RS1

RnotW

notCS

D0–7

Figure 1.2 IMS C011 Mode 2 block diagram

3

/30

2 Pin designations

Signal names are prefixed bynot if theyare active low,otherwise they are activehigh.

Pinout details for various packages are given on page 24.

Pin In/Out Function

VDD, GND Power supply and return

CapMinus External capacitor for internal clock power supply

ClockIn in Input clock

Reset in System reset

SeparateIQ in Select mode and Mode 1 link speed

LinkIn in Serial data input channel

LinkOut out Serial data output channel

Table 2.1 Services and link

Pin In/Out Function

I0-7 in Parallel input bus

IValid in Data on I0-7 is valid

IAck out Acknowledge I0-7 data received by other link

Q0-7 out Parallel output bus

QValid out Data onQ0-7 is valid

QAck in Acknowledge from device: data Q0-7 was read

IMS C011

Table 2.2 Mode 1 parallel interface

Pin In/Out Function

D0-7 in/out Bi-directional data bus

notCS in Chip select

RS0-1 in Register select

RnotW in Read/write control signal

InputInt out Interrupt on link receive buffer full

OutputInt out Interrupt on link transmit buffer empty

LinkSpeed in Select link speed as 10or 20 Mbits/sec

HoldToGND Must be connectedto GND

DoNotWire Must not be wired

Table 2.3 Mode 2 parallel interface

4

/30

3 System services

3 System services

System services include all the necessary logic to start up and maintain the IMS C011.

3.1 Power

Power is supplied to the devicevia the VDD and GND pins. The supply mustbe decoupled close to the

chip by at least one 100 nF low inductance (e.g. ceramic) capacitor between VDD and GND. Four layer

boards are recommended; if two layer boards are used, extra care should be taken in decoupling.

AC noise between VDD and GND must be kept below 200 mV peak to peak at all frequencies above

100 KHz. AC noise between VDD and the ground reference of load capacitances must be kept below

200 mV peakto peak atall frequencies above 30 MHz. Input voltagesmust not exceed specification with

respect to VDD and GND, even during power-up and power-downramping, otherwise

CMOS devices can be permanently damaged by excessive periods of latchup.

3.2 CapMinus

The internally derivedpower supply for internal clocks requires an external low leakage, low inductance

1F capacitor to be connected between VDD and CapMinus. A ceramic capacitor is preferred, with an

impedance less than 3 Ohms between 100 KHzand 10 MHz. If a polarised capacitor is used the negative

terminal should be connectedto CapMinus. TotalPCB track lengthshould be less than 50 mm. The positiveconnection ofthe capacitor mustbeconnecteddirectlytoVDD.Connectionsmust not otherwise touch

power supplies or other noisesources.

latchup

can occur.

VDD

P.C.B track

Decoupling

capacitor 1 F

Phase–locked

loops

GND

Figure 3.1 Recommended PLL decoupling

pin

VDD

CapMinus P.C.B track

3.3 ClockIn

Transputerfamily components usea standardclock frequency,supplied bythe user on theClockIn input.

The nominal frequency of this clock for all transputer family components is 5 MHz, regardless of device

type, transputer word length or processor cycle time. High frequency internal clocks are derived from

ClockIn, simplifying system design and avoiding problems of distributing high speed clocks externally.

Anumberoftransputerfamilydevicesmay be connectedto acommon clock,ormay have individualclocks

providing each one meets the specified stability criteria. In a multi-clock system the relative phasing of

ClockIn clocks isnot important, due to theasynchronous natureof the links.Mark/space ratio is unimportant provided the specified limits of ClockIn pulse widths are met.

Oscillator stability is important. ClockIn must be derived from a crystal oscillator; RC oscillators are not

sufficiently stable. ClockIn must not be distributedthrough a longchain of buffers.Clock edges mustbe

monotonic and remain within the specified voltage and time limits.

/30

5

IMS C011

Symbol Parameter Min Nom Max Units Notes

TDCLDCH ClockIn pulse width low 40 ns 1

TDCHDCL ClockIn pulse width high 40 ns 1

TDCLDCL ClockIn period 200 ns 1,2,4

TDCerror ClockIn timing error 0.5 ns 1,3

TDC1DC2 Difference in ClockIn for 2linked devices 400 ppm 1,4

TDCr ClockIn rise time 10 ns 1,5

TDCf ClockIn fall time 8 ns 1,5

Notes

1 Guaranteed, but not tested.

2 Measured between corresponding points on consecutive falling edges.

3 Variationof individual falling edgesfrom their nominal times.

4 This value allows the use of 200ppm crystal oscillatorsfor two devices connected together by

a link.

5 Clock transitions must be monotonic within the range VIH to VIL (table 7.3).

Table 3.1 Input clock

TDCerror

TDCerror

2.0V

1.5V

0.8V

TDCerror

TDCerror

TDCLDCH TDCHDCL

TDCLDCL

90%

10%

TDCf

90%

10%

TDCr

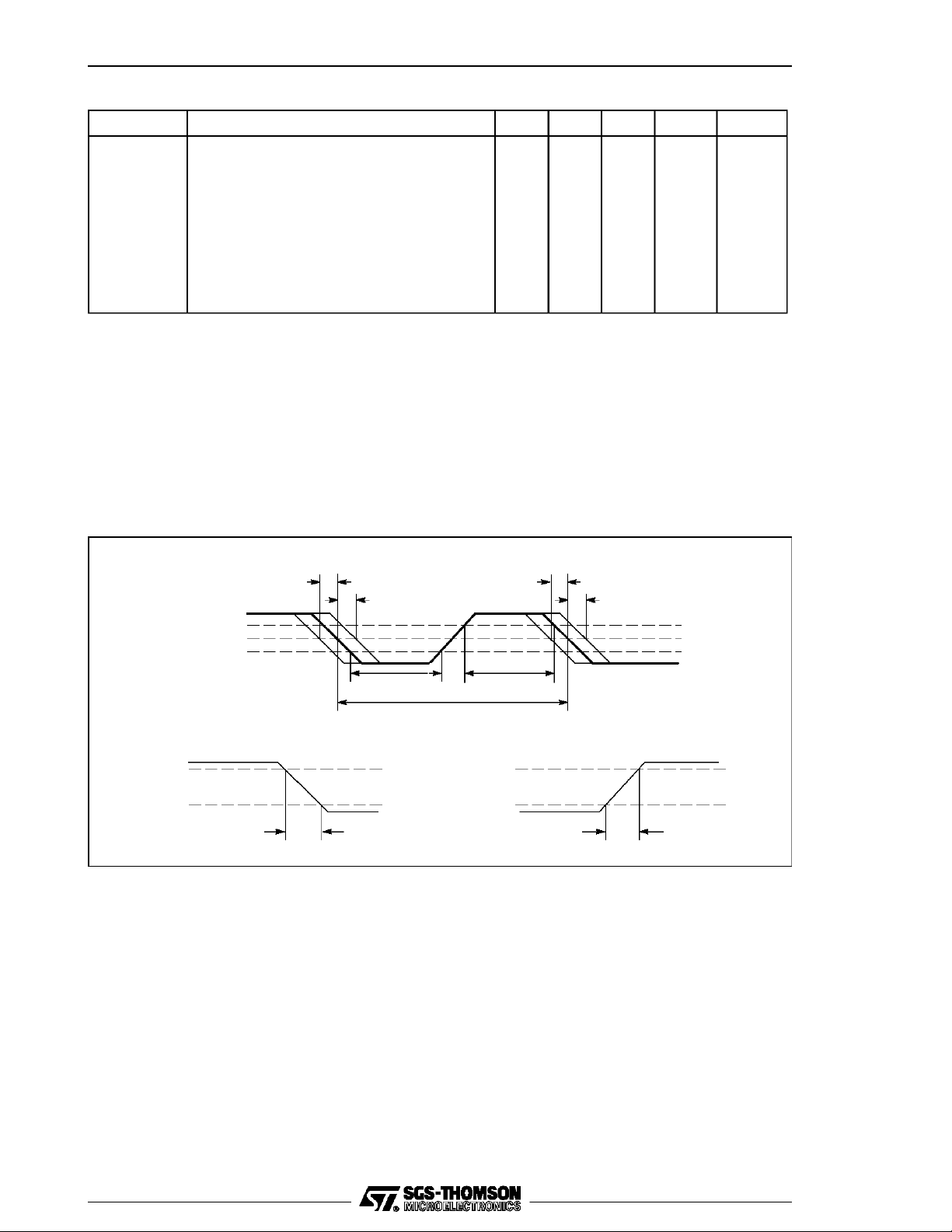

Figure 3.2 ClockIn timing

3.4 SeparateIQ

The IMS C011 link adaptor has two differentmodes of operation. Mode 1 is basically a link to peripheral

adaptor,whilst Mode 2 interfaces between a link and a microprocessor bus system.

Mode 1 can be selected for one of two link speeds by connectingSeparateIQ to VDD (10 Mbits/sec) or

to ClockIn (20 Mbits/sec).

Mode 2 is selected by connecting SeparateIQ to GND; in this mode 10 Mbits/sec or 20 Mbits/sec is selected byLinkSpeed. Link speeds arespecified for a ClockIn frequency of 5 MHz.

In order toselect thelink speed, SeparateIQ may be changeddynamically providing thelink is ina quiescentstateandno inputor outputisrequired.Resetmust beapplied subsequenttotheselectiontoinitialise

/30

6

3 System services

the device. If ClockIn is gated to achieve this, its skew must be limited to the value TDCHSIQH shown

in table3.3. The mode of operation (Mode 1, Mode 2) must not be changed dynamically.

SeparateIQ Mode Link Speed Mbits/sec

VDD 110

ClockIn 120

GND 210or20

Table 3.2 SeparateIQ mode selection

Symbol Parameter Min Nom Max Units Notes

TDCHSIQH Skew fromClockIn to ClockIn 20 ns 1

Notes

1 Skew between ClockIn arriving on the ClockIn pin and on the SeparateIQ pin.

Table 3.3 SeparateIQ

3.5 Reset

The Reset pin can go high withVDD, but must at no time exceed the maximumspecified voltageforVIH.

After VDD is valid ClockIn should be running for a minimum period TDCVRL before theendof Reset. All

inputs, with the exceptionof ClockIn and SeparateIQ (plus LinkSpeed in mode 2), must be heldin their

inactive state during reset.

Reset initialises theIMS C011to the following state: LinkOut is held low; the control outputs (IAck and

QValidin Mode 1, InputInt and OutputInt in Mode 2)are held low; interrupts (Mode2) are disabled; the

states of Q0-7 in Mode 1 are unspecified; D0-7 in Mode 2 are high impedance.

Symbol Parameter Min Nom Max Units Notes

TPVRH Power valid before Reset 10 ms

TRHRL Reset pulse width high 8 ClockIn 1

TDCVRL ClockIn running before Reset end 10 ms 2

TRLIvH Reset low before IValid high (mode 1) 0 ns

TRLCSL Reset low before chip select low (mode 2) 0 ns

Notes

1 Full periods of ClockIn TDCLDCL required.

2 At power-on reset.

Table 3.4 Reset

7

/30

ClockIn

VDD

IMS C011

TDCVRL

Reset

IValid

notCS

TPVRH

TRHRL

TRLIvH

TRLCSL

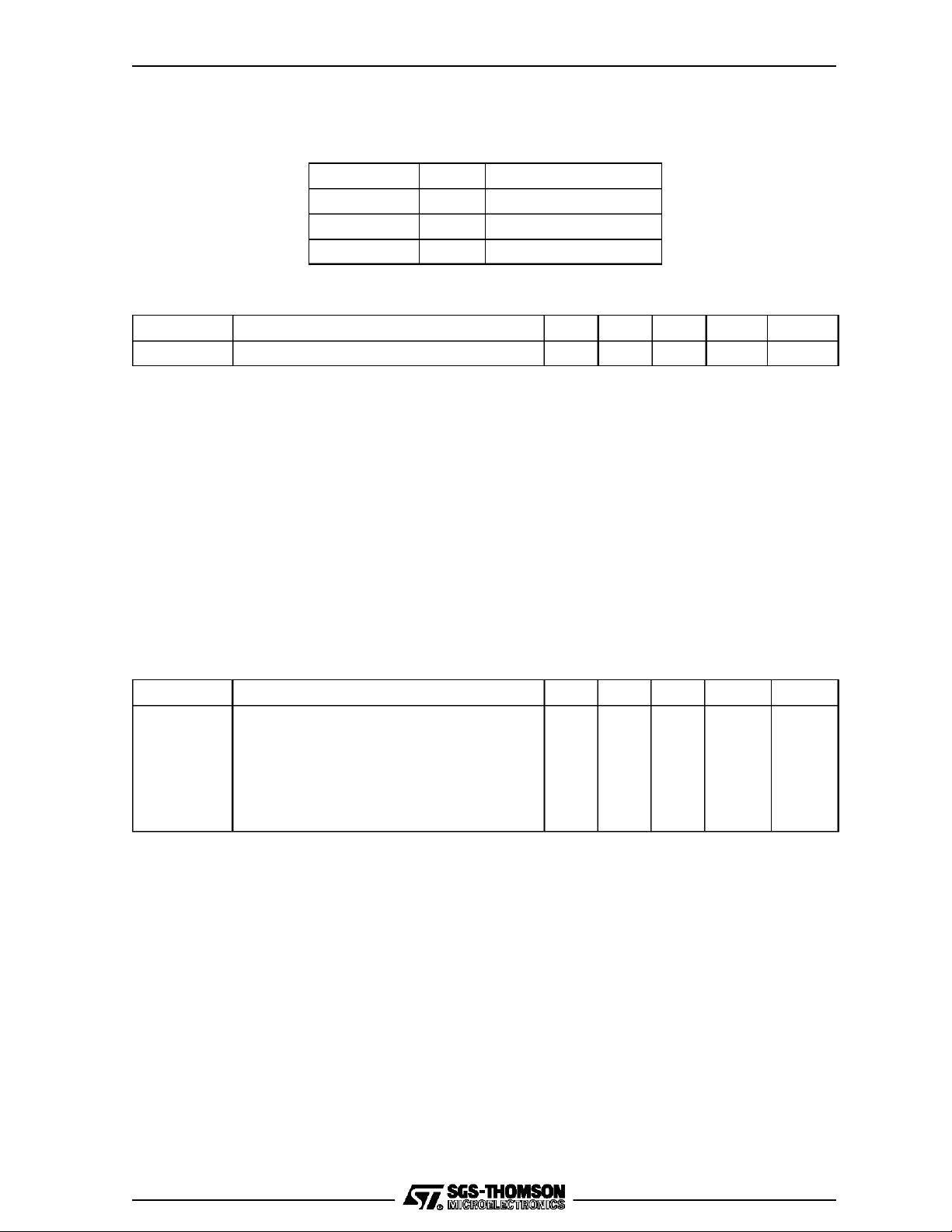

Figure 3.3 Reset timing

8

/30

4 Links

4 Links

INMOS bi-directional serial links provide synchronized communication between transputer productsand

with the outside world. Eachlink comprises aninput channel and output channel. A link between two devices is implemented byconnecting a link interface on onedevice to a link interfaceon the other device.

Everybyteof datasent onalinkis acknowledgedontheinput ofthesamelink,thus eachsignal line carries

both data and control information.

The quiescent state of a link output is low. Each data byte is transmitted as a high start bit followed by a

one bitfollowed by eight data bits followed bya low stopbit. The leastsignificant bit of data is transmitted

first. After transmitting a data byte the sender waits for the acknowledge,which consists of a high startbit

followed by a zero bit. The acknowledge signifies both that a process was able to receive the acknowledged data byte and that the receiving link is able to receive another byte.

Links are not synchronised with ClockIn and are insensitive to its phase. Thuslinks from independently

clockedsystemsmaycommunicate,providingonlythattheclocksarenominally identicaland withinspecification.

Links are TTL compatible andintended to be usedin electrically quietenvironments, between devices on

a singleprinted circuit board or between two boardsvia a backplane. Direct connectionmay be made between devices separated by a distance of less than 300 millimetres. For longer distances a matched

100 ohm transmissionline should be used with series matchingresistors RM. When this is donethe line

delay should be less than 0.4 bit time to ensure that the reflection returnsbefore the next databit is sent.

Buffers may be used for very long transmissions. If so, their overall propagation delay should be stable

within the skew tolerance of the link, although the absolute value of the delay is immaterial.

The IMS C011 link supports the standardINMOS communicationspeed of10 Mbits/sec. In addition it can

be used at 20Mbits/sec.Link speed canbe selectedin one of two ways.In Mode 1it is altered bySepara-

teIQ (page 6). In Mode 2 it is selected by LinkSpeed; when the LinkSpeed pin is low,the link operates

at the standard 10 Mbits/sec;when high it operates at 20 Mbits/sec.

HH L LH

01234567

Data

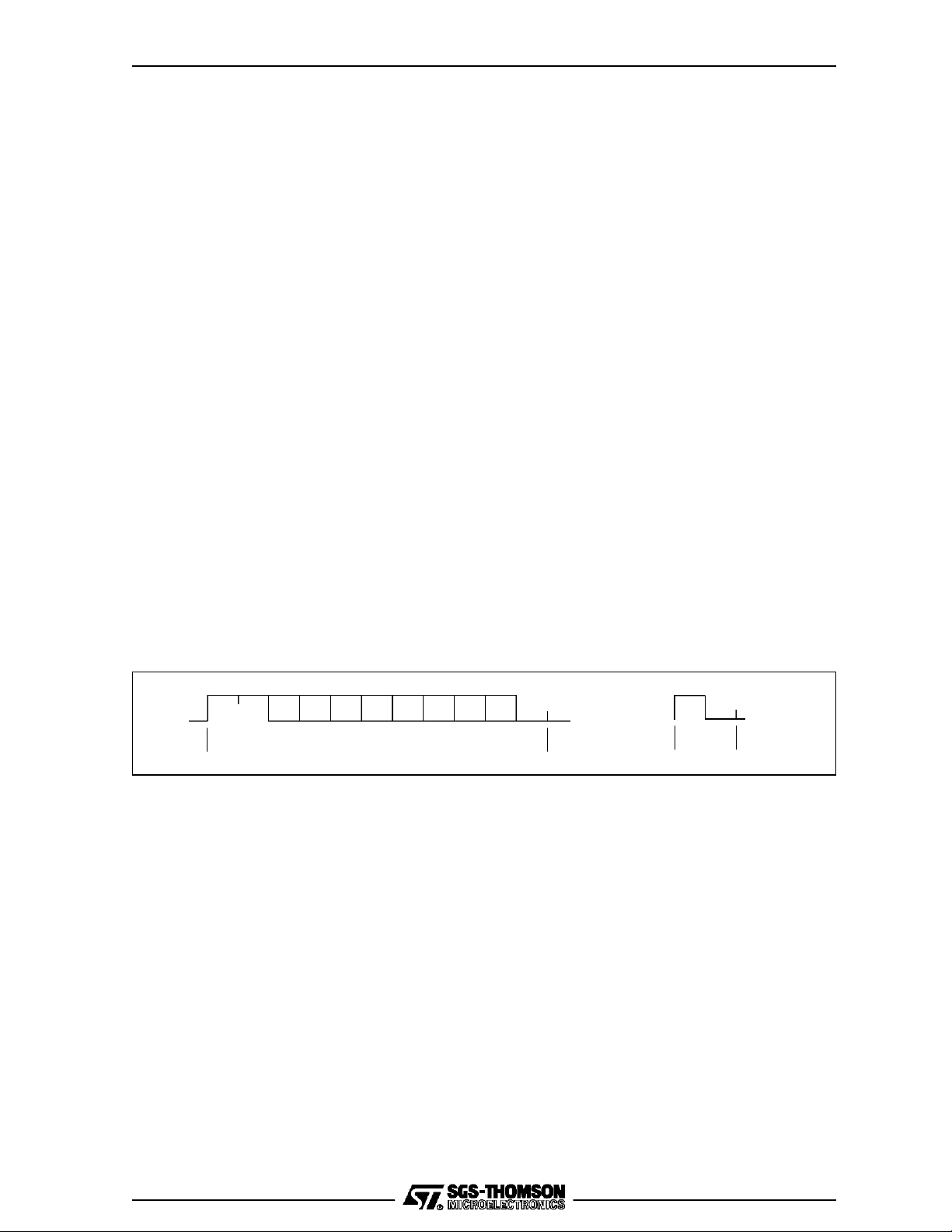

Figure 4.1 IMS C011link data and acknowledgepackets

Ack

9

/30

Loading...

Loading...