SGS Thomson Microelectronics ETC5057N, ETC5057FN, ETC5057D, ETC5054N, ETC5054FN Datasheet

...

ETC5054

ETC5057

SERIAL INTERFACECODEC/FILTER

COMPLETE CODEC AND FILTERING SYSTEM (DEVICE)INCLUDING:

– Transmithigh-passand low-pass filtering.

– Receivelow-passfilterwith sin x/x correction.

– ActiveRC noise filters

– µ-laworA-lawcompatibl eCOderandDECoder .

– Internalprecisionvoltage reference.

– SerialI/O interface.

– Internalauto-zerocircuitry.

A-LAW 16 PINS (ETC5057FN,20 PINS)

µ-LAW WITHOUT SIGNALING, 16 PINS

(ETC5054FN,20 PINS)

MEETS OR EXCEEDS ALL D3/D4 AND

CCITT SPECIFICATIONS

±

5V OPERATION

LOW OPERATING POWER - TYPICALLY 60

mW

POWER-DOWN STANDBY MODE - TYPICALLY 3 mW

AUTOMATIC POWER-DOWN

TTL OR CMOS COMPATIBLE DIGITAL IN-

TERFACES

MAXIMIZES LINE INTERFACE CARD CIR-

CUIT DENSITY

0to70°C OPERATION

DESCRIPTION

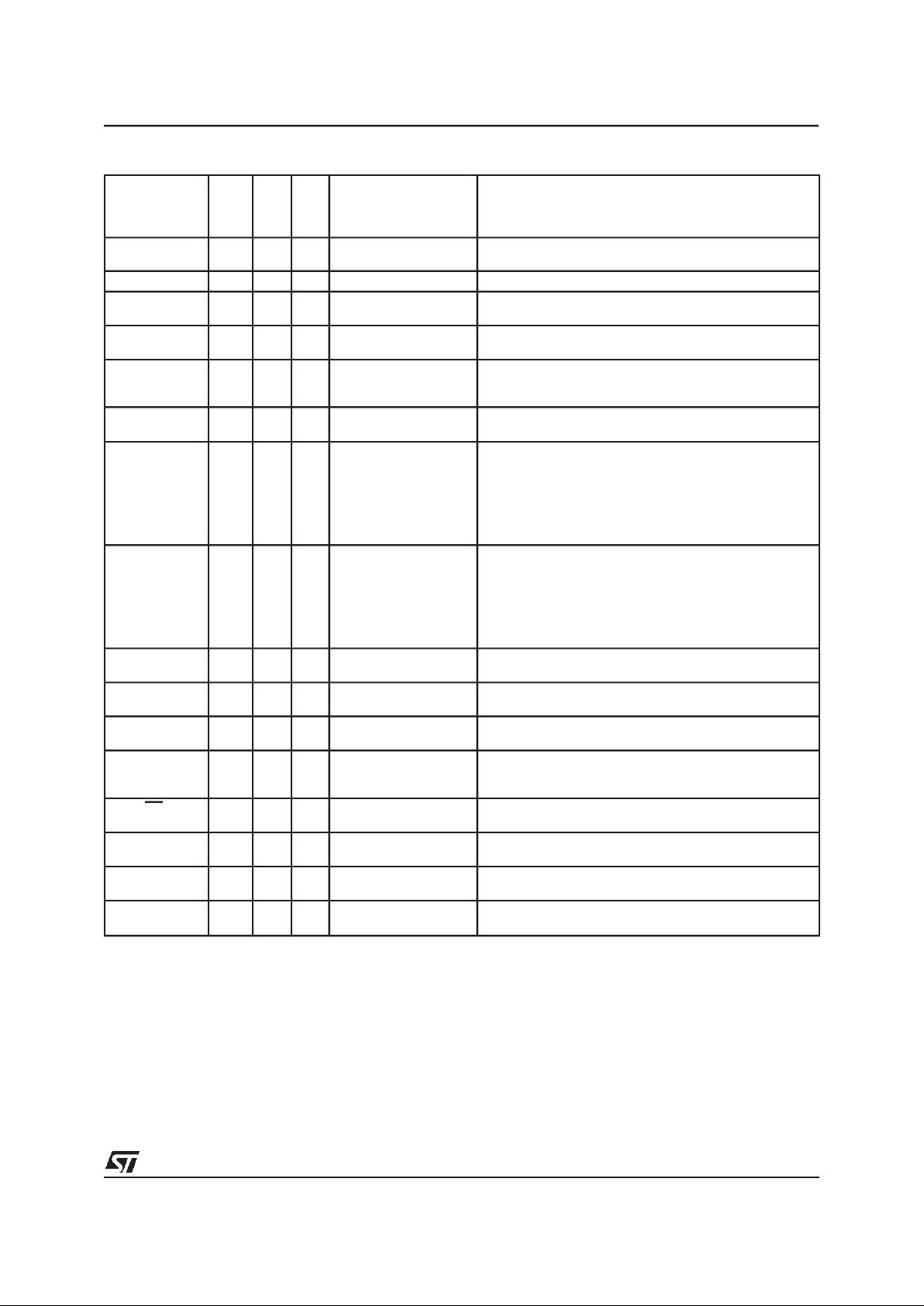

The ETC5057/ETC5054 family consists of A-law

and µ–law monolithic PCM CODEC/filters utilizing

the A/D and D/A conversionarchitectureshown in

the block diagram below, and a serial PCM interface. The devices are fabricated using doublepoly CMOS process. The encode portion of each

device consists of an input gain adjust amplifier,

an active RC pre-filter which eliminates very high

frequency noise prior to entering a switched-capacitor band-pass filter that rejects signals below

200 Hz and above 3400 Hz. Also included are

auto-zerocircuitry and a compandingcoder which

samples the filtered signal and encodes it in the

companded A-law orµ–law PCM format. The decode portion of each device consists of an expanding decoder, which reconstructs the analog

signal from the companded A-law or µ–law code,

a low-pass filter which corrects for the sin x/x response of the decoder output and rejects signals

above 3400 Hz and is followed by a single-ended

power amplifier capable of driving low impedance

loads. The devices require 1.536 MHz, 1.544

MHz, or 2.048 MHz transmit and receive master

clocks, which may be asynchronous,transmit and

receive bit clocks which may vary from 64 kHz to

2.048 MHz, and transmit and receive frame sync

pulses. The timing of the frame sync pulses and

PCM data is compatible with both industry standard formats.

This is advanced information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

March 2000

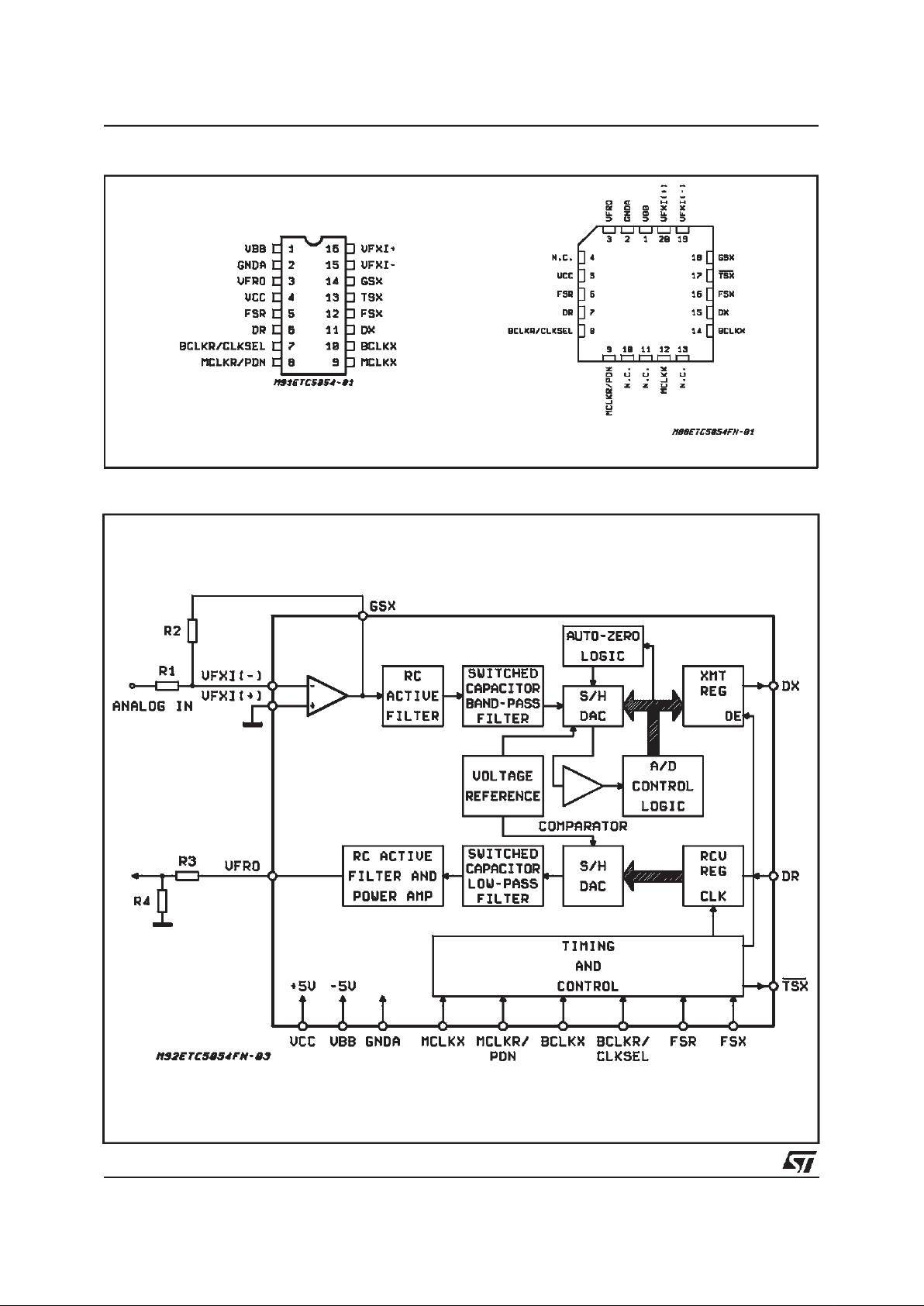

DIP16 (Plastic)

ORDERING NUMBERS:

ETC5057N

ETC5054N

SO16 (Wide)

ORDERING NUMBERS:

ETC5057D

ETC5054D

PLCC20

ORDERING NUMBERS:

ETC5057FN

ETC5054FN

1/18

PIN CONNECTIONS (Topview)

DIP and SO

PLCC

BLOCKDIAGRAM

ETC5054 - ETC5057

2/18

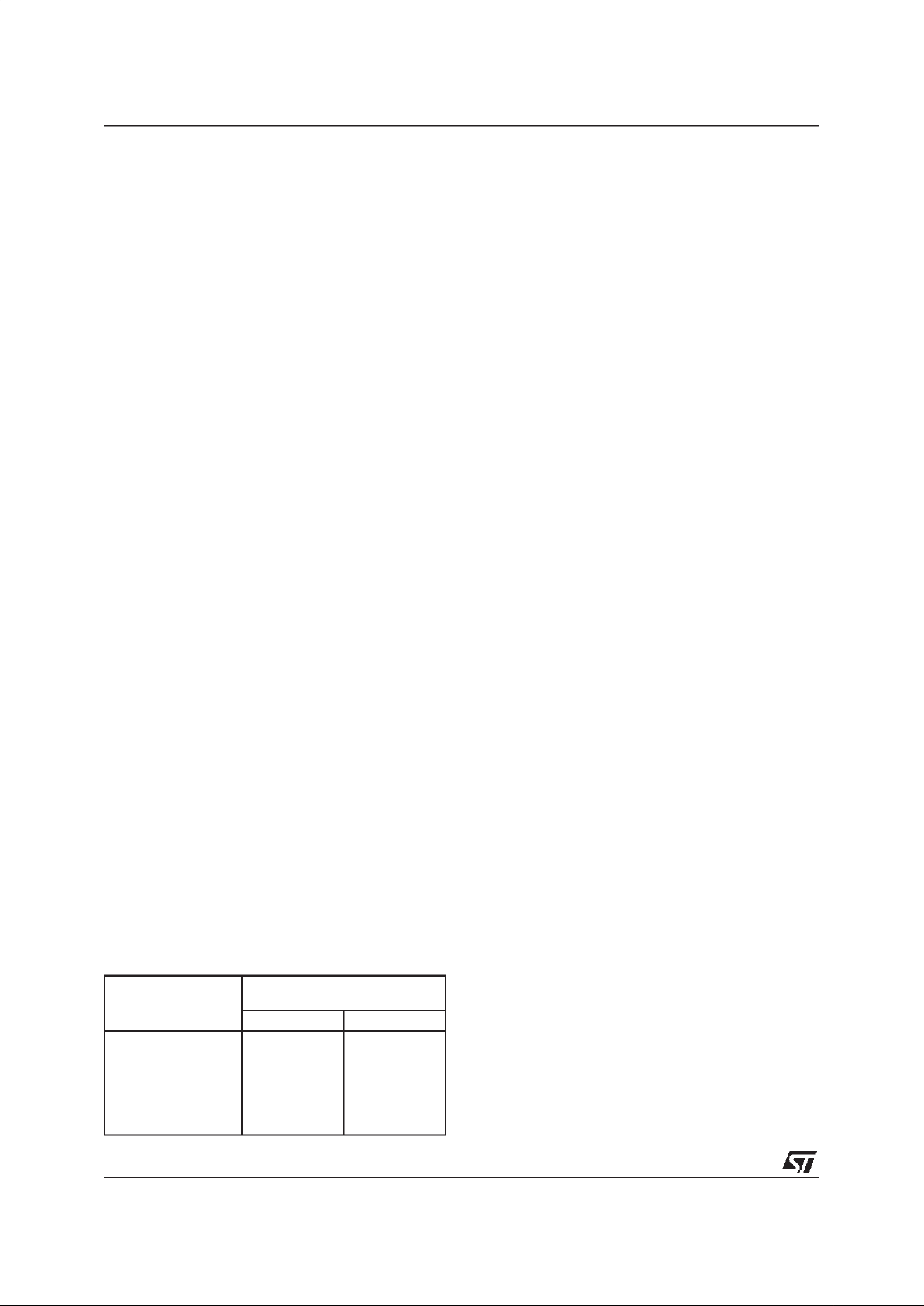

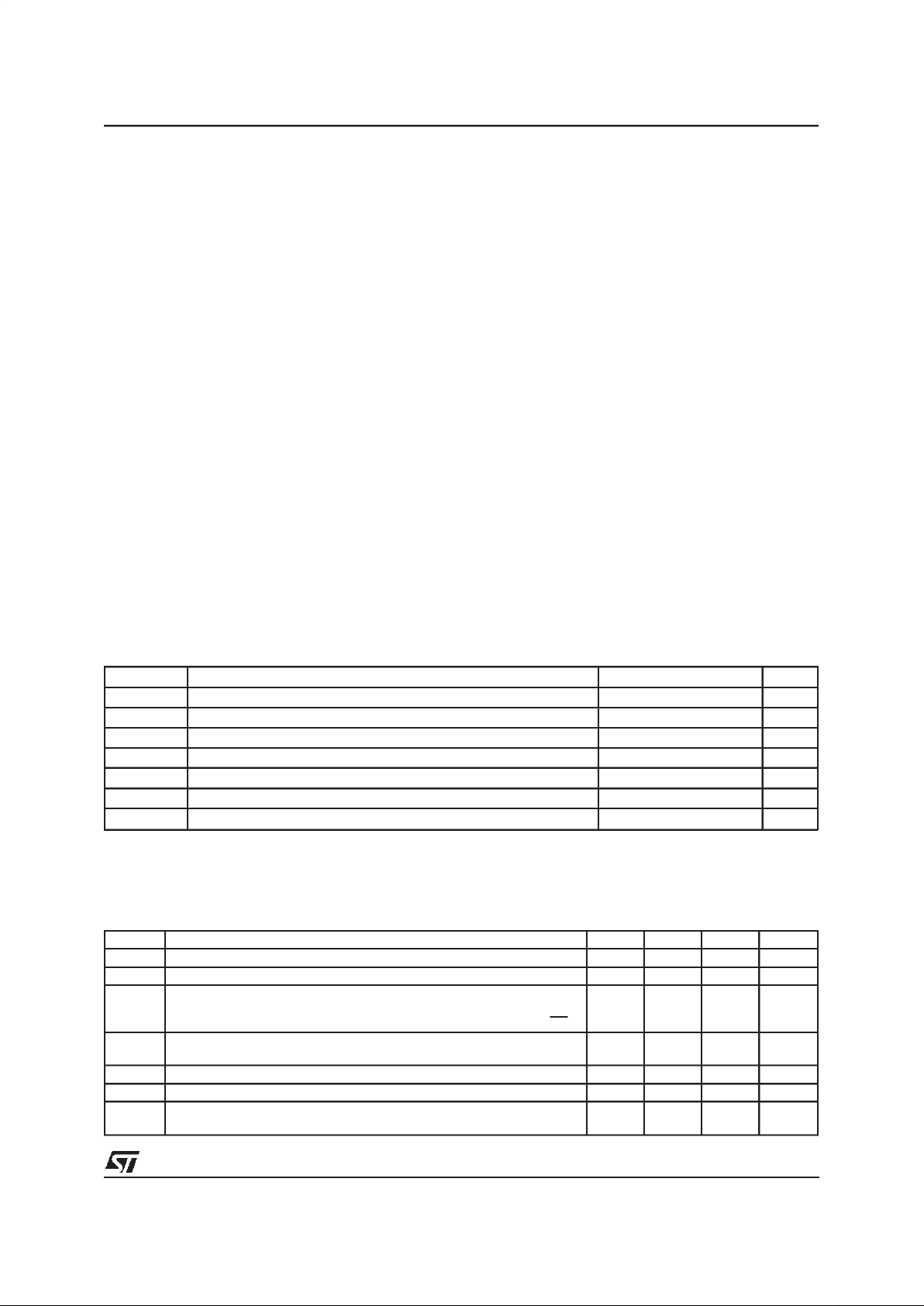

PIN DESCRIPTION

Name

Pin

Type

*

N

°

DIP

and

SO

N

°

PLCC

(**)

Function Description

V

BB

S 1 1 Negative

Power Supply

VBB=–5V±5%.

GNDA GND 2 2 Analog Ground All signals are referenced to this pin.

VF

R

O O 3 3 Receive Filter

Output

Analog Output of the Receive Filter

V

CC

S 4 5 Positive Power

Supply

VCC=+5V±5%.

FS

R

I 5 6 Receive Frame

Sync Pulse

Enables BCLKRto shift PCM data into DR.FSRis an

8kHz pulse train. See figures 1, 2 and 3 for timing

details.

D

R

I 6 7 Receive Data

Input

PCM data is shifted into DRfollowing the FSRleading

edge.

BCLK

R

/CLKSEL I 7 8 Shift-inClock Shifts data into DRafter the FSRleading edge. May

vary from 64 kHz to 2.048 MHz. Alternatively, may be

a logic input which selects either 1.536 MHz/1.544

MHz or 2.048 MHz for master clock in synchronous

mode and BCLK

X

is used for both transmit and receive

directions (see table 1). This input has an internal pullup.

MCLKR/PDN I 8 9 Receive Master Clock Must be 1.536 MHz, 1.544 MHz or 2.048 MHz. May be

asynchronous with MCLK

X

, but should be

synchronous with MCLK

X

for best performance. When

MCLK

R

is connected continuously low, MCLKXis

selected for all internal timing. When MCLK

R

is

connected continuously high, the device is powered

down.

MCLK

X

I 9 12 TransmitMaster Clock Must be 1.536 MHz, 1.544 MHz or 2.048 MHz. May be

asynchronous with MCLK

R

.

BCLK

XI

10 14 Shift-out Clock Shifts out the PCM data on DX. May vary from 64 kHz

to 2.048 MHz, but must be synchronous with MCLK

X

.

D

X

O 11 15 Transmit

Data Output

The TRI-STATE PCM data output which is enabled

by FS

X

.

FS

X

I 12 16 Transmit Frame

Sync Pulse

Enables BCLKXto shift out the PCM data on DX.FSXis

an 8 kHz pulse train. See figures 1, 2 and 3 for timing

details.

TS

X

O 13 17 Transmit Time Slot Open drain output which pulses low during the encoder

time slot. Recommended to be grounded if not used.

GS

X

O 14 18 Gain Set Analog output of the transmit input amplifier. Used to

set gain externally.

VF

X

I

–

I 15 19 Inverting Amplifier

Input

Inverting Input of the Transmit Input Amplifier.

VF

X

I

+

I 16 20 Non-inverting Amplifier

Input

Non-inverting Input of the Transmit Input Amplifier.

(*) I: Input, O: Output,S: Power Supply

(**) Pins 4,10,11 and 13 are not connected

TRI-STATEis a trademark of NationalSemiconductor Corp.

ETC5054 - ETC5057

3/18

FUNCTIONAL DESCRIPTION

POWER-UP

When power is first applied, power-on reset cir-

cuitry initializes the device and places it into

the power-down mode. All non-essential circuits

are deactivatedand the D

X

and VFRO outputs are

put in high impedance states. To power-up the

device, a logical low level or clock must be applied to the MCLK

R

/PDN pin and FSXand/or FS

R

pulses must be present. Thus, 2 power-down

control modes are available. The first is to pull the

MCLK

R

/PDN pin high ; the alternative is to hold

both FS

X

and FSRinputs continuously low. The

device will power-down approximately 2 ms after

the last FS

X

or FSRpulse. Power-up will occur on

the first FS

X

or FSRpulse. The TRI-STATE PCM

data output, D

X

, will remain in the high impedance

state until the secondFS

X

pulse.

SYNCHRONOUS OPERATION

For synchronous operation, the same master

clock and bit clock should be used for both the

transmit and receive directions. In this mode, a

clock must be applied to MCLK

X

and the

MCLK

R

/PDN pin can be used as a power-down

control. A low level on MCLK

R

/PDN powers up

the device and a high level powers down the device. In either case, MCLK

X

will be selected as

the master clock for both the transmit and receive

circuits.A bit clock must also be applied to BCLK

X

and the BCLKR/CKSEL can be used to select the

proper internal divider for a master clock of 1.536

MHz, 1.544 MHz or 2.048 MHz. For 1.544 MHz

operation, the device automatically compensates

for the 193rd clock pulse each frame. With a fixed

level on the BCLK

R

/CLKSEL pin, BCLKXwill be

selected as the bit clock for both the transmit and

receive directions. Table 1 indicates the frequencies of operation which can be selected, depending on the state of BCLK

R

/CLKSEL. In this syn-

chronous mode, the bit clock, BCLK

X

, may be

from 64 kHz to 2.048 MHz, but must be synchronous with MCLK

X

.

Each FS

X

pulse begins the encoding cycle and

the PCM data from the previous encode cycle is

shifted out of the enabled D

X

output on the posi-

tive edge of BCLK

X

. After 8 bit clock periods, the

TRI-STATE D

X

output is returned to a high im-

pedance state. With and FS

R

pulse, PCM data is

latched via the D

R

input on the negative edge of

BCLK

X

(or BCLKRif running). FSXand FSRmust

be synchronouswith MCLK

X/R

.

ASYNCHRONOUSOPERATION

For asynchronous operation, separate transmit

and receive clocks may be applied, MCLK

X

and

MCLK

R

must be 2.048 MHz for the ETC5057, or

1.536 MHz, 1.544 MHz for the ETC5054, and

need not be synchronous. For best transmission

performance, however, MCLK

R

should be syn-

chronous with MCLK

X

, which is easily achieved

by applying only static logic levels to the

MCLK

R

/PDN pin. This will automatically connect

MCLK

X

to all internal MCLKRfunctions (see pin

description).For 1.544 MHz operation, the device

automatically compensates for the 193rd clock

pulse each frame. FS

X

startseach encoding cycle

and must be synchronous with MCLK

X

and

BCLK

X

.FSRstartseach decoding cycle and must

be synchronous with BCLK

R

. BCLKRmust be a

clock, the logic levels shown in table 1 are not

valid in asynchronous mode. BCLK

X

and BCLK

R

may operate from 64 kHz to 2.048 MHz.

SHORTFRAME SYNC OPERATION

The device can utilize either a short frame sync

pulse or a long frame sync pulse. Upon power initialization, the device assumes a short frame

mode. In this mode, both frame sync pulses, FS

X

and FSR, must be one bit clock period long, with

timing relationships specifiedin figure 2. With FS

X

high during a falling edge of BCLKXthe next rising edge of BCLK

X

enables the DXTRI-STATE

output buffer, which will output the sign bit. The

followingseven rising edges clock out the remaining seven bits, and the next falling edge disables

the D

X

output.With FSRhigh during a fallingedge

of BCLK

R

(BCLKXin synchronous mode), the

next falling edge of BCLK

R

latchesin the sign bit.

The following seven falling edges latch in the

seven remaining bits. Both devices may utilize the

short frame sync pulse in synchronous or asynchronousoperatingmode.

LONGFRAME SYNC OPERATION

To use the long frame mode, both the frame sync

pulses, FS

X

and FSR, must be three or more bit

clock periodslong, with timing relationships specified in figure 3. Basedon the transmit frame sync,

FS

X

, the device will sense whether short or long

frame sync pulses are being used. For 64 kHz operation,the frame sync pulse must be kept low for

a minimum of 160 ns (see fig. 1). The D

X

TRISTATE output buffer is enabled with the rising

edge of FS

X

or the rising edge of BCLKX, whichever comes later, and the first bit clocked out is

the sign bit. The following seven BCLK

X

rising

Table 1:SelectionofMasterClockFrequencies.

BCLKR/CLKSEL

Master Clock Frequency

Selected

ETC5057 ETC5054

Clocked

0

1 (or open circuit)

2.048 MHz

1.536 MHz or

1.544 MHz

2.048 MHz

1.536 MHz or

1.544 MHz

2.048 MHz

1.536 MHz or

1.544 MHz

ETC5054 - ETC5057

4/18

edges clock out the remaining seven bits. The D

X

output is disabled by the falling BCLKXedge following the eighth rising edge, or by FS

X

going

low, which-evercomes later. A rising edge on the

receive frame sync pulse, FS

R

, will cause the

PCM data at D

R

to be latched in on the next eight

falling edges of BCLK

R

(BCLKXin synchronous

mode). Both devices may utilize the long frame

sync pulse in synchronous or asynchronous

mode.

TRANSMITSECTION

The transmit sectioninput is an operational ampli-

fier with provision for gain adjustment using two

external resistors, see figure6. The low noise and

wide bandwidth allow gains in excess of 20 dB

across the audio passband to be realized. The op

amp drives a unitygain filter consisting of RD active pre-filter, followed by an eighth order

switched-capacitorbandpassfilter clocked at 256

kHz. The outputof this filter directly drives the encoder sample-and-holdcircuit. The A/D is of companding type according to A-law (ETC5057)or µ–

law (ETC5054) coding conventions. A precision

voltage reference is trimmed in manufacturing to

provide an input overload (t

MAX

) of nominally2.5V

peak (see table of transmission characteristics).

The FS

X

frame sync pulse controls the sampling

of the filter output, and then the successive-ap-

proximation encoding cycle begins. The 8-bit

code is then loaded into a buffer and shifted out

through D

X

at the next FSXpulse. The total encoding delay will be approximately 165 µs (due to

the transmit filter) plus 125µs (due to encoding

delay), which totals 290µs. Any offset vol-tage

due to the filters or comparator is cancelled by

sign bit integration.

RECEIVESECTION

The receive section consists of an expanding

DAC which drives a fifth order switched-capacitor

low pass filter clocked at 256 kHz. The decoder is

A-law (ETC5057) or µ–law (ETC5054) and the

5th order low pass filter corrects for the sin x/x attenuation due to the 8 kHz sample and hold.

The filter is then followedby a2nd order RC active post-filterand power amplifier capable of driving a 600Ω load to a level of 7.2 dBm. The receive section is unity-gain.Upon the occurenceof

FS

R

, the data at the DRinput is clocked in on the

falling edge of the next eight BCLK

R

(BCLKX)periods. At the end of the decoder time slot, the decoding cycle begins, and 10µs later the decoder

DAC output is updated. The total decoder delay

is∼10µs (decoder update) plus 110µs (filter

delay) plus 62.5µs (1/2 frame), which gives ap-

proximately 180µs. A mute circuitry is a active

during 10ms when power up.

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

CC

VCCto GNDA 7 V

V

BB

VBBto GNDA – 7 V

V

IN,VOUT

Voltage at any AnalogInput or Output VCC+ 0.3 to VBB– 0.3 V

Voltage at Any Digital Input or Output V

CC

+ 0.3 to GNDA – 0.3 V

T

oper

Operating Temperature Range – 25 to + 125

°

C

T

stg

Storage Temperature Range – 65 to + 150

°

C

Lead Temperature (soldering, 10 seconds) 300

°

C

ELECTRICALOPERATING CHARACTERISTICS VCC= 5.0 V ± 5%, VBB= – 5.0 V ± 5%GNDA= 0 V,

T

A

=0°Cto70°C; Typical Characteristics Specifiedat VCC=5.0 V, VBB= – 5.0 V, TA=25°C ; all signals

are referenced to GNDA.

Symbol Parameter Min. Typ. Max. Unit

V

IL

Input Low Voltage 0.6 V

V

IH

Input High Voltage 2.2 V

V

OL

Output Low Voltage

I

L

= 3.2mA D

X

IL= 3.2mA, Open Drain TS

X

0.4

0.4

V

V

V

OH

Output High Voltage

I

H

= 3.2mA D

X

2.4 V

I

IL

Input Low Current (GNDA ≤ VIN≤ VIL, all digital inputs) –10 10 µA

I

IH

Input High Current (VIH≤ VIN≤ VCC) except BCLKR/BCLKSEL –10 10 µA

I

OZ

Output Current in HIGH Impedance State (TRI-STATE)

(GNDA ≤ V

O

≤ VCC)D

X

–10 10 µA

ETC5054 - ETC5057

5/18

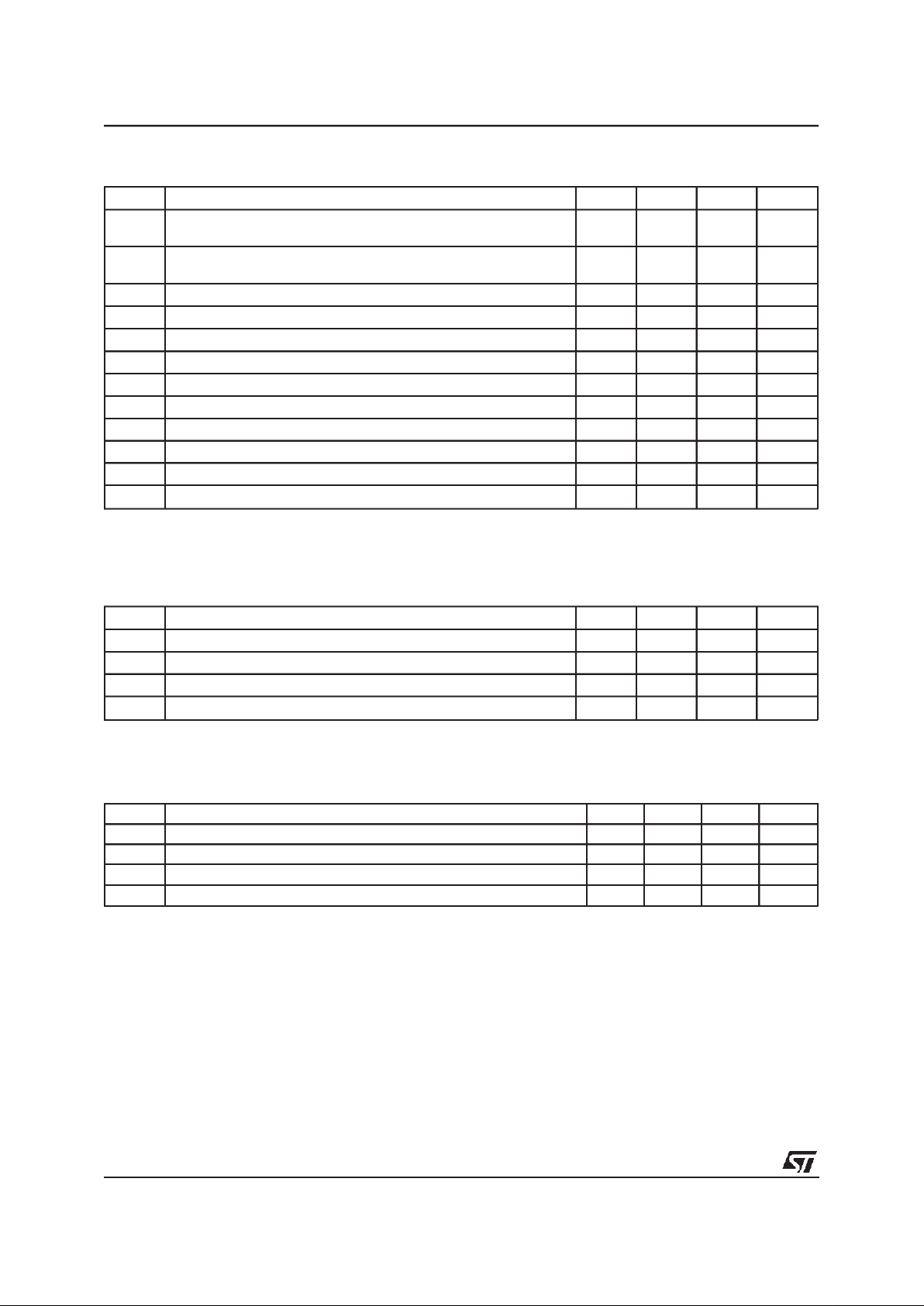

ANALOG INTERFACEWITH TRANSMIT INPUT AMPLIFIER (all devices)

Symbol Parameter Min. Typ. Max. Unit

I

I

XA Input Leakage Current VFXI+or VFXI

-

(–2.5V ≤ V ≤ +2.5V)

– 200 200 nA

R

I

XA Input Resistance VFXI+or VFXI

-

(–2.5V≤V≤+2.5V)

10 MΩ

R

O

XA OutputResistance (closed loop, unity gain) 1 3

Ω

R

L

XA Load Resistance GS

X

10 k

Ω

C

L

XA Load Capacitance GS

X

50 pF

V

O

XA Output Dynamic Range (R

L

≥

10KΩ)GS

X

±

2.8 V

AV

X

A Voltage Gain (VFXI+to GSX) 5000 V/V

F

U

XA Unity Gain Bandwidth 1 2 MHz

V

OS

XA Offset Voltage – 20 20 mV

V

CM

XA Common-mode Voltage – 2.5 2.5 V

CMRRXA Common-mode Rejection Ratio 60 dB

PSRRXA Power Supply Rejection Ratio 60 dB

ANALOG INTERFACEWITH RECEIVE FILTER (all devices)

Symbol Parameter Min. Typ. Max. Unit

R

O

RF OutputResistance VFRO13Ω

R

L

RF Load Resistance (VFRO=±2.5V) 600 Ω

C

L

RF Load Capacitance 500 pF

VOS

R

O Output DC Offset Voltage – 200 200 mV

POWERDISSIPATION(all devices)

Symbol Parameter Min. Typ. Max. Unit

I

CC

0 Power-down Current 0.5 1.5 mA

I

BB

0 Power-down Current 0.05 0.3 mA

I

CC

1 ActiveCurrent 6.0 9.0 mA

I

BB

1 Active Current 6.0 9.0 mA

ETC5054 - ETC5057

6/18

Loading...

Loading...