SGS Thomson Microelectronics 74VHC74 Datasheet

74VHC74

DUAL D-TYPE FLIP FLOP WITH PRESET AND CLEAR

■ HIGHSPEED:

f

=170MHz(TYP.)atVCC=5V

MAX

■ LOW POWERDISSIPATION:

=2 µA (MAX.) at TA=25oC

I

CC

■ HIGHNOISEIMMUNITY:

V

NIH=VNIL

■ POWERDOWN PROTECTIONON INPUTS

■ SYMMETRICALOUTPUTIMPEDANCE:

|I

|=IOL=8 mA (MIN)

OH

■ BALANCEDPROPAGATIONDELAYS:

t

≅ t

PLH

■ OPERATINGVOLTAGERANGE:

(OPR)= 2Vto5.5V

V

CC

■ PINANDFUNCTIONCOMPATIBLEWITH

=28%VCC(MIN.)

PHL

74SERIES74

■ IMPROVEDLATCH-UP IMMUNITY

DESCRIPTION

The 74VHC74 is an advancedhigh-speed CMOS

DUAL D-TYPE FLIP FLOP WITH PRESET AND

CLEAR fabricated with sub-micron silicon gate

and double-layer metal wiring C

2

MOS

technology.

A signal on the D INPUT is transfered to the Q

OUTPUT during the positive going transition of

the clock pulse.

(Micro Package)

CLEAR and PRESET are independent of the

clock and accomplished by a low setting on the

appropriateinput.

It is ideal for low power applications maintaining

high speed operation similar to equivalent Bipolar

SchottkyTTL.

Power down protection is provided on all inputs

and 0 to 7V can be accepted on inputs with no

regard to the supply voltage. This device can be

used to interface5V to 3V.

All inputs and outputs are equipped with

protection circuits against static discharge, giving

them 2KV ESD immunity and transient excess

voltage.

M

(TSSOPPackage)

ORDERCODES :

74VHC74M 74VHC74T

T

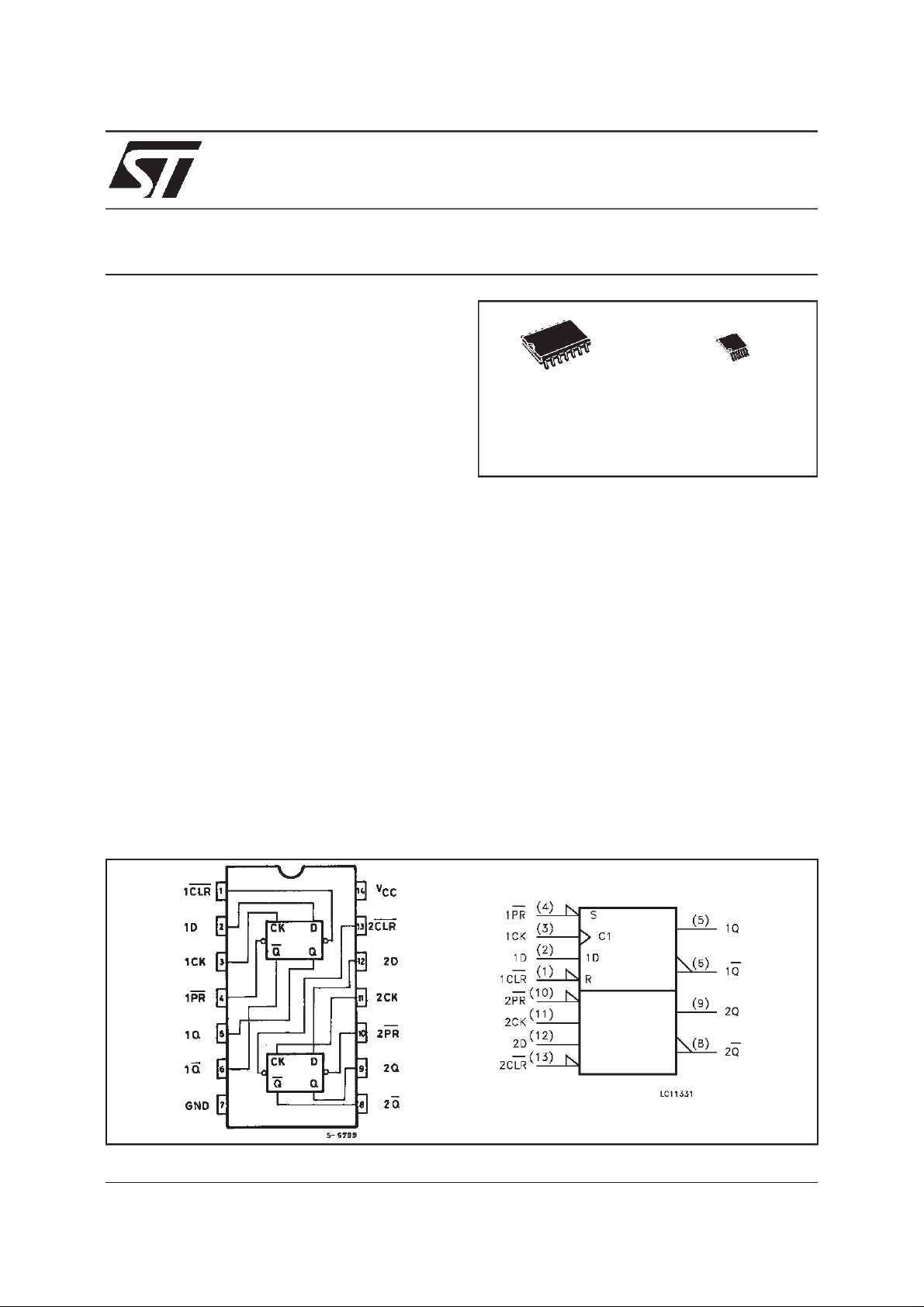

PIN CONNECTIONAND IEC LOGIC SYMBOLS

June 1999

1/10

74VHC74

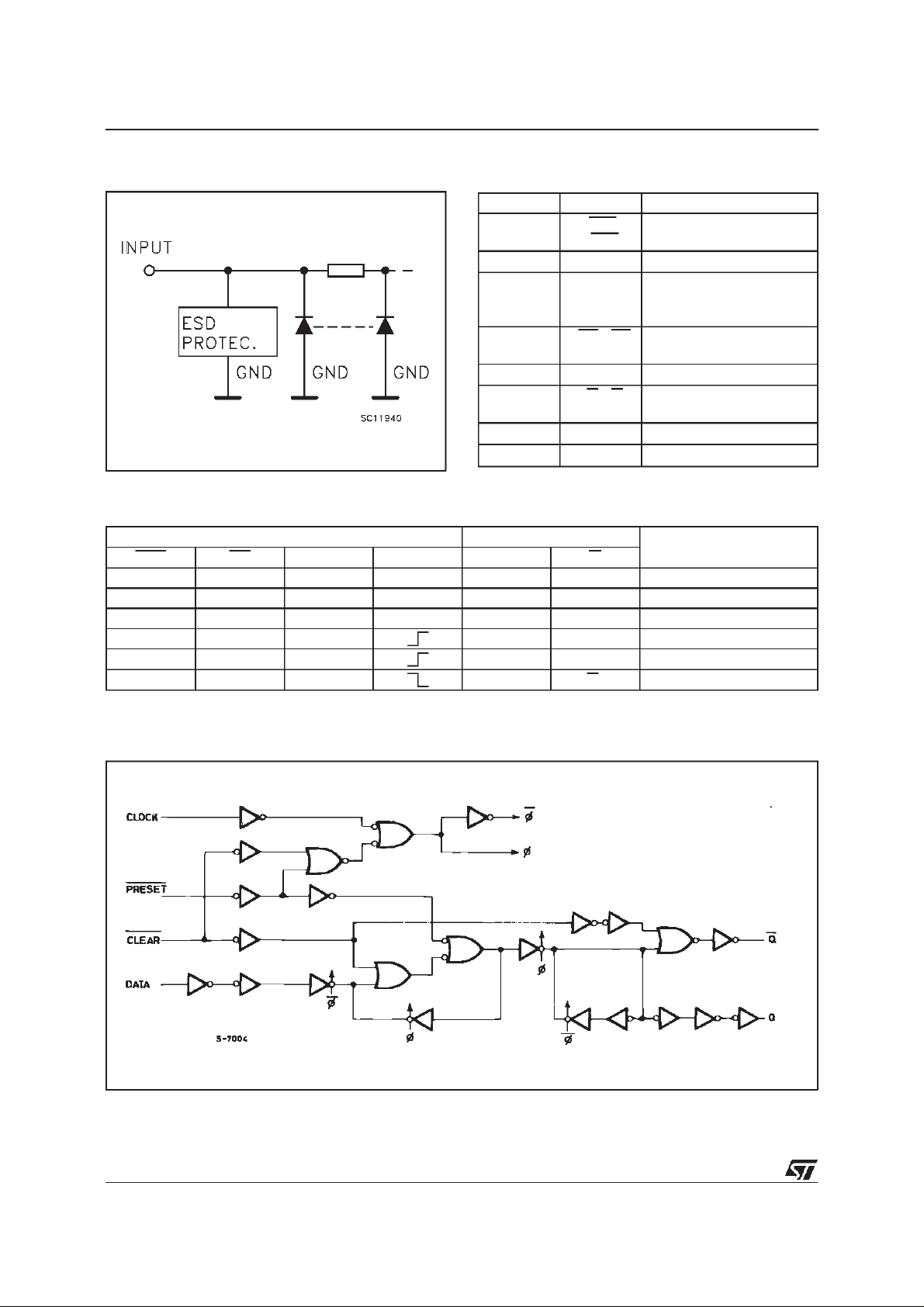

INPUT EQUIVALENTCIRCUIT

PIN DESCRIPTION

PI N No SYM BO L NAM E AND F U NCTIO N

1, 13 1CLR,

2CLR

Asyncronous Reset -

Direct Input

2, 12 1D, 2D Data Input

3, 11 1CK, 2CK Clock Input

(LOW-to-HIGH, Edge-

Triggered)

4, 10 1PR, 2PR Asyncronous Set - Direct

Input

5, 9 1Q, 2Q True Flip-Flop Outputs

6, 8 1Q, 2Q Complement Flip-Flop

Outputs

7 GND Ground (0V)

14 V

CC

Positive Supply Voltage

TRUTH TABLE

INP U T S OUT P UTS FUNCTI ON

CLRPRDCKQ Q

L H X X L H CLEAR

H L X X H L PRESET

LLXXHH

HHL LH

HHH HL

HHX Q

X:Don’tCare

n

Q

n

NO CHANGE

LOGICDIAGRAMS

Thislogic diagram has notbeused toestimate propagation delays

2/10

74VHC74

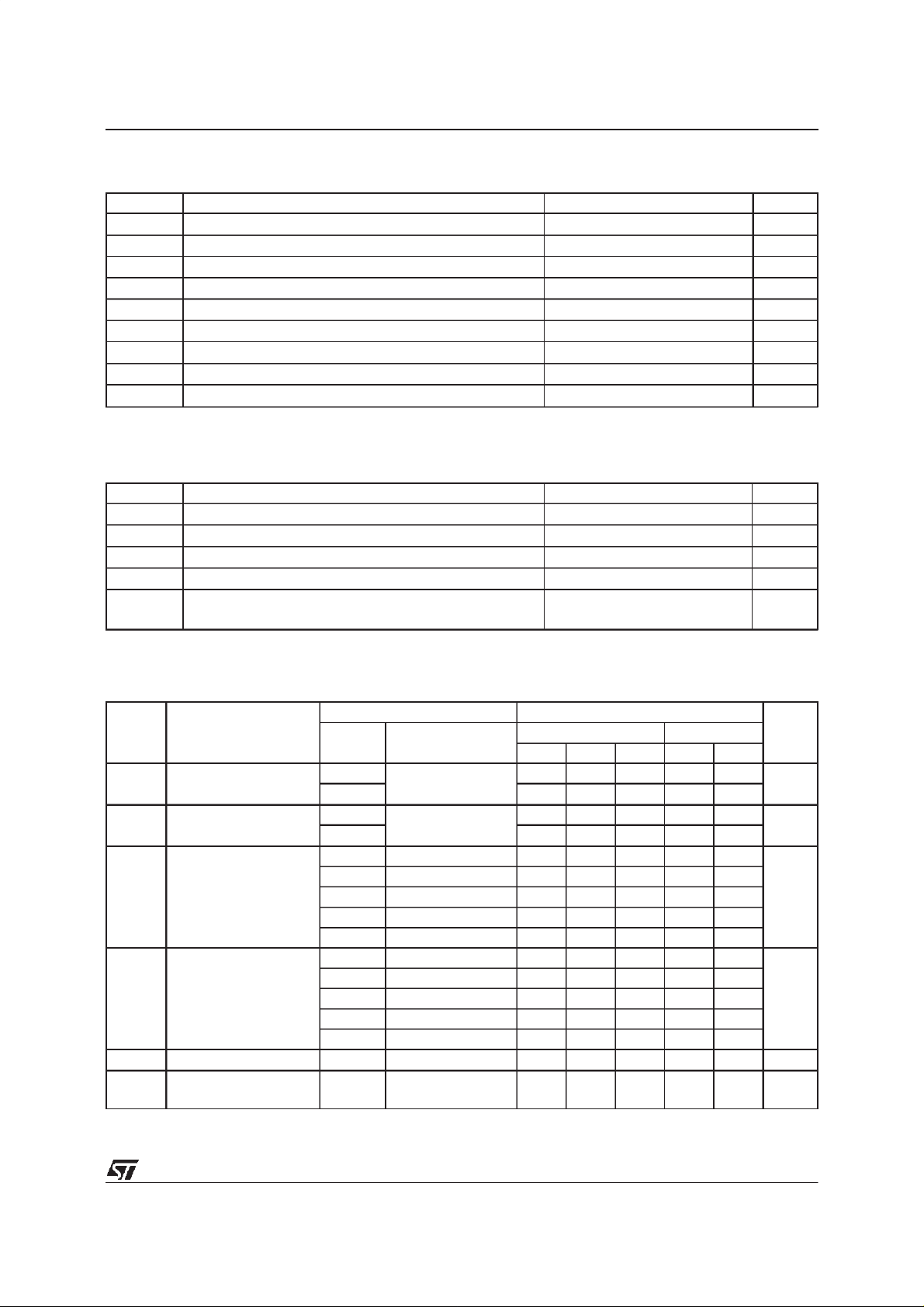

ABSOLUTE MAXIMUM RATINGS

Symb o l Para met er Val u e Un i t

V

V

V

I

I

OK

I

or I

I

CC

T

T

AbsoluteMaximum Ratingsarethosevaluesbeyond whichdamagetothedevicemayoccur. Functionaloperationunder these condition isnotimplied.

RECOMMENDEDOPERATINGCONDITIONS

Symb o l Para met er Value U n it

V

V

V

T

dt/dv

1)VINfrom30%to70%ofV

Supply Voltage -0.5 to +7.0 V

CC

DC Input Voltage -0.5 to +7.0 V

I

DC Output Voltage -0.5 to VCC+ 0.5 V

O

DC Input Diode Current - 20 mA

IK

DC Output Diode Current ± 20 mA

DC Output Current

O

DC VCCor Ground Current

GND

Storage Temperature -65 to +150

stg

Lead Temperature (10 sec) 300

L

Supply Voltage 2.0 to 5.5 V

CC

Input Voltage 0 to 5.5 V

I

Output Voltage 0 to V

O

Operating Temperature -40 to +85

op

(V

CC

CC

=3.3±0.3V)

=5.0±0.5V)

Input Rise and Fall Time (see note 1) (V

CC

25 mA

±

50 mA

±

CC

0 to 100

0to20

o

C

o

C

V

o

C

ns/V

ns/V

DC SPECIFICATIONS

Symb o l Parameter Test Conditio ns Val u e Uni t

=25oC - 40 t o 85oC

V

CC

(V)

High Level Input

V

IH

Voltage

V

Low Level Input

IL

Voltage

V

High Level Output

OH

Voltage

Low Level Output

V

OL

Voltage

Input Leakage Current 0 to 5.5 VI= 5.5V or GND ±0.1 ±1.0 µA

I

I

Quiescent Supply

I

CC

2.0 1.5 1.5

3.0 to 5.5 0.7V

2.0 0.5 0.5

3.0 to 5.5 0.3V

2.0 IO=-50 µA 1.9 2.0 1.9

3.0 I

4.5 I

3.0 I

4.5 I

=-50 µA 2.9 3.0 2.9

O

=-50µA 4.4 4.5 4.4

O

=-4 mA 2.58 2.48

O

=-8 mA 3.94 3.8

O

2.0 IO=50 µA 0.0 0.1 0.1

3.0 I

4.5 I

3.0 I

4.5 I

=50 µA 0.0 0.1 0.1

O

=50µA 0.0 0.1 0.1

O

=4 mA 0.36 0.44

O

=8 mA 0.36 0.44

O

5.5 VI=VCCorGND 2 20 µA

Current

T

A

Min. Typ. Max. Min. Max.

CC

0.7V

CC

0.3V

CC

CC

V

V

V

V

3/10

Loading...

Loading...