SGS Thomson Microelectronics 74VHC594TTR, 74VHC594MTR, 74VHC594M Datasheet

1/11February 2003

■ HIGH SPEED:t

PD

= 4.2ns (TYP.) at VCC=5V

■ LOW POWER DISSIPATION:

I

CC

=4µA (MAX.) at TA=25°C

■ HIGH NOISE IMMUNITY:

V

NIH=VNIL

= 28% VCC(MIN.)

■ POWER DOWN PROTECTION ON INPUTS

■ SYMMETRICAL OUTPUT IMPEDANCE:

|I

OH

|=IOL=8mA(MIN)

■ BALANCED PROPAG ATION DELAYS:

t

PLH

≅ t

PHL

■ OPERATING VOLTAGE RANG E:

V

CC

(OPR) = 2V to 5.5V

■ PIN AND FUNCTION COMPATIBLE WITH

74 SERIES 594

■ IMPROVED LATCH-UP IMMUNITY

■ LOW NOISE: V

OLP

= 0.8V (MAX.)

DESCRIPTION

The 74VHC594 is an high speed CMOS 8-BIT

SHIFT R EG ISTERS fabricated with sub-micron

silicon gate C

2

MOS technology.

This device contains an 8-bit serial-in, parallel-out

shift register that feeds an 8-bi t D-type s tora ge

register. Separate clocks and direct overriding

clear(SCLR,

RCLR) are p rovided for both the shift

register and the storage register.

A serial (QH’) output is provide d for cascading

purposes. Both the shift re gister and storage

register use positive-edge triggered c locks. If the

clocks are connected together, the shift register

state will always be one clock pulse ahead of the

storage register.

Power down protection is provided on all inputs

and 0 t o 7V can be accepted on inputs with no

regard to the supply voltage. This device can be

usedto interface 5V to 3V.

All inputs are equipped with protection circuits

against static discharge, giving them 2KV ESD

immunity and transient excess voltage.

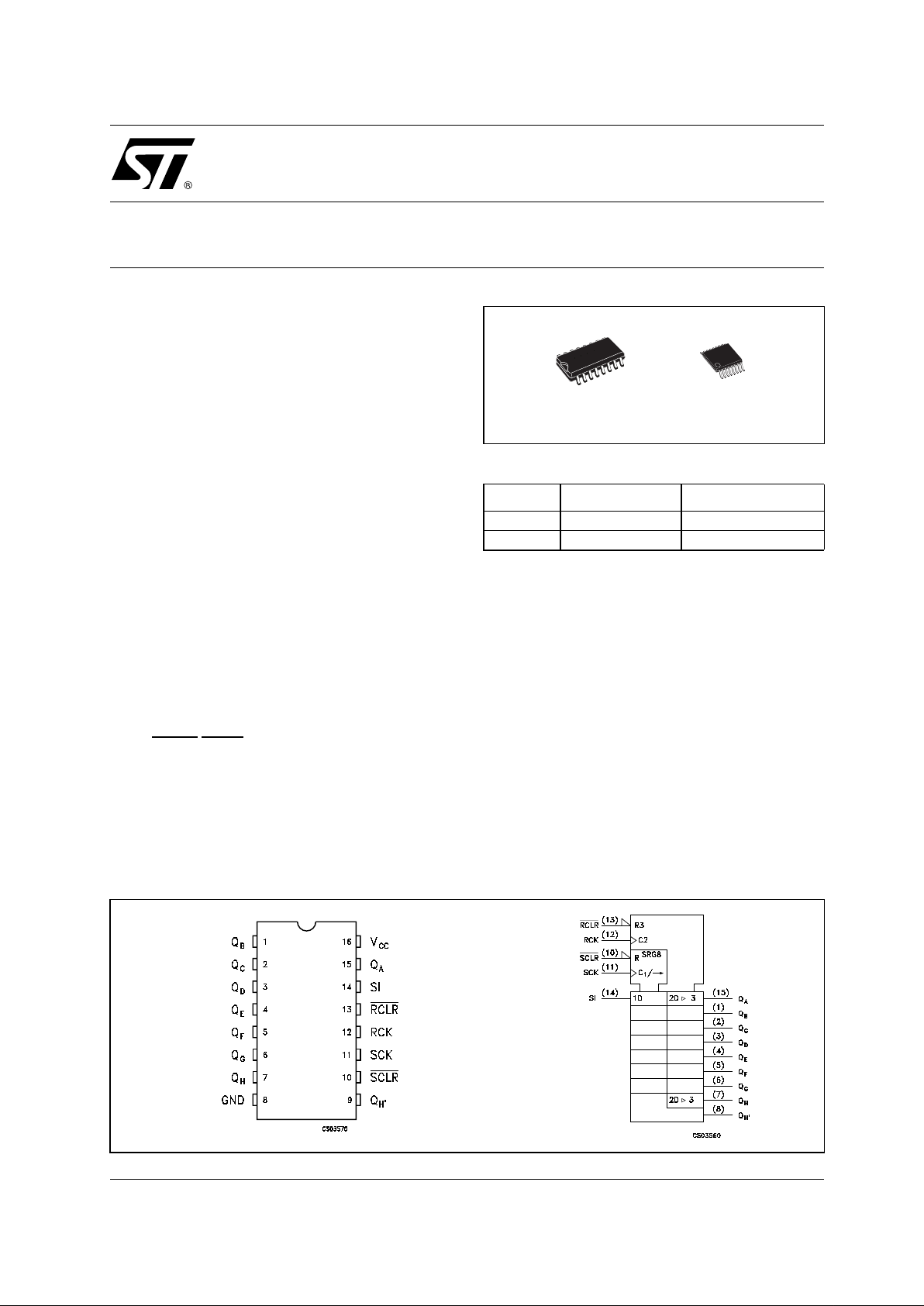

74VHC594

8 BIT SHIFT REGISTER

WITH OUTPUT REGISTER

PIN CO NNE CTION AND IEC LOGIC SYMB OLS

ORDER CODES

PACKAGE TUBE T & R

SOP M74VHC594M1R M74VHC594RM13TR

TSSOP M74VHC594TTR

TSSOPSOP

74VHC594

2/11

INPUT EQUIVALENT CIRCUIT PIN DESCRIPTION

TRUTH TABLE

X: Don’t Care

PIN No SYMBOL NAME AND FUNCTION

1, 2, 3, 4, 5,

6, 7, 15

QA to QH Data Outputs

9 QH’ Serial Data Output

10 SCLR

Shift Register Clear Input

11 SCK Shift Register Clock Input

13 RCLR

Storage Register Clear

Input

14 SI Serial Data Input

12 RCK Storage Register Clock

Input

8 GND Ground (0V)

16 V

CC

Positive Supply Voltage

INPUTS

OUTPUTS

SI SCK SCLR RCK RCLR

X X L X X SHIFT REGISTER IS CLEAR

LHXX

FIRST STAGE OF SHIFT REGISTER GOES LOW

OTHER STAGES STORE THE DATA OF PREVI-

OUS STAGE, RESPECTIVELY

HHXX

FIRST STAGE OF SHIFT REGISTER GOES HIGH

OTHER STAGES STORE THE DATA OF PREVI-

OUS STAGE, RESPECTIVELY

L H X X SHIFT REGISTER STATE IS NOT CHANGED

X X X X L STORAGE REGISTER IS CLEARED

XXX H

SHIFT REGISTER DATA IS STORED IN THE

STORAGE REGISTER

X X X H STORAGE REGISTER STATE IS NOT CHANGED

74VHC594

3/11

LOGIC DIAGRAM

This logic diagram has not be used to estimate propagation delays

74VHC594

4/11

TIMING CHART

ABSOLUTE MAXIMUM RATINGS

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is

not implied

Symbol Parameter Value Unit

V

CC

Supply Voltage

-0.5 to +7.0 V

V

I

DC Input Voltage

-0.5 to +7.0 V

V

O

DC Output Voltage -0.5 to VCC+ 0.5

V

I

IK

DC Input Diode Current

-20 mA

I

OK

DC Output Diode Current

± 20 mA

I

O

DC Output Current

± 25 mA

I

CC

or I

GND

DC VCCor Ground Current

± 50 mA

T

stg

Storage Temperature

-65 to +150 °C

T

L

Lead Temperature (10 sec)

300 °C