74VHC138

3 TO 8 LINE DECODER (INVERTING)

■ HIGH SPEED:t

■ LOW POWERDISSIPATION:

=4 µA(MAX.) at TA=25oC

I

CC

■ HIGHNOISEIMMUNITY:

V

NIH=VNIL

■ POWERDOWN PROTECTIONON INPUTS

■ SYMMETRICAL OUTPUTIMPEDANCE:

|=IOL=8 mA(MIN)

|I

OH

■ BALANCEDPROPAGATIONDELAYS:

t

≅ t

PLH

■ OPERATINGVOLTAGERANGE:

V

(OPR)= 2Vto 5.5V

CC

■ PINANDFUNCTION COMPATIBLEWITH

=28%VCC(MIN.)

PHL

=5.7ns (TYP.)at VCC=5V

PD

74SERIES138

■ IMPROVEDLATCH-UP IMMUNITY

DESCRIPTION

The 74VHC138 is an advanced high-speed

CMOS 3 TO 8 LINE DECODER (INVERTING)

fabricated with sub-micron silicon gate and

double-layermetal wiringC

2

MOS technology.

If the device is enabled, 3 binary select inputs (A,

B and C) determine which one of the outputs will

go low. If enable input G1 is held low or either

M1

(Micro Package)

(TSSOPPackage)

T

ORDERCODES :

74VHC138M 74VHC138T

G2A or G2B is held high, the decoding function is

inhibitedand all the 8 outputsgo to high.

Three enable inputs are provided to ease

cascade connection and application of address

decodersfor memory systems.

Power down protection is provided on all inputs

and 0 to 7V can be accepted on inputs with no

regard to the supply voltage. This device can be

used to interface5V to 3V.

All inputs and outputs are equipped with

protection circuits against static discharge, giving

them 2KV ESD immunity and transient excess

voltage.

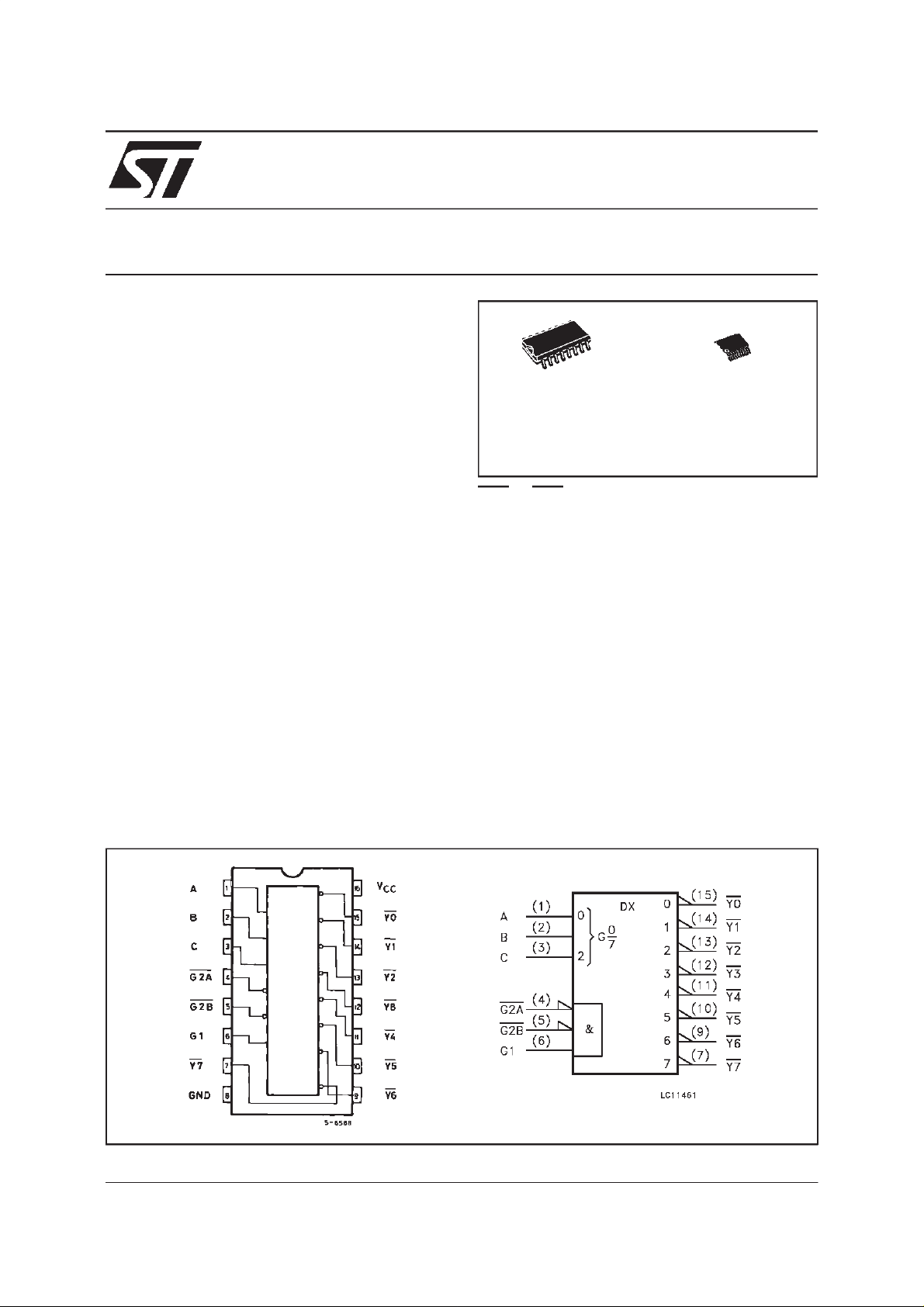

PIN CONNECTION AND IECLOGICSYMBOLS

June 1999

1/8

74VHC138

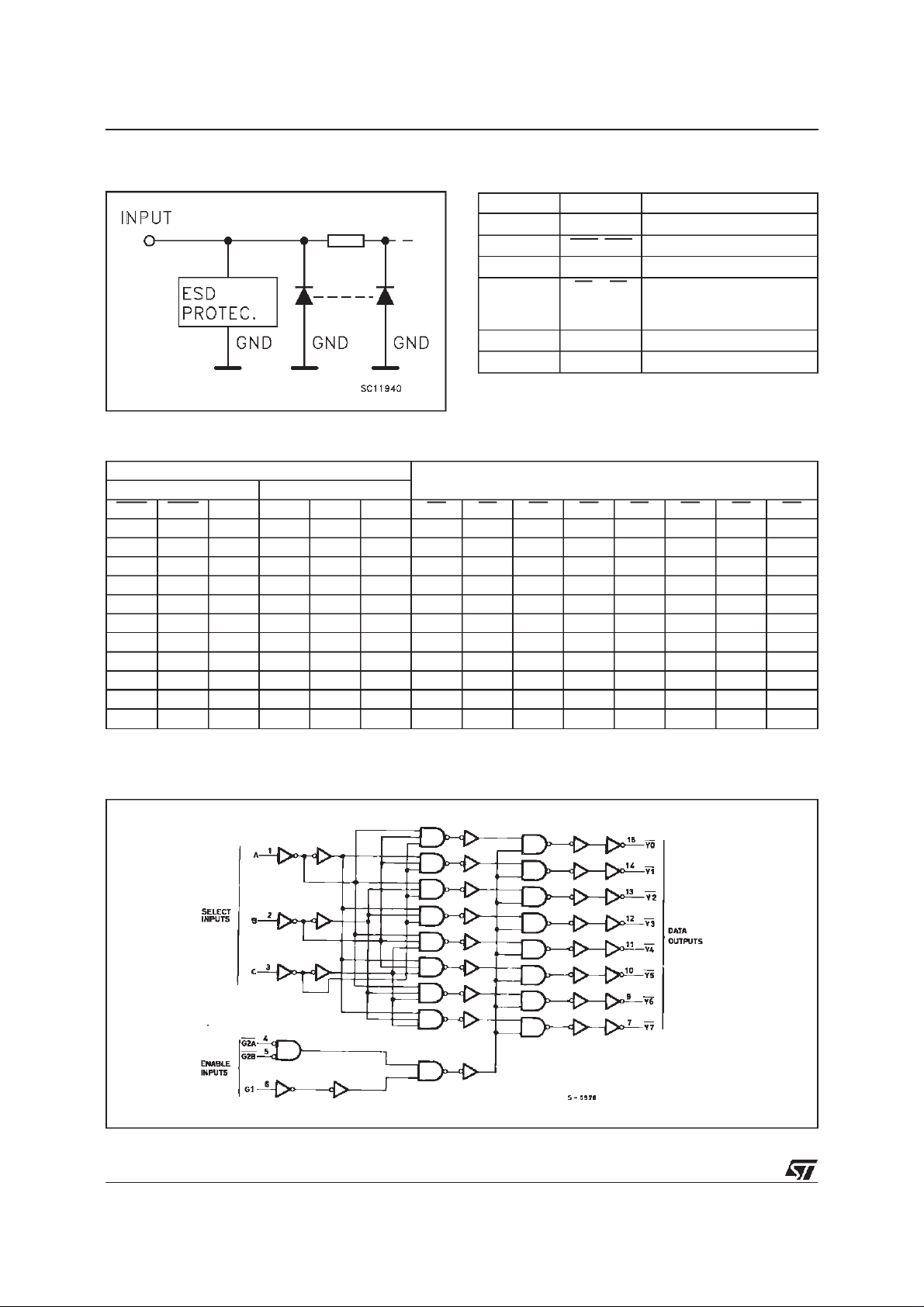

INPUT EQUIVALENTCIRCUIT

PIN DESCRIPTION

PI N No SYM BO L NAM E AND F U NCTI O N

1, 2, 3 A, B,C Address Inputs

4, 5 G2A, G2B Enable Inputs

6 G1 Enable Input

15, 14, 13,

12, 11, 10,

9, 7

8 GND Ground (0V)

16 V

Y0 to Y7 Outputs

CC

Positive Supply Voltage

TRUTH TABLE

INPUTS OUTPUTS

ENABLE SELECT

G2BG2AG1 C B A Y0Y1Y2Y3Y4Y5Y6Y7

XXLXXXHHHHHHHH

XHXXXXHHHHHHHH

HXXXXXHHHHHHHH

LLHLLLLHHHHHHH

LLHLLHHLHHHHHH

LLHLHLHHLHHHHH

LLHLHHHHHLHHHH

LLHHLLHHHHLHHH

LLHHLHHHHHHLHH

LLHHHLHHHHHHLH

LLHHHHHHHHHHHL

X:Don’tCare

LOGICDIAGRAM

Thislogicdiagram has notbe used toestimate propagation delays

2/8

74VHC138

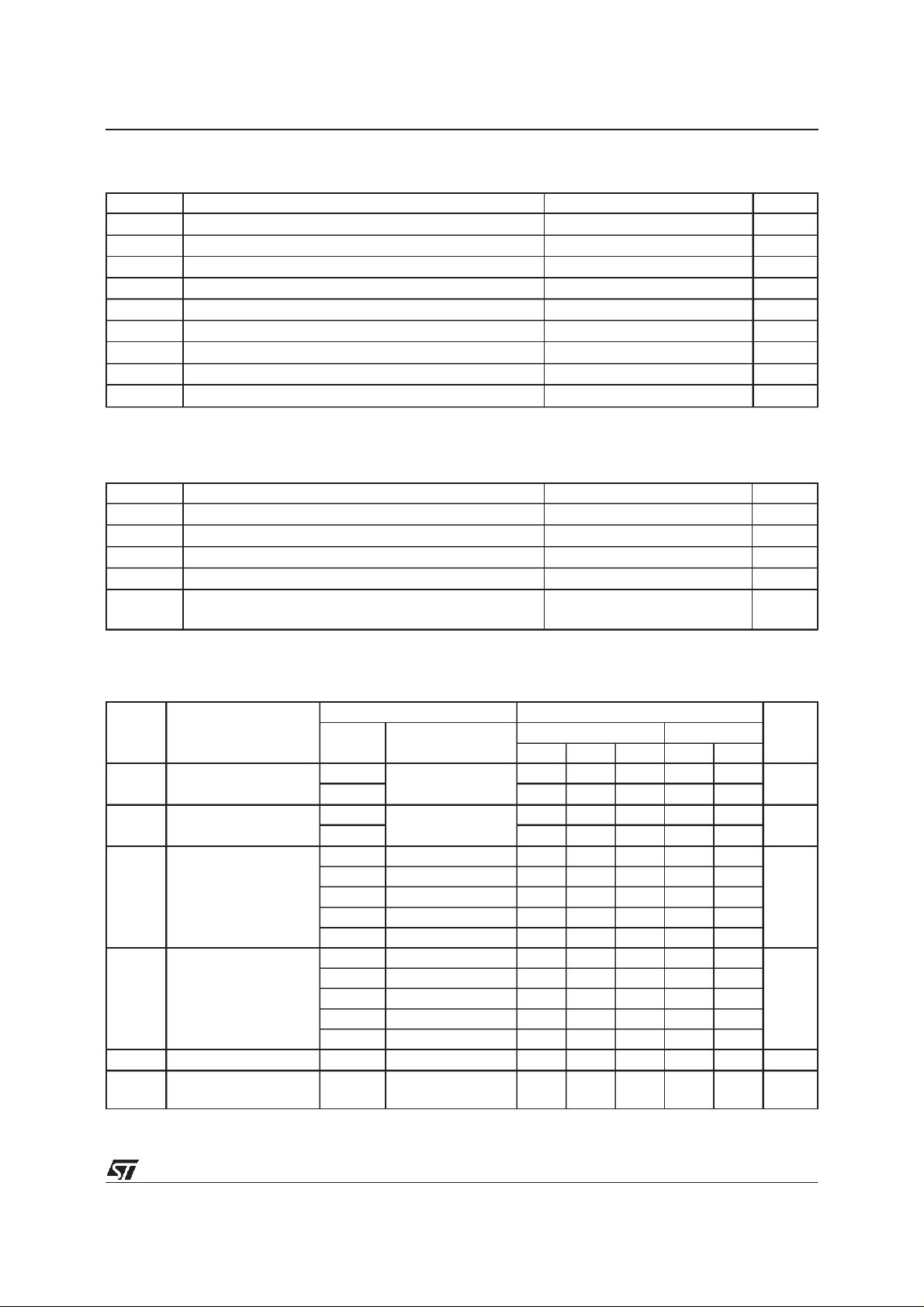

ABSOLUTE MAXIMUM RATINGS

Symb o l Para met er Val u e Uni t

V

V

V

I

I

OK

I

or I

I

CC

T

T

AbsoluteMaximumRatingsarethosevaluesbeyond whichdamagetothedevicemayoccur. Functional operation underthese condition isnotimplied.

RECOMMENDED OPERATING CONDITIONS

Symb o l Para met er Value Un it

V

V

V

T

dt/dv

1)VINfrom 30%to70%ofV

Supply Voltage -0.5 to +7.0 V

CC

DC Input Voltage -0.5 to +7.0 V

I

DC Output Voltage -0.5 to VCC+ 0.5 V

O

DC Input Diode Current - 20 mA

IK

DC Output Diode Current ± 20 mA

DC Output Current

O

DC VCCor Ground Current

GND

Storage Temperature -65 to +150

stg

Lead Temperature (10 sec) 300

L

Supply Voltage 2.0 to 5.5 V

CC

Input Voltage 0 to 5.5 V

I

Output Voltage 0 to V

O

Operating Temperature -40 to +85

op

(V

CC

CC

=3.3±0.3V)

=5.0±0.5V)

Input Rise and Fall Time (see note 1) (V

CC

25 mA

±

75 mA

±

CC

0 to 100

0to20

o

C

o

C

V

o

C

ns/V

ns/V

DC SPECIFICATIONS

Symb o l Para met er Test Con di ti o ns Val u e Uni t

=25oC -40 to 85oC

V

CC

(V)

High Level Input

V

IH

Voltage

V

Low Level Input

IL

Voltage

V

High Level Output

OH

Voltage

Low Level Output

V

OL

Voltage

Input Leakage Current 0 to 5.5 VI= 5.5V or GND ±0.1 ±1.0 µA

I

I

Quiescent Supply

I

CC

2.0 1.5 1.5

3.0 to 5.5 0.7V

2.0 0.5 0.5

3.0 to 5.5 0.3V

2.0 IO=-50 µA 1.9 2.0 1.9

3.0 I

4.5 I

3.0 I

4.5 I

=-50 µA 2.9 3.0 2.9

O

=-50µA 4.4 4.5 4.4

O

=-4 mA 2.58 2.48

O

=-8 mA 3.94 3.8

O

2.0 IO=50 µA 0.0 0.1 0.1

3.0 I

4.5 I

3.0 I

4.5 I

=50 µA 0.0 0.1 0.1

O

=50µA 0.0 0.1 0.1

O

=4 mA 0.36 0.44

O

=8 mA 0.36 0.44

O

5.5 VI=VCCorGND 4 40 µA

Current

T

A

Min. Typ. Max. Min. Max.

CC

0.7V

CC

0.3V

CC

CC

V

V

V

V

3/8

Loading...

Loading...