QUAD 2-INPUT OPEN DRAIN NAND GATE

■ HIGHSPEED:t

■ LOW POWER DISSIPATION:

=2 µA (MAX.)at TA=25oC

I

CC

■ HIGHNOISEIMMUNITY:

V

NIH=VNIL

■ POWERDOWNPROTECTIONON INPUTS

■ OPERATINGVOLTAGERANGE:

V

CC

■ PINANDFUNCTIONCOMPATIBLEWITH

=28%VCC(MIN.)

(OPR)= 2Vto5.5V

74SERIES03

■ IMPROVEDLATCH-UPIMMUNITY

■ LOWNOISE:V

DESCRIPTION

The 74VHC03 is an advanced high-speedCMOS

QUAD 2-INPUT OPEN DRAIN NAND GATE

fabricated with sub-micron silicon gate and

double-layermetal wiring C

The internal circuit is composed of 3 stages

including buffer output, which provides high noise

immunityand stableoutput.

This device can, with an external pull-up resistor,

=3.7ns(TYP.)atVCC=5V

PD

= 0.8V(Max.)

OLP

2

MOS technology.

74VHC03

PRELIMINARY DATA

M

(Micro Package)

(TSSOPPackage)

ORDERCODES :

74VHC03M 74VHC03T

be used in wired AND configuration. This device

can also be used as a led driver and in anyother

applicationrequiring a currentsink.

Power down protection is provided on all inputs

and 0 to 7V can be accepted on inputs with no

regard to the supply voltage. This device can be

used to interface 5V to 3V.

All inputs and outputs are equipped with

protection circuits against static discharge, giving

them 2kV ESD immunity and transient excess

voltage.

T

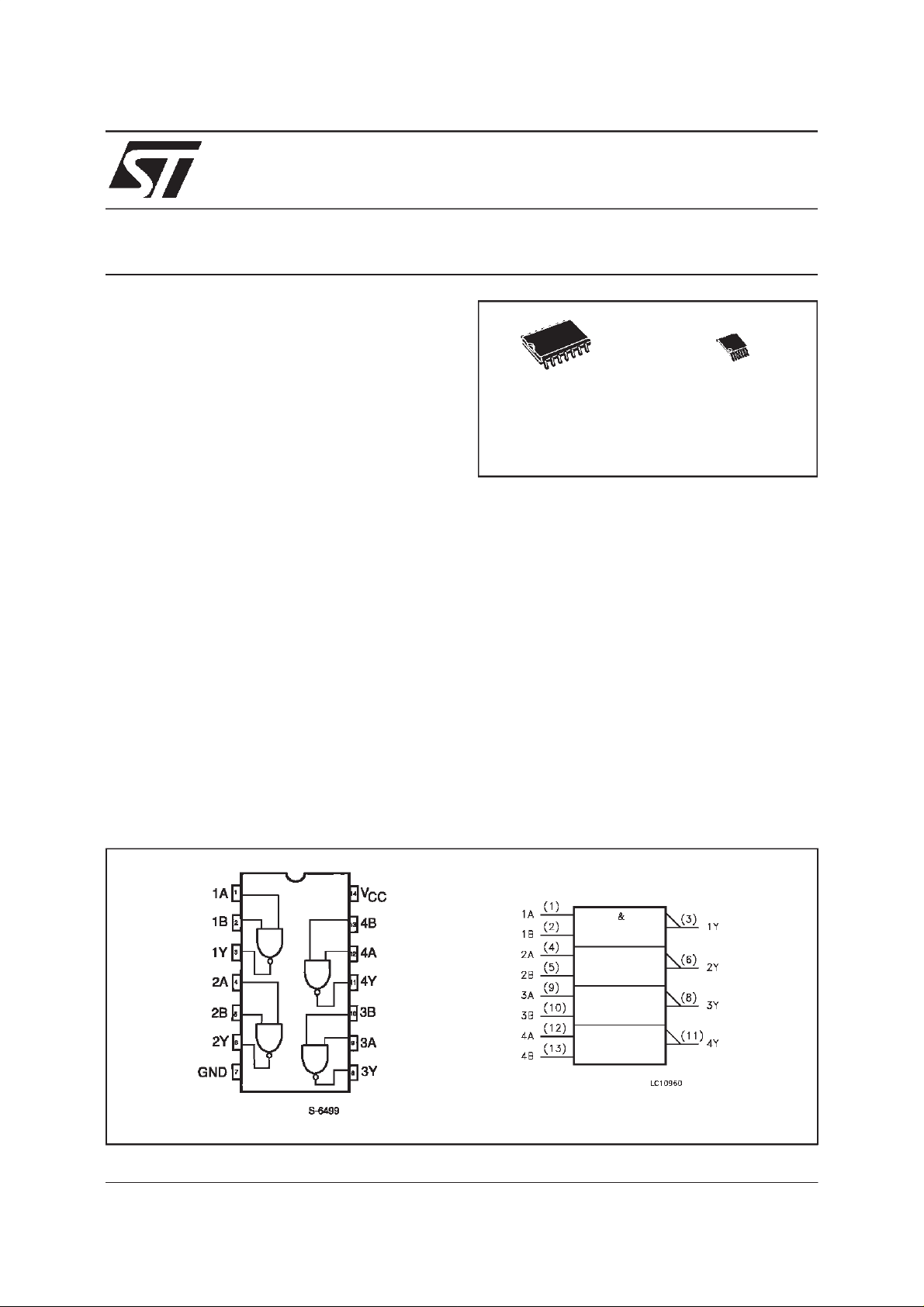

PIN CONNECTION AND IEC LOGICSYMBOLS

June 1999

1/7

74VHC03

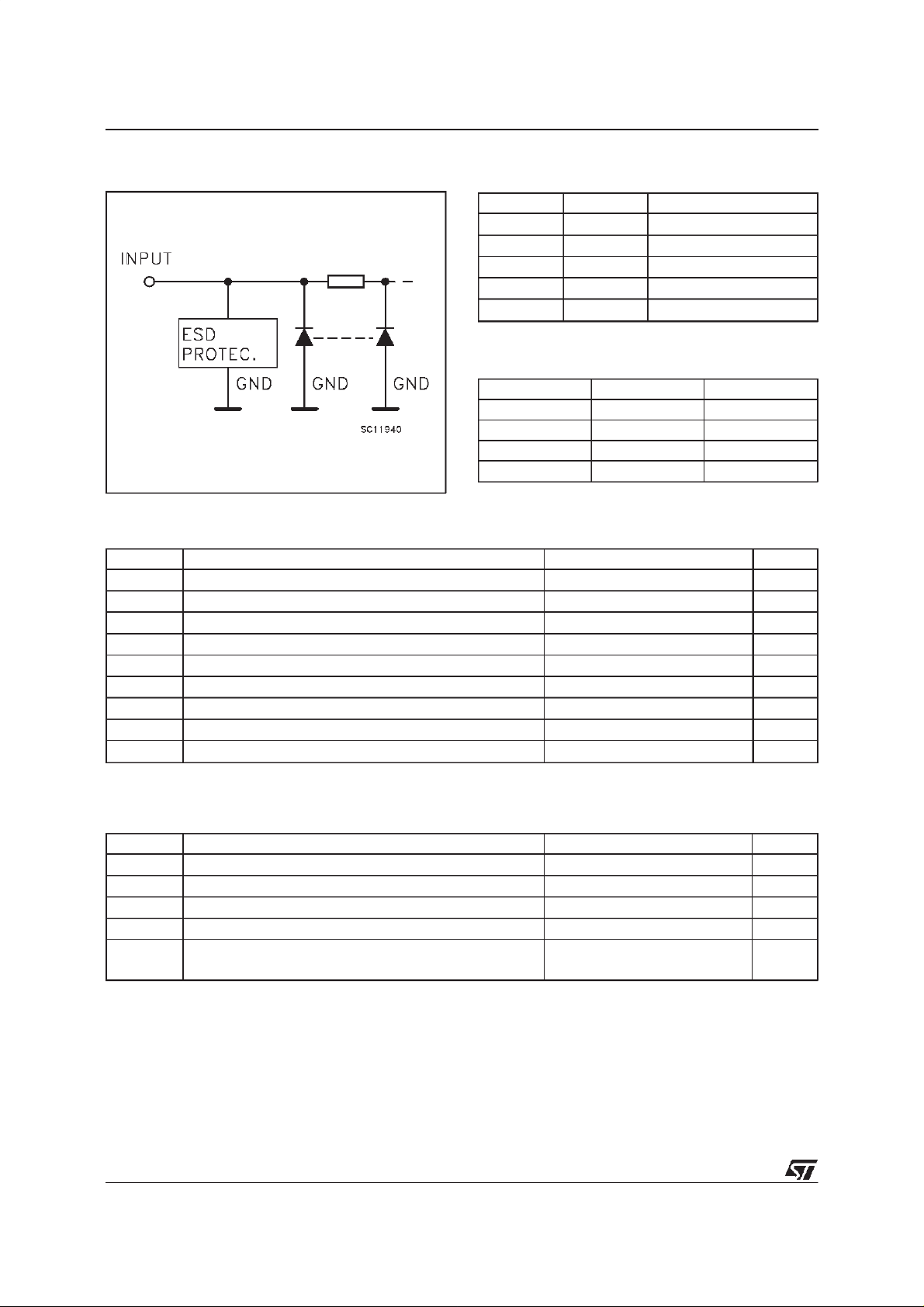

INPUT EQUIVALENTCIRCUIT

PIN DESCRIPTION

PI N No SYMB OL NAME AND FU NCTIO N

1, 4, 9, 12 1A to 4A Data Inputs

2, 5, 10,13 1B to 4B Data Inputs

3, 6, 8, 11 1Y to 4Y Data Outputs

7 GND Ground (0V)

14 V

CC

Positive Supply Voltage

TRUTH TABLE

ABY

LLZ

LHZ

HLZ

HHL

Z: High Impedance

ABSOLUTE MAXIMUM RATINGS

Symb o l Para met er Val u e Uni t

V

V

V

I

I

OK

I

or I

I

CC

T

T

AbsoluteMaximumRatingsarethosevaluesbeyondwhichdamageto thedevicemayoccur.Functionaloperation underthesecondition isnotimplied.

Supply Voltage -0.5 to +7.0 V

CC

DC Input Voltage -0.5 to +7.0 V

I

DC Output Voltage -0.5 to VCC+ 0.5 V

O

DC Input Diode Current - 20 mA

IK

DC Output Diode Current ± 20 mA

DC Output Current 25 mA

O

DC VCCor Ground Current ± 50 mA

GND

Storage Temperature -65 to +150

stg

Lead Temperature (10 sec) 300

L

o

C

o

C

RECOMMENDED OPERATINGCONDITIONS

Symb o l Para met er Value Un it

V

V

V

T

dt/dv

1)VINfrom30%to70%of V

2/7

Supply Voltage 2.0 to 5.5 V

CC

Input Voltage 0 to 5.5 V

I

Output Voltage 0 to V

O

Operating Temperature -40 to +85

op

(V

CC

CC

=3.3±0.3V)

=5.0±0.5V)

Input Rise and Fall Time (see note 1) (V

CC

CC

0 to 100

0to20

V

o

C

ns/V

ns/V

74VHC03

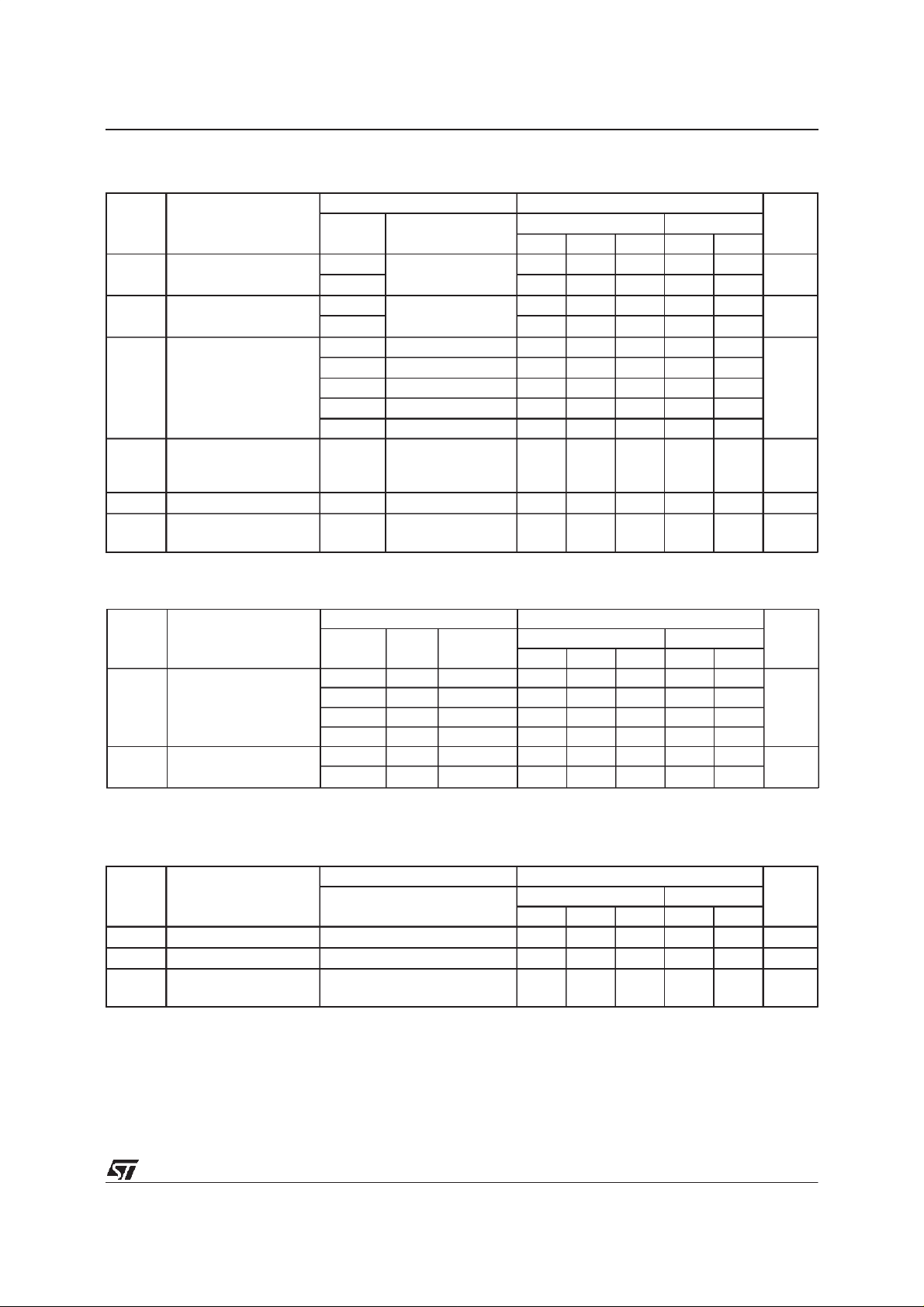

DC SPECIFICATIONS

Symb o l Para met er Test C o n diti o ns Val u e Uni t

T

V

CC

(V)

High Level Input

V

IH

Voltage

V

Low Level Input

IL

Voltage

V

Low Level Output

OL

Voltage

2.0 1.5 1.5

3.0 to 5.5 0.7V

2.0 0.5 0.5

3.0 to 5.5 0.3V

2.0 IO=50 µ A 0.0 0.1 0.1

3.0 I

4.5 I

3.0 I

4.5 I

High Impedance

I

OZ

Output Leakage

5.5

VO=VCCor GND

Current

Input Leakage Current 0 to 5.5 VI= 5.5V or GND

I

I

Quiescent Supply

I

CC

5.5 VI=VCCorGND 2 20

Current

Min. Typ. Max. Min. Max.

=50µA 0.0 0.1 0.1

O

=50µA 0.0 0.1 0.1

O

=4 mA 0.36 0.44

O

=8 mA 0.36 0.44

O

VI=VIHor V

IL

=25oC -40 to 85oC

A

CC

0.7V

CC

±0.25 ±2.5 µA

0.1

±

CC

0.3V

±

1.0

CC

µ

µ

V

V

V

A

A

AC ELECTRICAL CHARACTERISTICS (Inputtr=tf=3ns)

Symbol Parameter T est Condition Value Unit

t

Propagation Delay

PZL

Time

t

Propagation Delay

PLZ

Time

(*) Voltagerange is3.3V± 0.3V

(**) Voltagerangeis 5V± 0.5V

V

(V)

3.3

3.3

5.0

5.0

3.3

5.0

CC

(**)

(**)

(**)

C

L

(pF)

(*)

(*)

15 RL=1KΩ 5.5 7.9 1.0 9.5

50 RL=1KΩ 8.0 11.4 1.0 13.0

15 RL=1K

Ω

T

=25oC -40 to 85oC

A

Mi n . Typ. Max. Mi n . Max.

3.7 5.5 1.0 6.5

ns

50 RL=1KΩ 5.2 7.5 1.0 8.5

(*)

50 RL=1K

Ω

8.0 11.4 1.0 13.0

50 RL=1KΩ 5.2 7.5 1.0 8.5

ns

CAPACITIVE CHARACTERISTICS

Symb o l Para met er Test C o n diti o ns Val u e Uni t

=25oC -40 to 85oC

T

A

Min. Typ. Max. Min. Max.

Input Capacitance 4 10 10

C

IN

C

Output Capacitance 5

OUT

Power Dissipation

C

PD

6pF

Capacitance (note 1)

1)CPDisdefined asthevalue oftheIC’sinternal equivalentcapacitance whichis calculated fromtheoperatingcurrent consumptionwithout load.(Referto

TestCircuit).Average operatingcurrent canbeobtainedbythefollowingequation.I

(opr)= CPD• VCC• fIN+ICC/4(perGate)

CC

pF

pF

3/7

Loading...

Loading...