SGS Thomson Microelectronics 74VCXH16240TTR Datasheet

1/11February 2003

■ 3.6V TOLERANT INPUTS AND OUTPUTS

■ HIGH SPEED :

t

PD

= 2.5 ns (MAX.) at VCC=3.0to3.6V

t

PD

= 3.0 ns (MAX.) at VCC=2.3to2.7V

■ POWER DOWN PROTECTION ON INPUTS

AND OUTPUTS

■ SYMMETRICAL OUTPUT IMPEDANCE:

|I

OH

|=IOL= 24mA (MIN) at VCC=3.0V

|I

OH

|=IOL= 18mA (MIN) at VCC=2.3V

■ OPERATING VOLTAGE RANGE:

V

CC

(OPR) = 2.3V to 3.6V

■ PIN AND FUNCTION COMPATIBLE WITH

74 SERIES H16240

■ BUS HOLD PROVIDED ON DATA INPUTS

■ LATCH-UP P ERFO RMANCE EXCEEDS

300mA (JESD 17)

■ ESD PERFORMANCE:

HBM > 2000V (MIL STD 883 method 3015);

MM > 200V

DESCRIPTION

The 74VCXH16240 is a low voltage CMOS 16 BIT

BUS BUFFER (INVERTED) fabricated with

sub-micron silicon gate and five-layer metal wiring

C

2

MOS technology. It is ideal for low power and

very high s peed 2.3 to 3.6V applications; it can be

interfaced to 3.6V signal environment for both

inputs and outputs.

Any nG

output con trol governs four BUS

BUFFERS. Output Enable input (nG

) tied together

gives full 16-bit operation.

When nG

is LO W, the outputs are on. When nG is

HIGH, the output are in high impedance state.

This dev ice is designed to be us ed with 3 state

memory address drivers, etc. Bus hold on data

inputs is p ro vided in order to eli minate the need f or

external pull-up or pull-down resistor.

All inputs and outputs are equipped with

protection circuits against static discharge, giving

them 2KV ESD imm unity and transient excess

voltage.

74VCXH16240

LOW VOLTAGE CMOS 16-BIT BUS BUFFER (3-STATE INV.)

WITH 3.6V TOLERANT INPUTS AND OUTPUTS

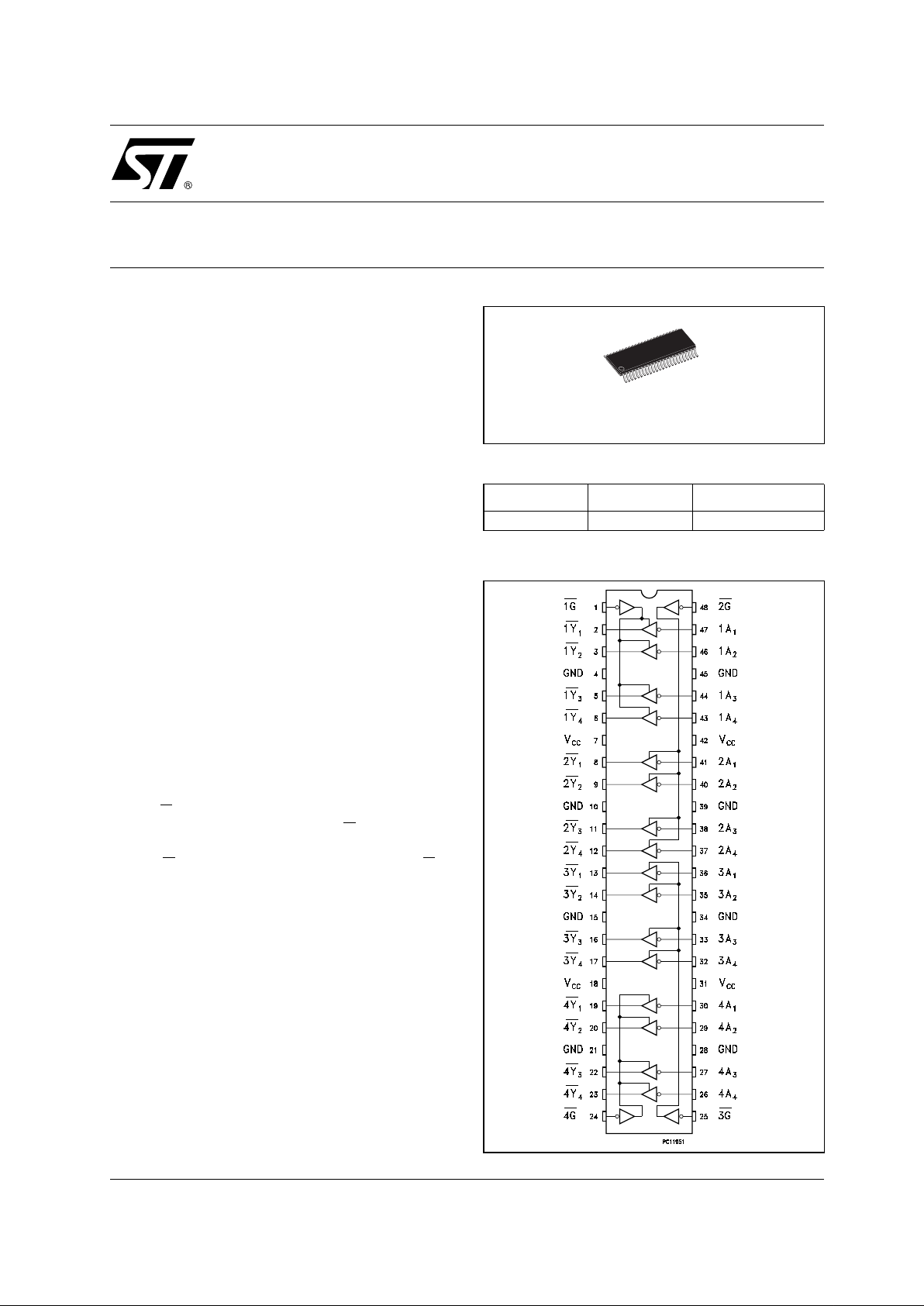

ORDER CODES

PACKAGE TUBE T & R

TSSOP 74VCXH16240TTR

TSSOP

PIN CO NNE CTION

74VCXH16240

2/11

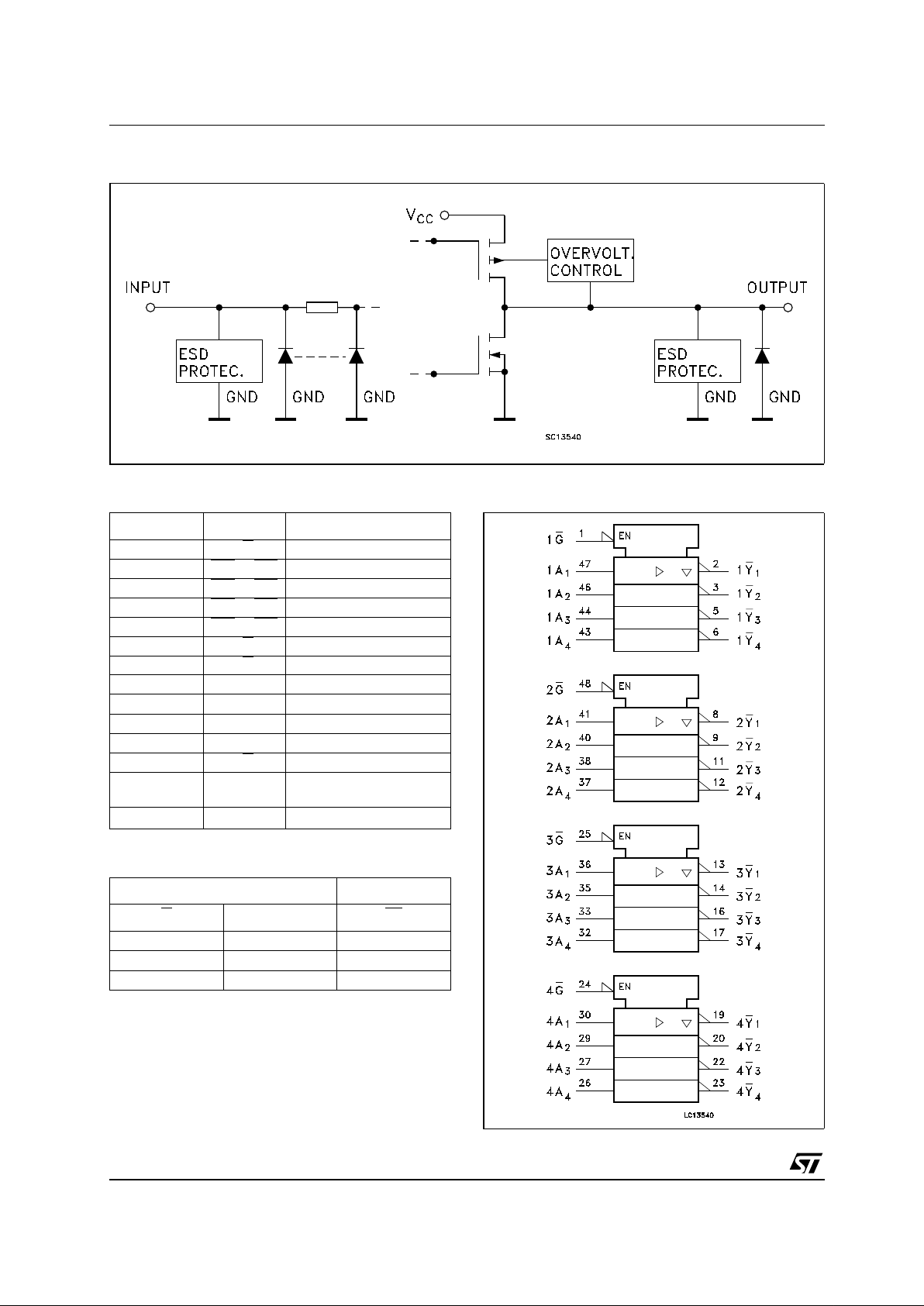

INPUT AND OUTPUT EQUIVALENT CIRCUIT

PIN DESCRIPTION

TRUTH TABLE

X : Don‘t Care

Z : High Impedance

IEC LOGIC SYMBOLS

PIN No SYMBOL NAME AND FUNCTION

11G

Output Enable Input

2, 3, 5, 6 1Y1

to 1Y4 Data Outputs

8, 9, 11, 12 2Y1

to 2Y4 Data Outputs

13, 14, 16, 17 3Y1

to 3Y4 Data Outputs

19, 20, 22, 23 4Y1

to 4Y4 Data Outputs

24 4G

Output Enable Input

25 3G

Output Enable Input

30, 29, 27, 26 4A1 to 4A4 Data Outputs

36, 35, 33, 32 3A1 to 3A4 Data Outputs

41, 40, 38, 37 2A1 to 2A4 Data Outputs

47, 46, 44, 43 1A1 to 1A4 Data Outputs

48 2G

Output Enable Input

4, 10, 15, 21,

28, 34, 39, 45

GND Ground (0V)

7, 18, 31, 42

V

CC

Positive Supply Voltage

INPUTS OUTPUT

G

An Yn

LLH

LHL

HXZ

74VCXH16240

3/11

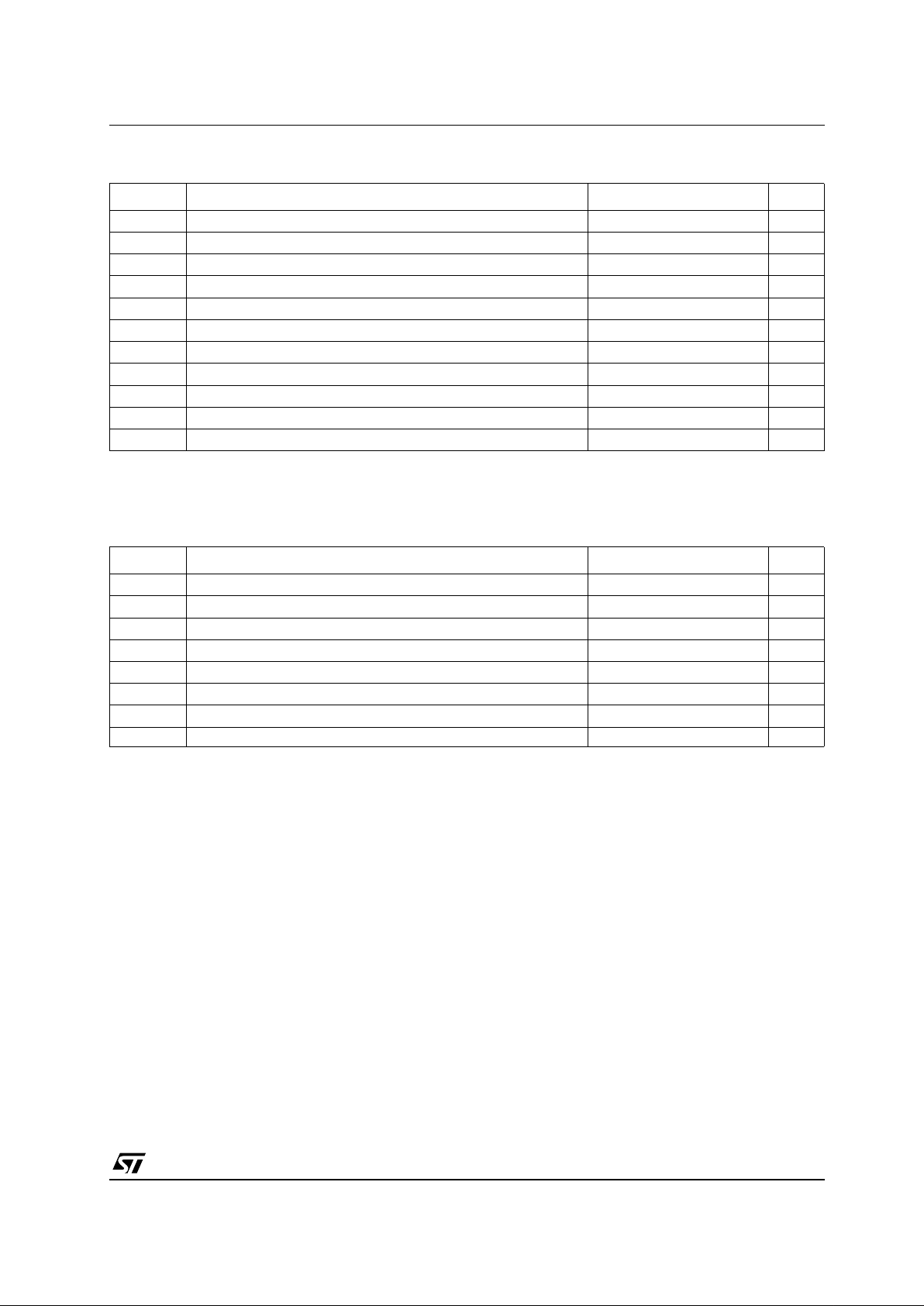

ABSOLUTE MAXIMUM RATINGS

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is

not implied

1) I

O

absolute maximum rating must be observed

2) V

O

<GND,VO>V

CC

RECOMMENDED OPERATING CONDITIONS

1) VINfrom0.8Vto 2V at VCC=3.0V

Symbol Parameter Value Unit

V

CC

Supply Voltage

-0.5 to +4.6 V

V

I

DC Input Voltage

-0.5 to +4.6 V

V

O

DC Output Voltage (OFF State)

-0.5 to +4.6 V

V

O

DC Output Voltage (High or Low State) (note 1) -0.5 to VCC+ 0.5

V

I

IK

DC Input Diode Current

-50 mA

I

OK

DC Output Diode Current (note 2)

-50 mA

I

O

DC Output Current

± 50 mA

I

CC

or I

GND

DC VCCor Ground Current per Supply Pin

± 100 mA

P

D

Power Dissipation

400 mW

T

stg

Storage Temperature

-65 to +150 °C

T

L

Lead Temperature (10 sec)

300 °C

Symbol Parameter Value Unit

V

CC

Supply Voltage

2.3 to 3.6 V

V

I

Input Voltage

-0.3 to 3.6 V

V

O

Output Voltage (OFF State)

0 to 3.6 V

V

O

Output Voltage (High or Low State) 0 to V

CC

V

I

OH,IOL

High or Low Level Output Current (VCC= 3.0 to 3.6V)

± 24 mA

I

OH,IOL

High or Low Level Output Current (VCC= 2.3 to 2.7V)

± 18 mA

T

op

Operating Temperature

-55 to 125 °C

dt/dv Input Rise and Fall Time (note 1) 0 to 10 ns/V

74VCXH16240

4/11

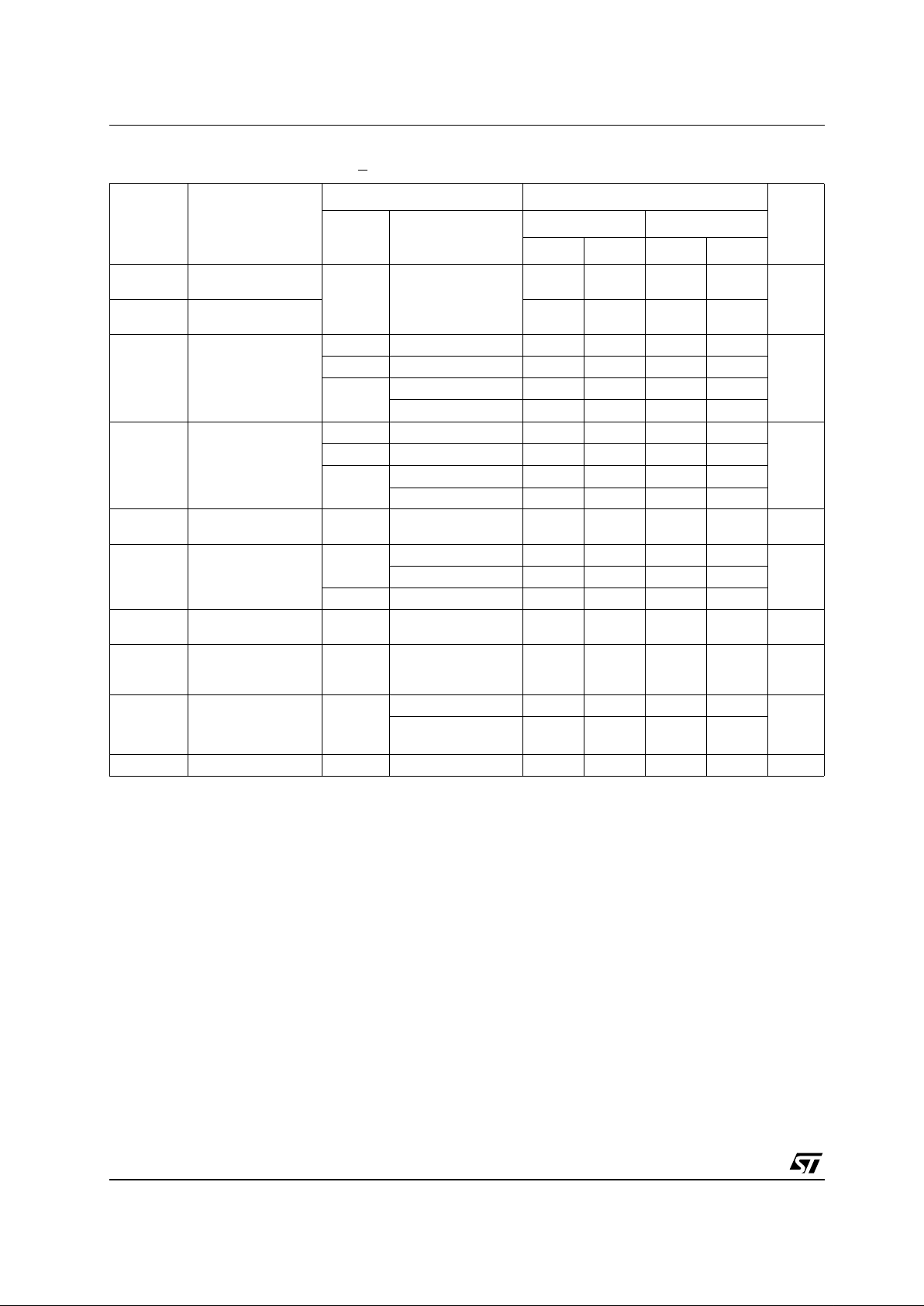

DC SPECIFICATIONS (2.7V < VCC< 3.6V unless otherwise specified)

Symbol Parameter

Test Condition Value

Unit

V

CC

(V)

-40to85°C -55to125°C

Min. Max. Min. Max.

V

IH

High Level Input

Voltage

2.7to3.6

2.0 2.0

V

V

IL

Low Level Input

Voltage

0.8 0.8

V

OH

High Level Output

Voltage

2.7to3.6

IO=-100 µAVCC-0.2 VCC-0.2

V

2.7

I

O

=-12 mA

2.2 2.2

3.0

I

O

=-18 mA

2.4 2.4

I

O

=-24 mA

2.2 2.2

V

OL

Low Level Output

Voltage

2.7to3.6

IO=100 µA

0.2 0.2

V

2.7

I

O

=12 mA

0.4 0.4

3.0

I

O

=18 mA

0.4 0.4

I

O

=24 mA

0.55 0.55

I

I

Input Leakage

Current

2.7to3.6

V

I=VCC

or GND

± 5 ± 5 µA

I

I(HOLD)

Input Hold Current

3.0

VI= 0.8V

75 75

µA

V

I

=2V

-75 -75

3.6

V

I

= 0 to 3.6V

± 500 ± 500

I

off

Power Off Leakage

Current

0

V

I

or VO= 0 to 3.6V

10 10 µA

I

OZ

High Impedance

Output Leakage

Current

2.7to3.6

V

I=VIH

or V

IL

VO= 0 to 3.6V

± 10 ± 10 µA

I

CC

Quiescent Supply

Current

2.7to3.6

V

I=VCC

or GND

20 20

µA

V

I

or VO=VCCto

3.6V

± 20 ± 20

∆I

CC

ICCincr. per Input

2.7to3.6

VIH=VCC-0.6V

750 750 µA

Loading...

Loading...