SGS Thomson Microelectronics 74VCX163245TTR, 74VCX163245TBR, 74VCX163245TB, 74VCX163245LBR, 74VCX163245LB Datasheet

1/15June 2003

■ HIGH SPEED:t

PD

= 4.4ns (MAX.) at TA=85°C

V

CCA

=3.0VV

CCB

=2.3V

■ LOW POWER DISSIPATION:

I

CCA=ICCB

=20µA(MAX.) at TA=85°C

■ SYMMETRICAL OUTPUT IMPEDANCE:

|I

OHA

|=I

OLA

= 12mA MIN at

V

CCA

=3.0VV

CCB

= 1.65V or 2.3V

|I

OHA

|=I

OLA

= 8mA MIN at

V

CCA

=2.3VV

CCB

= 1.65V)

■ BALANCED PROPAGATION DELAYS:

t

PLH

≅ t

PHL

■ POWER DOWN PROTECTION ON INPUTS

AND OUTPUTS

■ OPERATING VOLTAGE RANGE:

V

CCA

(OPR)=2.3Vto3.6V(1.2VDataRetention)

V

CCB

(OPR)=1.65Vto2.7V(1.2VDataRetention)

■ PIN AND FUNCTION COMPATIBLE WITH

74 SERIES 16245

■ LATCH-UP P ERFO RMANCE EXCEEDS

500mA (JESD 17)

■ ESD PERFORMANCE:

HBM > 2 000V (MIL STD 883 method 3015);

MM > 200V

DESCRIPTION

The 74VCX163245 is a dual s upply low voltage

CMOS 16-BIT BUS TRANSCEIVER fabricated

with sub-micron silicon gate and five-layer metal

wiring C

2

MOS technology. Designed for use as an

interface between a 3.3V bus and a 2.5V or 1.8V

bus in a mixed 3.3V/1.8V,3.3V/2.5V and 2.5V/

1.8V supply syste ms, it achieves high speed

operation while maintaining the CMOS low power

dissipation.

This IC is intended f or two-way asynchronous

communication between data buses and the

direction of data transmission is determined by

nDIR inputs. The enable inputs nOE

canbeused

to disable the device so that the buses are

effectively isolated. The A-port interfaces with the

3V bus, the B-port with the 2.5 V and 1.8V bu s.

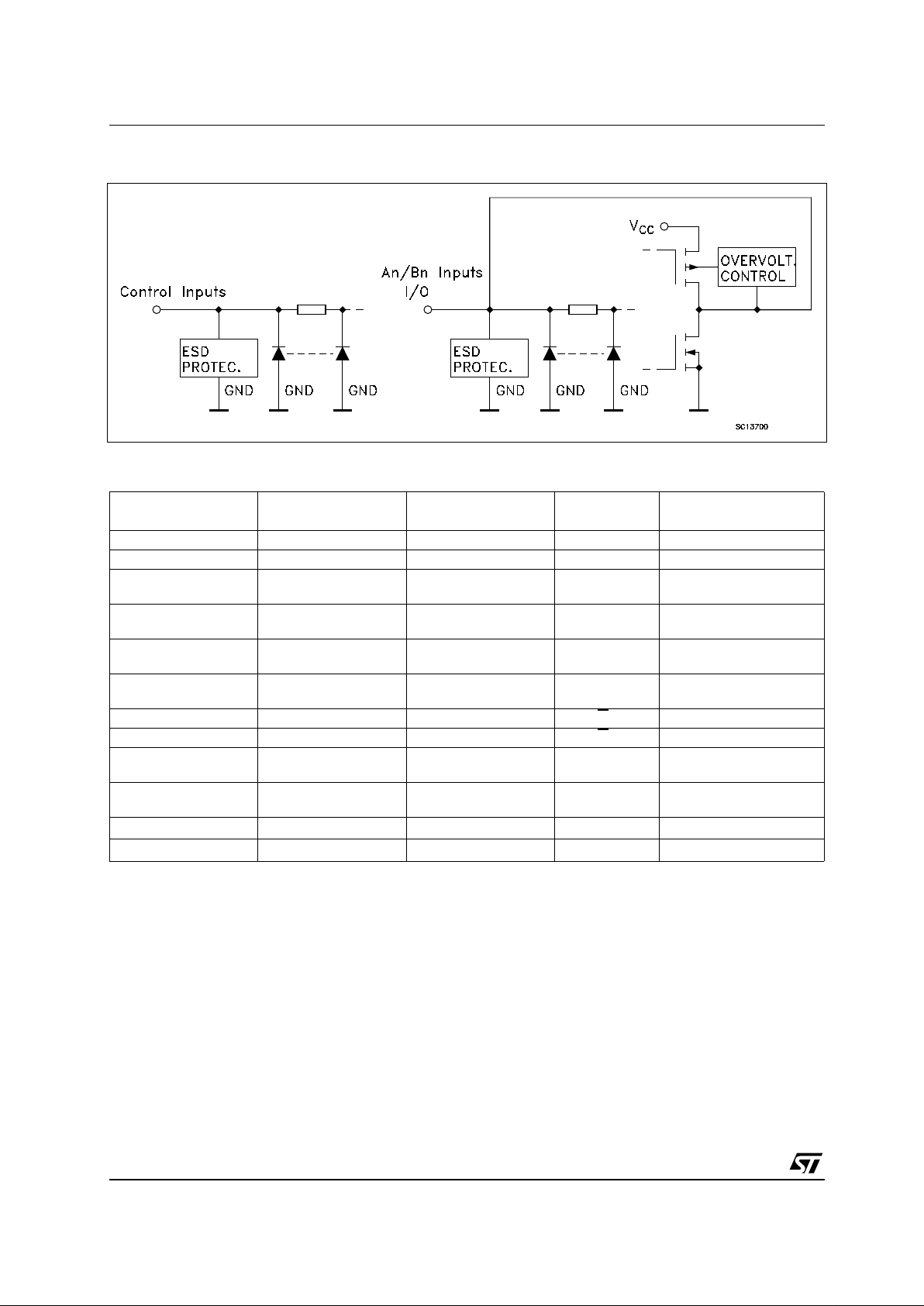

All inputs are equipped with protection circuits

against static discharge, giving them 2KV ESD immunity and transient excess voltage. All floating

bus terminals during High Z State must be held

HIGH or LOW.

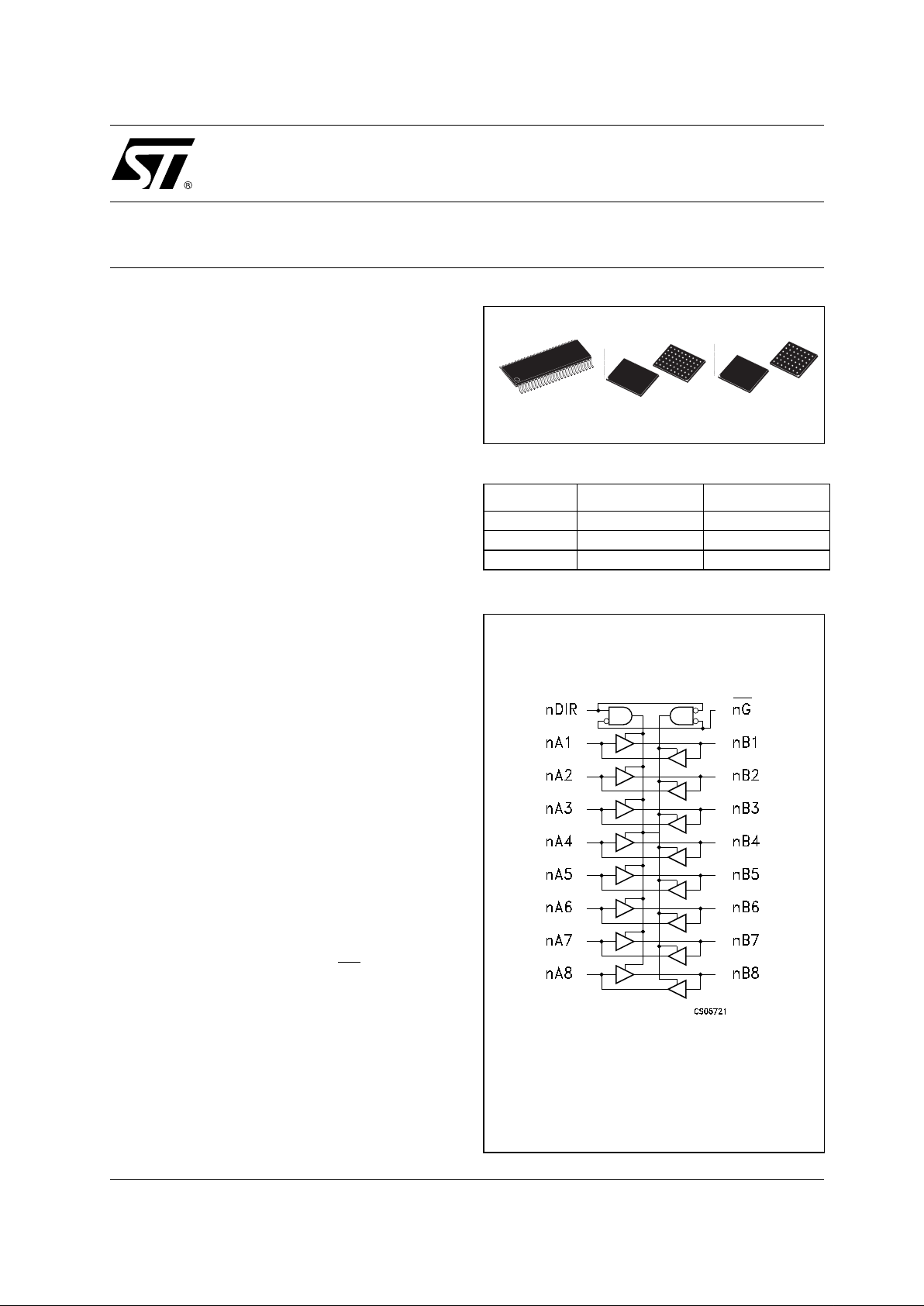

74VCX163245

16-BIT DUAL SUPPLY BUS TRANSCEIVER

LEVEL TRANSLATOR

This is preliminary information on a new product foreseen to be developed. Details are subject to change without notice.

ORDER CODES

PACKAGE TRAY T & R

TSSOP48 74VCX163245TTR

TFBGA54 74VCX163245LB 74VCX163245LBR

µTFBGA42 74VCX163245TB 74VCX163245TBR

TSSOP µTFBGATFBGA

TARGET DATA

LOGIC DIAGRAM

74VCX163245

2/15

INPUT AND OUTPUT EQUIVALENT CIRCUIT

PIN DESCRIPTION

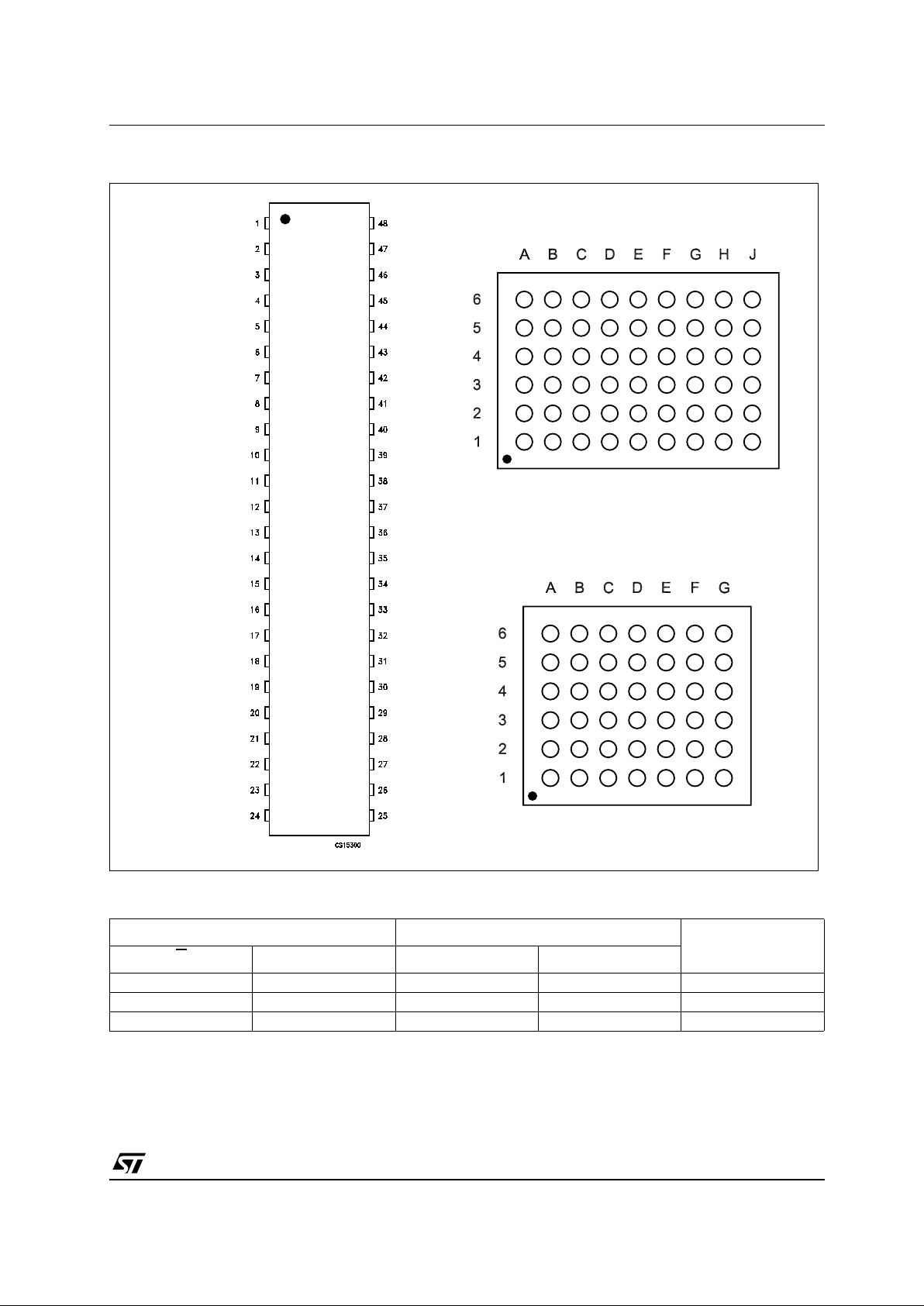

TFBGA54 PIN N

o

µTFBGA42 PIN N

o

TSSOP PIN N

o

SYMBOL NAME AND FUNCTION

A3 B3 1 1DIR Directional Controls

J3 F3 24 2DIR Directional Controls

A6, B5, B6, C5,

C6, D5, D6, E5

A4, A5, A6, B5,

B6, C5, C6, D5

47, 46, 44, 43,

41, 40, 38, 37

1A1 to 1A8 Data Inputs/Outputs

E6, F5, F6, G5,

G6, H5, H6, J6

D6, E5, E6, F5,

F6,G4, G5, G6

36, 35, 33, 32,

30, 29, 27, 26

2A1 to 2A8 Data Inputs/Outputs

A1, B2, B1, C2,

C1, D2, D1, E2

A3, A2, A1, B2,

B1, C2, C1, D2

2, 3, 5, 6,

8, 9, 11, 12

1B1 to 1B8 Data Inputs/Outputs

E1, F2, F1, G2,

G1, H2, H1, J1

D1, E2, E1, F2,

F1,G3, G2, G1

13, 14, 16, 17,

19, 20, 22, 23

2B1 to 2B8 Data Inputs/Outputs

J4 F4 25 G

2 Output Enable Inputs

A4 B4 48 G

1 Output Enable Inputs

D3, D4, E3, E4,

F3, F4

C3, C4, E3, E4 4,10,15, 21,

28, 34, 39, 45

GND Ground (0V)

A2, A5, B3, B4,

H3, H4, J2, J5

- - NC No Connected

C4, G4 D4 42, 31 V

CCA

Positive Supply Voltage

C3,G3 D3 7,18 V

CCB

Positive Supply Voltage

74VCX163245

3/15

PIN CONNECTION (top view for TSSOP, bottom view f or BGA)

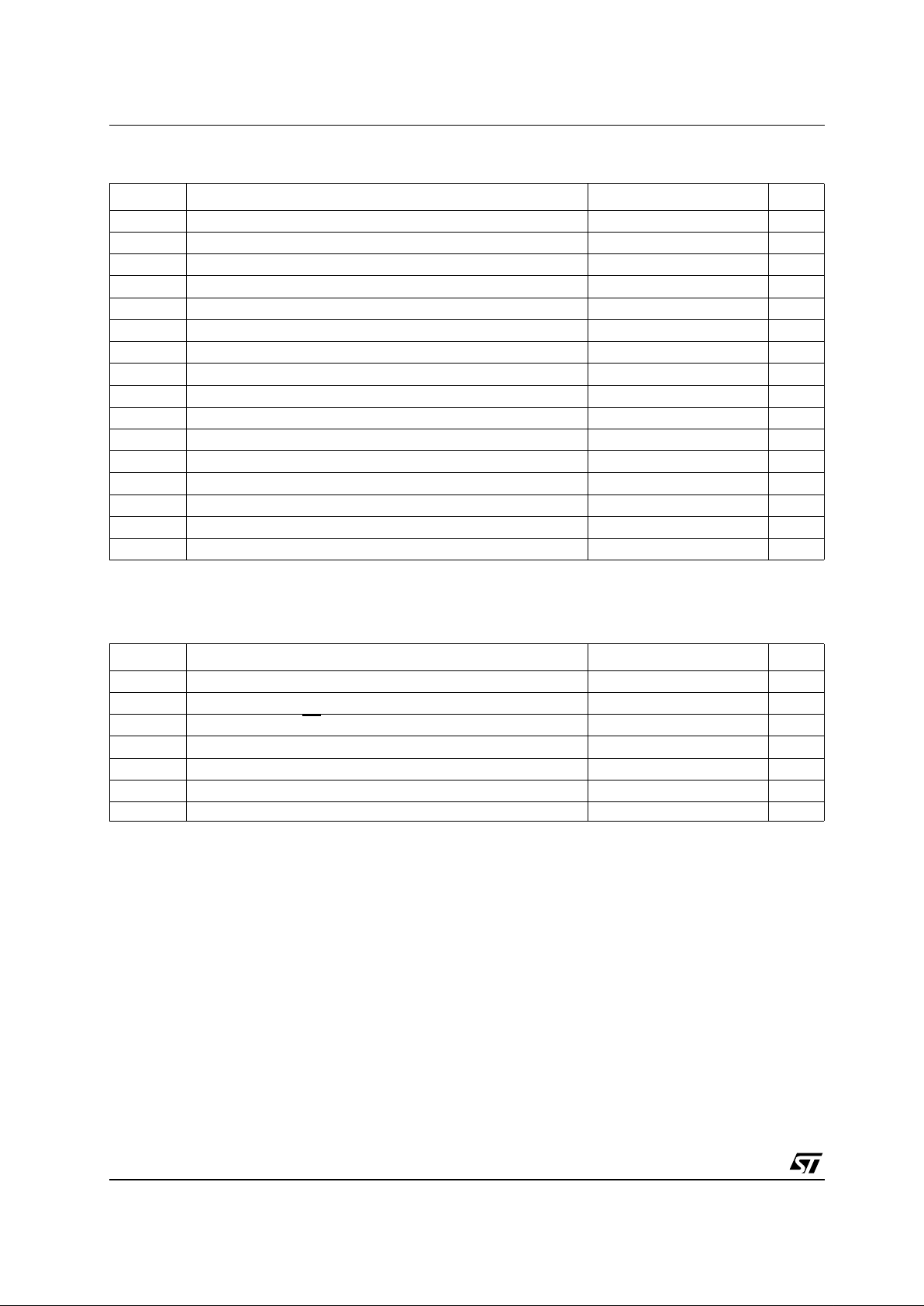

TRUTH TABLE

X=Don’t care; Z=High Impedance

INPUTS FUNCTION

OUTPUT

G

DIR A BUS B BUS

L L OUTPUT INPUT A = B

L H INPUT OUTPUT B = A

HXZZZ

TSSOP TFBGA

µTFBGA

74VCX163245

4/15

ABSOLUTE MAXIMUM RATINGS

Absolute Maximum Rating are those value beyond which damage to the device may occur. Functional operation under these condition is not

implied

(*) 500mW:≅ 65°C derated to 300mW by 10mW/°C: 65°C to 85°C

RECOMMENDED OPERATING CONDITIONS

1) VINfrom0.8Vto 2.0Vat VCC=3.0V

Symbol Parameter Value Unit

V

CCA

Supply Voltage

-0.5 to +4.6 V

V

CCB

Supply Voltage

-0.5 to +4.6 V

V

I

DC Input Volta ge

-0.5 to +4.6 V

V

I/OA

DC I/O Voltag e (Output disabled)

-0.5 to +4.6 V

V

I/OB

DC I/O Voltag e (Output disabled)

-0.5 to +4.6 V

V

I/OA

DC I/O Voltag e -0.5 to V

CCA

+ 0.5

V

V

I/OB

DC I/O Voltag e -0.5 to V

CCB

+ 0.5

V

I

IK

DC Input Diode Current

− 20 mA

I

OK

DC Output Diode Current

− 50 mA

I

OA

DC Output Current

± 50 mA

I

OB

DC Output Current

± 50 mA

I

CCA

DC VCCor Ground Current

± 100 mA

I

CCB

DC VCCor Ground Current

± 100 mA

P

d

Power Dissipation

400 mW

T

stg

Storage Temperature

-65 to +150 °C

T

L

Lead Temperatu re (10 sec)

300 °C

Symbol Parameter Value Unit

V

CCA

Supply Voltage

2.3 to 3.6 V

V

CCB

Supply Voltage

1.65 to 2.7 V

V

I

Input Voltage (Dir, OE) 0 to V

CCB

V

V

I/OA

I/O Vo ltage 0 to V

CCA

V

V

I/OB

I/O Vo ltage 0 to V

CCB

V

T

op

Operating Tempe rature

-40 to 85 °C

dt/dv Input Rise and Fall Time (note 1) 0 to 10 ns/V

74VCX163245

5/15

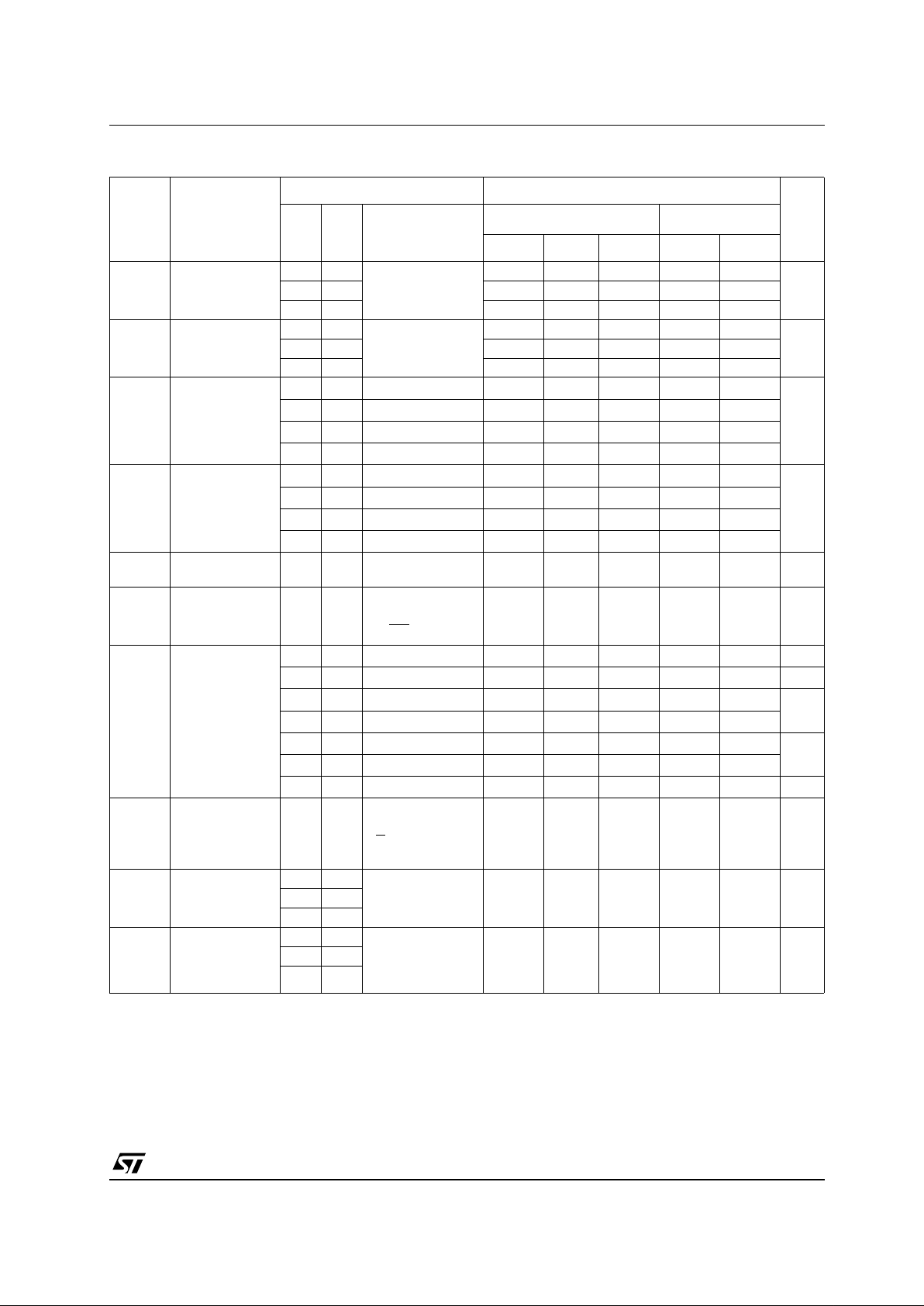

DC SPECIFICATION FOR V

CCA

Symbol Parameter

Test Condition Value

Unit

V

CCB

(*)

(V)

V

CCA

(*)

(V)

T

A

=25°C

-40 to 85 °C

Min. Typ. Max. Min. Max.

V

IHA

High Level Input

Voltage(An)

1.8 2.5 1.6 1.6

V1.8 3.3 2.0 2.0

2.5 3.3 2.0 2.0

V

ILA

Low Level Input

Voltage(An)

1.8 2.5 0.7 0.7

V1.8 3.3 0.8 0.8

2.5 3.3 0.8 0.8

V

OHA

High Level

Output Voltage

2.3 3.0

IO=-100 µA

2.8 2.8

V

2.3 3.0

I

O

=-24 mA

2.2 2.2

1.65 3.0

I

O

=-24 mA

2.2 2.2

1.65 2.3

I

O

=-18 mA

1.7 1.7

V

OLA

Low Level

Output Voltage

2.3 3.0

IO=100 µA

0.2 0.2

V

2.3 3.0

I

O

=24 mA

0.55 0.55

1.65 3.0

I

O

=24 mA

0.55 0.55

1.65 2.3

I

O

=18 mA

0.60 0.60

I

IA

Input Leakage

Current

2.7 3.6

V

I=VCC

or GND

± 0.5 ± 5 µA

I

OZA

High Impedance

Output Leakage

Current

2.7 3.6 V

IA

= Gnd or 3.6V

V

IB=VIHB

or V

ILB

OE =V

CCB

± 1.0 ± 10 µA

I

IA(HOLD)

Input Hold

Current

1.65 2.3

V

I

= 0.57V

25 25

µA

1.65 2.3

V

I

= 1.07V

-25 -25

1.65 3.0

V

I

= 0.57V

25 25

µA

1.65 3.0

V

I

= 1.07V

-25 -25

2.3 3.0

V

I

= 0.7V

45 45

µA

2.3 3.0

V

I

= 1.6V

-45 -45

2.7 3.6

V

IB

= 0 to 2.7V ± 300

I

OFF

Power Off

Leakage Current

00VIA= Gnd to 3.6V

V

IB

= Gnd to 3.6V

G

, Dir = GND to

3.6V

± 1.0 ± 10 µA

I

CCtA

Quiescent

Supply Current

1.95 3.6

V

IA=VCCA

or GND

V

IB=VCCB

or GND

220µA

1.95 2.7

2.7 3.6

∆I

CCtA

Maximum

Quiescent

Supply Current /

Input (An)

2.7 3.6

V

IA=VCCA

-0.6V

V

IB=VCCB

or GND

0.75 mA

1.95 3.6

1.95 2.7

Loading...

Loading...