1/9July 2001

■ HIGH SPEED:

t

PD

=5.8 ns (TYP.) at VCC = 3.3 V

■ COMPA TIBLE WITH TTL OU TPUTS

■ LOW POWER DISSIPATION:

I

CC

= 4 µA (MAX.) at TA=25°C

■ LOW NOISE:

V

OLP

= 0.4V (TYP.) at VCC = 3.3V

■ 75Ω TRANSMISSION LINE DRIVING

CAPABILITY

■ SYMMETRICAL OUTPUT IMPED ANCE:

|I

OH

| = IOL = 12mA (MIN) at VCC = 3.0 V

■ PCI BUS LEVELS GUARANTEED AT 24 mA

■ BALANCED PROPAGATION DELAYS:

t

PLH

≅ t

PHL

■ OPERATING VOLTAGE RANGE:

V

CC

(OPR) = 2V to 3.6V (1.2V Data Retention)

■ PIN AND FUNCTION COMPATIBLE WITH

74 SERIES 541

■ IMPROVED LATCH-UP IMMUNITY

DESCRIPTION

The 74LVQ541 is a low voltage CMOS OCTAL

BUS BUFFER with 3 STATE OUTPUTS NON

INVERTED fabricated with sub-micron silicon

gate and double-layer metal wiring C

2

MOS

technology. It is ideal for low power and low noise

3.3V applications.

The 3-STATE control gate operates as two input

and such that if either G1

and G2 are high, all

eight outputs are in the high impedance s tate. In

order to enhance PC boa rd layout, the 74AC541

offers a pinout having inputs and outputs on

opposite side of the package.

All inputs and outputs are equipped with

protection circuits against stat ic discharge, giving

them 2KV ESD immunity and transient excess

voltage.

74LVQ541

OCTAL BUS BUFFER

WITH 3 STATE OUTPUTS (NON INVERTED)

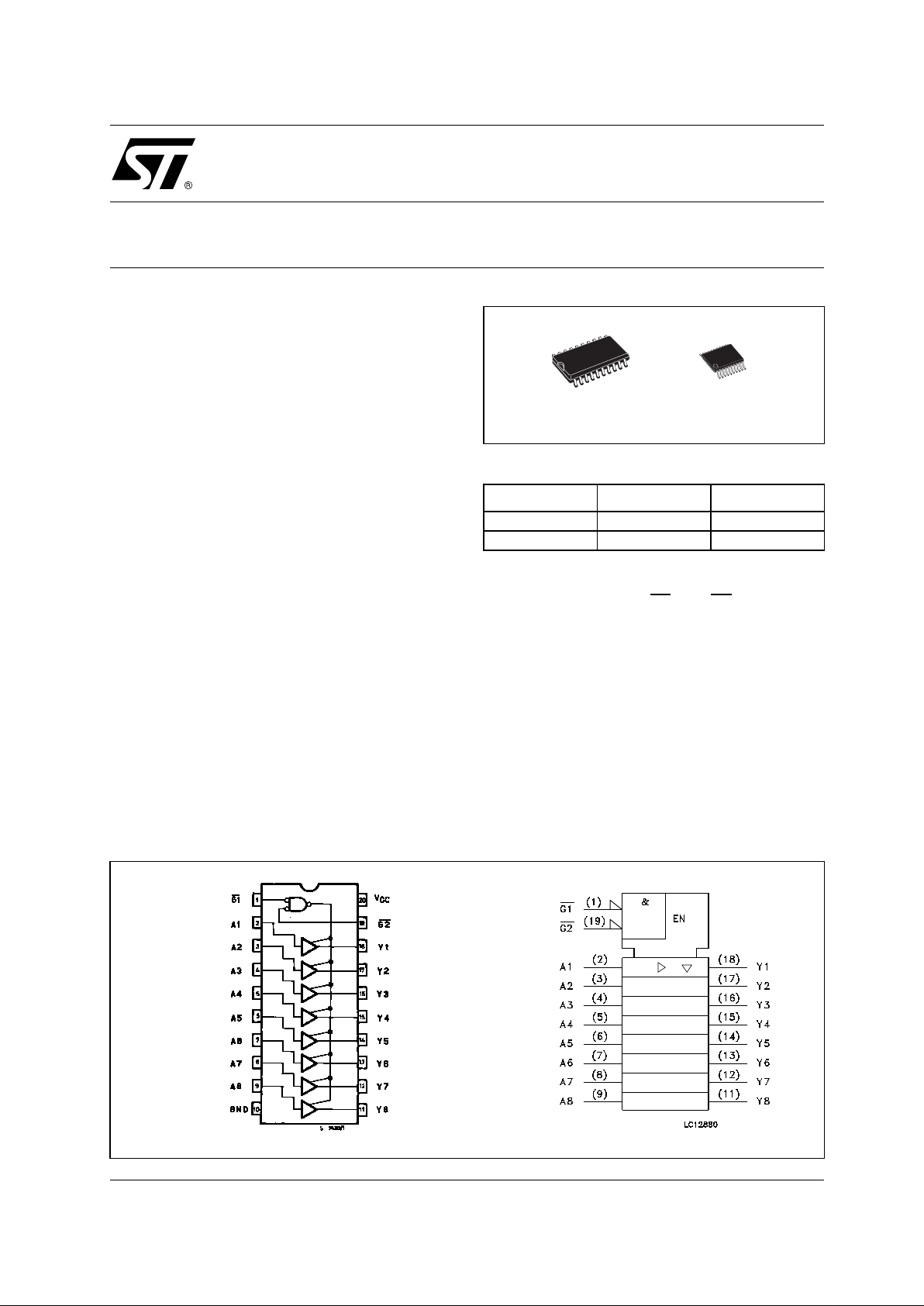

PIN CONNECTION AND IEC LOGIC SYMBOLS

ORDER CODES

PACKAGE TUBE T & R

SOP 74LVQ541M 74LVQ541MTR

TSSOP 74LVQ541TTR

TSSOPSOP

74LVQ541

2/9

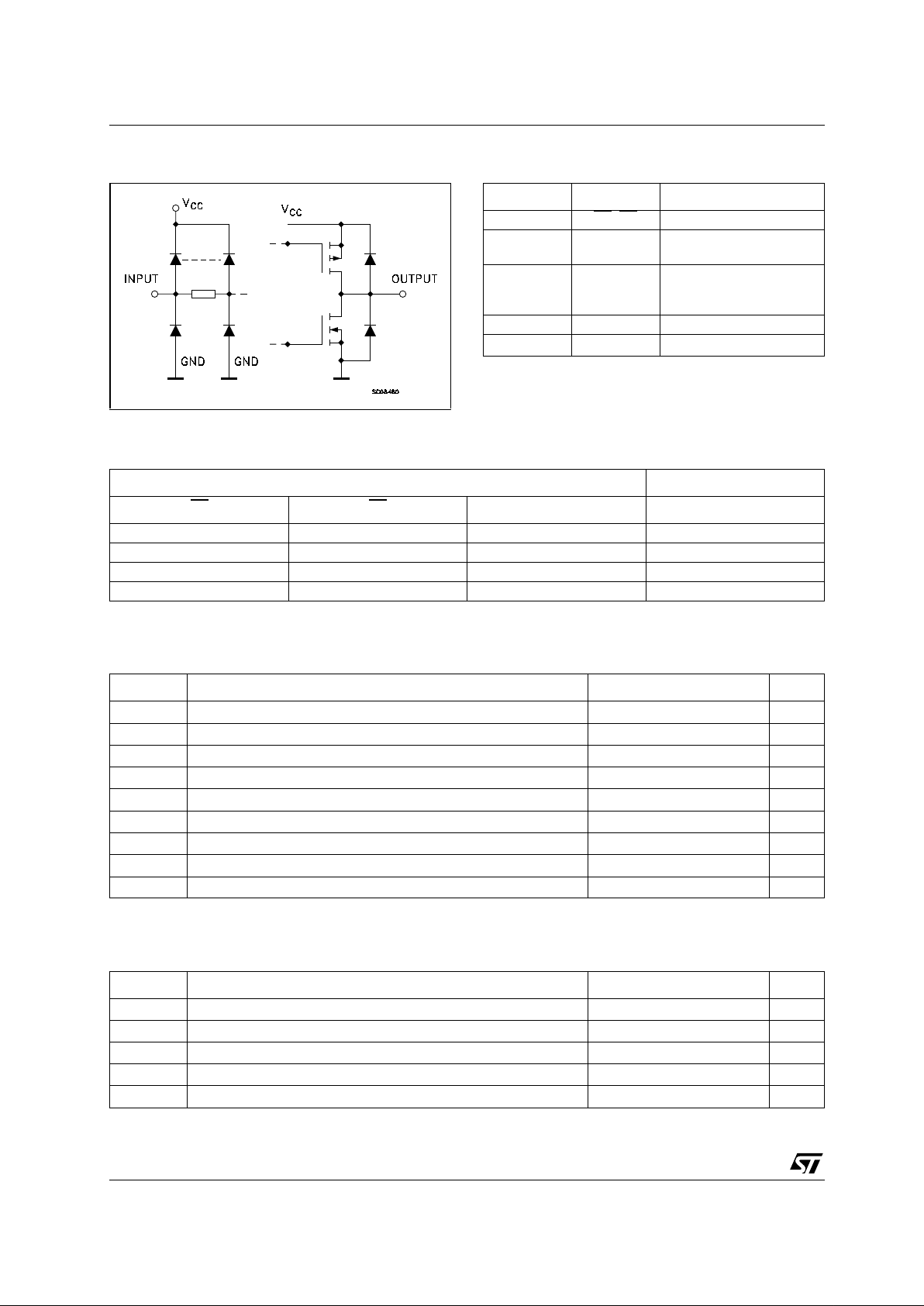

INPUT AND OUTPUT EQUIVALENT CIRCUIT PIN DESCRIPTION

TRUTH TABLE

X : Don’t Care

Z : High Impedance

ABSOLUTE MAXIMUM RATINGS

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is

not implied

RECOMMENDED OPERATING CONDITIONS

1) Truth T abl e guarante ed: 1.2V to 3.6 V

2) V

IN

from 0.8V to 2V

PIN No SYMBOL NAME AND FUNCTION

1, 19 G1

, G2 Output Enable Inputs

2, 3, 4, 5, 6,

7, 8, 9

A1 to A8 Data Inputs

18, 17, 16,

15, 14, 13,

12, 11

Y1 to Y8 Data Outputs

10 GND Ground (0V)

20 V

CC

Positive Supply Voltage

INPUTS OUTPUT

G1

G2 An Yn

HXXZ

XHXZ

LLLL

LLHH

Symbol Parameter Value Unit

V

CC

Supply Voltage

-0.5 to +7 V

V

I

DC Input Voltage -0.5 to VCC + 0.5

V

V

O

DC Output Voltage -0.5 to VCC + 0.5

V

I

IK

DC Input Diode Current

± 20 mA

I

OK

DC Output Diode Current

± 20 mA

I

O

DC Output Current

± 50 mA

I

CC

or I

GND

DC VCC or Ground Current

± 400 mA

T

stg

Storage Temperature

-65 to +150 °C

T

L

Lead Temperature (10 sec)

300 °C

Symbol Parameter Value Unit

V

CC

Supply Voltage (note 1)

2 to 3.6 V

V

I

Input Voltage 0 to V

CC

V

V

O

Output Voltage 0 to V

CC

V

T

op

Operating Temperature

-55 to 125 °C

dt/dv

Input Rise and Fall Time V

CC

= 3.0V (note 2)

0 to 10 ns/V

74LVQ541

3/9

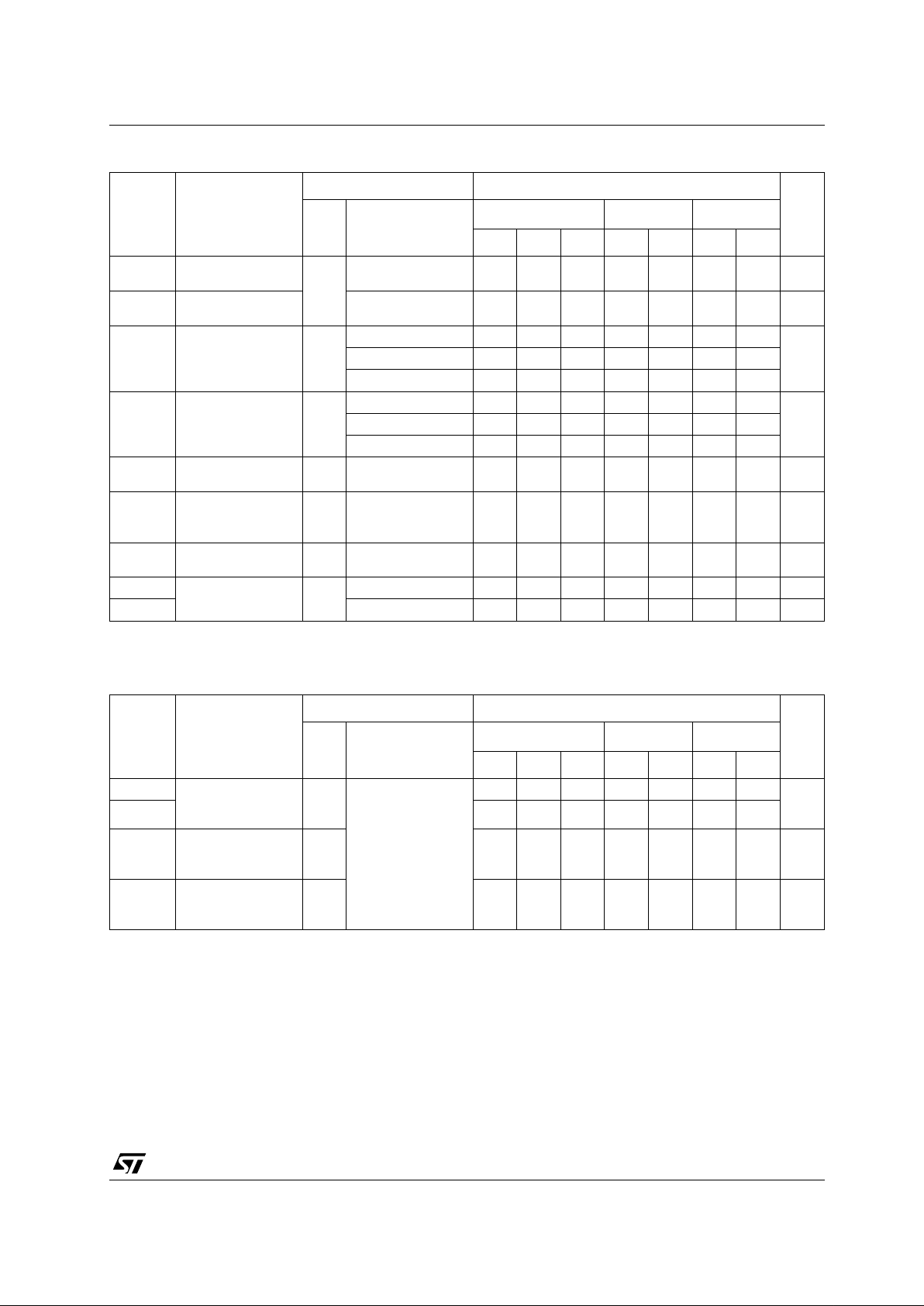

DC SPECIFICATIONS

1) Maxim um test duration 2ms, one out put loaded at time

2) Incid ent wave sw i tc hi ng is guara nt eed on transmi ssion lines with impedances a s low as 75Ω

DYNAMIC SWITCHING CHARACTERISTICS

1) Worst c ase package .

2) Max number of outp ut s defined as (n). Data inputs are driven 0V to 3.3V, (n-1) outputs switching and one output at GND.

3) Max number of data inputs (n) switching. (n-1) switching 0V to 3.3V. Inputs under test switching: 3.3V to threshold (V

ILD

), 0V to threshold

(V

IHD

), f=1MHz.

Symbol Parameter

Test Condition Value

Unit

V

CC

(V)

T

A

= 25°C

-40 to 85°C -55 to 125°C

Min. Typ. Max. Min. Max. Min. Max.

V

IH

High Level Input

Voltage

3.0 to

3.6

2.0 2.0 2.0 V

V

IL

Low Level Input

Voltage

0.8 0.8 0.8 V

V

OH

High Level Output

Voltage

3.0

I

O

=-50 µA

2.9 2.99 2.9 2.9

V

I

O

=-12 mA

2.58 2.48 2.48

I

O

=-24 mA

2.2 2.2

V

OL

Low Level Output

Voltage

3.0

IO=50 µA

0.002 0.1 0.1 0.1

V

I

O

=12 mA

0 0.36 0.44 0.44

I

O

=24 mA

0.55 0.55

I

I

Input Leakage

Current

3.6

V

I

= VCC or GND

± 0.1 ± 1 ± 1 µA

I

OZ

High Impedance

Output Leakage

Current

3.6

V

I

= VIH or V

IL

VO = VCC or GND

±0.25 ± 2.5 ± 5.0 µA

I

CC

Quiescent Supply

Current

3.6

V

I

= VCC or GND

44040µA

I

OLD

Dynamic Output

Current (note 1, 2)

3.6

V

OLD

= 0.8 V max

36 25 mA

I

OHD

V

OHD

= 2 V min

-25 -25 mA

Symbol Parameter

Test Condition Value

Unit

V

CC

(V)

T

A

= 25°C

-40 to 85°C -55 to 125°C

Min. Typ. Max. Min. Max. Min. Max.

V

OLP

Dynamic Low

Voltage Quiet

Output (note 1, 2)

3.3

C

L

= 50 pF

0.5 0.8

V

V

OLV

-0.8 -0.6

V

IHD

Dynamic High

Voltage Input

(note 1, 3)

3.3 2 V

V

ILD

Dynamic Low

Voltage Input

(note 1, 3)

3.3 0.8 V

Loading...

Loading...