SGS Thomson Microelectronics 74LVQ174 Datasheet

HEX D-TYPE FLIP FLOP WITH CLEAR

■ HIGHSPEED:

=150MHz(TYP.)atVCC=3.3V

f

MAX

■ COMPATIBLEWITHTTLOUTPUTS

■

LOW POWERDISSIPATION:

I

=4 µA (MAX.) atTA=25oC

CC

■ LOWNOISE:

=0.3V (TYP.)atVCC=3.3V

V

OLP

■ 75ΩTRANSMISSIONLINEDRIVING

CAPABILITY

■ SYMMETRICALOUTPUTIMPEDANCE:

|I

|=IOL=12 mA (MIN)

OH

■

PCIBUSLEVELSGUARANTEEDAT24mA

■ BALANCEDPROPAGATIONDELAYS:

t

≅ t

PLH

PHL

■ OPERATINGVOLTAGERANGE:

V

(OPR)= 2V to3.6V(1.2VDataRetention)

CC

■

PINANDFUNCTION COMPATIBLEWITH

74SERIES174

■ IMPROVEDLATCH-UPIMMUNITY

DESCRIPTION

The LVQ174 is a low voltage CMOS HEX

D-TYPE FLIP FLOP WITH CLEAR NON

INVERTING fabricated with sub-micron silicon

gate and double-layer metal wiring C

technology.It is idealfor low power and low noise

2

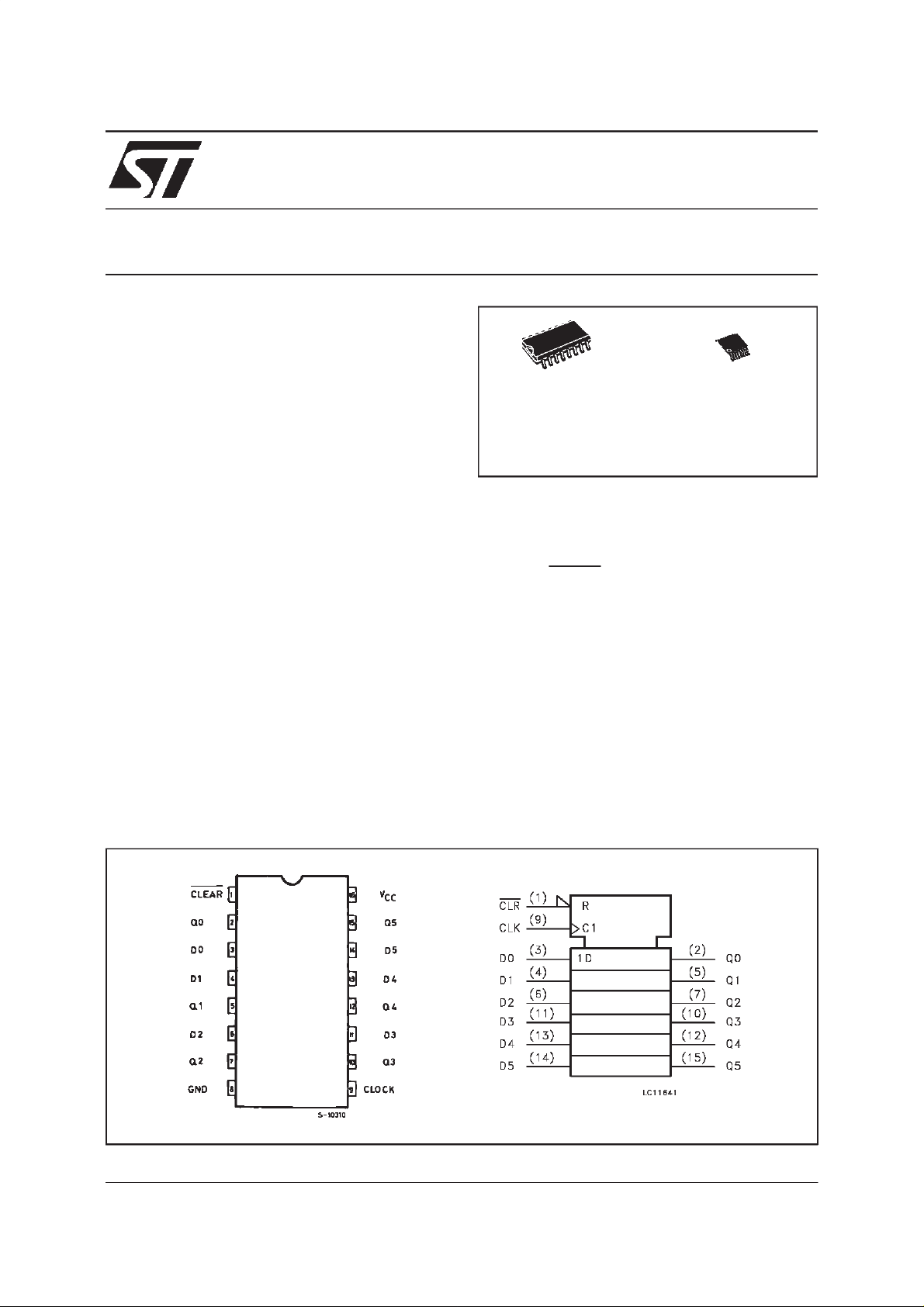

MOS

74LVQ174

M

(Micro Package)

(TSSOPPackage)

ORDERCODES :

74LVQ174M 74LVQ174T

3.3Vapplications.

Information signals applied to D inputs are

transfered to the Q outputs on the positive going

edgeof the clock pulse.

Whenthe CLEAR input is held low, the Q outputs

are held low independentelyof the other inputs .

It has better speed performance at 3.3V than 5V

LS-TTL family combined with the true CMOS low

powerconsumption.

All inputs and outputs are equipped with

protection circuits against static discharge, giving

them 2KV ESD immunity and transient excess

voltage.

T

PIN CONNECTION AND IEC LOGIC SYMBOLS

February 1999

1/10

74LVQ174

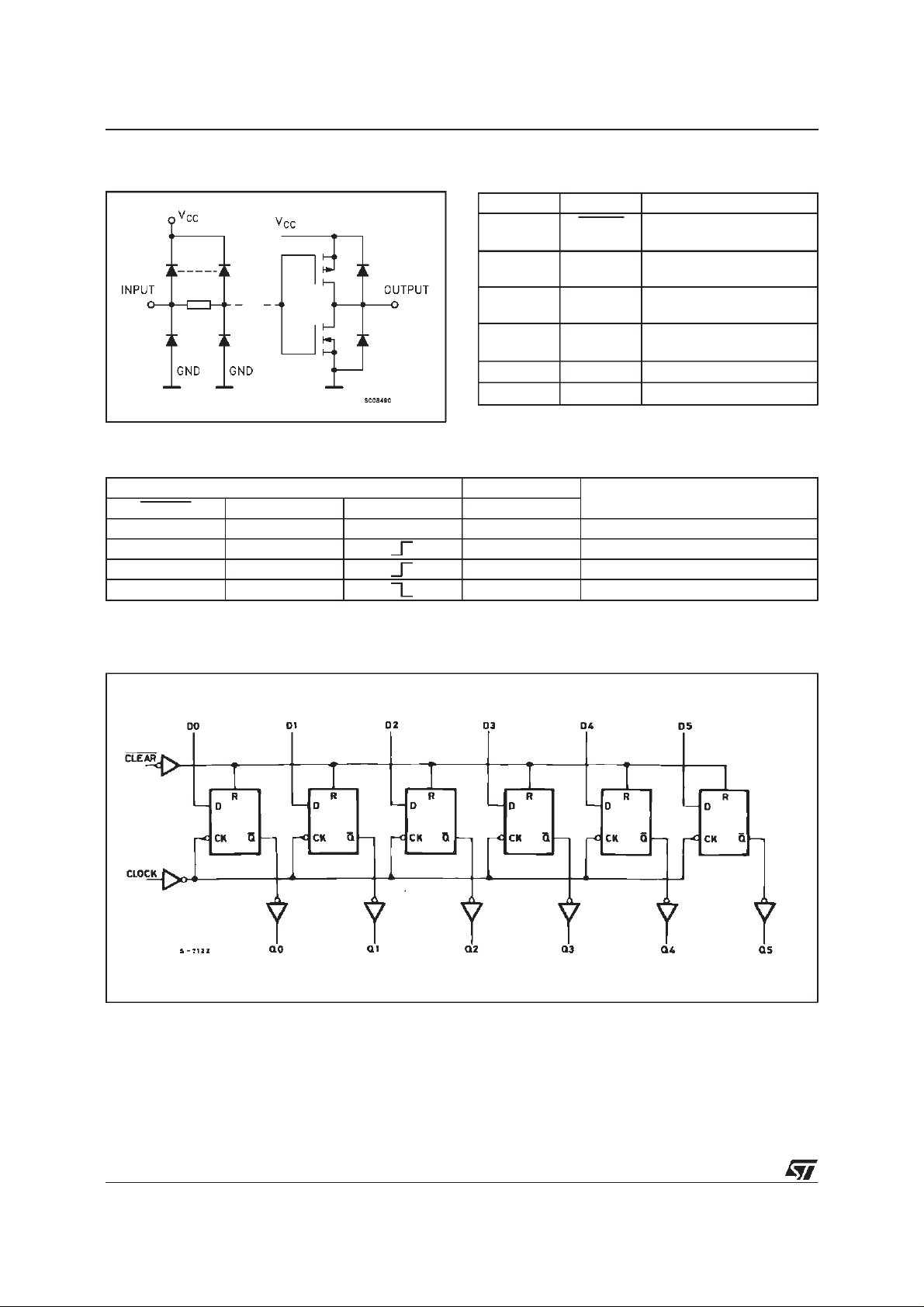

INPUT AND OUTPUT EQUIVALENTCIRCUIT

TRUTH TABLE

INPUTS OUTPUTS FUNCTION

CLE AR D CLOCK Q

L X X L CLEAR

HL L

HH H

HX Q

X:Don’tCare

PIN DESCRIPTION

PI N No SYM BO L NAM E AND F UNCT I O N

1 CLEAR Asyncronous Master Reset

(ActiveLOW)

2, 5, 7, 10,

12, 15

3, 4, 6, 11,

13, 14

9 CLOCK ClockInput (LOW-to-HIGH,

8 GND Ground(0V)

16 V

n

Q0 to Q5 Flip-Flop Outputs

D0 to D5 DataInputs

Edge-Triggered)

CC

PositiveSupply Voltage

NO CHANGE

LOGICDIAGRAM

Thislogic diagram has not be used to estimate propagation delays

2/10

74LVQ174

ABSOLUTE MAXIMUM RATINGS

Symb o l Para met er Val u e Uni t

V

V

V

I

I

OK

I

or I

I

CC

T

T

AbsoluteMaximumRatingsarethose values beyond whichdamagetothedevicemayoccur.Functionaloperationunderthese conditionisnotimplied.

RECOMMENDED OPERATINGCONDITIONS

Symb o l Para met er Value Un it

V

V

V

T

dt/dv InputRiseand FallTime (V

1) Truth Table guaranteed: 1.2V to 3.6V

2)V

from0.8Vto 2V

IN

SupplyVoltage -0.5 to +7 V

CC

DC InputVoltage -0.5 to VCC+ 0.5 V

I

DC OutputVoltage -0.5 to VCC+ 0.5 V

O

DC InputDiode Current ± 20 mA

IK

DC OutputDiodeCurrent ± 20 mA

DC OutputCurrent

O

DC VCCorGround Current

GND

Storage Temperature -65 to +150

stg

LeadTemperature (10 sec) 300

L

SupplyVoltage(note1) 2 to 3.6 V

CC

InputVoltage 0 to V

I

OutputVoltage 0 to V

O

OperatingTemperature: -40 to +85

op

=3V)(note2) 0 to 10 ns/V

CC

50 mA

±

300 mA

±

CC

CC

o

C

o

C

V

V

o

C

3/10

Loading...

Loading...