SGS Thomson Microelectronics 74LVQ161TTR, 74LVQ161MTR, 74LVQ161M Datasheet

1/13July 2001

■ HIGH SPEED:

f

MAX

= 180 MHz (TYP.) at VCC = 3.3 V

■ COMPA TIBLE WITH TTL OU TP U TS

■ LOW POWER DISSIPATION:

I

CC

= 4 µA (MAX.) at TA=25°C

■ LOW NOISE:

V

OLP

= 0.3V (TYP.) at VCC = 3.3V

■ 75Ω TRANSMISSION LINE DRIVING

CAPABILITY

■ SYMMETRICAL OUTPUT IMPEDANCE:

|I

OH

| = IOL = 12mA (MIN) at VCC = 3.0 V

■ PCI BUS LEVELS GUARANTEED AT 24 mA

■ BALANCED PROPAGATION DELAYS:

t

PLH

≅ t

PHL

■ OPERATING VOLTAGE RANGE:

V

CC

(OPR) = 2V to 3.6V (1.2V Data Retention)

■ PIN AND FUNCTION COMPATIBLE WITH

74 SERIES 161

■ IMPROVED LATCH-UP IMMUNITY

DESCRIPTION

The 74LVQ161 is a low voltage CMOS

SYNCHRONOUS PRESETTABLE COUNTER

fabricated with sub-micron silicon gate and

double-layer metal wiring C

2

MOS technology. It is

ideal for low power and low noise 3.3V

applications. It is a 4 bit binary counter with

Asynchronous Clear.

The circuit have four fundamental modes of

operation, in order of preference: synchronous

reset, parallel load, count-up and hold. Four

control inputs, Master Reset (CLEAR

), Parallel

Enable Input (PE) and Count Enable Carry Input

(TE), determine the mode of operation as shown

in the Truth Table. A LOW signal on CLEAR

overrides counting and parallel loading and sets

all outputs on LOW state. A LOW signal on LOAD

overrides counting and allows information on

Parallel Data Qn inputs to be loaded into the

flip-flops on the next rising edge of CLOCK . With

LOAD

and CLEAR, PE and TE permit counting

when both are high. Conversely, a LOW signal on

either PE and TE inhibits counting. All inputs and

outputs are equipped with protection circuits

against static discharge, giving them 2KV ESD

immunity and transient excess voltage.

74LVQ161

SYNCHRONOUS PRESETTABLE 4-BIT COUNTER

PIN CONNECTION AND IEC LOGIC SYMBOLS

ORDER CODES

PACKAGE TUBE T & R

SOP 74LVQ161M 74LVQ161MTR

TSSOP 74LVQ161TTR

TSSOPSOP

74LVQ161

2/13

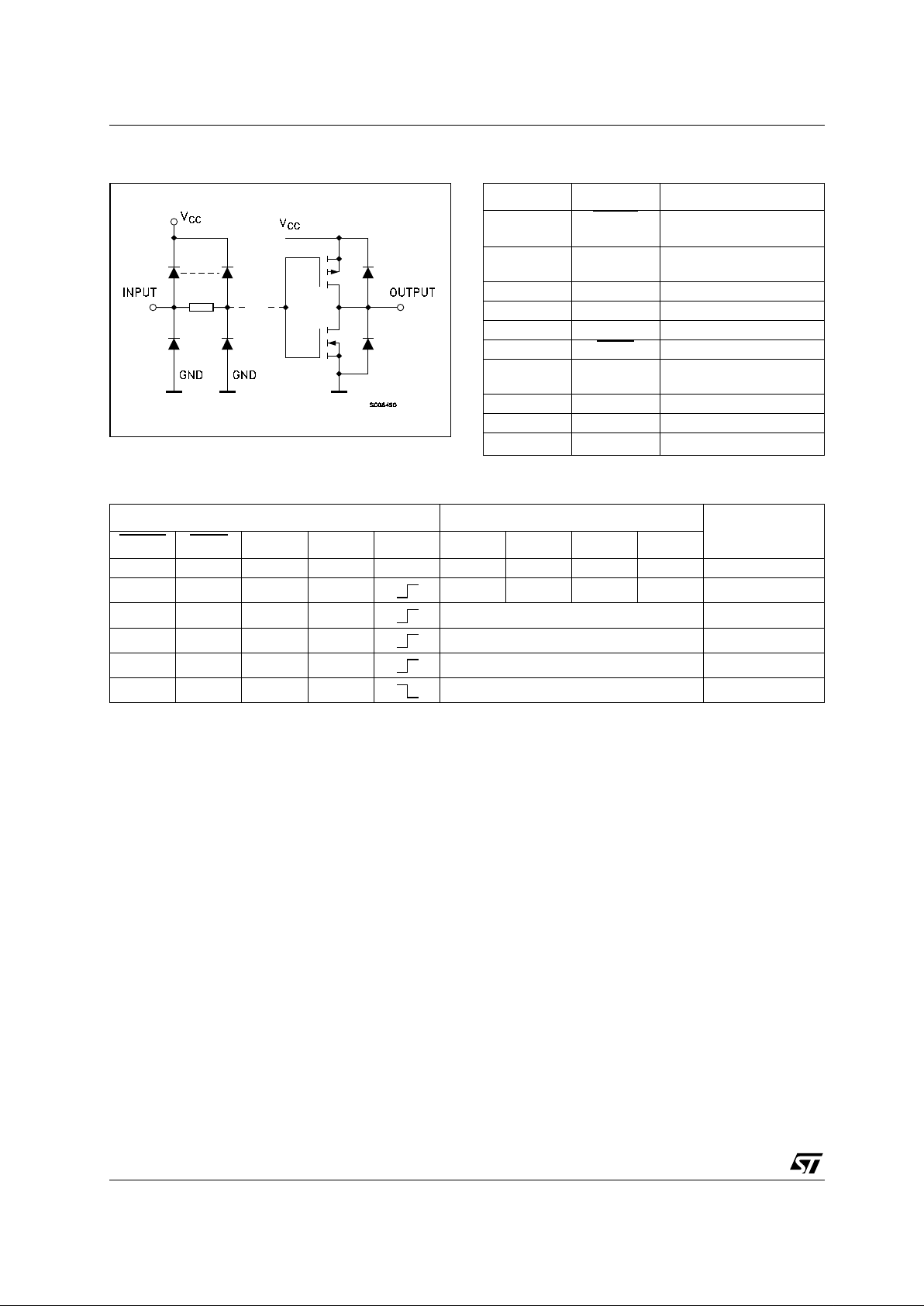

INPUT AND OUTPUT EQUIVALENT CIRCUIT PIN DESCRIPTION

TRUTH TABLE

X : Don’t Care; A, B, C, D; Logic level of data input; CARRY OUT : TE x QA x QB x QC x QD

PIN No SYMBOL NAME AND FUNCTION

1 CLEAR

Asynchronous Master

Reset

2 CLOCK Clock Input (LOW to

HIGH Edge Trigger)

3, 4, 5, 6 A, B, C, D Data Inputs

7 PE Count Enable Input

10 TE Count Enable Carry Input

9LOAD

Parallel Enable Input

14, 13, 12, 11QA to QD Flip-Flop Outputs

15 CARRY OUT Terminal Count Output

8 GND Ground (0V)

16 V

CC

Positive Supply Voltage

INPUTS OUTPUTS

FUNCTION

CLEAR

LOAD PE TE CK

LXXXXLLLLRESET TO "0"

H L X X A B C D PRESET DATA

H H X L NO CHANGE NO COUNT

H H L X NO CHANGE NO COUNT

HHHH COUNT UP COUNT

H X X X NO CHANGE NO COUNT

74LVQ161

3/13

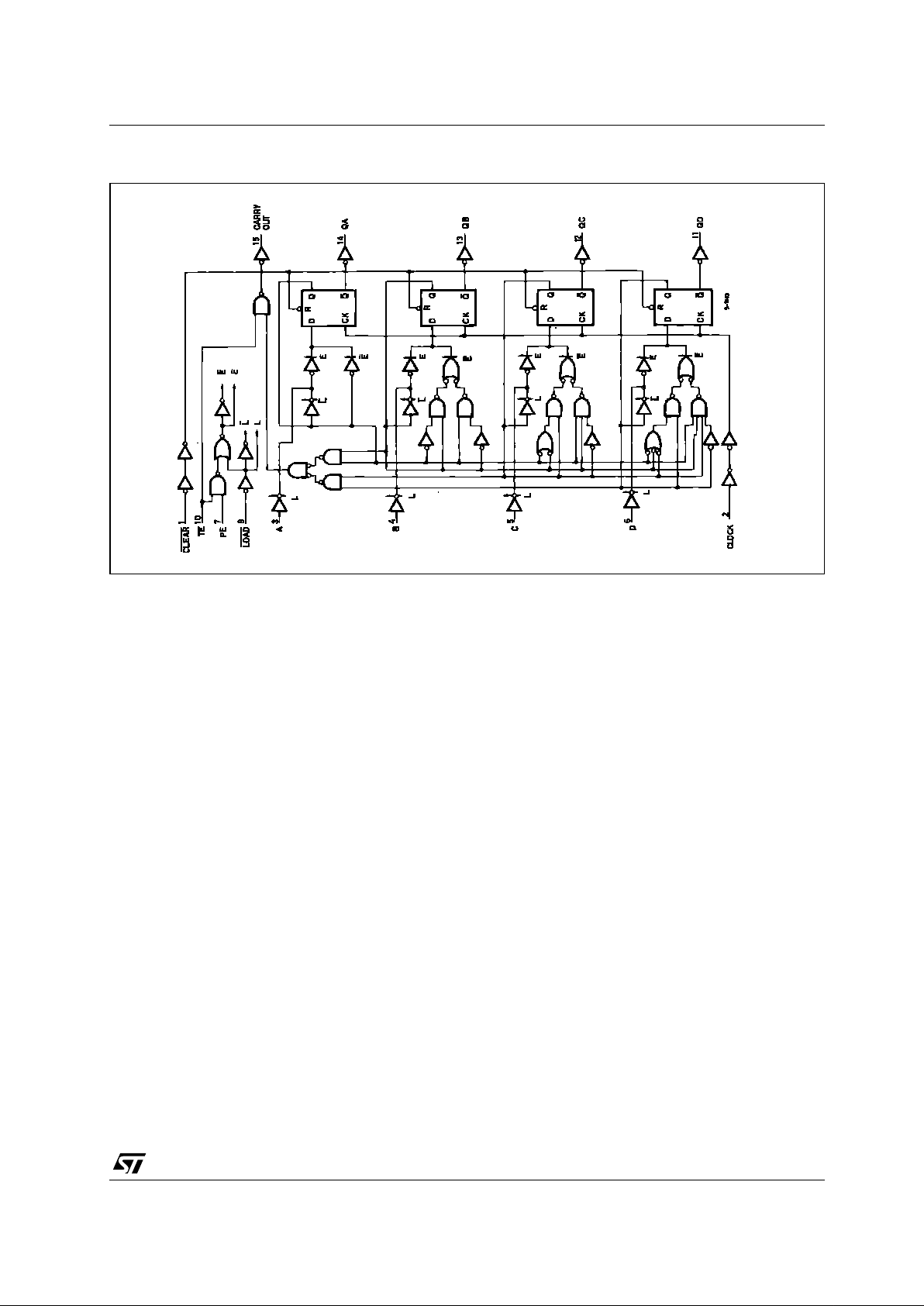

LOGIC DIAGRAM

74LVQ161

4/13

TIMING CHART

ABSOLUTE MAXIMUM RATINGS

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is

not implied

Symbol Parameter Value Unit

V

CC

Supply Voltage

-0.5 to +7 V

V

I

DC Input Voltage -0.5 to VCC + 0.5

V

V

O

DC Output Voltage -0.5 to VCC + 0.5

V

I

IK

DC Input Diode Current

± 20 mA

I

OK

DC Output Diode Current

± 20 mA

I

O

DC Output Current

± 50 mA

I

CC

or I

GND

DC VCC or Ground Current

± 300 mA

T

stg

Storage Temperature

-65 to +150 °C

T

L

Lead Temperature (10 sec)

300 °C

Loading...

Loading...