SGS Thomson Microelectronics 74LVQ138 Datasheet

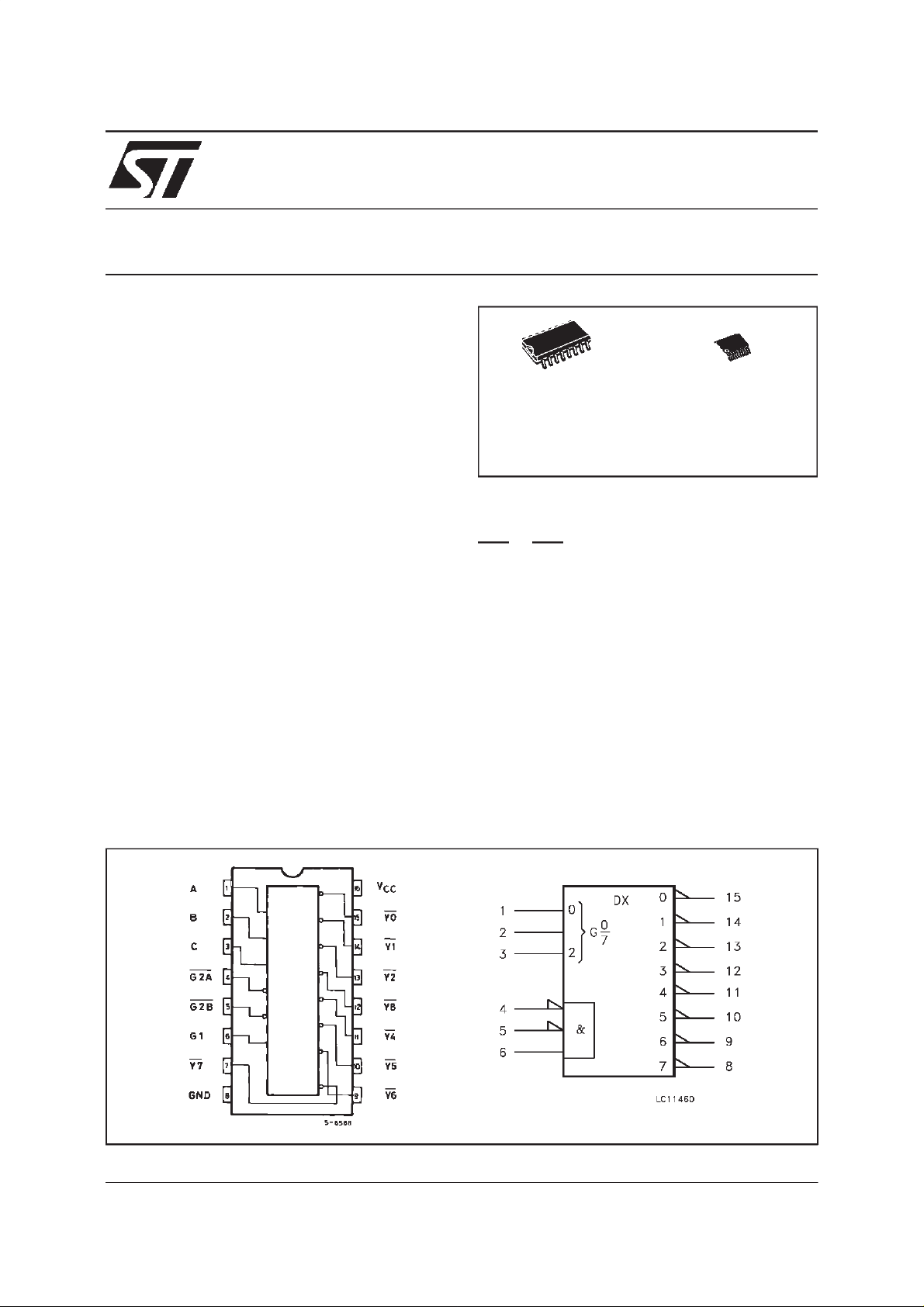

74LVQ138

3 TO 8 LINE DECODER (INVERTING)

■ HIGH SPEED:t

■

COMPATIBLEWITH TTLOUTPUT

■ LOW POWERDISSIPATION:

I

=4µA (MAX.)at TA=25oC

CC

■ LOWNOISE:

V

=0.2V(TYP.)atVCC=3.3V

OLP

■

75ΩTRANSMISSIONLINEDRIVING

=5.5ns(TYP.)atVCC=3.3V

PD

CAPABILITY

■ SYMMETRICALOUTPUTIMPEDANCE:

|I

|=IOL=12 mA(MIN)

OH

■ PCIBUSLEVELSGUARANTEED AT24mA

■

BALANCEDPROPAGATIONDELAYS:

t

≅ t

PLH

PHL

■ OPERATINGVOLTAGERAN GE:

V

(OPR)= 2V to3.6V(1.2VDataRetention)

CC

■ PINANDFUNCTIONCOMPATIBLEWITH

74SERIES138

■ IMPROVEDLATCH-UPIMMUNITY

DESCRIPTION

The LVQ138 is a low voltageCMOS3 TO 8 LINE

DECODER (INVERTING) fabricated with

sub-micron silicon gate and double-layer metal

wiringC

2

MOStechnology.

It is ideal for low power and low noise 3.3V

applications.

M1

(Micro Package)

(TSSOPPackage)

T

ORDERCODES :

74LVQ138M 74LVQ138T

If the device is enabled, 3 binary select inputs (A,

B and C) determine which one of the outputswill

go low. If enable input G1 is held low or either

G2A or G2B is held high, the decoding function is

inhibitedand all the 8 outputsgo high.

Three enable inputs are provided to ease

cascade connection and application of address

decodersfor memory systems.

It has better speed performance at 3.3V than 5V

LSTTL family combinad with the true CMOS low

powerconsumption.

All inputs and outputs are equipped with

protection circuits against static discharge, giving

them 2KV ESD immunity and transient excess

voltage.

PIN CONNECTION AND IEC LOGIC SYMBOLS

February 1999

1/9

74LVQ138

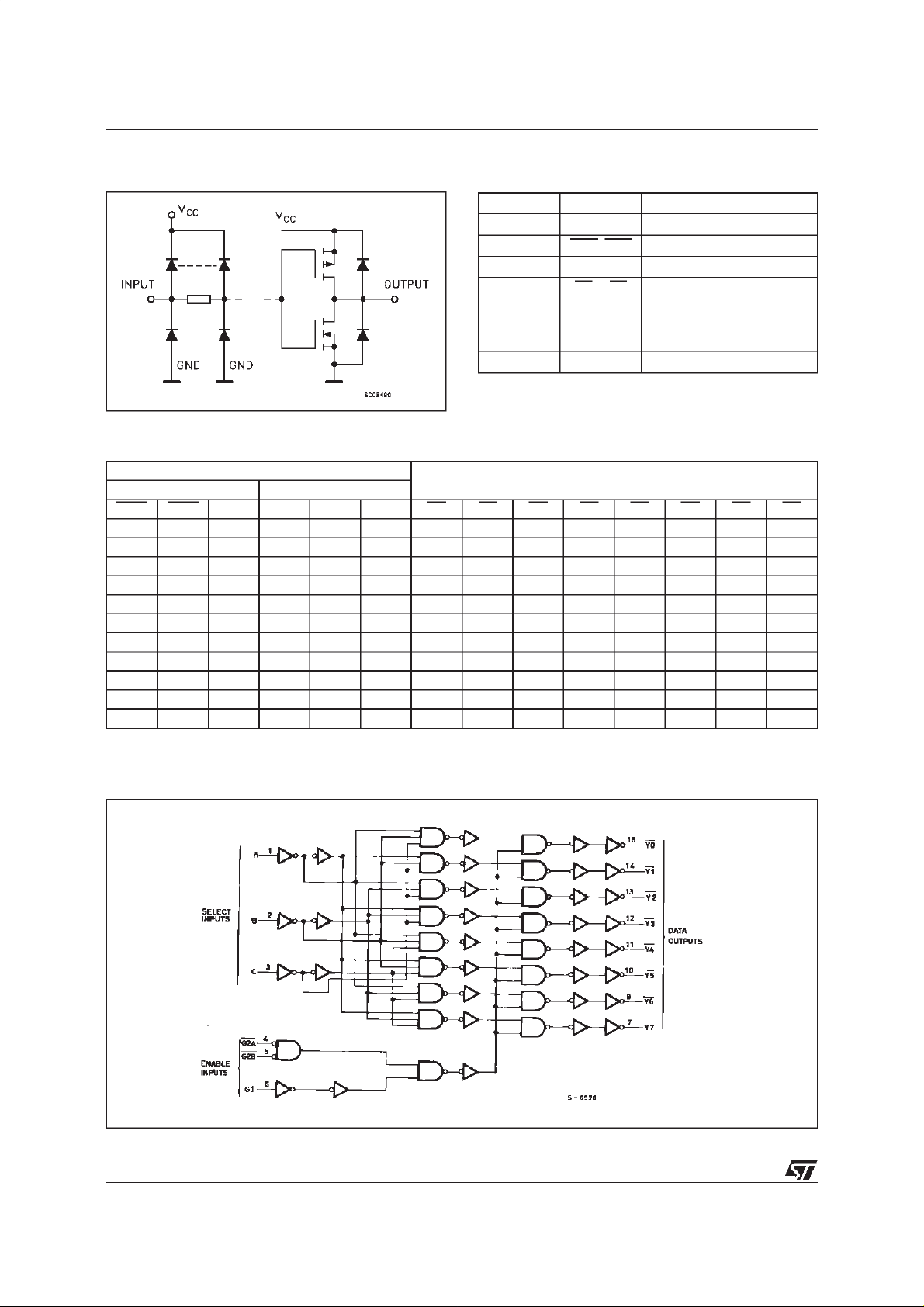

INPUT AND OUTPUT EQUIVALENTCIRCUIT

PIN DESCRIPTION

PI N No SYM BO L NAM E AN D FUNCTION

1, 2, 3 A, B, C Address Inputs

4, 5 G2A, G2B Enable Inputs

6 G1 Enable Input

15, 14, 13,

12, 11, 10,

9, 7

8 GND Ground (0V)

16 V

Y0 to Y7 Outputs

CC

Positive Supply Voltage

TRUTH TABLE

INPUTS OUTPUTS

ENABLE SELECT

G2BG2AG1 C B A Y0Y1Y2Y3Y4Y5Y6Y7

XXLXXXHHHHHHHH

XHXXXXHHHHHHHH

HXXXXXHHHHHHHH

LLHLLLLHHHHHHH

LLHLLHHLHHHHHH

LLHLHLHHLHHHHH

LLHLHHHHHLHHHH

LLHHLLHHHHLHHH

LLHHLHHHHHHLHH

LLHHHLHHHHHHLH

LLHHHHHHHHHHHL

X:Don’tCare

LOGICDIAGRAM

Thislogic diagram has notbe used to esimate propagation delays

2/9

74LVQ138

ABSOLUTE MAXIMUM RATINGS

Symb o l Para met er Val u e Uni t

V

V

V

I

I

OK

I

or I

I

CC

T

T

AbsoluteMaximumRatingsarethosevaluesbeyond whichdamagetothedevicemayoccur. Functional operationunder these condition isnotimplied.

(*)500mW: ≅ 65

RECOMMENDED OPERATINGCONDITIONS

Symb o l Para met er Value Un it

V

V

V

T

dt/dv Input Rise and Fall Time (V

1) Truth Table guaranteed: 1.2V to 3.6V

from 0.8V to2V

2)V

IN

Supply Voltage -0.5 to +7 V

CC

DC Input Voltage -0.5 to VCC+ 0.5 V

I

DC Output Voltage -0.5 to VCC+ 0.5 V

O

DC Input Diode Current ± 20 mA

IK

DC Output Diode Current ± 20 mA

DC Output Current

O

DC VCCor Ground Current

GND

Storage Temperature -65 to +150

stg

Lead Temperature (10 sec) 300

L

o

Cderatedto 300mW by10mW/oC:65oCto85oC

Supply Voltage (note 1) 2 to 3.6 V

CC

Input Voltage 0 to V

I

Output Voltage 0 to V

O

Operating Temperature: -40 to +85

op

= 3V) (note 2) 0 to 10 ns/V

CC

50 mA

±

200 mA

±

CC

CC

o

C

o

C

V

V

o

C

3/9

Loading...

Loading...