74ACT573

OCTAL D-TYPE LATCH

WITH 3 STATE OUTPUT NON INVERTING

■ HIGHSPEED:t

■

LOW POWER DISSIPATION:

I

=8 µA (MAX.) at TA=25oC

CC

■

COMPATIBLEWITHTTL OUTPUTS

V

=2V(MIN),VIL=0.8V(MAX)

IH

■ 50Ω TRANSMISSIONLINEDRIVING

=5ns(TYP.)atVCC=5V

PD

CAPABILITY

■ SYMMETRICALOUTPUTIMPEDANCE:

|I

|=IOL=24mA(MIN)

OH

■ BALANCEDPROPAGATIONDELAYS:

t

≅ t

PLH

PHL

■

OPERATINGVOLTAGERANGE:

V

(OPR)= 4.5Vto 5.5V

CC

■ PINANDFUNCTION COMPATIBLEWITH

74SERIES573

■ IMPROVEDLATCH-UP IMMUNITY

DESCRIPTION

The ACT573 is an advanced high-speed CMOS

OCTAL D-TYPE LATCH with 3 STATE OUTPUT

NON INVERTING fabricated with sub-micron

silicon gate and double-layermetal wiring C

2

MOS

technology. It is ideal for low power applications

mantaining high speed operation similar to

equivalentBipolarSchottky TTL.

These 8 bit D-Type latch are controlledby a latch

enable input (LE) and an output enable input

(OE).

M

(Micro Package)

B

(PlasticPackage)

ORDER CODES :

74ACT273B

74ACT273M

(TSSOPPackage)

T

While the LE inputs is held at a high level, the Q

outputs will follow the data input precisely or

inversely. When the LE is taken low, the Q

outputs will be latched precisely or inversely at

the logic level of D input data. While the (OE)

input is low, the 8 outputswill be in a normallogic

state (high or low logic level) and while high level

the outputs will be ina high impedancestate.

This device is designed to interface directly High

Speed CMOS systems with TTL and NMOS

components.

All inputs and outputs are equipped with

protection circuits against static discharge, giving

them 2KV ESD immunity and transient excess

voltage.

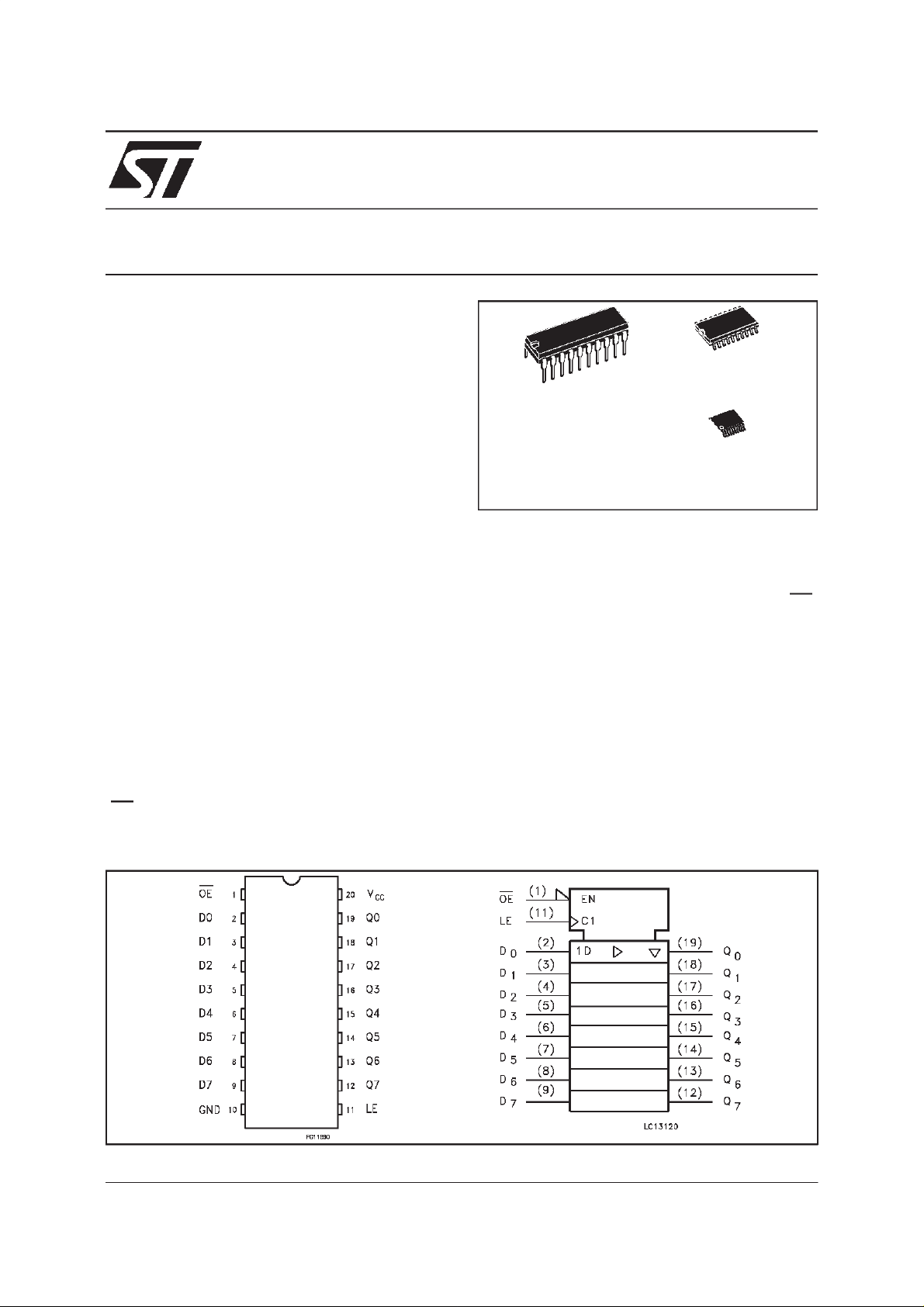

PIN CONNECTION AND IEC LOGIC SYMBOLS

May 1999

1/11

74ACT573

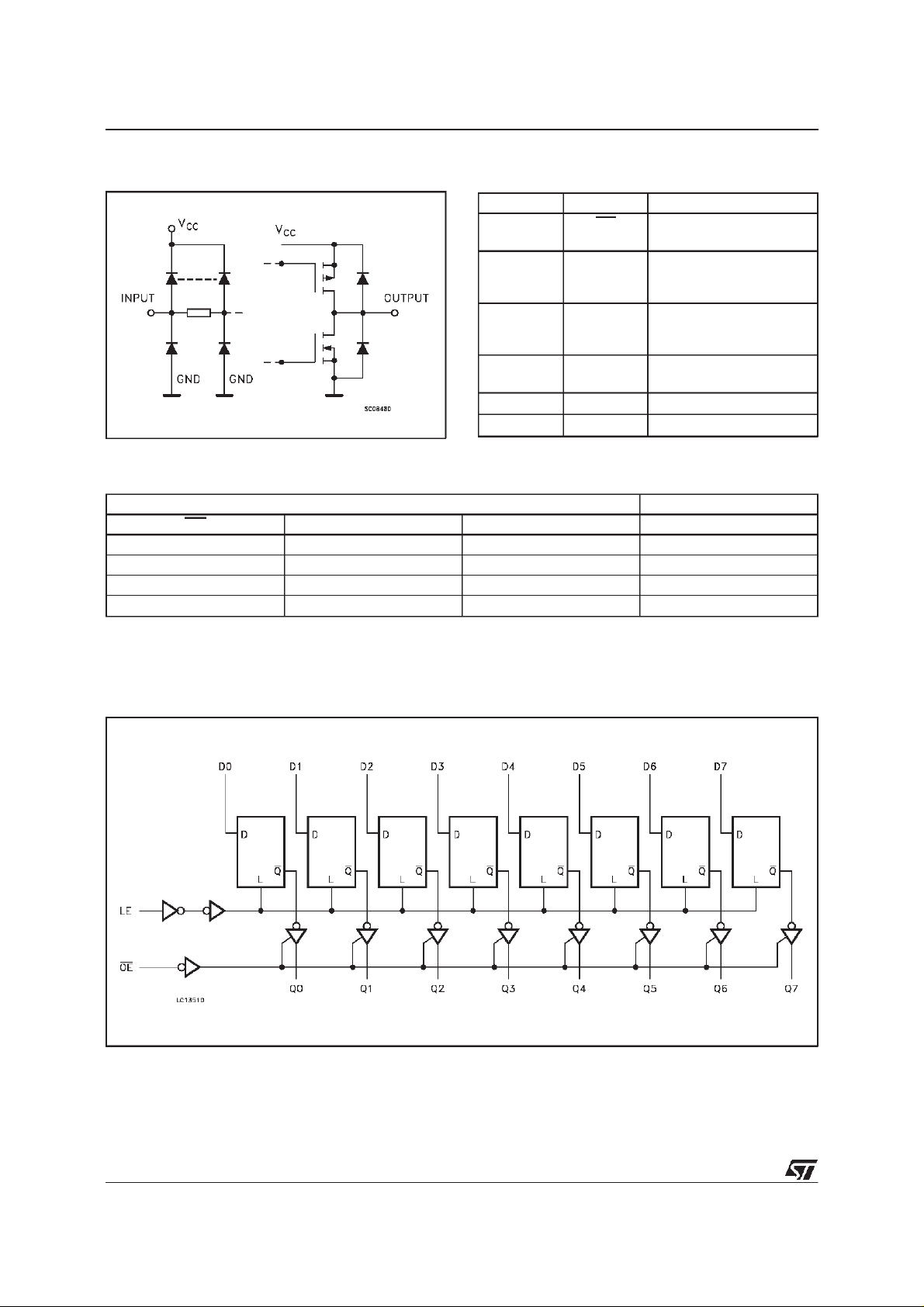

INPUT AND OUTPUT EQUIVALENTCIRCUIT PIN DESCRIPTION

PI N No SYMB OL NAME AND FUNCTIO N

1 OE 3 State Output Enable

2, 3, 4,

5, 6, 7,

8, 9

12, 13, 14,

15, 16, 17,

18, 19

11 LE Latch Enable

10 GND Ground (0V)

20 V

TRUTH TABLE

INPUTS OUTPUTS

OE CK D Q

HXXZ

L L X NO CHANGE *

LHLL

LHHH

X:DON’TCARE

Z:HIGHIMPEDANCE

*:Q OUTPUTSARELATCHEDATTHETIMEWHENTHELEINPUTISTAKENLOWLOGICLEVEL.

D0 to D7 Data Inputs

Q0 to Q7 3 State Outputs

CC

Input (Active LOW)

Input

Positive Supply Voltage

LOGICDIAGRAMS

2/11

74ACT573

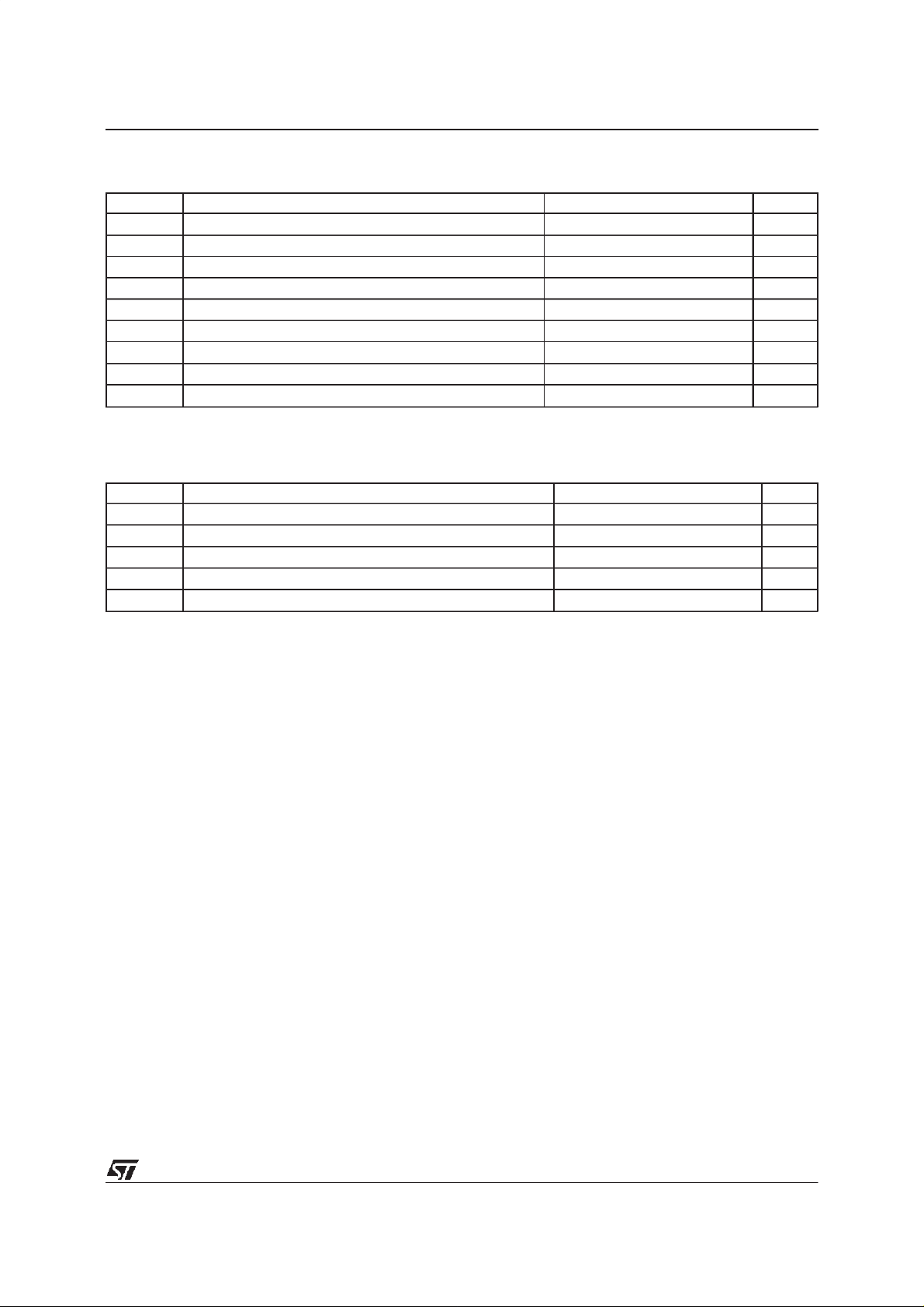

ABSOLUTE MAXIMUM RATINGS

Symb o l Paramet er Val u e Uni t

V

V

V

I

I

OK

I

or I

I

CC

T

T

AbsoluteMaximumRatingsarethosevaluesbeyondwhichdamagetothedevicemayoccur.Functionaloperation underthese conditionisnot implied.

RECOMMENDEDOPERATINGCONDITIONS

Symb o l Parameter Val u e Uni t

V

V

V

T

dt/dv Input Rise and Fall Time V

1)VINfrom0.8V to2.0V

Supply Voltage -0.5 to +7 V

CC

DC Input Voltage -0.5 to VCC+ 0.5 V

I

DC Output Voltage -0.5 to VCC+ 0.5 V

O

DC Input Diode Current ± 20 mA

IK

DC Output Diode Current ± 20 mA

DC Output Current

O

DC VCCor Ground Current

GND

Storage Temperature -65 to +150

stg

Lead Temperature (10 sec) 300

L

Supply Voltage 4.5 to 5.5 V

CC

Input Voltage 0 to V

I

Output Voltage 0 to V

O

Operating Temperature: -40 to +85

op

= 4.5 to 5.5V (note 1) 8 ns/V

CC

50 mA

±

400 mA

±

CC

CC

o

C

o

C

V

V

o

C

3/11

74ACT573

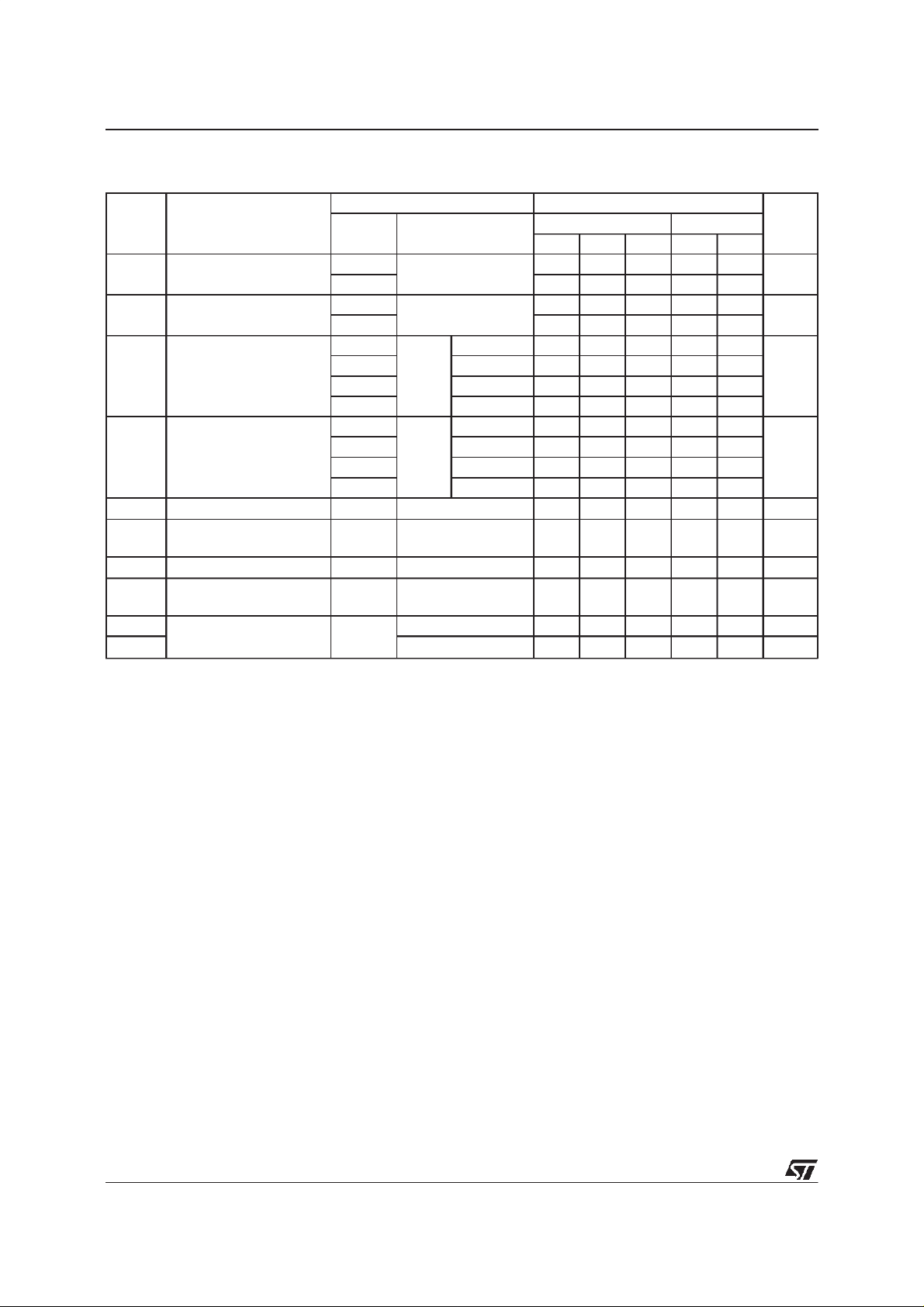

DC SPECIFICATIONS

Symbol Parameter Test Conditi ons Value Unit

T

V

CC

(V)

High Level Input Voltage 4.5 VO= 0.1V or

V

IH

5.5 2.0 1.5 2.0

Low Level Input Voltage 4.5 VO= 0.1V or

V

IL

5.5 1.5 0.8 0.8

High Level Output

V

OH

Voltage

4.5

5.5 I

V

V

4.5 I

5.5 I

Low Level Output

V

OL

Voltage

4.5

5.5 I

V

V

4.5 I

5.5 I

Input Leakage Current 5.5 VI=VCCor GND ±0.1 ±1 µA

I

I

3 State Output Leakage

I

OZ

5.5 VI=VIHor V

Current

Max ICC/Input 5.5 VI=VCC-2.1V 0.6 1.5 mA

I

CCT

Quiescent Supply

I

CC

5.5 VI=VCCor GND 8 80 µA

-0.1 V

V

CC

V

-0.1 V

CC

IO=-50µA 4.4 4.49 4.4

(*)

=

I

IH

V

IL

(*)

I

IH

V

IL

=-50 µA 5.4 5.49 5.4

O

or

=-24 mA 3.86 3.76

O

=-24 mA 4.86 4.76

O

IO=50 µA 0.001 0.1 0.1

=

=50 mA 0.001 0.1 0.1

O

or

=24 mA 0.36 0.44

O

=24 mA 0.36 0.44

O

IL

VO=VCCor GND

Current

Dynamic Output Current

I

OLD

OHD

(note 1, 2)

I

1) Maximum test duration 2ms,one output loaded attime

2)Incident wave switchingis guaranteed ontransmissionlineswithimpedancesaslow as50 Ω.

(*)All outputs loaded.

5.5 V

= 1.65 V max 75 mA

OLD

V

= 3.85 V min -75 mA

OHD

=25oC -40 t o 85oC

A

Min. Typ. Max. Min. Max.

2.0 1.5 2.0

1.5 0.8 0.8

±0.5 ±5 µA

V

V

V

V

4/11

Loading...

Loading...