74ACT280

9 BIT PARITY GENERATOR/CHECKER

■ HIGHSPEED:t

■

LOW POWERDISSIPATION:

I

=4 µA (MAX.) atTA=25oC

CC

■

COMPATIBLEWITHTTLOUTPUTS

V

=2V(MIN),VIL=0.8V(MAX)

IH

■ 50Ω TRANSMISSIONLINEDRIVING

=4ns(TYP.)atVCC=5V

PD

CAPABILITY

■ SYMMETRICALOUTPUTIMPEDANCE:

|I

|=IOL=24mA (MIN)

OH

■ BALANCEDPROPAGATIONDELAYS:

t

≅ t

PLH

PHL

■

OPERATINGVOLT AGERANGE:

V

(OPR)= 4.5 Vto 5.5V

CC

■ PINANDFUNCTIONCOMPATIBLEWITH

74SERIES280

■ IMPROVEDLATCH-UPIMMUNITY

DESCRIPTION

The AC280 is an advanced high-speed CMOS 9

BIT PARITY GENERATOR - CHECKER

fabricated with sub-micron silicon gate and

double-layermetal wiring C

2

MOS technology.It is

ideal for low power applications mantaining high

speed operation similar to eqivalent Bipolar

SchottkyTTL.

It is composed of nine data inputs (A to I) and

odd/evenparity outputs(ΣODD andΣEVEN).The

B

(PlasticPackage)

(Micro Package)

M

ORDERCODES :

74ACT280B 74ACT280M

nine data inputs control the output conditions.

When the number of high level input is odd,

ΣODD output is kept high and ΣEVEN outputlow.

Conservely, when the output is even,ΣEVEN

output is kept high and ΣODD low.

The IC generates either odd or even parity

makingit flexibleapplication.

The word-length capability is easily expanded by

cascading.

The device is designed to interface directly High

Speed CMOS systems with TTL, NMOS and

CMOSoutput voltage levels.

All inputs and outputs are equipped with

protection circuits against static discharge, giving

them 2KV ESD immunity and transient excess

voltage.

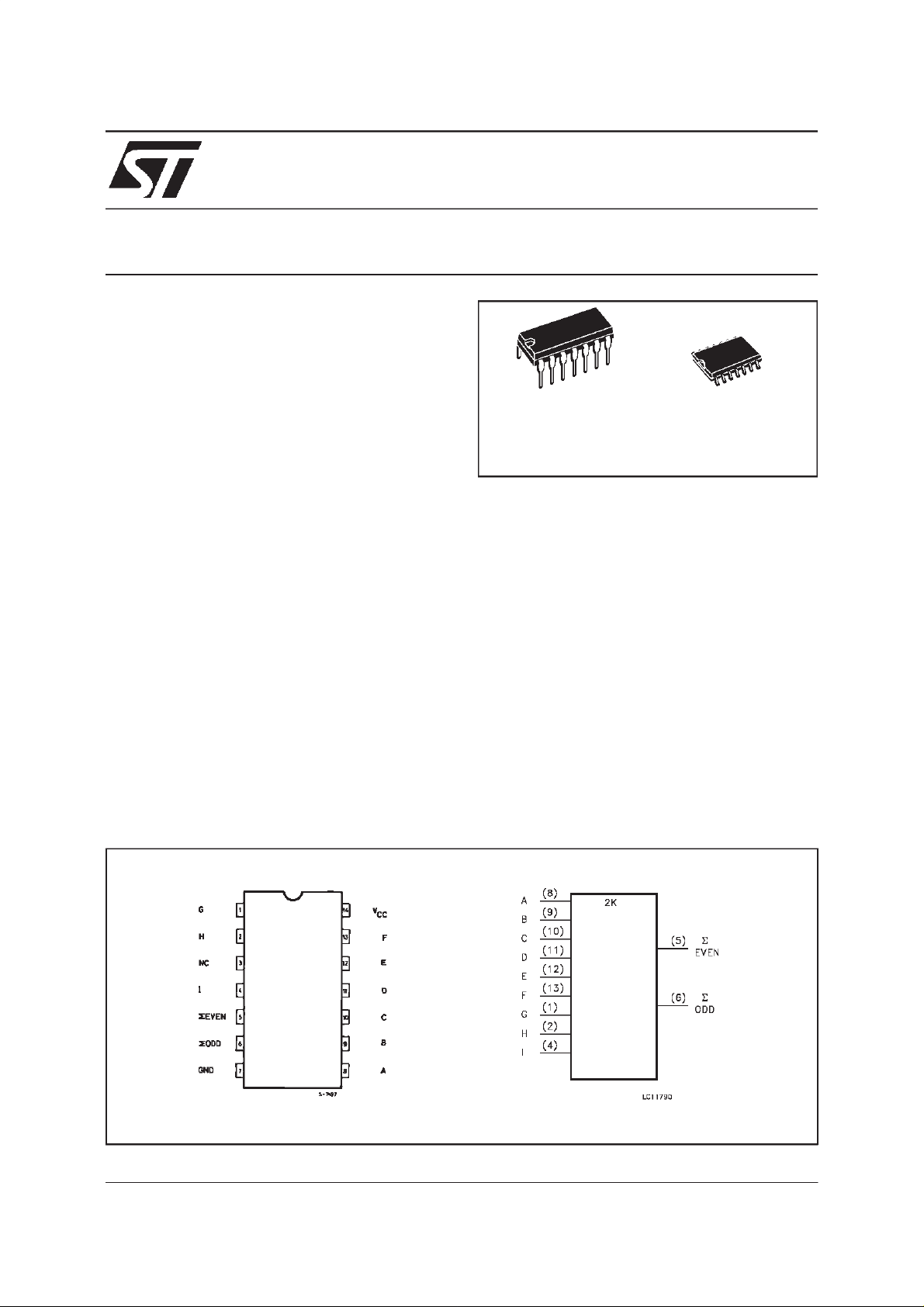

PIN CONNECTION AND IEC LOGICSYMBOLS

December 1998

1/8

74ACT280

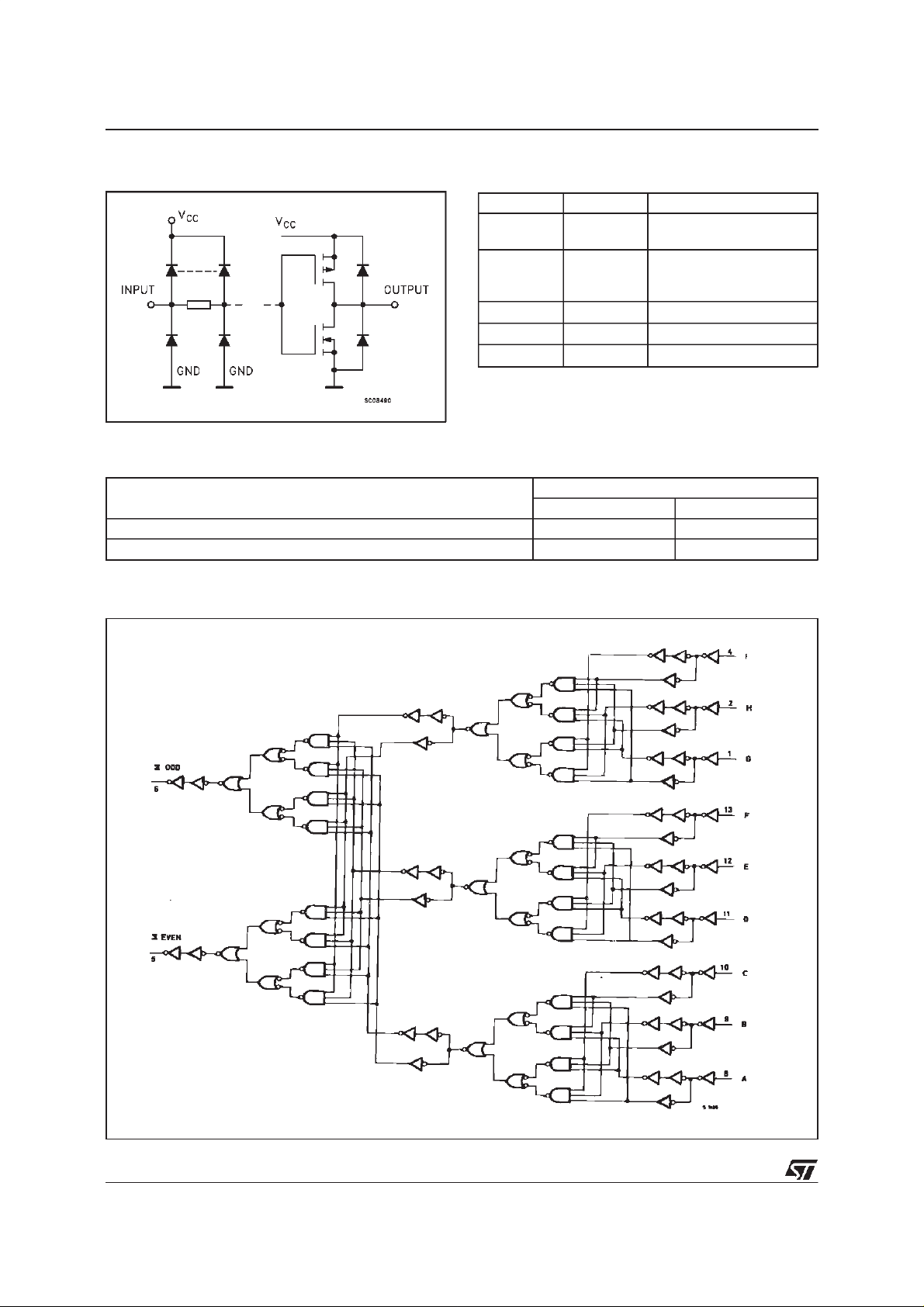

INPUT AND OUTPUT EQUIVALENTCIRCUIT

TRUTH TABLE

NUMB E R OF INP UT A TRHU I THAT ARE HIGH OUT P UT

0, 2, 4, 6, 8 H L

1, 3, 5, 7, 9 L H

LOGICDIAGRAM

PIN DESCRIPTION

PI N No SYMB OL NAME AND FUNCT I O N

5, 6

8, 9, 10, 11,

12, 13, 1, 2,

4

3 NC No Connection

7 GND Ground (0V)

14 V

EVEN

Σ

ΣODD

A to I Data Inputs

CC

EVEN

Σ

Parity Outputs

Positive Supply Voltage

ODD

Σ

2/8

74ACT280

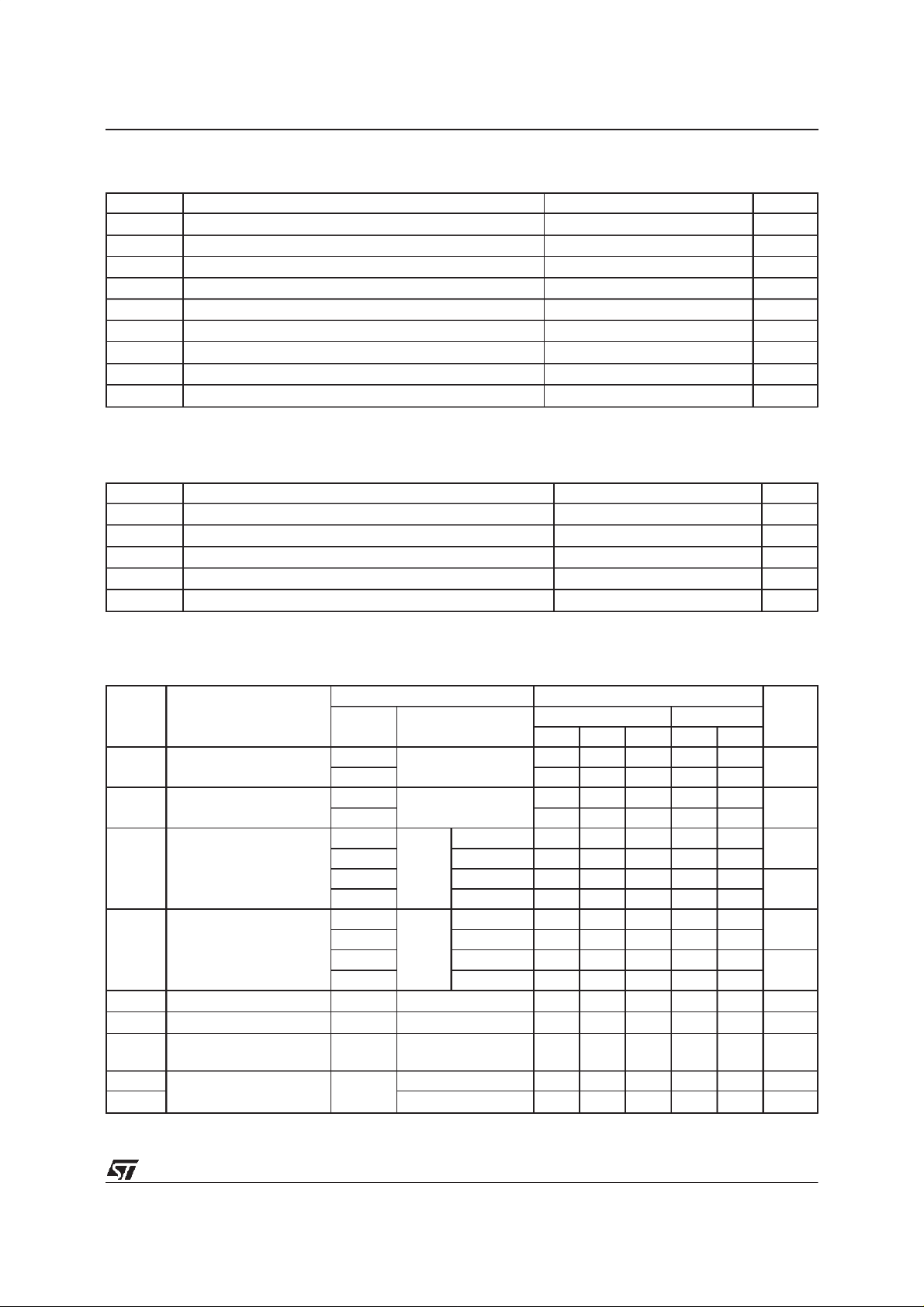

ABSOLUTE MAXIMUM RATINGS

Symb o l Para met er Val u e Uni t

V

V

V

I

I

OK

I

or I

I

CC

T

T

AbsoluteMaximumRatingsarethosevaluesbeyond whichdamagetothedevicemayoccur.Functionaloperationunderthese condition isnotimplied.

RECOMMENDED OPERATINGCONDITIONS

Symb o l Parameter Val u e Uni t

V

V

V

T

dt/dv Input Rise and Fall Time V

1)VINfrom0.8V to2.0V

Supply Voltage -0.5 to +7 V

CC

DC Input Voltage -0.5 to VCC+ 0.5 V

I

DC Output Voltage -0.5 to VCC+ 0.5 V

O

DC Input Diode Current ± 20 mA

IK

DC Output Diode Current ± 20 mA

DC Output Current

O

DC VCCor Ground Current

GND

Storage Temperature -65 to +150

stg

Lead Temperature (10 sec) 300

L

Supply Voltage 4.5 to 5.5 V

CC

Input Voltage 0 to V

I

Output Voltage 0 to V

O

Operating Temperature: -40 to +85

op

= 4.5 to 5.5V (note 1) 8 ns/V

CC

50 mA

±

200 mA

±

CC

CC

o

C

o

C

V

V

o

C

DC SPECIFICATIONS

Symbol Parameter Test Conditions Value Unit

=25oC -40 to 85oC

V

CC

(V)

High Level Input Voltage 4.5 VO= 0.1V or

V

IH

5.5 2.0 1.5 2.0

Low Level Input Voltage 4.5 VO= 0.1V or

V

IL

5.5 1.5 0.8 0.8

High Level Output

V

OH

Voltage

4.5

5.5 I

4.5 I

5.5 I

Low Level Output

V

OL

Voltage

4.5

5.5 I

4.5 I

5.5 I

Input Leakage Current 5.5 VI=VCCor GND ±0.1 ±1 µA

I

I

Max ICC/Input 5.5 VI=VCC-2.1V 0.6 1.5 mA

I

CCT

Quiescent Supply

I

CC

5.5 VI=VCCor GND 4 40

V

-0.1 V

CC

V

-0.1 V

CC

IO=-50 µA 4.4 4.49 4.4

(*)

=

V

I

V

IH

V

IL

(*)

V

I

V

IH

V

IL

=-50 µA 5.4 5.49 5.4

O

or

=-24 mA 3.86 3.76

O

=-24 mA 4.86 4.76

O

IO=50µA 0.001 0.1 0.1

=

=50 mA 0.001 0.1 0.1

O

or

=24 mA 0.36 0.44

O

=24 mA 0.36 0.44

O

Current

Dynamic Output Current

I

OLD

OHD

(note 1, 2)

I

1) Maximum test duration 2ms, one output loaded attime

2)Incident waveswitchingisguaranteed on transmissionlines withimpedances aslowas 50Ω.

5.5 V

= 1.65 V max 75 mA

OLD

V

= 3.85 V min -75 mA

OHD

T

A

Min. Typ. Max. Min. Max.

2.0 1.5 2.0

1.5 0.8 0.8

µ

V

V

V

V

A

3/8

Loading...

Loading...