SGS Thomson Microelectronics 74ACT00 Datasheet

74ACT00

QUAD 2-INPUT NAND GATE

■ HIGH SPEED: t

■ LOWPOWERDISSIPATION:

=4µA (MAX.)at TA=25oC

I

CC

■ COMPATIBLEWITH TTL OUTPUTS

V

=2V(MIN),VIL= 0.8V (MAX)

IH

■ 50Ω TRANSMISSIONLINE DRIVING

=5 ns (TYP.)atVCC=5V

PD

CAPABILITY

■ SYMMETRICAL OUTPUT IMPEDANCE:

|I

|=IOL=24mA (MIN)

OH

■ BALANCED PROPAGATIONDELAYS:

t

≅ t

PLH

PHL

■ OPERATINGVOLTAGERANGE:

V

(OPR)= 4.5V to 5.5V

CC

■ PIN AND FUNCTION COMPATIBLE WITH

74SERIES00

■ IMPROVED LATCH-UP IMMUNITY

DESCRIPTION

The ACT00 is an advanced high-speed CMOS

QUAD 2-INPUT NAND GATE fabricated with

sub-micron silicon gate and double-layer metal

wiring C

2

MOS technology. It is ideal for low

power applications mantaining high speed

B

(Plastic Package)

(Micro Package)

M

ORDERCODES:

74ACT00B

operation similar to equivalent Bipolar Schottky

TTL.

The internal circuit is composed of 3 stages

including buffer output, which enables high noise

immunityand stable output.

The device is designed to interface directly High

Speed CMOS systems with TTL, NMOS and

CMOSoutput voltage levels.

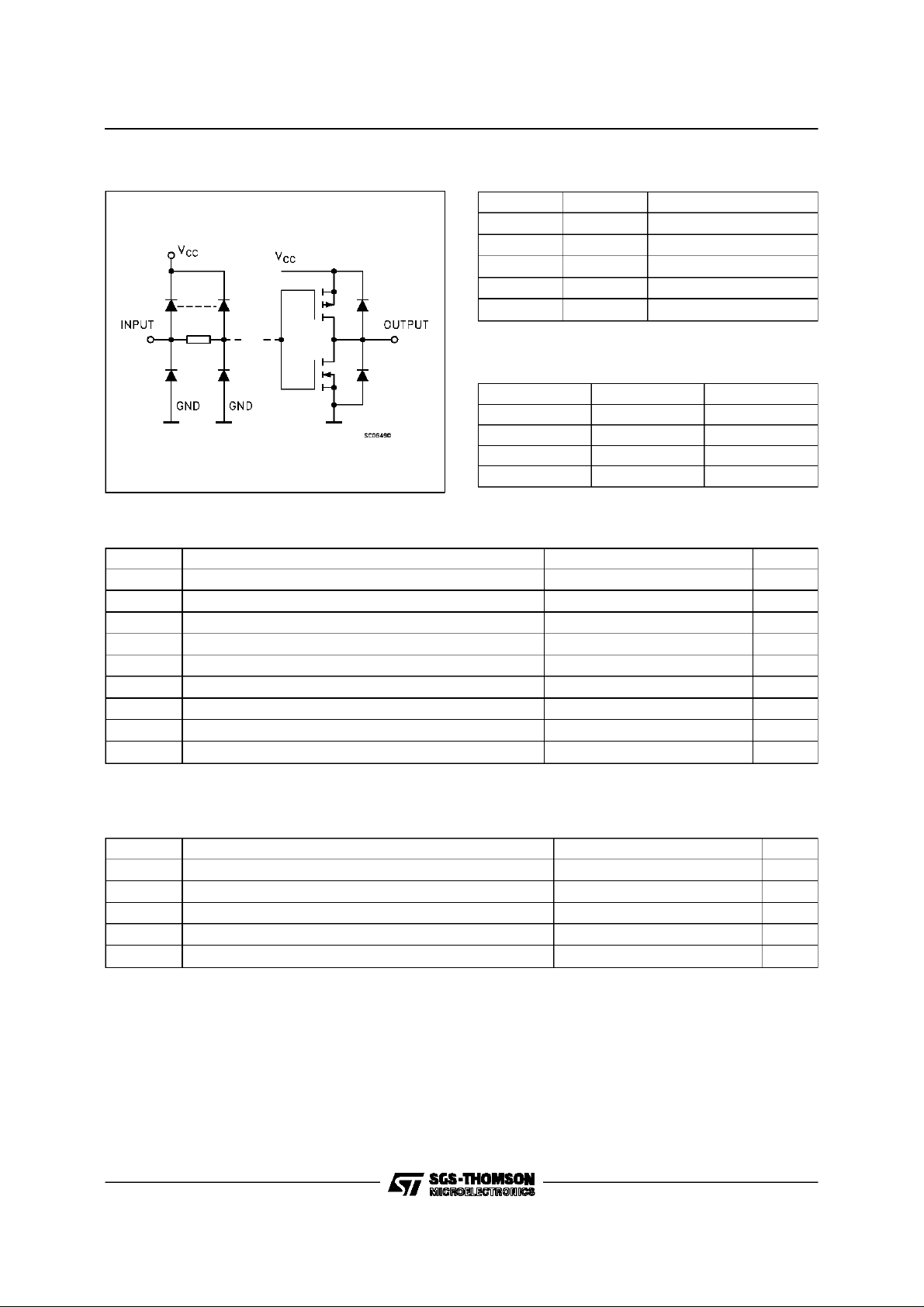

All inputs and outputs are equipped with

protectioncircuits against static discharge, giving

them 2KV ESD immunity and transient excess

voltage.

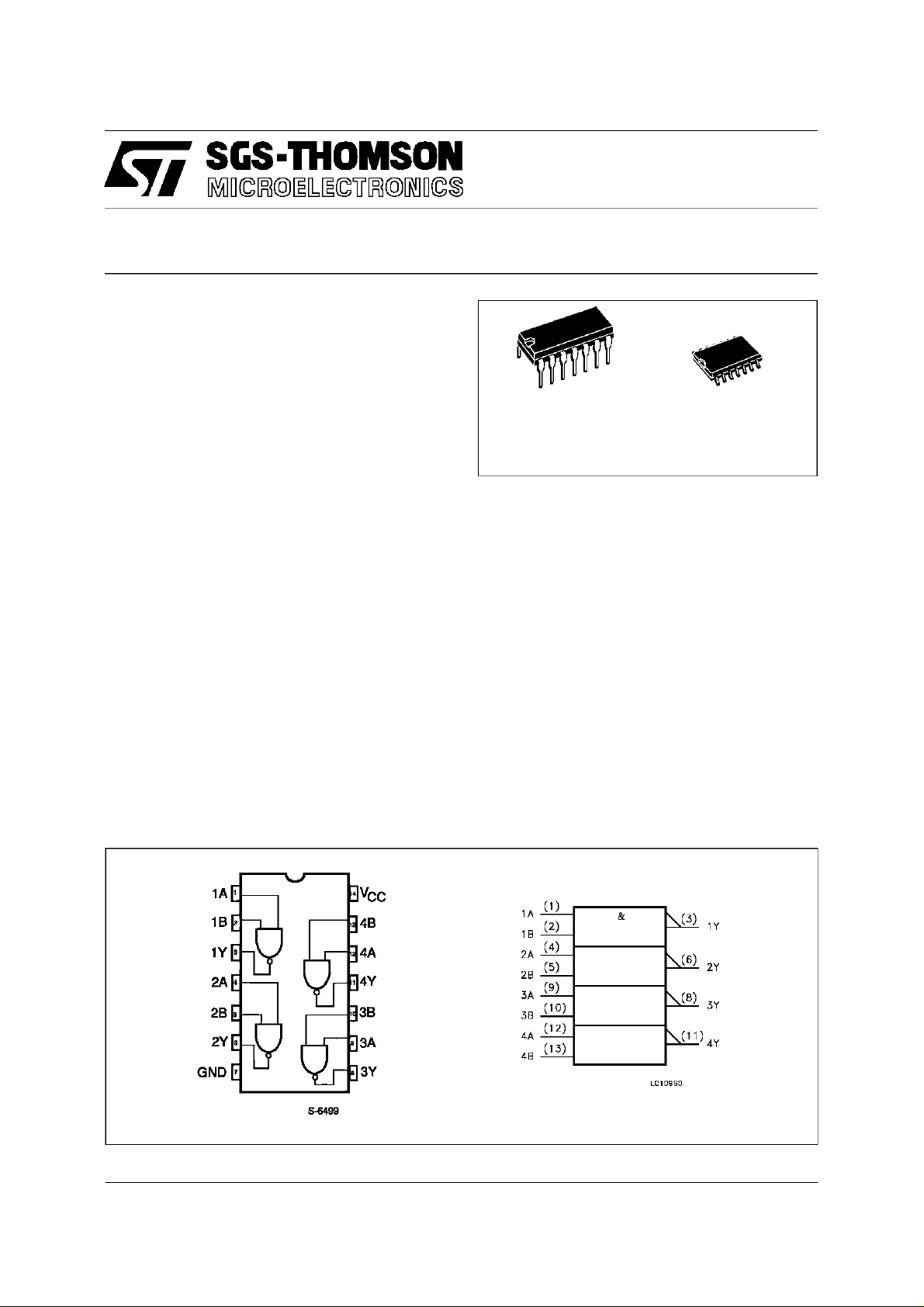

PINCONNECTION AND IEC LOGIC SYMBOLS

April 1997

1/7

74ACT00

INPUTAND OUTPUTEQUIVALENTCIRCUIT

PIN DESCRIPTION

PI N No SYM B O L NAME AN D FUNCT I ON

1, 4, 9, 12 1A to 4A Data Inputs

2, 5, 10, 13 1B to 4B Data Inputs

3, 6, 8, 11 1Y to 4Y Data Outputs

7 GND Ground (0V)

14 V

CC

Positive Supply Voltage

TRUTHTABLE

ABY

LLH

LHH

HLH

HHL

ABSOLUTE MAXIMUM RATINGS

Symb o l Parame t er Val u e Uni t

V

V

V

I

I

OK

I

orI

I

CC

T

T

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these condition is not implied.

Supply Voltage -0.5 to +7 V

CC

DC Input Voltage -0.5 to VCC+ 0.5 V

I

DC Output Voltage -0.5 to VCC+ 0.5 V

O

DC Input Diode Current ± 20 mA

IK

DC Output Diode Current ± 20 mA

DC Output Current ± 50 mA

O

DC VCCor Ground Current ± 200 mA

GND

Storage Temperature -65 to +150

stg

Lead Temperature (10 sec) 300

L

o

C

o

C

RECOMMENDED OPERATINGCONDITIONS

Symbol Parameter Valu e Unit

V

V

V

T

dt/dv Input Rise and Fall Time V

1) VINfrom0.8V to2.0V

2/7

Supply Voltage 4.5 to 5.5 V

CC

Input Voltage 0 to V

I

Output Voltage 0 to V

O

Operating Temperature: -40to +85

op

= 4.5 to 5.5V (note 1) 8 ns/V

CC

CC

CC

V

V

o

C

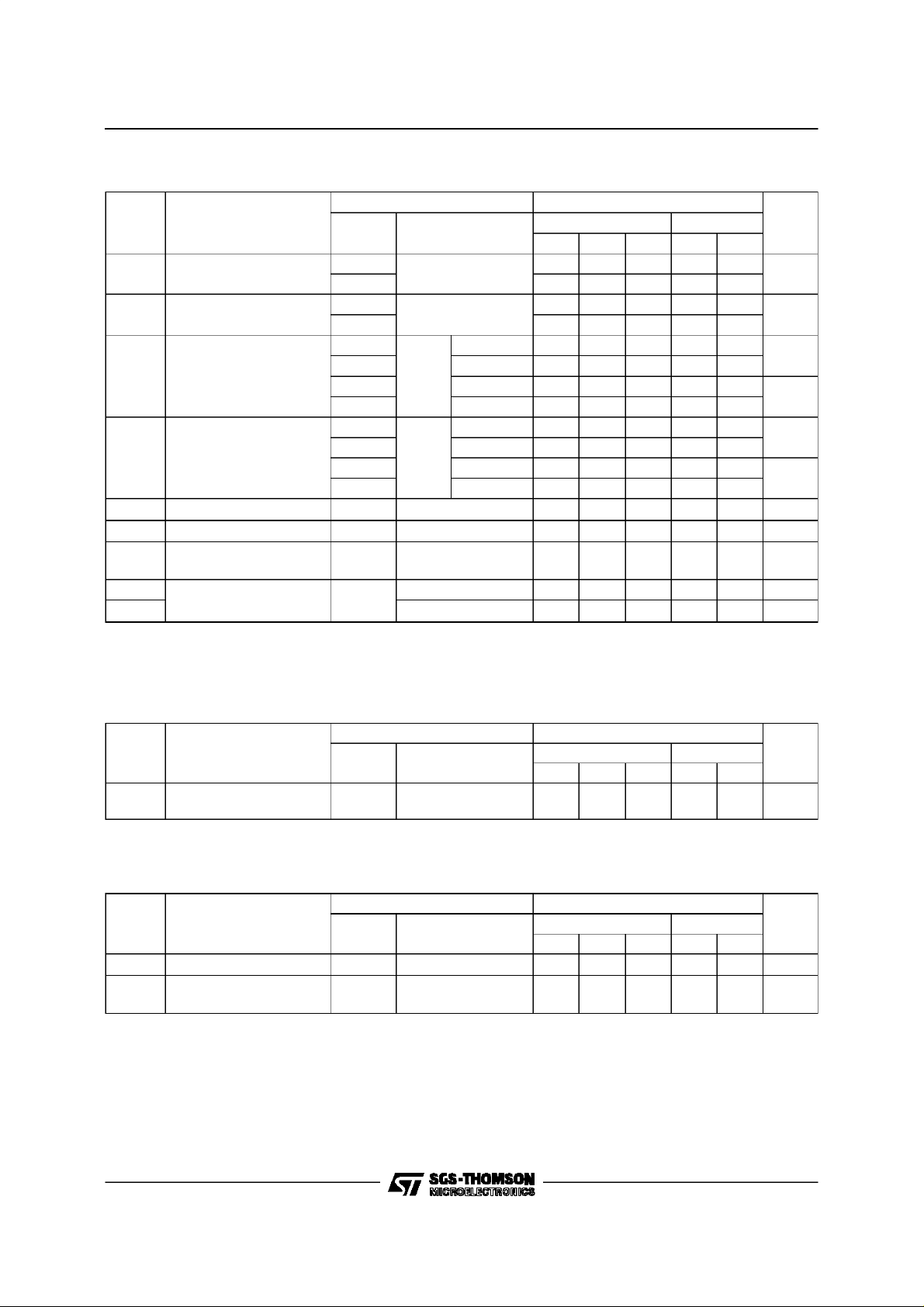

DC SPECIFICATIONS

74ACT00

Symbol Parameter Test Condit ions Value Unit

T

V

CC

(V)

High Level Input Voltage 4.5 VO= 0.1 V or

V

IH

5.5 2.0 1.5 2.0

Low Level Input Voltage 4.5 VO= 0.1 V or

V

IL

5.5 1.5 0.8 0.8

High Level Output

V

OH

Voltage

4.5

5.5 I

4.5 I

5.5 I

Low Level Output

V

OL

Voltage

4.5

5.5 I

4.5 I

5.5 I

Input Leakage Current

I

I

Max ICC/Input 5.5 VI=VCC-2.1 V 0.6 1.5 mA

I

CCT

Quiescent Supply

I

CC

5.5

5.5 VI=VCCor GND 4 40 µA

V

- 0.1 V

CC

- 0.1 V

V

CC

IO=-50 µA 4.4 4.49 4.4

(*)

=

V

I

V

IH

V

IL

(*)

V

I

V

IH

V

IL

=-50 µA 5.4 5.49 5.4

O

or

=-24 mA 3.86 3.76

O

=-24 mA 4.86 4.76

O

IO=50 µA 0.001 0.1 0.1

=

=50 mA 0.001 0.1 0.1

O

or

=24 mA 0.36 0.44

O

=24 mA 0.36 0.44

O

VI=VCCor GND ±0.1 ±1 µA

=25oC-40to85

A

Min. Typ. Max. Min . Max.

2.0 1.5 2.0

1.5 0.8 0.8

o

C

Current

Dynamic Output Current

I

OLD

OHD

(note 1, 2)

I

1) Maximum testduration 2ms, one output loaded at time

2) Incident wave switching is guaranteed on transmission lines with impedances as low as 50 Ω.

(*)All outputs loaded.

5.5 V

= 1.65 V max 75 mA

OLD

V

= 3.85 V min -75 mA

OHD

V

V

V

V

AC ELECTRICAL CHARACTERISTICS (CL= 50 pF, RL=500 Ω, Inputtr=tf=3ns)

Symbol Parameter Test Cond itio n Value Unit

t

Propagation Delay Time 5.0

PLH

t

PHL

(*) Voltagerangeis5V± 0.5V

V

(V)

CC

(*)

T

=25oC-40to85

A

Min. Typ. Max. Min . Max.

1.5 5.0 9.0 1.0 9.5 ns

o

C

CAPACITIVE CHARACTERISTICS

Symbol Parameter Test Condit ions Value Unit

=25oC-40to85

T

A

Min. Typ. Max. Min . Max.

4

Input Capacitance

C

IN

Power Dissipation

C

PD

V

CC

(V)

5.0

5.0 31 pF

Capacitance (note 1)

1) CPDis defined as the value ofthe IC’s internal equivalent capacitance which is calculated from the operating current consumption without load. (Refer to

Test Circuit). Average operating current can be obtained by the following equation. I

(opr) =CPD• VCC•fIN+ICC/n (percircuit)

CC

o

C

pF

3/7

Loading...

Loading...