SENSORY SC-601 Technical data

SC-601

Speech And Music Processor

Data sheet

© 2002 Sensory Inc.

P/N 80-0207-A

1

Features

Advanced, integrated speech synthesizer for

high-quality sound.

Operates up to 12.32 MHz (Performs up to 12

MIPS)

Single chip solution for up to 24 Minutes of

speech (using 1.57 Mb of onboard program +

data ROM)

Supports high-quality synthesis algorithms

Such as MX, CX, Simple CX, LX, ADPCM, and

Polyphonic Music

Simultaneous speech plus music capabilities

Very low-power operation, ideal for handheld

devices

Low-voltage operation, sustainable by three

batteries

Reduced power stand-by modes, less than 10

µA in deep-sleep mode

640-Word RAM

32 I/O Pins consisting of: 24 general purpose

bit configurable I/O, 8 inputs with programmable

pullup resistor and a dedicated interrupt (KeyScan)

Direct Speaker Driver, 32Ω (PDM)

One-bit comparator with edge-detection

interrupt service

Resistor-trimmed oscillator or 32.768kHz crystal

reference oscillator

Serial scan port for in-circuit emulation and

diagnostics

The SC-601 is sold in die form or 100-pin LQFP

package.

An emulator device is available in a ceramic

package for development (SC-614-P).

Description

The SC-601 is a low-cost, mixed-signal

processor that combines a speech synthesizer,

general-I/O, onboard ROM, and direct speaker

drive in a single package. The computational

unit utilizes a powerful DSP which gives the SC601 unprecedented speed and computational

flexibility compared with previous devices of its

type. The SC-601 supports a variety of speech

and audio coding algorithms, providing range of

options for speech duration and sound quality.

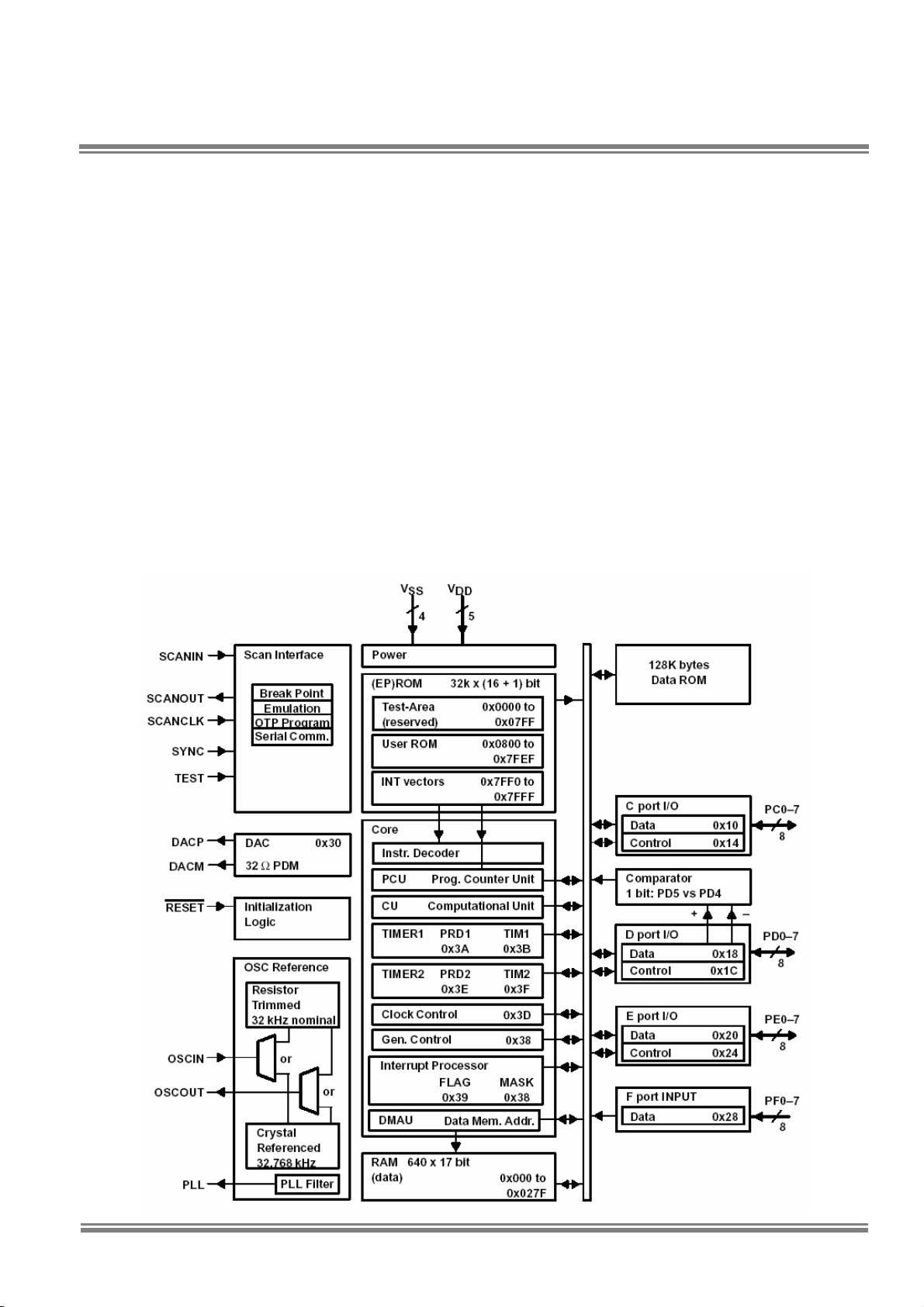

The device consists of a micro-DSP core,

embedded program, and data memory, and a

self-contained generation system. Generalpurpose periphery is comprised of 32 bits of partially configurable I/O.

The core processor is a general-purpose 16-bit microcontroller with DSP capability. The basic core includes

computational unit (CU), data address unit, program address unit, two timers, eight level interrupt processor,

and several system and control registers. The core processor gives the SC-601 break-capability in emulation.

The processor is Harvard type for efficient DSP algorithm execution. It requires separate program and memory

blocks to permit simultaneous access. The ROM has a protection scheme to prevent third-party pirating. It is

configured in 32K 17-bit words.

The total ROM space is divided into three areas:

1. The lower 2K words are reserved by Sensory a built-in self-test

2. The upper 30K words are for user program/data

3. An additional 1 Mb data ROM provides for up to 24 minutes of speech.

SC-601 Block Diagram

16-Bit

Microprocessor

640-words

RAM

192 KBytes

ROM

TIMER 1

TIMER 2

PLLM

10-Bit

DAC

32 I/O

COMPARATOR

查询SC601-R供应商

SC-601

Data sheet

2

P/N 80-0207-A

© 2002 Sensory Inc.

The data memory is internal static RAM. The RAM is configured in 640 17-bit words. All memories are designed

to consume minimum power at a given system clock and algorithm acquisition frequency.

A flexible clock generation system enables the software to control the clock over a wide frequency range. The

implementation uses a phase-locked loop (PLL) circuit that drives the processor clock at a selectable frequency

between the minimum and maximum achievable. Selectable frequencies for the processor clock are spaced

apart in 65.536 kHz steps. The PLL clock-reference is also selectable; either a resistor-trimmed oscillator or a

crystal-referenced oscillator may be used. Internal and external clock sources are controlled separately to

provide different levels of power management.

The periphery consists of three 8-bit wide general-purpose I/O ports and one 8-bit wide dedicated input port.

The bidirectional I/O can be configured under software control as either high-impedance inputs or as totem-pole

outputs. They are controlled via addressable I/O registers. The input-only port has a programmable pullup

option (70-kΩ minimum resistance) and a dedicated service interrupt. These features make the input port

especially useful as a key-scan interface.

A simple one-bit comparator is also included in the periphery. The comparator is enabled by a control register,

and its pin access is shared with two pins in one of the general-purpose I/O ports. Rounding out the SC-601

periphery is a built-in pulse-density-modulated DAC (digital-to-analog converter) with direct speaker-drive

capability. The functional block diagram gives an overview of the SC-601 functionality.

Functional Block Diagram

Data Sheet

SC-601

© 2002 Sensory Inc.

P/N 80-0207-A

3

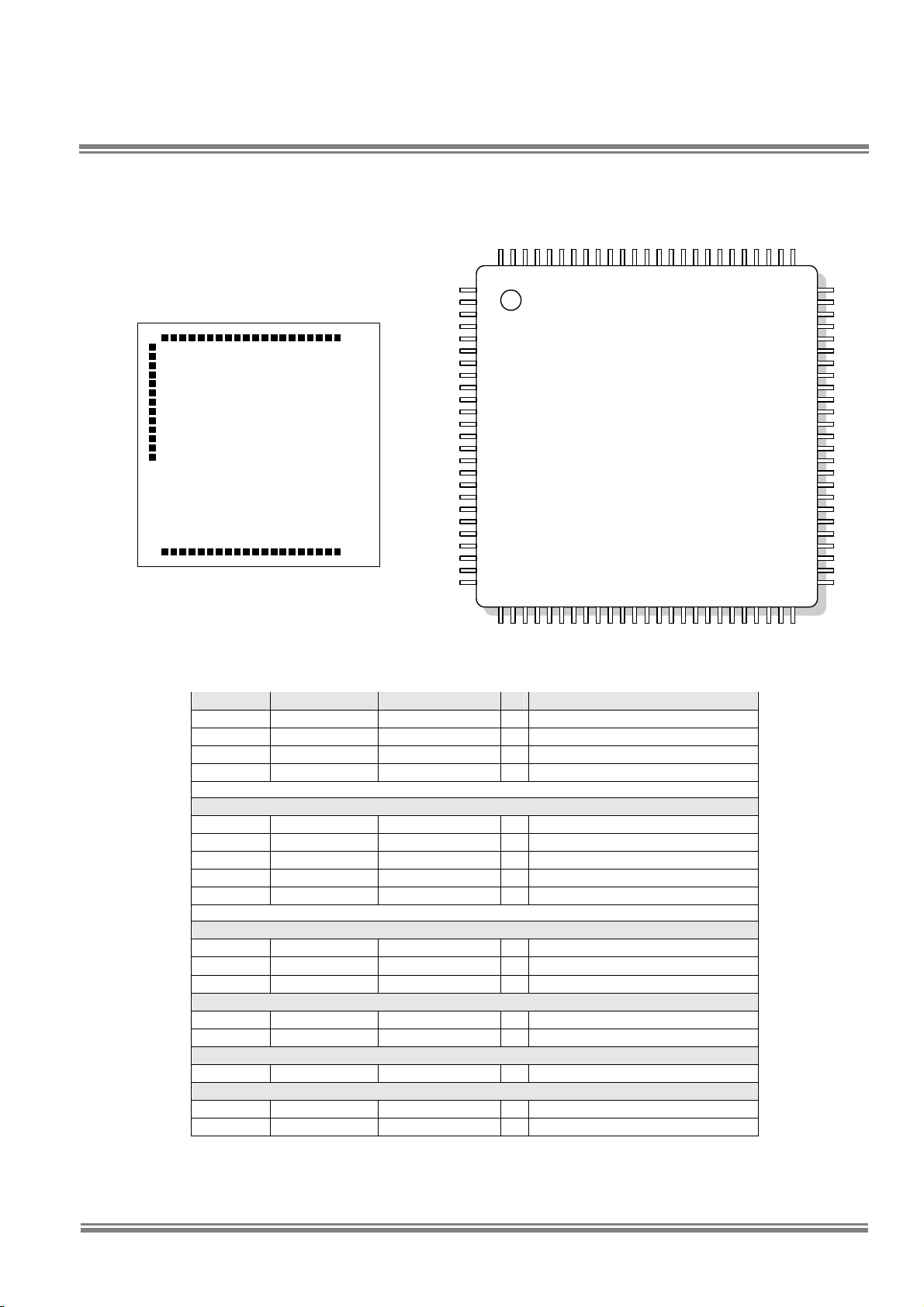

Pin/Pad Assignment

SC-601

(top view of the die)

19

20

32

33

52

1

SC-601

(100-lead LQFP)

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

75

74

73

72

71

70

69

68

67

66

65

60

59

58

57

56

NC

NC

NC

55

54

53

NC64

NC

NC

NC

63

62

61

NC52

NC51

26272829303132

33

4142434445

NCNCNCNCNC

VDD

VDD

SCANOUT

PE5

PE4

PE3

PE2

PE1

34353637383940

TEST

SYNC

SYNCLK

SCANIN

RESET_

PE7

PE6

4647484950

PE0

PLL

OSCIN

OSCOUT

VSS

100

9998979695949392919089

81

VSS

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

VDD

VSS

PC0

NC

88878685848382

PC1

PC2

PC3

PC4

PC5

PC6

PC7

8079787776

NCNCNCNCNC

NC

NC

NC

NC

DACM

VDD

DAVP

VDD

PF7

PF6

PF5

PF4

NC

1

2

3

4

5

6

7

8

9

10

11

12

20

PF3

PF2

PF1

PF0

VSS

NC

NC

13

14

15

16

17

18

19

NC

NC

NC

NC

NC

21

22

23

24

25

NAME PIN NO. PAD NO. I/O DESCRIPTION

PC0 – PC7 89 → 82 8 → 1 I/O Port C general-purpose I/O (1 Byte)

PD0 – PD7 99 → 92 18 → 11 I/O Port D general-purpose I/O (1 Byte)

PE0 – PE7 46 → 39 48 → 41 I/O Port E general-purpose I/O (1 Byte)

PF0 – PF7 16 → 9 31 → 24 I/O Port F general-purpose I/O (1 Byte)

Pins PD4 and PD4 may be dedicated to the comparator function, if the comparator enable bit is set.

Scan Port Control Signals

SCANIN 37 39 I Scan port data input

SCANOUT 33 35 O Scan port data output

SCANCLK 36 38 I Scan port clock

SYNC 35 37 I Scan port synchronization

TEST 34 36 I SC-601: test modes

The scan port pins must be bonded out on any SC-601 production board.

Reference Oscillator Signals

OSCOUT 49 51 O Resistor/crystal reference out

OSCIN 48 50 I Resistor/crystal reference in

PLL 47 49 O Phase-lock-loop filter

Digital-to-Analog Sound Output (DAC)

DACP 7 22 O Digital-to-analog plus output (+)

DACM 5 20 O Digital-to-analog minus output (–)

Initialization

RESET_ 38 40 I Initialization

Power Signals

VSS 17, 50, 90, 100† 32, 52, 9, 19† - Ground

VDD 6

†

, 8, 31, 32, 91 21†, 23, 33, 34, 10 - Processor power (+)

† The V

SS

and VDD connections service the DAC circuitry. Their pins tend to sustain a higher current draw. A dedicated decoupling capacitor

across these pins is therefore required.

Loading...

Loading...