HRM-TDC

USER MANUAL

High Resolution Time-to-Digital Converter Module

Document Overview

This document provides the user with a comprehensive

description of the hardware and software of the HRMTDC module, including system description, the various

timing modes, software GUI and DLL drivers. The

document is split up into the following sections:

GETTING STARTED

This section provides instructions for unpacking the HRM-TDC and a brief overview.

SYSTEM DESCRIPTION

This section gives a description of the system hardware, the various ports and communication channels, the internal

processor, and the specic timing features.

SENSL INTEGRATED ENVIRONMENT (SIE)

The SIE is a user interface for setting up and controlling the HRM-TDC module. While the interface provides an

extensive range of operating modes and measurement processes, including graphical presentation, it does not fully

cover all features available in the HRM-TDC module. This section of the User Manual includes instructions for the

installation of the necessary software, and detailed description of each part of the SIE and how to set up and use it.

APPENDIX

The HRM-TDC DLL provides a set of functions that will allow full control of the HRM-TDC for all features. For

complex experiments that require control beyond the scope of the SIE, it is expected that the user will write their own

real-time application utilizing the various functions in this DLL. The Appendix of the User Manual covers Registers,

low level DLL functions, high level DLL functions, DLL error reporting and examples, as well as help and examples

for resolving time-tag values,an explanation of the correlation function used and the Labview drivers provided.

SensL © 2011

1

HRM-TDC

USER MANUAL

> Contents > Getting Started

Contents

Document Overview .................................................................................................................................. 1

Glossary ..................................................................................................................................................... 5

Getting Started .......................................................................................................................................... 6

Contact & Support ................................................................................................................................. 6

Unpacking the System and Preparing for Use ........................................................................................ 6

Safety Considerations ............................................................................................................................ 6

System Installation Procedures .............................................................................................................. 6

Signal Inputs and Outputs ..................................................................................................................... 8

I/O Port Connector Pin Allocation .......................................................................................................... 8

HRM-TDC System Description ................................................................................................................. 9

Block Diagram ....................................................................................................................................... 9

Memory ........................................................................................................................................ 9

Time-to-Digital Converter Module ................................................................................................. 9

High Speed USB 2.0 Interface ...................................................................................................... 9

16-Bit General Purpose I/O Port ................................................................................................... 10

System Processor and Controller .................................................................................................. 10

System Processor and Controller Detailed Description ........................................................................... 10

Command Interpreter.................................................................................................................... 10

DMA to USB Fast Transfer Interface .............................................................................................. 11

Time-Bin and Time-Tag Controller ................................................................................................. 11

Data Router Module ...................................................................................................................... 11

Address Router Module ................................................................................................................ 11

Dual Port Memory Arbiter ............................................................................................................. 11

HRM-TDC Specic Feature Overview .................................................................................................... 12

HISTOGRAM ................................................................................................................................ 13

FIFO ............................................................................................................................................. 13

Histogram – Single-stop (“TCSPC” MODE) ............................................................................................ 14

Histogram – Multi-stop (“Multiscaler/Counter”) ....................................................................................... 15

SensL © 2011

SensL © 2011

2

2

HRM-TDC

USER MANUAL

> Contents > Getting Started

FIFO – Single-stop (“TCSPC - with Macro-Time”) ................................................................................... 16

FIFO – Multi-stop (“FIFO - Time Tagging”) .............................................................................................. 17

SensL Integrated Environment (SIE) ........................................................................................................ 18

System Requirements ............................................................................................................................ 18

Installation ............................................................................................................................................. 18

Using the SensL Integrated Environment (SIE) ....................................................................................... 19

Main Page .................................................................................................................................... 19

Module Information ....................................................................................................................... 19

“HISTOGRAM –TCSPC” (Histogram Single-stop) .......................................................................... 20

“HISTOGRAM – Multi-scaler” (Histogram Multi-stop) .................................................................... 22

“FIFO – TCSPC with MACRO time” (FIFO Single-stop) .................................................................. 23

“FIFO – Time Tagging” (FIFO – Multi-stop) ..................................................................................... 26

Correlation .................................................................................................................................... 30

Appendix ................................................................................................................................................... 32

HRM-TDC Registers and Low Level DLL Functions ............................................................................... 32

Initialization Low Level Drivers ....................................................................................................... 32

ARR – Address Route Register ..................................................................................................... 33

DRR – Data Route Register ........................................................................................................... 35

LAL, LAH – Load Address LO/HI Register ..................................................................................... 36

LFL, LFH – Load Fill Value LO/HI Register ..................................................................................... 37

UAL, UAH – Load Address LO/HI Register ................................................................................... 37

MBR – Mode Bits Register ............................................................................................................ 38

ESR – Edge Sensitivity Register .................................................................................................... 39

RRR – Routing Reset Register ....................................................................................................... 40

MCL, MCH – Memory Count LO/HI Register ................................................................................ 40

FSR – Frequency Select Register .................................................................................................. 41

IDR – I/O Direction Register .......................................................................................................... 41

IVR – I/O Value Register ................................................................................................................ 41

BCL, BCH – Bin Count LO/HI Register ......................................................................................... 42

UCL, UCH – USB Count HI/LO Register ....................................................................................... 42

SensL © 2011

SensL © 2011

3

3

HRM-TDC

USER MANUAL

> Contents > Getting Started

HRS, HRM-TDC Status Register ................................................................................................... 43

PCR – Product Code Register ...................................................................................................... 44

SRR – Software Revision Register ................................................................................................. 44

MIR – Module ID 1, 2, 3, 4 Register .............................................................................................. 44

WCH – Write Count HI Register .................................................................................................... 45

WCL – Write Count LO Register .................................................................................................... 45

Non-Register Specic Low Level Drivers ....................................................................................... 46

High Level DLL Functions ...................................................................................................................... 48

DLL Error Reporting ............................................................................................................................... 56

DLL Application Examples ..................................................................................................................... 57

Resolving Free Running FIFO Time-Tag Values ...................................................................................... 66

Free Running Algorithm Explained ................................................................................................. 66

Resync Algorithm Explained .......................................................................................................... 68

Correlation Function Algorithm ............................................................................................................... 70

Labview Driver details ............................................................................................................................ 71

HRM-TDC LabView Driver VI List .................................................................................................. 71

Sample LabView Application ......................................................................................................... 84

SensL © 2011

SensL © 2011

4

4

HRM-TDC

USER MANUAL

> Glossary > Getting Started

Glossary

Here are words and phrases used in this user manual in relation to the HRM-TDC module.

SIE - SensL Integrated Environment - the GUI that runs on the SensL DLL and provides an example

program allowing the user to make measurements with the HRM-TDC.

LSB - Least Signicant Bit: The right most bit in a binary integer, and in the case of the HRM-TDC

it determines the minimum timing resolution possible.

Histogram - The use of consecutive memory locations to store counts that represent points on a graph.

Each memory location represents a time range that can be specied via software, down to

the LSB value of the HRM-TDC (27ps).

FIFO - First In, First Out: in the HRM-TDC, timing data can be stored in memory before being

downloaded to the PC. FIFO is analogous to putting the data into a queue in memory,

whereby the rst loaded in, will also be the rst downloaded to the PC.

TCSPC - Time Correlated Single Photon Counting: A technique used to study properties of molecules

by exciting with a laser source and measuring the subsequent relaxation time through the

acquisition of lifetime curves.

Time bin - The time interval covered by one memory location in one of the HRM-TDC’s Histogram

modes.

Time Tag - The timing value recorded between a START of a STOP signal, in one of the HRM-TDC’s

FIFO modes.

Curve - The data resulting from one of the HRM-TDCs histogramming modes.

Micro time - The timing value between a START signal and any given STOP signal in FIFO single-stop

(TCSPC) mode. In the FIFO multi-stop (time-tagging) mode, it refers to the value of the highresolution TDC when the event occured.

Macro time - The time elapsed since the experiment began in FIFO single-stop (TCSPC) mode. In FIFO

multi-stop (time-tagging) mode, it refers to the the coarse timer that, used in conjunction with

the micro-time, allows the user to determine the absolute time of the event.

SensL © 2011

SensL © 2011

5

5

HRM-TDC

USER MANUAL

> Getting Started > Contact & Support

Getting Started

CONTACT & SUPPORT

For all enquiries, please email: support@sensl.com

Supporting documentation can be found on the SensL website at www.sensl.com/documentation/

Downloadable copies of the SensL HRM-TDC software and release note can be found at

www.sensl.com/support/sw/

UNPACKING THE SYSTEM AND PREPARING FOR USE

Unpack the contents and identify each of the components.

• HRM-TDC Module

• Power Supply, with country specic connector

• USB cable

SAFETY CONSIDERATIONS

1. Only use the power supply supplied with the HRM-TDC module.

2. The power supply should be disconnected from the mains supply when the module is not in use.

3. The module is not intended for outdoor use

4. The power supply should not be opened nor should the module covers be removed at any time as there

are no user adjustable components or settings, except via the SensL Integrated Environment Software.

5. Liquids should not be spilled on or into the module.

SYSTEM INSTALLATION PROCEDURES

For software driver and SensL Integrated Environment installation instructions see the SIE User Guide on page 18

of this document.

Please follow the instructions carefully and ensure you have installed the QuickUSB drivers as instructed.

SensL © 2011

SensL © 2011

6

6

HRM-TDC

USER MANUAL

> Getting Started > System Installation Procedures

SYSTEM CHARACTERISTICS AND SPECIFICATIONS

Dimensions 164mm (L) x 96mm (W) x 34 mm (H)

Weight 680g

Power +5V @ 0.65 A

Temperature Operating: 0°C to +50°C

Storage: -20°C to +70°C

Specications

Number of channels per module 4

Time channels per curve 1 to 4,194,304

Number of curves in memory 1 to 4,194,304

Input voltage range LVTTL (5V TTL tolerant)

START/STOP channels input impedance 51kW

Minimum input pulse width 6ns

Minimum Time/Channel 27ps

Histogram/channel depth 65,535 or 4,294,967,295 bits (16 or 32 bits)

Dead time 190ns

Saturated count rate 4.5MHz

Usable count rate 9MHz *

Burst rate timing Up to 100MHz (Mode dependent)

Macro Timing resolution Down to 5ns

Memory size 8Mbytes

Memory format Dual ported linear or dual ported FIFO (mode

dependent)

Readout during operation Fully dual-ported memory (no stop start operation

required)

Multi detector operation Up to 4

Multi module operation Number depends on USB capability of PC

I/O control 16 fully programmable I/O ports

Software SensL Integrated Environment (SIE) and DLL

drivers

PC Interface High speed USB 2.0

* Useful count rate is maximum count rate without loss of greater than 50%

SensL © 2011

SensL © 2011

7

7

HRM-TDC

USER MANUAL

> Getting Started > Signal Inputs And Outputs

SIGNAL INPUTS AND OUTPUTS

L K

ABCD

JIEFGH

Figure 1 HRM-TDC ports and connectors labelled

A Channel 0 Start Input (SMA LVTTL*) B Channel 0 Stop Input (SMA LVTTL*)

C Channel 1 Start Input (SMA LVTTL*) D Channel 1 Stop Input (SMA LVTTL*)

E Channel 2 Start Input (SMA LVTTL*) F Channel 2 Stop Input (SMA LVTTL*)

G Channel 3 Start Input (SMA LVTTL*) H Channel 3 Stop Input (SMA LVTTL*)

I USB connector J LEMO power supply connector (for SensL PSU use only)

K 26-way I/O port connector L Programmable Clock output (SMA LVTTL 50W)

* 5V TTL tolerant

I/O PORT CONNECTOR PIN ALLOCATION

Pins 1 to 16: I/O ports 0 to 15 respectively

Pin 17: Test clock signal ENABLE (LO to disable test clocks)

Pin 18 to 22: Test clock signals (outputs)

Pin 23, 24: +5v

Pin 25, 26: Ground

SensL © 2011

SensL © 2011

8

8

HRM-TDC

Data

Control

Start 0

Stop 0

High Speed 2.0

USB Interface

Time to Digital

Converter Module

Time to Digital

Converter Module

Time to Digital

Converter Module

Time to Digital

Converter Module

Memory

(8 MB)

16-bit General

Purpose

I/O Port LVTTL

System Processor

and

Controller (FPGA)

Start 1

Stop 1

Start 2

Stop 2

Start 3

Stop 3

USER MANUAL

> Hrm-tdc System Description > Block Diagram

HRM-TDC System Description

BLOCK DIAGRAM

The HRM-TDC system consists of 4 ‘time-to-digital’ modules (each having a START and a STOP input), 16 I/O

ports, a high speed USB interface, memory storage and an FPGA based processor, as depicted in Fig. 2. The

purpose of each element is as follows:

Memory

The memory module is an HRM-TDC format plug-in mezzanine board providing 8 Mbytes of memory.

Time-to-Digital Converter Module

This module is the front end of the system and is responsible for resolving the timing between the START and STOP

inputs of each of up to four channels. Each channel is controlled by the FPGA and can be programmed to start and

stop on either LO-HI or HI-LO transitions.

Figure 2 An overview of the HRM-TDC operation

High Speed USB 2.0 Interface

The USB interface is used to command/congure the HRM-TDC as well as download, in real-time, timing data to the

host computer. This USB interface implements high speed USB 2.0 protocol allowing real time continuous logging

of timing data up to rates of 4.5MHz without data loss.

SensL © 2011

SensL © 2011

9

9

HRM-TDC

USER MANUAL

> Hrm-tdc System Description > System Processor And Controller Detailed Description

16-Bit General Purpose I/O Port

This general purpose I/O port is used to allow multi-dimensional curve readings. The position of curve data, within

the system memory, can be dened by these ports. These ports can be set directly by outside control lines (inputs)

or by software to drive outside equipment (outputs).

System Processor and Controller

The ‘System Processor/Controller’ is responsible for implementing all the functionality of the HRM-TDC module.

This module decodes commands from the USB and executes the timing function accordingly. All results are saved

in memory as either time-bins for curve measurements or time-tags for continuous recording. In this latter mode

the memory is congured as a large FIFO to allow continuous downloading of time-tag data up to rates of 4.5MHz.

SYSTEM PROCESSOR AND CONTROLLER DETAILED DESCRIPTION

Figure 3 Overview of the system processor and controller

Command Interpreter

This module is responsible for receiving a set of commands from the host computer and controlling the system

accordingly. HRM-TDC is a fully programmable system with a wide range of parameters that can be user dened.

The Command Interpreter is responsible for setting these parameters and starting the execution of a particular task.

SensL © 2011

SensL © 2011

10

10

HRM-TDC

USER MANUAL

> Hrm-tdc System Description > System Processor And Controller Detailed Description

DMA to USB Fast Transfer Interface

The system memory is dual ported between the USB and the Time-Bin/Time-Tag controller. This module controls

the reading of data from memory to the USB interface by means of high speed DMA block transfers. The Command

Interpreter initializes this module with a start address and block data count. When commanded to start, this module

interfaces with the Dual Port Memory Arbiter to read the pre-programmed data block. The rate of this process is

such that data can be transferred from the memory to the USB port as fast as required. This allows the USB 2.0 high

speed interface to operate at full speed without loss of data.

Time-Bin and Time-Tag Controller

This module is responsible for carrying out the particular Time-Tag or Time-Bin process as dened by the Command

Interpreter. This module communicates with the Timing Modules and saves the results of the measurements in the

dual ported memory. The format of these results is determined by the mode of operation. In time-bin mode, this

module will use the time information from the Timing Modules to determine the particular bin to be incremented. In

time-tag mode this module will treat the memory as a large FIFO, saving time-tag data in consecutive locations. The

format of the time-tag data is determined by the Data Router Module.

Data Router Module

The Data Router Module is a complex programmable multiplexer that allows any of a wide range of inputs to be

routed to any of the 32 memory data bits. In time-bin mode this module is bypassed to allow the Time-Bin and

Time-Tag Controller to directly access the memory for the purpose of incrementing time-bins. In Time-Tag mode this

module determines the format of the time-tag data. The Command Interpreter presets the routing of this module

to dene which bits of the time-tag are Time-Tag data (both Micro and Macro) from the Time-Bin and Time-Tag

Controller and I/O data from external equipments.

Address Router Module

The Address Router Module is a complex programmable multiplexer that allows any of a wide range of inputs, plus

an internal address counter, to be routed to any of the memory address lines. In time-tag mode this module will

normally be programmed to present the internal address counter bits as the memory address. The internal address

counter automatically increments after each memory write, creating a FIFO type interface. In time-bin mode the

Command Interpreter presets the routing of this module to a mix of the address counter, time-tag data and I/O data.

Routing the time-tag data to the address will create a range of consecutive bins separated by the time resolution of

the LSB. The address counter bits can be used to dene the base address of a particular curve whilst the I/O data

can be used by external equipments to move the curve for multi-dimensional measurements.

Dual Port Memory Arbiter

This module controls the data transfers to/from system memory to the USB and Time-Bin/Time-Tag Controller. Each

port presents an address, direction (R/W) and request signal. This module detects the particular request, carries out

the memory access and directs the data to/from the requesting port at the requested address.

SensL © 2011

SensL © 2011

11

11

HRM-TDC

USER MANUAL

> Hrm-tdc System Description > Hrm-tdc Specic Feature Overview

HRM-TDC TYPICAL APPLICATION

Figure 4 Example application using the HRM-TDC

Note: Figure 4 shows a typical application setup utilizing a wide range of the HRM-TDC features. In this example the

experiment is a TCSPC application where a LASER is stimulated by a clock and the time before a photon is detected

is measured. The LASER is continually pulsed at a xed frequency (typically 50MHz). The LASER output will affect a

setup resulting in a photon arriving at the APD Detector such as the SensL PCDMiniSL. It is assumed that the rate

of photons arriving at the APD is far less than the rate of the LASER pulses. As a photon is not guaranteed for each

cycle of the LASER, the system will use the photon event as the start of the TCSPC process and a delayed version

of the LASER pulse as the stop signal. This technique avoids countless dead cycles and simplies the associated

electronics required for recording the events.

The HRM-TDC module measures and records the time delay between clock and photon from the experiment and

uploads the results, in real time, to the host computer via the USB interface. In some cases the experiment will

involve multiple TCSPC curve measurements as the experiment changes the settings of external equipment. The

programmable I/O of the HRM-TDC module is used to cater for such applications. The external equipment, such

as a microscope, can indicate its X,Y movement to the HRM-TDC module allowing multiple curves to be measured.

Alternatively, the HRM-TDC module can be programmed as outputs to control the external equipment and cause

the actual X,Y positioning of the equipment.

HRM-TDC SPECIFIC FEATURE OVERVIEW

The exibility of the HRM-TDC allows it to be used in a variety of modes. The following are examples of how the SIE

software utilizes the START and STOP signals in different ways to cater for different applications.

SensL © 2011

SensL © 2011

12

12

HRM-TDC

USER MANUAL

> Hrm-tdc System Description > Hrm-tdc Specic Feature Overview

HISTOGRAM

Histogram modes use consecutive memory locations to store counts that represent points on a graph. These

memory locations or time bins are incremented based on the value of a time measurement. Each memory location

represents a time range equal to the resolution of the timer. Within the HISTOGRAM category there are two distinct

modes of operation, single-stop and multi-stop.

Single-stop histogram

Following a START event, the rst stop event is measured and the corresponding time bin is incremented. This is

repeated to build up a histogram (curve) in memory showing the distribution of 1st events following a start input.

This mode is also referred to as “TCSPC” mode due to its application in Time Correlated Single Photon Counting.

Multi-stop histogram

Following a START event, all stop events are measured and their corresponding time bins incremented. The next

START input will reset the timer and the following events processed again. This is repeated to build up a histogram

in memory showing the distribution of STOP events following a START input. This mode is also referred to as

“Multiscaler/Counter” mode.

FIFO

FIFO modes continually record the timing of events and save the results in consecutive locations in memory. When

the last location in memory is lled, if not commanded to stop, the module continues to record data starting at the

beginning of memory again. The host PC, via the USB interface, keeps up in time with the module, reading the data

from memory to a le in the host computer. Hence the memory can be regarded as a very large FIFO. Providing the

host PC can keep up with the module, timing data can be recorded indenitely. Within the FIFO category there are

two distinct modes of operation, single-stop and multi-stop.

Single-stop FIFO

In this mode the module carries out the single-stop histogram process as described previously. However, along with

the single-stop measurement, the information stored in the FIFO also has a MACRO time that denes what time

during the experiment the timing measurement was made. This mode is also referred to as “TCSPC with Macro

time”.

Multi-stop FIFO

This mode is also referred to as “FIFO time tagging” and offers 2 options:

Free Running:

Using this option the process is started with a single start pulse. The module will then ll the memory with time

tags dening the time of each stop event with relation to the initial single start pulse. Any further Start inputs will

be ignored.

Resync:

This option uses a 250KHz clock output from the module as the Start input. The clock continuously resynchronizes the module to eliminate long term drift between channels. This is the preferred method when it is

required to compare the data from more than one channel.

SensL © 2011

SensL © 2011

13

13

HRM-TDC

Fig.1c

USER MANUAL

> Hrm-tdc System Description > Histogram – Single-stop (“tcspc” Mode)

HISTOGRAM – SINGLE-STOP (“TCSPC” MODE)

a)

b)

c)

d)

Figure 5

Histogram modes use consecutive memory locations to store counts that represent successive timing values (Fig.5a).

These memory locations or “time bins” are incremented based on the result of a time measurement between a

START and the rst STOP received. In this single-stop mode, this is repeated to build up a histogram in memory

showing the distribution of rst events (STOPs) following a START input. This process is illustrated in Fig.5b and

Fig.5c, and an example GUI data plot is shown in Fig.5d. Data is saved to the PC in .CSV format. This mode is also

referred to as ‘TCSPC’ in the SIE, due to its application in Time Correlated Single Photon Counting.

Note: In this mode the START of each channel will be the event and the STOP will be a delayed version of the

LASER clock. On receipt of an event the timing value will be read and then the timing module will immediately be

reset. The reset will clear the channel ready for the next event. Each time-stamp from the timing module will be used

as an address to increment a memory location (time-bin). The resolution of the bins and the position of the curve in

memory will be dened by the highly exible Address Routing Module. The timing value, address counter and I/O

bits can all be routed to the memory address lines. This exibility allows many options, from a simple single curve to

multiple curves dened by the address counter and external control from the I/O port.

Min Time Bin Size: 27ps

Max Time Bin Size: 143ms

Max No. Time Bins: 4,194,304

Time Bin Depth: 65,536 or 4,294,967,296

Max Count Rate: 4.5Mcps

Max Image Size: 2048 x 4096

SensL © 2011

SensL © 2011

14

14

HRM-TDC

Fig.2b

USER MANUAL

> Hrm-tdc System Description > Histogram – Multi-stop (“multiscaler/counter”)

HISTOGRAM – MULTI-STOP (“MULTISCALER/COUNTER”)

a)

b)

c)

Figure 6

In this mode, multiple STOP events following a single START event are recorded and their corresponding time bins in

the histogram incremented (Fig.6a). The following START input will reset the timer and the following STOP events will

be again recorded until another START is received. The process is illustrated in Fig.6b and Fig.6c. This is repeated to

build up a histogram in memory. Data is saved in .CSV format. The GUI will display a plot similar to that in Fig.5d. This

mode is also referred to as “Multiscaler/Counter” in the SIE. Please note that FIFO is not employed in this mode.

The Td (dead time) parameter is applicable in histogram multi-stop mode and limits the maximum frequency

achievable. Tm is the minimum time between any start and a subsequent stop.

Note: In this mode the START signal is a low frequency clock (less than 7 MHz). The STOP signals will be the events.

Unlike the single-stop mode, the 27ps timing module is not reset after the rst event. Due to the long clock period it

will be possible for the same channel to receive a number of events per clock cycle. Hence, in this mode the time-

bins will ll up to plot the occurrence of events over the period of the clock cycle. Each new START signal will reset

the 27ps timing module. This allows the system to build up a plot of all the events within the START pulse cycle.

Once again the exibility of the Address Routing Register provides a wide range of options from single to multiple

curves.

Min Time Bin Size: 27ps

Max Time Bin Size: 143ms

Max No. Time Bins: 4,194,304

Time Bin Depth: 65,536 or 4,294,967,296

Max Count Rate: 4.5Mcps

Max Image Size: 2048 x 4096

SensL © 2011

SensL © 2011

15

15

HRM-TDC

Fig.3c

Fig.3d

USER MANUAL

> Hrm-tdc System Description > Fifo – Single-stop (“tcspc - With Macro-time”)

FIFO – SINGLE-STOP (“TCSPC - WITH MACRO-TIME”)

a)

c) d)

b)

Figure 7

FIFO modes continually record the timing of events and save the results in consecutive locations in memory as

shown in Fig.7a. When the last location in memory is lled, if not commanded to STOP, the module continues to

record data starting at the beginning of memory again. The host PC, via the USB interface, keeps up in time with the

module, reading the data from memory to a le in the host computer. Hence the memory can be regarded as a very

large FIFO. Providing the host PC can keep up with the module, timing data can be recorded indenitely.

In this mode the module carries out the Single-STOP process as described previously and illustrated in Fig.7b and

Fig.7c. However, along with the timing of the Single-STOP event, a MACRO time (the time during the experiment that

this measurement is made) is also recorded. Both times are recorded in the FIFO. An example of the data recorded

is shown in Fig.5d. Data is saved in .CSV format. This mode is also referred to as ‘TCSPC (with Macro Time)’ in

the SIE, due to its application in Time Correlated Single Photon Counting.

Note: In this mode the START of each channel will be the event and the STOP will be a delayed version of the LASER

clock. On receipt of an event the timing value will be read and the MICRO time will be immediately reset. The reset

will clear the channel ready for the next event. All subsequent STOP pulses will be ignored until a new START pulse

arrives. Each time-stamp will be a 32-bit word giving the time since the last START (MICRO-time Tt1 or Tt2 in Fig.7c)

and the value of a free running clock dening the time within the experiment (MACRO-time Tc). Due to the highly

exible Data Routing Module the resolution and number of bits for the micro time, macro time and channel ID bits is

selectable using the USB selection registers. When this process begins, 32-bit timing values will be inserted into the

shared memory. The memory will be congured as a large FIFO interfacing to the USB interface. Suitable handshake

signals are implemented allowing continuous transfer of time-tags from the FIFO to the PC via the USB port. With

counts of up to 4.5MHz this process can run indenitely without loss of data.

SensL © 2011

SensL © 2011

16

16

HRM-TDC

Fig.4b

Fig.4c

USER MANUAL

> Hrm-tdc System Description > Fifo – Multi-stop (“fo - Time Tagging”)

FIFO – MULTI-STOP (“FIFO - TIME TAGGING”)

a)

c)

b)

Figure 8

In this mode the process is started with a single START pulse. The module will then ll the memory with time tags

dening the time of each STOP event with relation to the initial single START pulse. Any further START inputs will be

ignored. This mode is illustrated in Fig.8a and Fig.8c and is also referred to as ‘Time Tagging’. Data is saved as a

.CSV le. A typical data le is shown in Fig.8b.

There is a further ‘Re-Sync’ option within this mode that uses a 250KHz clock output from the module as the START

input. The clock continuously re-synchronizes the module to eliminate long term drift between channels. This is the

preferred method when it is required to compare the data from more than one channel.

Note: In this mode all STOP events will be time-stamped and saved to memory. Each time-tag will be comprised

of two 32-bit words. These two words will provide timing value, with a resolution of 27ps, and the channel ID.

The memory will be congured as a large FIFO interfacing to the USB interface. Suitable handshake signals are

implemented allowing continuous transfer of these time-tags from the FIFO to the PC via the USB port. Hence, in

this mode, continuous time tagging to the host PC can be achieved indenitely.

SensL © 2011

SensL © 2011

17

17

HRM-TDC

USER MANUAL

> Sensl Integrated Environment (sie) > System Requirements

SensL Integrated Environment (SIE)

The SIE is a user interface for setting up and controlling the HRM-TDC module. While the interface provides an

extensive range of operating modes and measurement processes, including graphical presentation, it does not fully

cover all features available in the HRM-TDC module.

The SIE communicates with the module via a low level DLL. This DLL has been designed to provide a set of functions

that will allow full control of the HRM-TDC for all features. For complex experiments that require control beyond the

scope of the SIE, it is expected that the user will write their own real-time application utilizing the various function in

this DLL. For details of the DLL functions, see the Appendix in this document.

SYSTEM REQUIREMENTS

• Windows XP SP2 operating system

• 1 GByte of RAM

• At least one spare High Speed USB 2.0 port

• .NET Framework installed (included)

• JAVA runtime environment installed (included)

• Microsoft Visual C++ runtime components (included)

INSTALLATION

To install the TDC software and USB drivers, follow these steps:

• Go to www.sensl.com/support/sw/ and download both the ‘Release Note’ PDF and the ‘HRM-TDC

Software’ EXE les.

• Run the HRM-TDC_Install_XpXX.exe (where the XpXX is the revision number) le and follow the

instructions. After the GUI and DLLs are installed, you will be prompted to install QuickUSB drivers which

are necessary for communication with the TDC.

• Now power up the HRM-TDC module and connect the USB cable.

• The PC will recognize that new hardware has been added. Depending on the operating system the drivers

may be located automatically, or it may be necessary to select them manually by directing the PC to the

directory c:\Program Files\SensL\HRM-TDC\QuickUSB* where the necessary le will be located.

• The PC is ready to launch the TDC software. It can be found in the directory C:\Program Files\SensL\

HRM-TDC *

* This assumes you have used the default directory settings for your installation.

SensL © 2011

SensL © 2011

18

18

HRM-TDC

USER MANUAL

> Sensl Integrated Environment (sie) > Using The Sensl Integrated Environment (sie)

USING THE SENSL INTEGRATED ENVIRONMENT (SIE)

Main Page

When the SIE software is launched it will search the USB for available HRM-TDC modules and initialize them ready

for use. Once this has been carried out the main SIE page will appear as shown in Figure 9. A list of available devices

will be shown. To inspect and select the various operating modes available, right click on the module name and then

select the particular mode you require (see Fig. 9).

Figure 9 SIE Main Page screen

Module Information

This page displays the conguration information unique to this module. This information includes the module ID

number and the various measurement modes. This page also allows the user to upgrade the internal FPGA image.

To upgrade the FPGA image the user must rst click on the Update FPGA button. This will launch the Update Wizard

as shown in Figure 10. Use the Browse button to nd the RPD le for upgrading. Finally click the Update Device

button to start the upgrade.

WARNING:

USB communication must be maintained during this process. Do NOT disconnect the USB cable during the update.

SensL © 2011

SensL © 2011

19

19

HRM-TDC

USER MANUAL

> Sensl Integrated Environment (sie) > Using The Sensl Integrated Environment (sie)

Updating the FPGA should only be carried out if you are instructed to do so by SensL. This procedure requires a

valid RPD le as provided by SensL.

Failure to carry out this process correctly may render the module inoperable resulting in the need to return it to SensL

for reconguration.

Figure 10 SIE Module Information screen

“HISTOGRAM –TCSPC” (Histogram Single-stop)

When this page is launched the top half will display a graph page. Left click on this graph to reveal the conguration

settings. The size of the conguration and graph area can be adjusted by dragging the partition to suite. Figure 11

show this page with the partition adjusted to reveal the entire conguration controls.

Programmable Clock Output

The Programmable Clock Output is made available for all modes and is used to set the frequency and duty cycle of

the internal programmable clock. This clock is available at an SMA output for test purposes. This clock is provided

for testing and diagnostics. The clock will exhibit a level of jitter that would not be suitable for accurate measurements

as part of an experiment.

External Clock Period

This should be set to the period of the external LASER clock.

SensL © 2011

SensL © 2011

20

20

HRM-TDC

USER MANUAL

> Sensl Integrated Environment (sie) > Using The Sensl Integrated Environment (sie)

Reverse Plot

Due to the method of TCSPC measurement, where the start and stop events are reversed, it is sometimes useful to

plot the curves with the TIME axis reversed. Selecting this option will reverse the time axis for the plot.

Show Time Bins as Bars

Selecting this option will result in the graphical output being displayed as histogram bars rather than as a single best

t line as shown in Fig 11.

Microtime LSB

The smallest bin width is 27ps. In some cases it may not be necessary to be this accurate. Selecting the LSB of the

microtime denes the bin resolution. Bit 0 is the highest resolution of 27ps. Bit 1 will set the bin width to 54ps (2 x

27) bit 2 will set the bin width to 108ps (4 x 27) and so forth.

The choice of bin width is application specic. Should the experiment not require such accuracy it may be better

to select a lower resolution than 27ps. This will give the added advantage of allowing a wider time range over the

available memory and/or more room for multiple curves.

Channel Enable and Edge Selection

These check boxes allow the individual channels to be enabled/disabled and the sensitivity of the START/STOP

inputs to be specied.

Note: Press the Apply changes button to set your selected conguration.

Figure 11 SIE Histogram TCSPC screen

SensL © 2011

SensL © 2011

21

21

HRM-TDC

USER MANUAL

> Sensl Integrated Environment (sie) > Using The Sensl Integrated Environment (sie)

Graphical Presentation

Once the conguration is selected, the conguration page can be removed by clicking on the X tab to display the

graph section only (see Figure 12).

To start processing, click on the green right arrow at the top of the page. This can be done numerous times to

display multiple traces on the same graph. Fig 11 shows the result of a simple TCSPC experiment. The right hand

side of the display shows the traces. In this case two traces are displayed both from channel0. These traces can be

saved to le or cleared by selecting them with the relevant checkbox and using the save and clear buttons.

Once the processing has been stopped, the graph can be analyzed.

To zoom in, hold right mouse button down and size selection box over area of interest.

To zoom out, sweep mouse from right to left with right mouse button held down.

To measure between points, click on the graph with right button and left button to position the two cursors. The

position of these two cursors and their X and Y differences will be displayed at the top of the graph (see Fig 12).

Figure 12 SIE Histogram - TCSPC, graph section only

“HISTOGRAM – Multi-scaler” (Histogram Multi-stop)

When in this mode the conguration setup and operation is identical to the HISTOGRAM-TCSPC mode. In TCSPC

mode the system repeatedly plots the time of the rst event after a LASER pulse. In Multi-scaler/Counter mode the

operation is very different. The start event is a slow clock of less than 7MHz. The system records and saves all stop

SensL © 2011

SensL © 2011

22

22

HRM-TDC

USER MANUAL

> Sensl Integrated Environment (sie) > Using The Sensl Integrated Environment (sie)

events in their respective time bins. Each start event will reset the timer and a new set of stop events will be added

to the existing array of time bins. This process will result in a histogram being built up of all the events following the

start. This is particularly useful for plotting pulse shapes, decay curves etc.

“FIFO – TCSPC with MACRO time” (FIFO Single-stop)

When this page is launched the top half will display a graph page. Left click on this graph to reveal the conguration

settings. The size of the conguration and graph area can be adjusted by dragging the partition to suite.

This page is a graphical demonstration of the TCSPC with MACRO time feature of the HRM-TDC module. The HRMTDC allows the user to carry out TCSPC and save time tags. These time tags consist of the TCSPC measurement

plus a MACRO time dening at what time during the experiment the measurement was made. For normal operation,

this feature would use data streaming that would allow the user to continually record time-tags indenitely to a PC

le. This mode of the SIE records for a given period or until the HRM-TDC memory is full.

Programmable Clock Output

The Programmable Clock Output is made available for all modes and is used to set the frequency and duty cycle of

the internal programmable clock. This clock is available at an SMA output for test purposes. This clock is provided

mainly for testing and diagnostics. The clock will exhibit a level of jitter that would not be suitable for accurate

measurements as part of an experiment.

Recording Length

The recording length should be set to the desired period over which the TCSPC measurements are to be taken.

Note that the processing will stop prematurely if the Maximum Event Count is reached.

Maximum Event Count

This denes the maximum number of events to be stored before recording stops. This value is used to ensure the

storage data size does not exceed the capacity of the system.

External Clock Period

This should be set to the period of the external LASER clock.

Reverse Plot

Due to the method of TCSPC measurement, where the start and stop events are reversed, it is sometimes useful to

plot the curves with the TIME axis reversed. Selecting this option will reverse the time axis for the plot.

Macro and Micro Time Conguration Selection

These elds allow the user to select the number of MACRO and MICRO bits and resolution to appear in the 32-bit

time tag word. As bit counts and resolution are changed the resulting roll over times and resolution values will be

automatically displayed in the boxes to the right hand side. If the user attempts to input an illegal value the relevant

text boxes will turn red.

SensL © 2011

SensL © 2011

23

23

HRM-TDC

USER MANUAL

> Sensl Integrated Environment (sie) > Using The Sensl Integrated Environment (sie)

Channel Enable and Edge Selection

These check boxes allow the individual channels to be enabled/disabled and the START/STOP inputs sensitivity to

be specied.

Note: Press Apply changes button to set your selected conguration.

Data Recording

Once the conguration is selected, the mode is now ready for recoding data. In FIFO – TCSPC mode two forms of

data recording are available, Graphical Presentation and Streaming TCSPC Time Tags.

Graphical Presentation

In this mode recording is carried out at the module until the recording length or the maximum event count is

reached. To start processing, click on the green right arrow at the top of the page. Figure 13 shows the result

of a simple experiment. The right hand side of the display will show which channels are active. In this example

only channel 0 is active.

After starting the experiment the module will run for the Recording Length or until the memory is full. Once the

process has stopped the top graph will display a plot of the event frequency over time. The user can now use

the cursors to select a time period of the top graph. When this is done the software will automatically plot the

TCSPC curve for the time tags over that particular period.

The user can, at any time, save these curves and run the experiment again. Fig 13 shows an example of this

mode of operation. The user can, for each run, save a particular TCSPC curve or set of curves and compare it

with other curves at different MACRO time ranges and/or runs.

Once the processing has been stopped, the graphs can be analyzed.

To zoom in, hold right mouse button down and size selection box over area of interest.

To zoom out, sweep mouse from right o left with right mouse button held down.

To measure between points click on graph with right button and left button to position two cursors. The position

of these two cursors and their X and Y differences will be displayed at the top of the graph (see Fig 13).

This mode of operation is particularly useful for carrying out preliminary tests to determine the best conguration,

before carrying out a full experiment using continuous streaming of results to a PC le.

Streaming TCSPC Time Tags

Once the conguration is selected, the user can now select a path and le name for saving the data. It is

recommended that the le name have a sufx of CSV. Doing this will allow the le to be easily viewed using a

spreadsheet package. Once this is done the process can be started by clicking the Start button. Clicking the

Start button will start the module streaming all time tags to the chosen le until the recording time is reached, the

maximum event count is reached or the process is manually stopped.

After the process is stopped the le will be available for viewing. Figure 14 shows a section of a typical output le.

As can be seen in Fig 14, four columns are used to dene the tag number, channel ID, macro time and micro

time.

The example experiment used the test waveform set to 1MHz with a 50% duty cycle. This signal was fed directly

into both the start and stop inputs of channel 0. The start was set to trigger on the LO-HI transition and the stop

SensL © 2011

SensL © 2011

24

24

HRM-TDC

USER MANUAL

> Sensl Integrated Environment (sie) > Using The Sensl Integrated Environment (sie)

was set o trigger on the HI-LO transition. As can be seen in Fig 14, the time-tags are repeating every 200 counts

of the MACRO time. As the resolution of the MACRO time was set to 5ns, this represents a repetition rate of

1ms (200 x 5 ns). The TCSPC time is typically 18712. As the resolution of the MICRO time was set to 27ps, this

represents a TCSPC MICRO time of ~505ns (18712 x 27ps). The value of 505ns rather than the theoretical value

of 500ns is due to the jitter of the clock and the quality of the cabling.

Figure 13 SIE showing the “FIFO - TCSPC with Macro Time” screen

SensL © 2011

SensL © 2011

25

25

HRM-TDC

USER MANUAL

> Sensl Integrated Environment (sie) > Using The Sensl Integrated Environment (sie)

Figure 14 Typical output data from streaming TCSPC Time Tags

“FIFO – Time Tagging” (FIFO – Multi-stop)

This page is used to continuously stream event time tags, as shown in Fig. 15. This mode offers 2 methods that are

selected by the value of the programmable clock. If the programmable clock is set to 1280 HI and 1280 LO then the

Resync option is selected. Any other clock value will select the Free Running option.

Free Running:

Once the conguration is selected, the user can start the module recording. The module will wait for the rst

single start pulse and then start recording every stop event until the recording time is reached, the maximum

event count is reached or the process is manually stopped. The rst start pulse will begin recording. All following

stop events will be stamped and saved. Any following start pulses during the process will be ignored. Hence, all

events, after the initial start signal, can be saved indenitely.

SensL © 2011

SensL © 2011

26

26

HRM-TDC

USER MANUAL

> Sensl Integrated Environment (sie) > Using The Sensl Integrated Environment (sie)

Resync:

Using this method, the user must feed the programmable clock output to the Start input of any channel being

used. Once the conguration is selected, the user can start the module recording. The module will wait for the

rst Start pulse and then start recording every stop event until the recording time is reached, the maximum event

count is reached or the process is manually stopped.

Programmable Clock Output

Free Running:

The Programmable Clock Output is made available for all modes and is used to set the frequency and duty

cycle of the internal programmable clock. This clock is available an SMA output for test purposes. This clock

is provided for testing and diagnostics only. The clock will exhibit a level of jitter that would not be suitable for

accurate measurements as part of an experiment.

Resync:

With the clock programmed to 1280 HI, 1280 LO (FSR register set to 0xFFFF) the module will operate in Resync.

Figure 15 SIE screen for FIFO - Time Tagging

SensL © 2011

SensL © 2011

27

27

HRM-TDC

USER MANUAL

> Sensl Integrated Environment (sie) > Using The Sensl Integrated Environment (sie)

Recording Length

The recording length should be set to the desired period over which the TCSPC measurements are to be taken.

Maximum Event Count

This denes the maximum number of events to be stored before recording stops. This value is used to ensure the

storage data size does not exceed the capacity of the system.

Timer LSB

This is used to select the resolution of the time tag. Selecting bit 0 will give the time tag a resolution of 27ps. Bit 1

will set the resolution to 54ps (2 x 27), bit 2 will set the resolution to 108ps (4 x 27) and so forth.

Channel Enable and Edge Selection

These check boxes allow the individual channels to be enabled/disabled and the START/STOP inputs sensitivity to

be specied.

Note: Press the Apply changes button to set your selected conguration.

Data Recording

Once the conguration is selected, the mode is now ready for recoding data. In FIFO – Time Tagging mode two

forms of data recording are available, Graphical Presentation and Streaming FIFO Time Tags.

Graphical Presentation

In this mode recording is carried out at the module until the recording length or the maximum event count

is reached. To start processing, click on the green right arrow at the top of the page. The right hand side of

the display will show which channels are active. On completion the graph will display a plot of event density

(frequency) over time.

This mode of operation is particularly useful for carrying out preliminary tests to determine the best conguration,

before carrying out a full experiment using continuous streaming of results to a PC le.

Streaming FIFO Time Tags

Once the conguration is selected, the user can now select a path and le name for saving the data. It is

recommended that the le name have a sufx of CSV. Doing this will allow the le to be easily viewed using a

spreadsheet package. Once this is done the process can be started by clicking the Start button. Clicking the

Start button will start the module streaming all time tags to the chosen le until the recording time is reached, the

maximum event count is reached or the process is manually stopped. In this mode there is no TCSPC. The rst

start pulse will begin recording. All following stop events will be stamped and saved in the target PC le. Hence,

all events, after the initial start signal, can be saved to le indenitely.

After the process is stopped the le will be available for viewing. The format of the output le will differ depending

on whether the mode used the Free Running or Resync option. Figure 16 shows a section of a typical output

le for both options.

As can be seen in Fig. 16, four columns are used to dene the tag number, channel ID, macro time and micro

SensL © 2011

SensL © 2011

28

28

HRM-TDC

USER MANUAL

> Sensl Integrated Environment (sie) > Using The Sensl Integrated Environment (sie)

time.

The time tag for this mode consists of 2 x 32-bit words. The rst word is a micro time that has a resolution down

to 27ps. Using the Free Running option this timer will roll over at the count of 5308415 (Hex 50FFFF). Using the

Resync option this timer will roll over every 4 microseconds. In both cases the MACRO counter is a count of how

many times the MICRO counter has rolled over.

Note: The LSB value of 27ps is not an exact value. This value is a simplied (rounded up) value that is suitable for

all other modes. The true LSB value is 26.9851ps. As this mode involves the continuous running of the MICRO

clock for very long periods it is recommended that the value of 26.9851 is used to avoid a cumulative error

occurring over long periods of time.

Figure 16 Data from Free Running mode Data from Resync mode

Example: If the MACRO time value is 28 and the MICRO time is 11232 then the absolute time of the tag from the

start pulse is:

Free Running

((28 x 5308416) + 11232) x 26.9851ps = 4011250921ps. Note: 5308416 = Hex 510000.

Resync

(28 x 4000000) + (11232 x 26.9851) = 112303097 ps. Note: Rollover is every 4000000 ps.

SensL © 2011

SensL © 2011

29

29

HRM-TDC

USER MANUAL

> Sensl Integrated Environment (sie) > Using The Sensl Integrated Environment (sie)

Correlation

The Correlation feature allows the user to carry out cross and auto correlation on FIFO-TCSPC streams for both the

TCSPC values and the MACRO times. The correlation screen is shown in Fig. 17.

In Correlation mode the conguration setup is identical to FIFO-TCSPC mode. However, channel select is restricted

to a maximum of two channels. A single channel selected will result in auto-correlation on that input. Two channels

will result in cross-correlation on the two channels. Further correlation specic settings are as follows:

Target Data Set

Use these two mutually exclusive radio buttons to select correlation on the MICRO (TCSPC) or MACRO time.

Bin Size/Resolution

This setting determines the bin size to be used for the correlation function. Increasing this value will direct the

correlation function to group greater numbers of consecutive time tags into software bins. These bins are then used

for phase sweeping the streams to create the correlation curve.

Maximum Lag

This denes the maximum number of bins to be used for carrying out the correlation algorithm.

Graphical Presentation

Once the conguration is selected, the mode is now ready for recording data. In this mode recording is carried out

at the module until the recording length or the maximum event count is reached. To start processing, click on the

green right arrow at the top of the page.

After starting the experiment the module will run for the Recording Length, the maximum event count is reached or

until the memory is full. Once the process has stopped the top graph will display a plot of the event frequency over

time. The bottom graph will display the correlation curve as specied by the conguration parameters. For details of

the correlation algorithm see the Appendix in this document.

SensL © 2011

SensL © 2011

30

30

HRM-TDC

USER MANUAL

> Sensl Integrated Environment (sie) > Using The Sensl Integrated Environment (sie)

Figure 17 SIE Correlation screen

SensL © 2011

SensL © 2011

31

31

HRM-TDC

USER MANUAL

> Appendix > Hrm-tdc Registers And Low Level Dll Functions

Appendix

HRM-TDC REGISTERS AND LOW LEVEL DLL FUNCTIONS

The control and setup of the HRM-TDC is carried out by a series of commands to a set of conguration registers

within the module. To simplify the control of these registers, a set of low level drivers, in a DLL, is available. The low

level drivers will return an HRM_STATUS of value HRM_OK or HRM_ERROR.

For standard ‘C’ programming the user must use the DLL HRMTimeAPI.DLL

For LabVIEW the user must use the modied version of the DLL providid called HRMTimeALI_LV.DLL

In both cases a copy of the relevant DLL MUST reside in the same folder as the application.

Initialization Low Level Drivers

Before the user can read/write to these conguration registers communication must be established with the module.

To do this the following low level driver functions must be used.

Driver - HRM_GetDLLVersion

HRM_API const char* WINAPI HRM_GetDLLVersion(void)

This function returns a pointer to a text string describing the revision level of the drivers.

Driver - HRM_SetCongurationPath

HRM_API void WINAPI HRM_SetCongurationPath(char* path)

path: Pointer to text string dening path.

This function is used to dene the path where the conguration data for the module resides.

Driver - HRM_RefreshConnectedModuleList

HRM_API bool HRM_RefreshConnectedModuleList(void)

This function can be called at any time to determine if the list of connected modules has changed. This can be used

to periodically poll the USB bus to determine if modules have been connected or disconnected.

Driver - HRM_GetConnectedModuleCount(void)

HRM_API UINT WINAPI HRM_GetConnectedModuleCount(void)

This function is used to determine how many HRM-TDC modules are currently connected to the USB bus.

Driver - HRM_GetConnectedModuleList

HRM_API void WINAPI HRM_GetConnectedModuleList(HANDLE* handleList)

handleList: Pointer to array of HRM-TDC handles for initialization.

SensL © 2011

SensL © 2011

32

32

HRM-TDC

USER MANUAL

> Appendix > Hrm-tdc Registers And Low Level Dll Functions

This function initializes an array of HRM-TDC handles to allow communication with all HRM-TDC modules present

on the USB bus. The size of the array must be greater or equal to the number of modules detected using the function

HRM_GetConnectedModuleCount.

Driver - HRM_CloseModule

HRM_STATUS WINAPI HRM_CloseModule(HANDLE handle)

On completion of the application, this function must be called to release the handle and close the session.

Example:

int moduleCount;

HANDLE handleArr[20];

HRM_RefreshConnectedModuleList();

moduleCount = HRM_GetConnectedModuleCount();

if(moduleCount)

{

HRM_GetConnectedModuleList(handleArr);

APPLICATION CODE HERE

HRM_CloseModule(handleArr);

}

else

printf(“No HRM-TDC modules detected”);

In this example the APPLICATION CODE can address up to ‘moduleCount’ HRM-TDC modules.

Now that communication with the module has been established the conguration registers can be programmed

using the associated low level driver.

ARR – Address Route Register

Register Description

The method of time-binning is based on using the received time-tag data and discrete I/O inputs to form the address

in memory for time-bin processing. In its simplest form, a time-tag could be used as the address bus so that each

time-bin is separated by the resolution of the least signicant bit. On receipt of a time-tag the system outputs the

time-tag as an address and then increments that location (time-bin). In the HRM-TDC system further data bits are

included in the address selection to allow multiple curve plotting based on multiple channel inputs and discrete

inputs for X, Y array plotting. To allow maximum exibility the AAR register can dene any bit to be placed in any

SensL © 2011

SensL © 2011

33

33

HRM-TDC

USER MANUAL

> Appendix > Hrm-tdc Registers And Low Level Dll Functions

position within the address bus for the shared memory.

Understanding the ARR is critical as it is the controller that denes the resolution, curve count and array size of all

measurements.

Before programming the ARR the user must rst assert an RRR (Route Register Reset) command to initialize the

system. Once this is done the ARR is then programmed by sending 27 consecutive writes. The address bus of the

memory is 27 bits (A26-A0). Starting with A0, each write denes the bit number of the ‘Address Option Bits’ to be

routed to that particular address bit. The ‘Address Option Bits’ are as follows:

AOB[24.. 0] TagData

AOB[51..25] Address Counter

AOB[67..52] 16-bit I/O Data

AOB[79..68] Pixel Counter

AOB[91..80] Line Counter

AOB[92] Fix to logic 0

TagData

This is the time-tag data as received by the Pico-Second Timing Interface. Bits 23,24 dene on which channel

the time-tag was received – 00, 01, 10 or 11. The bits 22 down to 0 dene the time with bit 0 being the LSB

(LSB = 26.9851ps).

Address Counter

These bits provide a 27-bit counter that can be routed to the address bus. This counter can be pre-loaded

with a given value. After each write to memory this counter will be automatically incremented. This counter

would be most used when the system is in time-tag mode. Here the system reads time-tags and stores them

in consecutive locations in memory. These bits are also available to be used in Time-bin mode. However, in this

case the address is not incremented. Instead the address counter bits are used purely as an offset address in

memory for saving curves.

16-Bit I/O Data

The value of the 16 I/O data bits can be routed to any address line. This would be useful for plotting X, Y curves.

For example, the I/O could be used as 8-bit X and 8-bit Y inputs allowing a 256 x 256 array of curves to be

plotted.

Pixel Counter/Line Counter/Frame Reset

The 16-bit I/O method of X,Y plotting is limited to 256 x 256 arrays. An alternative method that allows larger

arrays is to use 2 discrete inputs to clock counters that in turn can be used as the address in memory. The

HRM-TDC module provides a 12-bit Pixel Counter and a 12-bit Line Counter. The Pixel Counter is incremented

by clock inputs to IODATA(0) and the line counter is incremented by clock inputs to IODATA(1). If these bits are

routed to the address lines then the user can command the HRM-TDC module to move from one curve to the

next by clocking the IODAT(0) and IOADAT(1) lines. This allows arrays of up to 4096 x 4096.

The contents of the LINE and PIXEL counters are cleared when:

1. A write is sent to the Routing Reset Register (RRR)

2. A LO-HI transition is detected on the IODATA(2) port.

SensL © 2011

SensL © 2011

34

34

HRM-TDC

USER MANUAL

> Appendix > Hrm-tdc Registers And Low Level Dll Functions

The IODATA(2) can be used as a Frame Reset clock input for synchronizing an X,Y pixel image with an external

instrument such as a microscope.

Fix to logic 0

Selecting this bit will drive the particular address line low. This is used for driving the chip select line of a single

memory card. If two memory cards are used then the chip select should be an address counter bit.

Example:

WRITE: 1,2,3,4,5,6,7,8, 23,24, 25,26,27,28,29,30,31,32,33,34,35,36,37,38,39,40,41

This would set up the system recording 4 curves, one from each channel. Each curve would consist of 256 bins

(8 bits) with a bin size of 54ps. This reduced resolution is due to bit 1 (second bit) of the time-tag being routed to

address bit 0. The channel bits 23, 24 will move each channel event to a different curve. The base start address

of these curves will be dened by the pre-programmed value of the Address Counter.

Driver - HRM_SetAddressRouteRegister

HRM_STATUS WINAPI HRM_SetAddressRouteRegister(HANDLE handle, BYTE* arrData)

handle: HRM-TDC module handle

arrData: Array of bytes to write to the address route register.

Note:

The arrData bytes must be padded with 0 values after each routing value. Therefore, for the example, the arrData

array must be set to:

1,0,2,0,3,0,4,0,5,0,6,0,7,0,8,0,23,0,24,0,25,0,26,0,27,0,28,0,29,0,

30,0,31,0,32,0,33,0,34,0,35,0,36,0,37,0,38,0,39,0,40,0,41,0

DRR – Data Route Register

Register Description

When the HRM-TDC system is in time-tag mode it will continually save time-stamps to memory. Each time-stamp

will always be 32-bits, however the format of the time-stamp is programmable using the DRR. To allow maximum

exibility the DRR register can dene any ‘Data Option Bit’ bit to be placed in any position within the 32-bit time-tag.

Before programming the DRR the user must rst assert an RRR (Route Register Reset) command to initialize the

system. Once this is done the DRR is then programmed by sending 32 consecutive writes. Starting with D0, each

write denes the bit number of the ‘Data Option Bits’ to be routed to that particular data bit within the time-tag. The

‘Data Option Bits’ are as follows:

DOB[24.. 0] TagData

DOB[56..25] Macro Counter

DOB[57] Fix to logic 0

SensL © 2011

SensL © 2011

35

35

HRM-TDC

USER MANUAL

> Appendix > Hrm-tdc Registers And Low Level Dll Functions

TagData

This is the time-tag data as received by the Pico-Second Timing Interface. Bits 23,24 dene the channel the

time-tag was received on – 00, 01, 10 or 11. The bits 22 down to 0 dene the time with bit 0 being the LSB

(LSB = 26.9851ps).

Macro Counter

When time-tag recording the user may, along with the TCSPC time, wish to record the chronological time

that the event occurred. A 32-bit Macro Time Counter is made available that is cleared at the start of time-tag

processing and will increment every 5ns. The user can select a range of these bits to provide a macro time to

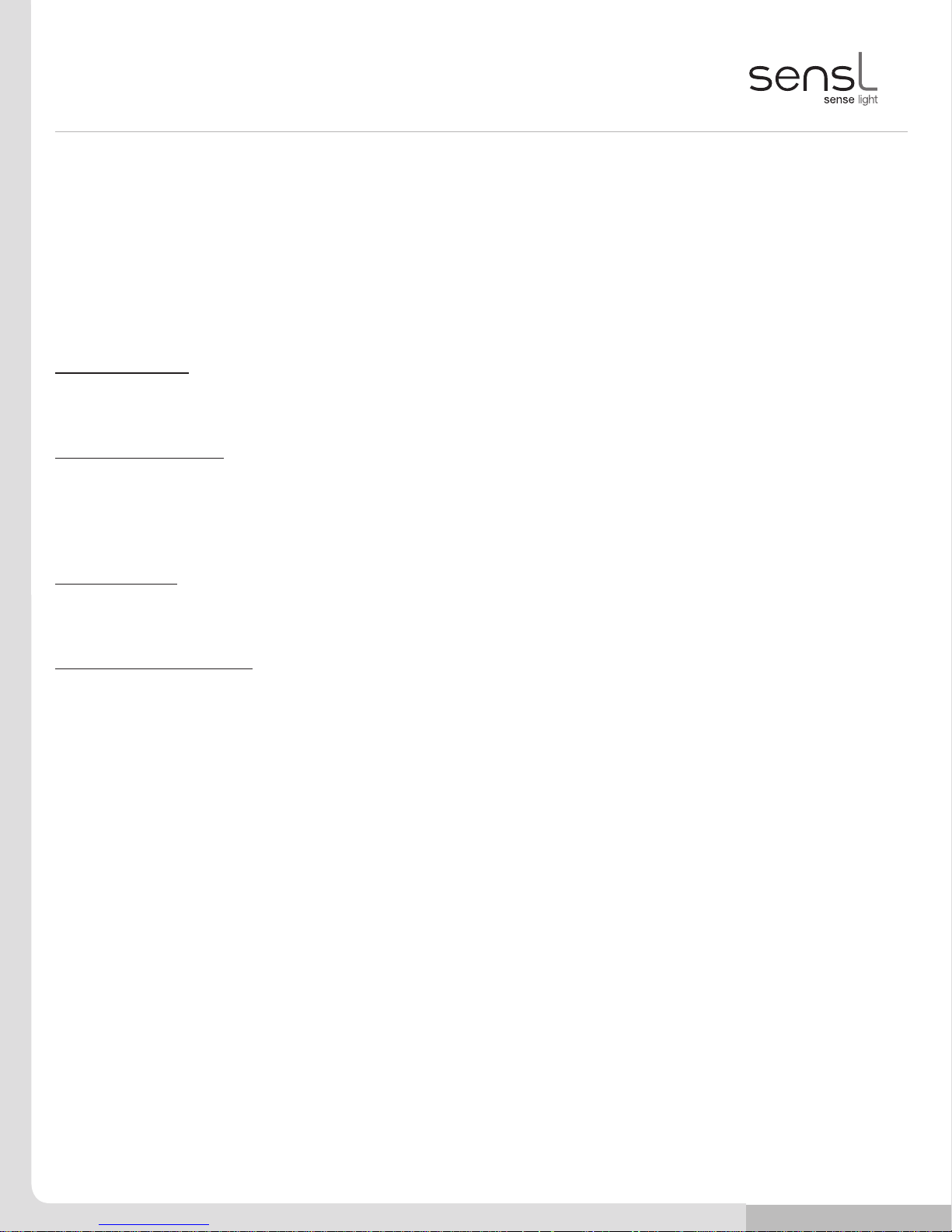

time-stamp each time-tag.

Example:

WRITE: 0,1,2,3,4,5,6,7 26,27,28,29,30,31,32,33,34,35,36,37,38,39,40,41,42,43,44,45,46,47 23,24

This would set up the time-tag as follows:

D[7..0] = TCSPC time (LSB = 26.9851ps)

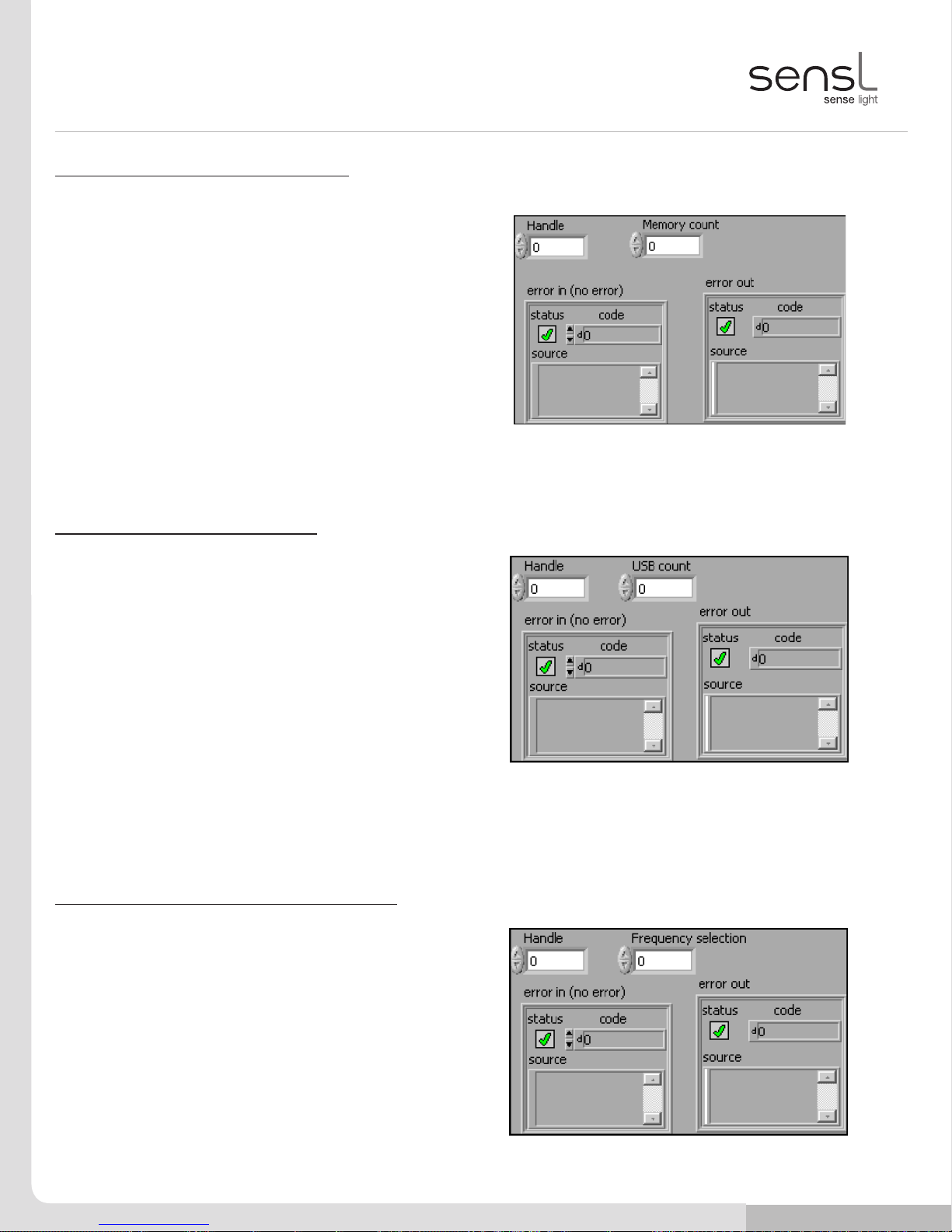

D[29..8] = 22-bit Macro time with LSB resolution of 5ns

D[31..30] = 2-bit channel code 00, 01, 10, 11 for channels 0 to 3.

Driver - HRM_SetDataRouteRegister

HRM_STATUS WINAPI HRM_SetDataRouteRegister(HANDLE handle, BYTE* drrData)

handle: HRM-TDC module handle

drrData: Array of bytes to write to the data route register.

Note:

The drrData bytes must be padded with 0 values after each routing value. Therefore, for the example, the drrData

array must be set to:

0,0,1,0,2,0,3,0,4,0,5,0,6,0,7,0,26,0,27,0,28,0,29,0,30,0,31,0,32,0,33,0,34,0,

35,0,36,0,37,0,38,0,39,0,40,0,41,0,42,0,43,0,44,0,45,0,46,0,47,0,23,0,24,0

LAL, LAH – Load Address LO/HI Register

Register Description

These two registers are used to initialize the ‘Address Counter’ (see ARR register) to a pre-dened value. The order

of loading the initialization address must be LAL followed by LAH. The LAL command will dene the least signicant

16 bits (A15 down to A0) of the counter. The least signicant 11 bits of the LAH command will dene counter bits

A26 down to A16. On completion of the LAH command the ‘Address Register’ will be loaded with the new value.

SensL © 2011

SensL © 2011

36

36

HRM-TDC

USER MANUAL

> Appendix > Hrm-tdc Registers And Low Level Dll Functions

Driver - HRM_SetAddressRegister

HRM_STATUS WINAPI HRM_SetAddressRegister(HANDLE handle, ULONG arData)

handle: HRM-TDC module handle

arData: 32-bit address to set LAH, LAL to.

LFL, LFH – Load Fill Value LO/HI Register

Register Description

The user can command the HRM-TDC module to ll a range of memory with a given value. The value used for this

command is dened using these 2 commands. The initialization value is a 32-bit value. The most signicant 16 bits

is dened by LFH and the least signicant 16 bits is dened bits LFL.

Driver - HRM_SetFillValueRegister

HRM_STATUS WINAPI HRM_SetFillValueRegister(HANDLE handle, ULONG fvrData)

handle: HRM-TDC module handle

arData: 32-bit value to set LFH, LFL to.

UAL, UAH – Load Address LO/HI Register

Register Description

These two registers are used to initialize the USB address counter. The block DMA transfers from memory to the

USB start at the address dened by these two commands. On completion of each USB transfer the USB address

counter is automatically incremented. This address is a 32-bit ‘long word’ address. All USB block transfers are

carried out in long words (4 bytes at a time). The order of loading the initialization address must be UAL followed by

UAH. The UAL command will dene the least signicant 16 bits (A15 down to A0) of the counter. The least signicant

10 bits of the UAH command will dene counter bits A25 down to A16. On completion of the UAH command the

‘Address Register’ will be loaded with the new value.

UAL:

D15 D14 D13 D12 D11 D10 D09 D08 D07 D06 D05 D04 D03 D02 D01 D00

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

UAH:

D15 D14 D13 D12 D11 D10 D09 D08 D07 D06 D05 D04 D03 D02 D01 D00

Nu Nu Nu Nu Nu Nu A25 A24 A23 A22 A21 A20 A19 A18 A17 A16

SensL © 2011

SensL © 2011

37

37

HRM-TDC

USER MANUAL

> Appendix > Hrm-tdc Registers And Low Level Dll Functions

Driver - HRM_SetUSBAddressRegister

HRM_STATUS WINAPI HRM_SetUSBAddressRegister(HANDLE handle, ULONG uarData)

handle: HRM-TDC module handle

uarData: 32-bit address to set UAH, UAL to.

MBR – Mode Bits Register

Register Description

This register denes a number of settings for the HRM-TDC module as follows:

D15 D14 D13 D12 D11 D10 D09 D08 D07 D06 D05 D04 D03 D02 D01 D00

Rmd Mem Nu Nu Nu Nu Nu Nu Nu BCe Rvd Rvd Size Md2 Md1 Md0

Md[2..0] These bits dene in which mode the HRM-TDC module will operate.

000 = Fill ‘n’ memory locations with the LFL,LFH value.

The value of ‘n’ is dened by the MCL,MCH registers.

The start address is dened by the LAL,LAH registers.

001 = Run in TIME-TAG with TCSPC mode.

010 = Run in TIME-TAG continuous mode.

011 = Run in TIME-BIN with TCSPC mode.

100 = Run in TIME-BIN continuous mode.

All other Md[] combinations are reserved. Power-up default = 000.

Size

In TIME-BIN mode the bin size can be set for 16 bits or 32 bits. If ‘Size’ is set to ‘1’ the bin size will be 16 bits.