THIS DOCUMENT CONTAINS PROPRIETARY INFORMATION AND SUCH

INFORMATION MAY NOT BE DISCLOSED TO OTHERS FOR ANY

PURPOSES WITHOUT WRITTEN PERMISSION FROM

SELEX Sistemi Integrati Inc.

Copyright © 2008, SELEX Sistemi Integrati Inc.

Operations and Maintenance Manual

Model 1150A Doppler

VHF Omnirange (DVOR)

571150A-0002 Rev - November, 2008

SELEX Sistemi Integrati Inc.

11300 West 89th Street

Overland Park, KS U.S.A. 66214

THIS SHEET INTENTIONALLY BLANK

SAFETY SUMMARY

The following are general safety precautions that are unrelated to specific procedures and therefore do not appear

elsewhere in this publication. These are recommended precautions that personnel should understand and apply

during through the many phases of operation and maintenance.

ELECTROSTATIC SENSITIVE DEVICES PRECAUTIONS

Since most modules used in all models of equipment have Electrostatic Discharge (ESD) sensitive devices included

in them, all modules should be considered sensitive to electrostatic discharge. Handling in the field shall be the

same as in the factory. Each system is shipped with a wrist strap that must be worn while maintaining the

equipment. The wrist strap shall be fastened to the equipment chassis either in the designated plug-in or attached to

the equipment chassis with the alligator clip. The wrist strap must be used before any modules are removed from

the equipment and at all times while handling the modules until they are placed in a protective environment such as

an anti-static bag. Modules or boards must not be placed on any non-conducting surface such as wooden work

benches, painted metal work benches, plastics, or technical manuals. Any work surface to be used must have a

conducting mat placed on it and attached to earth ground. The mat and additional wrist straps can be obtained from

SELEX Sistemi Integrati Inc.

KEEP AWAY FROM LIVE CIRCUITS

Operating personnel must at all times observe all safety regulations. Under no circumstances should any person

remove any protective covers that expose lethal voltages. Do not replace components or make adjustments inside

the equipment with primary power supply turned on. Under certain conditions, dangerous potentials may exist when

the power is in the off position, due to charges retained by capacitors. To avoid casualties, always remove power

and allow time for the capacitors to discharge before touching it.

DO NOT SERVICE OR ADJUST ALONE

Under no circumstances should any person reach into or enter the enclosure for the purpose of servicing or adjusting

the equipment except in the presence of someone who is capable of rendering aid.

RESUSCITATION

Personnel working with or near high voltages should be familiar with modern methods of resuscitation.

THIS SHEET INTENTIONALLY BLANK

SELEX Sistemi Integrati Inc.

This equipment is supplied by SELEX Sistemi Integrati Inc. For replacement parts and repair service, contact

SELEX Sistemi Integrati Inc. using the contact information provided below.

HOW TO ORDER REPLACEMENT PARTS

When ordering replacement parts, you should contact SELEX Sistemi Integrati Inc. by fax, phone or email. Please

address the following items (as applicable) in your correspondence to enable us to provide the best possible service.

1. SELEX Sistemi Integrati Inc. model number, type and serial number of equipment.

2. Unit sub-assembly number (where applicable).

3. Item or reference symbol number from parts list or schematic.

4. SELEX Sistemi Integrati Inc. part number and description.

5. Manufacturer's code, name and part number (where applicable).

6. Quantity of each replacement part required.

HOW TO REQUEST REPAIR SERVICE

In order to ensure prompt attention, parts returned for repair should have the following:

1. RMA number (Return Material Authorization number), assigned prior to return when requesting

repair service.

2. Unit part number

3. Site location

4. System information

5. Ship-to address for return

6. Contact name and number

7. Date and time of request

CONTACT INFORMATION

SELEX Sistemi Integrati Inc.

11300 W 89th Street

Overland Park KS, 66214, USA

Main Switchboard: (913) 495-2600

Main Fax: (913) 492-0870

Toll free: (800) 331-2744

CSM Direct Phone: (913) 495-2625

CSM E-mail: Support@selex-si-us.com

World Wide Web URL: www.selex-si-us.com

THIS SHEET INTENTIONALLY BLANK

MANUFACTURER’S WARRANTY

SELEX Sistemi Integrati Inc.

The following warranty is applicable in all cases, except where modified or superseded by specific contract terms.

Contact SELEX Sistemi Integrati Inc. if clarification is required.

A. The Manufacturer warrants to the original Purchaser, subject to the limitations and exclusions stated below,

that mechanical and electrical parts of products which it manufactures, (the “Products” will be free of

defects in materials and workmanship for a period of (I) one (1) year from the date of installation or (ii) 18

months from the date of shipment, whichever first occurs (the “Warranty Period”).

B. If the Customer believes a Product is defective, notice thereof shall be provided to the Manufacturer’s

Customer Service Department at the address provided on the cover page and (if applicable) to the selling

distributor. A defect in material and workmanship covered by this warranty shall be deemed to have

occurred only if, and as of the time when, the Manufacturer is notified in writing by the Customer, within

the Warranty Period, that the Product has become defective, and the Manufacturer’s personnel verify that

the said Product, in fact, does not comply with the warranty provided hereunder and it is determined that:

(i) The Products, during the entire Warranty Period, have been operated within normal service

conditions, recommended by the Manufacturer and recognized in the industry, and

(ii) The Products have been installed and adjusted according to the Manufacturer’s procedures as

stated in the Instruction Manual or other instructions supplied in writing by the Manufacturer.

C. Failures caused by lightning or other acts of God, or power surges, are not considered to be defects in

materials and workmanship and are not covered under this warranty. Routine Maintenance and calibration

are also not considered to be defects in materials and workmanship and are not covered under this

warranty. Any change, modification or alteration of the Manufacturer’s Products not specifically

authorized by the Manufacturer will void this warranty.

D. If it is determined that the conditions for warranty coverage, as described above, have been satisfied, the

Manufacturer shall repair or replace the defective products or parts thereof in accordance with the

following procedures:

(i) Customer will contact the Manufacturer’s customer Service Department which will issue the

Customer a Return Authorization (RA) number.

(ii) The Component, defective part, or Product, as appropriate, shall be returned to the Manufacturer

for inspection, freight prepaid by the customer. The Component, defective part, or Product MUST

be packaged with an industry standard anti-static protective bag sufficient to prevent any ESD

intrusion during handling and shipment, and MUST ALSO be packaged to protect from damage

due to rough handling encountered during shipment. FAILURE TO COMPLY WITH THIS

REQUIREMENT WILL VOID THE WARRANTY OF THE RETURNED ITEM. The RA

number must be clearly displayed on the exterior of the shipping container. No shipments will be

accepted without a RA number. All custom duties, fees, etc. will be paid by the Customer.

(iii) If, upon inspection it is determined by Manufacturer’s personnel that the Product or component

thereof is indeed defective and covered by this warranty, then Manufacturer, at its option, may

either repair the Product or defective components thereof and return the same to the Customer or

ship a replacement for the defective Product or part thereof, freight paid. All customs duties, fees,

etc. will be paid by the Customer. The Product or component thereof will be returned to the

Customer utilizing a shipping mode similar to that used by Customer to ship the same to the

Manufacturer.

(iv) If, upon inspection by Manufacturer, it is determined that the Product or component thereof was

not defective or was not covered by this warranty, then the cost of all of Manufacturer’s

inspections and the return shipping charges will be charged to Customer.

E. The Manufacturer reserves the right to make modifications and alterations to Products without obligation to

install such improvements on, in, or in place of theretofore manufactured products of Manufacturer.

MANUFACTURER’S WARRANTY (cont.)

F. Manufacturer does not warranty any Products, components, subassemblies, or parts not of its own

manufacture. Manufacturer hereby transfers to Customer any and all warranties (if any) which it receives

from its suppliers.

G. Periodic calibration / re-calibration of test equipment is not covered under this or any Seller’s warranty, and

is the sole responsibility of the Purchaser.

H. Any and all claims for shortages, missing or damaged items must be presented, in writing, to the Seller

within 120 days of the date of shipment from Seller’s factory.

I. This warranty applies only to the original purchaser and, unless Customer receives the express written

consent of an officer of Manufacturer, this warranty may not be assigned, transferred, or conveyed to any

third party, even if the third party is a bon a fide purchaser of the Products.

J. THIS WARRANTY IS EXPRESSLY IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED OR

IMPLIED, WHETHER STATUTORY OR OTHERWISE, INCLUDING IMPLIED WARRANTY

OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. IN NO EVENT

SHALL THE MANUFACTURER BE LIABLE FOR INDIRECT, INCIDENTAL, COLLATERAL,

PUNITIVE, OR CONSEQUENTIAL DAMAGES OF ANY KIND, WHETHER ARISING OUT OF

CONTRACT, TORT, NEGLIGENCE, STRICT LIABILITY OR OTHER PRODUCTS LIABILITY

THEORY.

K. CUSTOMER’S SOLE REMEDY FOR ANY BREACH OF THE WARRANTY SHALL BE THE

REPAIR OR REPLACEMENT OF THE PRODUCTS BY THE MANUFACTURER AS

PROVIDED HEREIN, AND IN NO EVENT SHALL THE MANUFACTURER BE REQUIRED TO

INCUR COSTS FOR THE REPAIR OR REPLACEMENT OF ANY PRODUCT IN EXCESS OF

THE PURCHASE PRICE OF SUCH PRODUCT, PLUS ANY TRANSPORTATION CHARGES

ACTUALLY PAID ATTRIBUTABLE TO SUCH PRODUCTS.

Model 1150A DVOR

TABLE OF CONTENTS

ragraph

Pa

# Description Page #

1 GENERAL INFORMATION AND REQUIREMENTS......................................................................1-1

1.1 INTRODUCTION ................................................................................................................................1-1

1.2 EQUIPMENT DESCRIPTION.............................................................................................................1-2

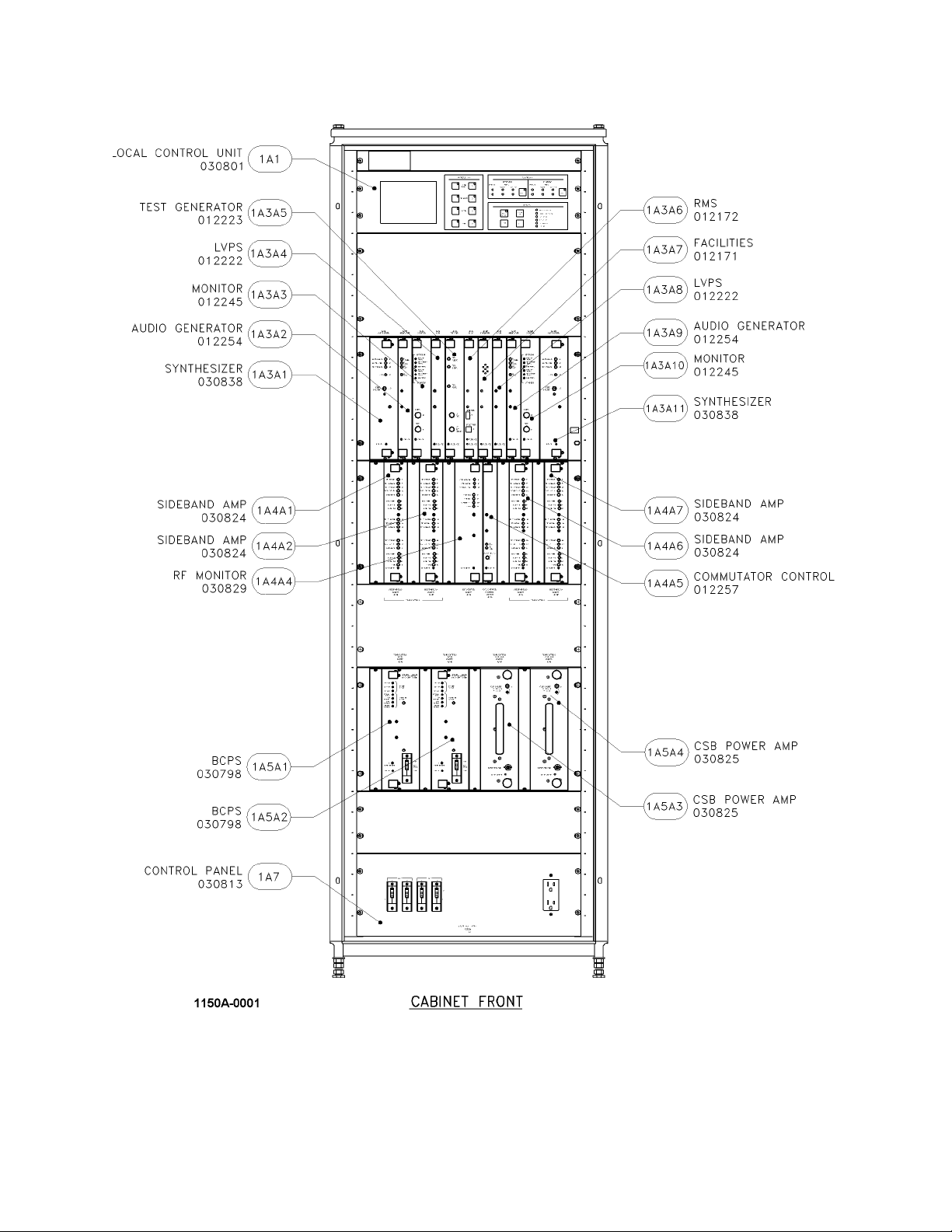

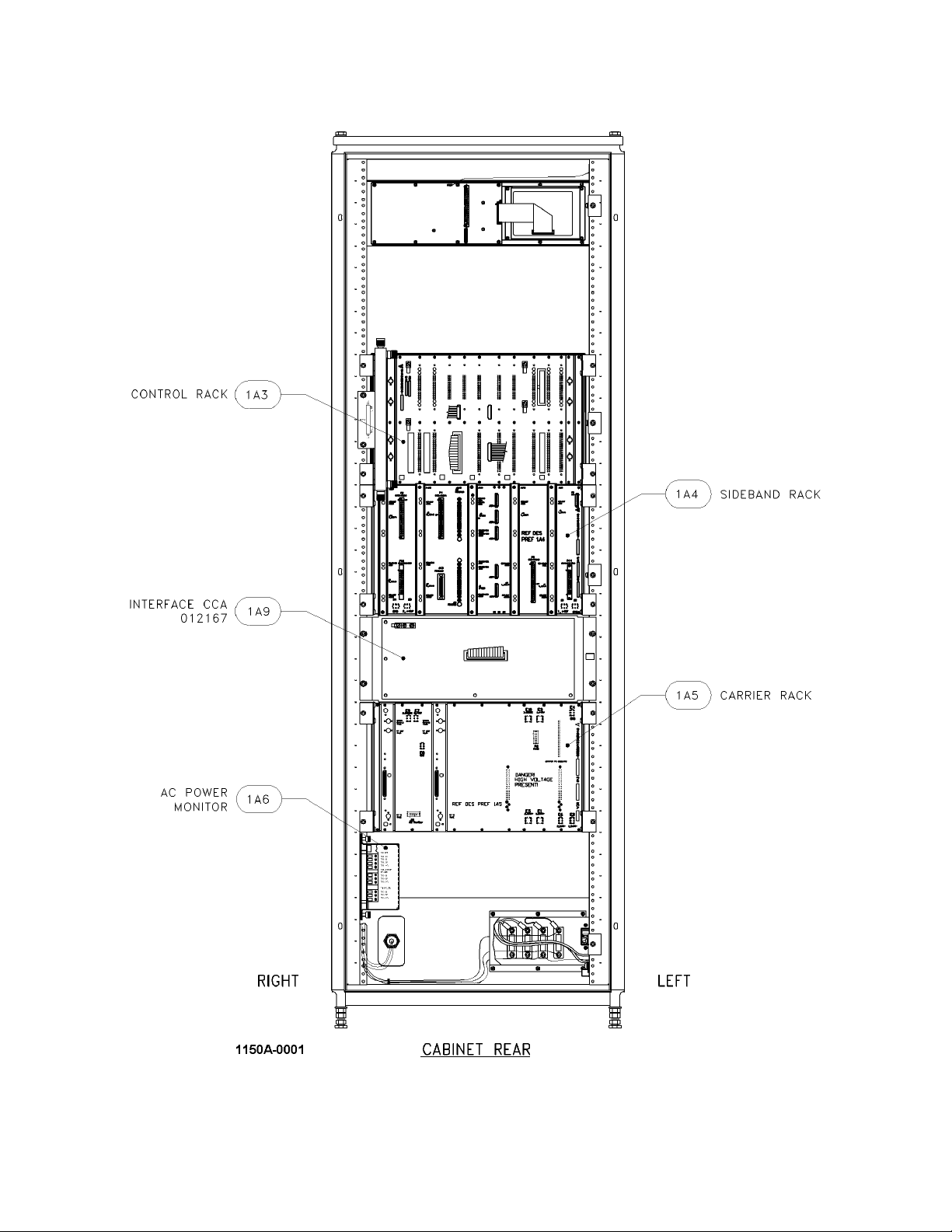

1.2.1 Electronics Cabinet...............................................................................................................................1-2

1.2.1.1 Local Control Unit (LCU) (1A1)..........................................................................................................1-3

1.2.1.2 Synthesizer Assembly (1A3A1, 1A3A11)............................................................................................1-3

1.2.1.3 Audio Generator CCA (1A3A2, 1A3A9) .............................................................................................1-3

1.2.1.4 Monitor CCA (1A3A3, 1A3A10).........................................................................................................1-7

1.2.1.5 Low Voltage Power Supply (LVPS) CCA (1A3A4, 1A3A8)...............................................................1-7

1.2.1.6 Test Generator CCA (1A3A5)..............................................................................................................1-7

1.2.1.7 Remote Monitoring System (RMS) Processor CCA ( 1A3A6)............................................................1-7

1.2.1.8 Facilities CCA (1A3A7) .......................................................................................................................1-7

1.2.1.9 Sideband Amplifier Assembly (1A4A1, 1A4A2, 1A4A6, 1A4A7)......................................................1-7

1.2.1.10 RF Monitor Assembly (1A4A4)...........................................................................................................1-7

1.2.1.11 Commutator Control CCA (1A4A5).....................................................................................................1-7

1.2.1.12 Battery Charging Power Supply (BCPS) Assembly (1A5A1, 1A5A2) ................................................1-8

1.2.1.13 Carrier Power Amplifier Assembly (1A5A3, 1A5A4)..........................................................................1-8

1.2.1.14 Interface CCA (1A9).............................................................................................................................1-8

1.2.1.15 AC Power Monitor Assembly (1A6) ....................................................................................................1-8

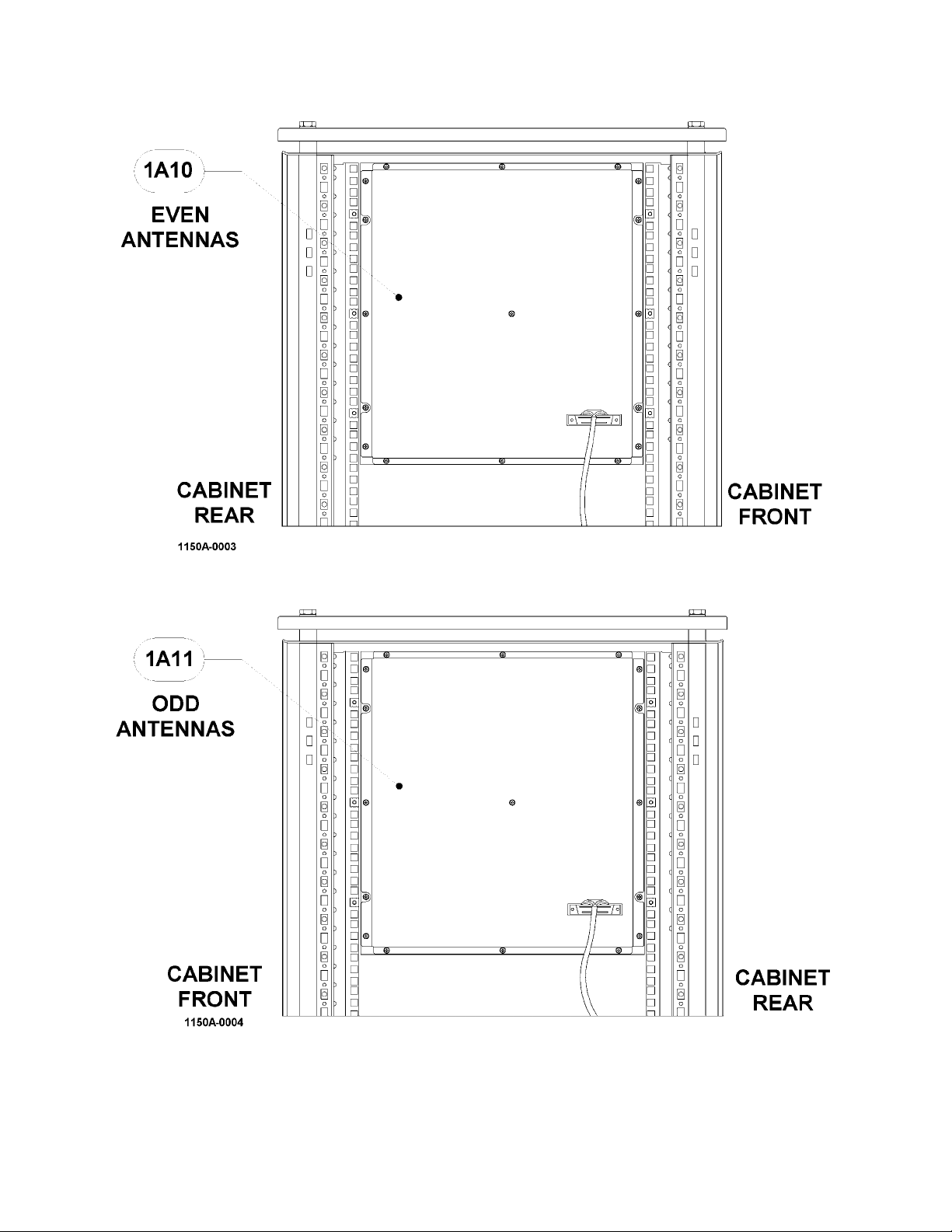

1.2.1.16 Commutator CCA (1A10, 1A11)..........................................................................................................1-8

1.2.2 Portable Maintenance Data Terminal (PMDT) .....................................................................................1-8

1.2.3 Transmitting Antenna System...............................................................................................................1-9

1.2.3.1 Carrier Antenna.....................................................................................................................................1 -9

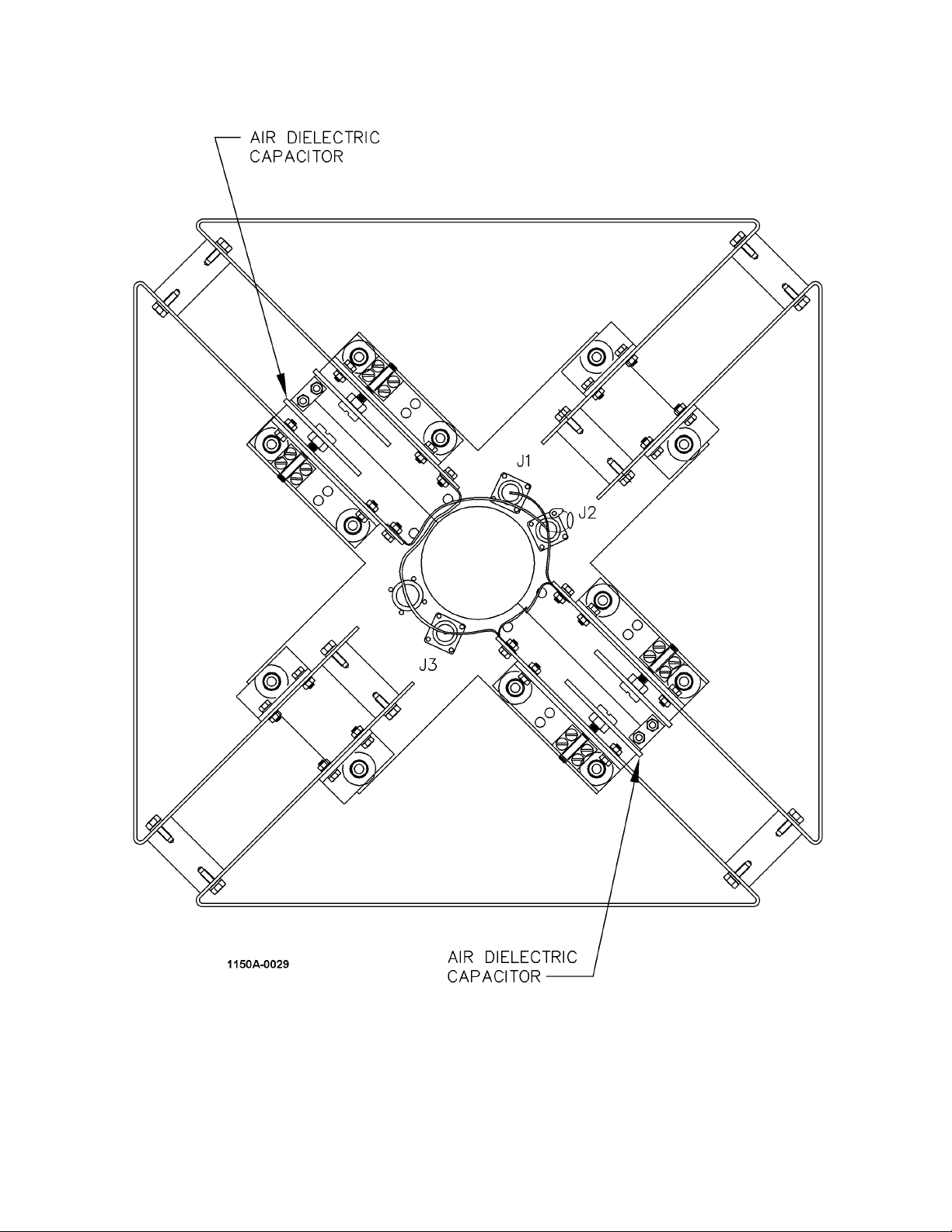

1.2.3.2 Sideband Antenna...............................................................................................................................1-12

1.2.3.3 Balun...................................................................................................................................................1-13

1.2.3.4 Tuning Stub.........................................................................................................................................1-14

1.2.3.5 Positioning Piece.................................................................................................................................1-14

1.2.3.6 Pedestal...............................................................................................................................................1-14

1.2.3.7 Radome ...............................................................................................................................................1-14

1.2.4 Field Monitor Antenna........................................................................................................................1-15

1.2.5 Counterpoise .......................................................................................................................................1-15

1.2.6 Equipment Shelter............................................................................................................................... 1 -16

1.2.7 Battery Backup Unit (Optional)..........................................................................................................1-16

1.3 EQUIPMENT SPECIFICATION DATA...........................................................................................1-16

1.3.1 Transmitter and Antenna System........................................................................................................1-16

1.3.1.1 Transmitter ..........................................................................................................................................1-16

1.3.1.2 Antenna System..................................................................................................................................1-18

1.3.1.3 Field Monitor......................................................................................................................................1-18

1.3.2 Monitor ...............................................................................................................................................1-19

1.3.3 Mechanical and Electrical...................................................................................................................1-20

1.3.4 Remote Control System......................................................................................................................1-20

1.3.4.1 Design Features...................................................................................................................................1 -20

1.3.4.2 RCSU Controls and Indicators............................................................................................................1 -21

1.3.4.3 RSU Controls and Indicators ..............................................................................................................1-21

1.3.5 Remote Maintenance Monitoring System (RMM) .............................................................................1-22

1.3.5.1 Design Features...................................................................................................................................1 -22

1.3.5.2 RMM Functions..................................................................................................................................1-22

1.4 EQUIPMENT AND ACCESSORIES SUPPLIED.............................................................................1-23

1.5 OPTIONAL EQUIPMENT.................................................................................................................1-23

2 TECHNICAL DESCRIPTION.............................................................................................................2-1

2.1 INTRODUCTION ................................................................................................................................2-1

Rev. - November, 2008

This document contains proprietary information and such information may not be disclosed

to others for any purposes without written permission from SELEX Sistemi Integrati Inc.

i

Model 1150A DVOR

TABLE OF CONTENTS (cont.)

Paragraph

# Description Page #

2.2 OPERATING PRINCIPLES.................................................................................................................2-1

2.2.1 DVOR Antenna Principles....................................................................................................................2-3

2.3 DVOR TRANSMITTER THEORY OF OPERATION........................................................................2-3

2.3.1 Simplified System Block Diagram........................................................................................................2-3

2.3.1.1 Electronics Cabinet (Unit 1)..................................................................................................................2-6

2.3.2 System Block Diagram Theory.............................................................................................................2-6

2.3.2.1 Frequency Synthesizer (1A3A1, 1A3A11)...........................................................................................2-7

2.3.2.1.1 Frequency Synthesizer Block Diagram Theory....................................................................................2-7

2.3.2.1.2 Frequency Synthesizer (1A3A1, 1A3A11) Detailed Circuit Theory....................................................2-9

2.3.2.1.2.1 Frequency Reference Circuitry.............................................................................................................2-9

2.3.2.1.2.2 Carrier PLL Synthesizer Circuitry......................................................................................................2-10

2.3.2.1.2.3 Carrier Phase Control Loop ................................................................................................................2-12

2.3.2.1.2.4 Sideband RF Generation Loops..........................................................................................................2-14

2.3.2.2 Audio Generator CCA (1A7, 1A23) Theory.......................................................................................2-15

2.3.2.2.1 Audio Generator CCA Block Diagram Theory...................................................................................2-15

2.3.2.3 Audio Generator CCA Detailed Circuit Theory..................................................................................2-17

2.3.2.4 CSB Power Amplifier Assembly (1A5A3, 1A5A4)...........................................................................2-19

2.3.2.4.1 CSB Power Amplifier Assembly Block Diagram Theory ..................................................................2-19

2.3.2.4.2 Power Amplifier Assembly Detailed Circuit Theory..........................................................................2 -20

2.3.2.5 Bi-Directional Coupler (1DC1)...........................................................................................................2-22

2.3.2.6 Sideband Generator Assembly (1A4A1, 1A4A2, 1A4A6, 1A5A7)....................................................2-22

2.3.2.6.1 Sideband Generator Assembly Block Diagram Theory......................................................................2-22

2.3.2.6.2 Sideband Generator CCA Detailed Circuit Theory.............................................................................2-24

2.3.2.7 RF Monitor Assembly (1A4A4) Theory.............................................................................................2-27

2.3.2.8 RF Monitor Assembly Block Diagram Theory...................................................................................2-27

2.3.2.8.1 RF Monitor Assembly (1A2) Detailed Circuit Theory.......................................................................2-28

2.3.2.9 RMS Processor Block Diagram Theory..............................................................................................2-30

2.3.2.9.1 RMS CCA Detailed Theory................................................................................................................2-32

2.3.2.10 Facilities CCA Theory........................................................................................................................2-34

2.3.2.10.1 Facilities CCA Detailed Theory..........................................................................................................2-36

2.3.2.11 Interface CCA Theory.........................................................................................................................2-38

2.3.2.12 Interface CCA Block Diagram Theory...............................................................................................2-38

2.3.2.12.1 Interface CCA Detailed Theory..........................................................................................................2-39

2.3.2.13 AC Power Monitor CCA Theory........................................................................................................2-40

2.3.2.13.1 AC Power Monitor CCA Block Diagram Theory...............................................................................2-41

2.3.2.13.2 AC Power Monitor CCA Detailed Theory..........................................................................................2-41

2.3.2.14 Local Control Unit Theory..................................................................................................................2-42

2.3.2.14.1 Local Control Unit Block Diagram Theory ........................................................................................2-43

2.3.2.14.1.1 DC to DC Converter ...........................................................................................................................2-43

2.3.2.14.1.2 Power Fail Detectors...........................................................................................................................2-43

2.3.2.14.1.3 Key Switch Registers..........................................................................................................................2-43

2.3.2.14.1.4 Parallel Interface .................................................................................................................................2-43

2.3.2.14.1.5 1.8432MHz Oscillator/Divider Chains ...............................................................................................2-44

2.3.2.14.1.6 Positive Alarm Register......................................................................................................................2-44

2.3.2.14.1.7 Negative Alarm Register.....................................................................................................................2-44

2.3.2.14.1.8 20 Second Delay Counter ...................................................................................................................2-44

2.3.2.14.1.9 LCU Transfer Control State Machine #1 and #2 and Discrete Controls.............................................2-45

2.3.2.14.1.10 LED Control........................................................................................................................................2-45

2.3.2.14.1.11 Audible Alarm ....................................................................................................................................2-45

2.3.2.14.1.12 Monitor Alarm Interface.....................................................................................................................2-45

2.3.2.14.1.13 Station Control Logic..........................................................................................................................2-45

ii Rev. - November, 2008

This document contains proprietary information and such information may not be disclosed

to others for any purposes without written permission from SELEX Sistemi Integrati Inc.

Model 1150A DVOR

TABLE OF CONTENTS (cont.)

ragraph

Pa

# Description Page #

2.3.2.14.1.14 System Configuration Inputs...............................................................................................................2-46

2.3.2.15 Test Generator (1A3A5) CCA Theory................................................................................................2-46

2.3.2.15.1 Test Generator CCA Block Diagram Theory...................................................................................... 2 -46

2.3.2.15.2 Test Generator CCA Detailed Circuit Theory.....................................................................................2-48

2.3.2.16 Low Voltage Power Supply (1A3A4, 1A3A8) CCA Theory.............................................................2-50

2.3.2.16.1 Low Voltage Power Supply (LVPS) CCA Block Diagram Theory....................................................2-50

2.3.2.16.2 Low Voltage Power Supply (LVPS) CCA Detailed Circuit Theory...................................................2-51

2.3.2.17 Monitor CCA (1A3A3, 1A3A9) Theory............................................................................................. 2 -52

2.3.2.17.1 Monitor CCA Block Diagram Theory ................................................................................................2-52

2.3.2.17.2 Monitor CCA Detailed Circuit Theory...............................................................................................2-55

2.3.2.18 Power Panel Theory............................................................................................................................2-61

2.3.2.19 Battery Charger Power Supply (BCPS) Theory..................................................................................2-61

2.3.2.19.1 BCPS CCA Block Diagram Theory....................................................................................................2-61

2.3.2.20 Battery Charger Detailed Circuit Theory............................................................................................2-63

2.3.2.21 Extender Board Block Diagram Theory..............................................................................................2-65

2.3.2.22 Commutator Control CCA Theory......................................................................................................2-66

2.3.2.22.1 Commutator Control CCA Block Diagram Theory............................................................................2-67

2.3.2.22.2 Commutator Control CCA Detailed Circuit Theory...........................................................................2-68

2.3.2.23 Commutator CCA (1A10, 1A11) Theory ...........................................................................................2-72

2.3.2.23.1 Commutator CCA Block Diagram Theory .........................................................................................2-72

2.3.2.23.2 Commutator CCA (2A2, 2A3) Detailed Circuit Theory.....................................................................2-74

2.4 PMDT (Portable Maintenance Data terminal (UNIT 2)......................................................................2-76

2.5 BATTERIES (UNIT 3).......................................................................................................................2-76

2.6 FIELD MONITOR KIT (UNIT 4)......................................................................................................2-76

3 OPERATION....................................................... ............................................................................ .....3-1

3.1 Introduction...........................................................................................................................................3-1

3.2 REMOTE CONTROL STATUS UNIT (RCSU)..................................................................................3-1

3.3 REMOTE STATUS UNIT (RSU)........................................................................................................3-1

3.4 Remote Status Display Unit (RSDU)....................................................................................................3-1

3.5 PORTABLE MAINTENANCE DATA TERMINAL (PMDT)............................................................3-1

3.5.1 Equipment Turn On ..............................................................................................................................3-1

3.5.1.1 Connecting the PMDT..........................................................................................................................3-1

3.5.1.2 Starting the PMDT Application...................................................................................... ......................3-2

3.5.1.3 Turning On the VOR.............................................................................................................................3-2

3.5.2 Equipment Shutdown............................................................................................................................3-2

3.5.2.1 Equipment Turn Off..............................................................................................................................3-2

3.5.2.2 PMDT PC Turn Off..............................................................................................................................3-2

3.6 PMDT Screens......................................................................................................................................3-2

3.6.1 General............................... ...................................... ............................................................................ .3-2

3.6.2 Menus....................................................................................................................................................3-2

3.6.3 System Status at a Glance - Sidebar Status and Control.......................................................................3-4

3.6.4 Screen Area ...........................................................................................................................................3-5

3.6.5 Configuring the PMDT.........................................................................................................................3-5

3.6.6 Connecting to the VOR.........................................................................................................................3-6

3.6.6.1 Security Levels......................................................................................................................................3-6

3.6.6.2 PMDT Logon via Direct or Modem Connection..................................................................................3-7

3.6.7 RMS Screens.........................................................................................................................................3-9

3.6.7.1 RMS Status Screens..............................................................................................................................3-9

3.6.7.1.1 VOR/DME Status Screen......................................................................................................................3-9

3.6.7.1.2 Monitor/Transmitter Status Screen.....................................................................................................3-10

3.6.7.1.3 Software Revisions Screen..................................................................................................................3-11

Rev. - November, 2008

This document contains proprietary information and such information may not be disclosed

to others for any purposes without written permission from SELEX Sistemi Integrati Inc.

iii

Model 1150A DVOR

TABLE OF CONTENTS (cont.)

Paragraph

# Description Page #

3.6.7.1.4 Hardware Revisions Screen................................................................................................................3-12

3.6.7.2 RMS Data Screens..............................................................................................................................3-13

3.6.7.2.1 RMS Maintenance Alerts Screen........................................................................................................ 3 -13

3.6.7.2.2 Power Supply Data Screen..................................................................................................................3-14

3.6.7.2.3 Digital I/O Screen...............................................................................................................................3-15

3.6.7.2.4 Temperature Data Screen....................................................................................................................3-16

3.6.7.2.5 A/D Data Screen .................................................................................................................................3-17

3.6.7.3 RMS Logs Screen...............................................................................................................................3-18

3.6.7.3.1 Operational Summary Screen .............................................................................................................3-18

3.6.7.3.2 Alarm Log Screen...............................................................................................................................3-19

3.6.7.3.3 Maintenance Alert Log Screen............................................................................................................3-20

3.6.7.3.4 Command Activity Screen..................................................................................................................3-21

3.6.7.3.5 Parameter Change Log Screen............................................................................................................3-22

3.6.7.4 RMS Configuration Screen.................................................................................................................3-23

3.6.7.4.1 General RMS Configuration Screen ...................................................................................................3-24

3.6.7.4.2 Station Configuration Screen..............................................................................................................3-26

3.6.7.4.3 Power Supply Limits Configuration Screen.......................................................................................3-28

3.6.7.4.4 A/D Limits Configuration Screen......................................................................................................3-29

3.6.7.4.5 Security Codes Configuration Screen.................................................................................................3-30

3.6.7.4.5.1 User Account Maintenance.................................................................................................................3-30

3.6.7.4.5.2 Add a User Account............................................................................................................................3-30

3.6.7.4.5.3 Change a User’s Password..................................................................................................................3-31

3.6.7.4.5.4 Delete a User’s Account .....................................................................................................................3-31

3.6.7.5 RMS Commands.................................................................................................................................3-32

3.6.8 Monitor Screens..................................................................................................................................3-35

3.6.8.1 All Monitor Screens............................................................................................................................3-35

3.6.8.1.1 Monitors Data Screens........................................................................................................................3-35

3.6.8.1.1.1 Integral Monitor Data Screen.............................................................................................................. 3 -35

3.6.8.1.1.2 Notch Monitor Data Screen ................................................................................................................3-36

3.6.8.1.1.3 Sideband Antenna VSWR Screen.......................................................................................................3-37

3.6.8.1.2 Monitor Configuration Screens...........................................................................................................3-38

3.6.8.1.2.1 General Configuration Screen.............................................................................................................3-38

3.6.8.1.2.2 Monitor Alarm Limit Configuration Screen.......................................................................................3-39

3.6.8.1.3 Monitor Commands ............................................................................................................................3-40

3.6.8.2 Monitor 1 & 2 Screens........................................................................................................................3-40

3.6.8.2.1 Monitor Data Screens..........................................................................................................................3-40

3.6.8.2.1.1 Integral Monitor Data Screen.............................................................................................................. 3 -41

3.6.8.2.1.2 Monitor Status Screen.........................................................................................................................3-42

3.6.8.2.2 Monitor Test Results Screens..............................................................................................................3-43

3.6.8.2.2.1 Completed Test Results ......................................................................................................................3-44

3.6.8.2.2.2 In Process Test Results .......................................................................................................................3-45

3.6.8.2.2.3 Monitor1>>Test Generator Screen .....................................................................................................3-46

3.6.8.2.3 Monitor Fault History Screens............................................................................................................3-47

3.6.8.2.3.1 Integral Monitor Fault History Screen................................................................................................3-47

3.6.8.2.3.2 Local Control Unit Fault History System Status Screen.....................................................................3-48

3.6.8.2.4 Monitor Offsets and Scale Factors......................................................................................................3-49

3.6.8.2.5 Monitor Test Signal Output Control...................................................................................................3-50

3.6.8.3 Transmitter Data Screens....................................................................................................................3-51

3.6.8.3.1 Transmitter Data Screen......................................................................................................................3-51

3.6.8.3.2 VOR Ground Check Data Screen .......................................................................................................3-52

3.6.8.3.3 VOR Ground Check Data Advanced Screen ......................................................................................3-53

iv Rev. - November, 2008

This document contains proprietary information and such information may not be disclosed

to others for any purposes without written permission from SELEX Sistemi Integrati Inc.

Model 1150A DVOR

TABLE OF CONTENTS (cont.)

ragraph

Pa

# Description Page #

3.6.8.3.4 Transmitter Status Screen ...................................................................................................................3-54

3.6.8.4 Transmitter Configuration Screens.....................................................................................................3-55

3.6.8.4.1 Nominal Configuration Screen ...........................................................................................................3-55

3.6.8.4.2 Transmitter Offsets & Scale Factors...................................................................................................3 -56

3.6.8.5 Transmitter Commands.......................................................................................................................3-57

3.6.8.6 Diagnostics Screen..............................................................................................................................3-58

3.6.8.6.1 Power-Up Diagnostics Results............................................................................................................3-58

3.6.8.6.2 Fault Isolation Test Results.................................................................................................................3-59

3.6.8.7 Controlling the Transmitter via the PMDT.........................................................................................3-60

3.6.8.7.1 General Transmitter Control...............................................................................................................3-60

3.6.8.7.2 Change the Azimuth Index..................................................................................................................3-60

3.6.8.7.3 Change the CSB Output Power...........................................................................................................3-60

3.6.8.7.4 Change the Voice Depth of Modulation .............................................................................................3-60

3.6.8.7.5 Change the Identification Depth of Modulation..................................................................................3-60

3.6.8.7.6 Change the Reference Depth of Modulation.......................................................................................3-61

3.6.8.7.7 Change the Sideband Power Level .....................................................................................................3-61

3.7 RMM...................................................................................................................................................3-61

3.8 CONTROLS AND INDICATORS.....................................................................................................3-62

3.8.1 POWER CONTROL PANEL............................................................................................................. 3 -62

3.8.2 LOCAL CONTROL UNIT (LCU) .....................................................................................................3-62

3.8.2.1 LCU Display Messages.......................................................................................................................3-63

3.8.2.1.1 Integral Monitor..................................................................................................................................3-63

3.8.2.1.2 Transmitter Power Supply and Temperature Monitor ........................................................................3-63

3.8.3 BCPS Asssembly Assembly (1A5A3, 1A5A4) ..................................................................................3-67

3.8.4 Carrier Amplifier Assembly (1A5A3, 1A5A4)...................................................................................3-68

3.8.5 Monitor CCA (1A3A3, 1A3A10).......................................................................................................3-69

3.8.6 Remote Monitoring System (RMS) CCA...........................................................................................3-70

3.8.7 Facilities CCA (1A3A7) .....................................................................................................................3-71

3.8.8 Synthesizer CCA (1A3A1, 1A3A11)..................................................................................................3-72

3.8.9 Sideband Generator Assembly (1A4A1, 1A4A2, 1A4A5, 1A4A6)....................................................3-73

3.8.10 Audio Generator CCA (1A3A2, 1A3A9) ...........................................................................................3-75

3.8.11 Low Voltage Power Supply (LVPS) CCA (1A3A4,1A3A8)..............................................................3-76

3.8.12 Test Generator CCA (1A3A5)............................................................................................................3-76

3.8.13 RF Monitor Assembly (1A4A4).........................................................................................................3-77

4 STANDARDS AND TOLERANCES..................................................................................................4-1

4.1 INTRODUCTION ................................................................................................................................4-1

5 PERIODIC MAINTENANCE..............................................................................................................5-1

5.1 INTRODUCTION ................................................................................................................................5-1

5.2 PERFORMANCE CHECK SCHEDULE.............................................................................................5-1

5.3 DoCUMENTATION AND DATA COLLECTION.............................................................................5-1

6 MAINTENANCE PROCEDURES ...................................................................................................... 6 -1

6.1 INTRODUCTION ................................................................................................................................6-1

6.1.1 Normal State Definition........................................................................................................................6-1

6.1.2 Bypass State..........................................................................................................................................6 -1

6.1.3 Turn OFF DVOR..................................................................................................................................6-1

6.1.4 Turn ON DVOR....................................................................................................................................6-1

6.1.5 Test Equipment.....................................................................................................................................6-1

6.2 PERFORMANCE CHECK PROCEDURES........................................................................................6-2

6.2.1 Battery Backup Transfer Performance Check.......................................................................................6-2

6.2.2 Carrier Output Power Performance Check............................................................................................6-2

6.2.3 Carrier Frequency Performance Check.................................................................................................6-2

Rev. - November, 2008

This document contains proprietary information and such information may not be disclosed

to others for any purposes without written permission from SELEX Sistemi Integrati Inc.

v

Model 1150A DVOR

TABLE OF CONTENTS (cont.)

Paragraph

# Description Page #

6.2.4 Monitor 30 Hz and 9960 Hz Modulation Percentage and Deviation Ratio Performance Check..........6-2

6.2.5 Modulation Frequency Performance Check..........................................................................................6-3

6.2.6 Antenna VSWR Performance Check....................................................................................................6-3

6.2.7 Automatic Transfer Performance Checks (Dual Equipment only) .......................................................6-3

6.2.8 VOR Monitor Performance Check........................................................................................................6-3

6.2.9 Monitor Integrity Test of VOR Monitor (Refer to Section 3.6.8.2.2)...................................................6-4

6.2.10 RSCU Operation Performance Check...................................................................................................6-4

6.2.10.1 Single Equipment Performance Check .................................................................................................6-4

6.2.10.2 Dual Equipment Performance Check...................................................................................................6-4

6.2.11 Identification Frequency and Modulation Level Checks......................................................................6-4

6.3 Equipment Inspection Procedures.........................................................................................................6-5

6.3.1 Site Inspection.......................................................................................................................................6-5

6.3.2 Inspection of Transmission Antennas...................................................................................................6-5

6.3.3 Inspection of the Field Monitor Antenna..............................................................................................6-5

6.3.4 Transmitter Cabinet Inspection.............................................................................................................6-6

6.3.5 Battery Backup Unit Inspection............................................................................................................6-6

6.4 ALIGNMENT PROCEDURES............................................................................................................6-6

6.4.1 Battery Charging Power Supply (BCPS) Alignment Procedures..........................................................6-6

6.4.1.1 System AC Voltage Alignment.............................................................................................................6-6

6.4.1.2 System AC Current Alignment .............................................................................................................6-6

6.4.1.3 Obstruction Light AC Voltage Alignment............................................................................................6-7

6.4.1.4 Obstruction Light AC Current Alignment ............................................................................................6-7

6.4.2 Alarm Volume Adjustment Procedure..................................................................................................6-8

6.4.3 RMS Facilities Exterior and Interior Temperature Calibration.............................................................6-8

6.4.4 Reassign Main/Standby Transmitters (Dual Systems Only).................................................................6-8

6.4.5 Verification of BITE VSWR Calibration..............................................................................................6-8

6.4.6 Verification of BITE Frequency Counter Calibration...........................................................................6-9

6.4.7 Verification of BITE Wattmeter Calibration ........................................................................................6-9

6.4.8 RMS Lithium Battery Check Procedure.............................................................................................6-10

6.4.9 Replacing RMS CPU (1A3A6) CCA..................................................................................................6 -10

6.4.10 Update of DVOR Software.................................................................................................................6-11

6.4.11 Changing the Station Rotation (Azimuth)...........................................................................................6-11

6.4.12 Changing the Monitoring Offsets........................................................................................................6-11

6.4.13 DME Keying Check............................................................................................................................6-12

6.4.14 DVOR Frequency Synthesizer Alignment..........................................................................................6-12

6.4.15 DVOR Sideband Amplifier Alignment...............................................................................................6-13

6.4.16 Antenna VSWR Check for New Frequency .......................................................................................6-14

7 CORRECTIVE MAINTENANCE .......................................................................................................7-1

7.1 INTRODUCTION ................................................................................................................................7-1

7.2 TEST EQUIPMENT REQUIRED........................................................................................................7-1

7.3 ON-SITE CORRECTIVE MAINTENANCE.......................................................................................7-1

7.3.1 General Troubleshooting Information...................................................................................................7-1

7.3.2 Test Point Waveform References..........................................................................................................7-1

7.4 OFFSITE REPAIR................................................................................................................................7-4

7.5 PACKING INSTRUCTIONS...............................................................................................................7-4

8 PARTS LIST.........................................................................................................................................8 -1

8.1 INTRODUCTION ................................................................................................................................8-1

9 INSTALLATION, INTEGRATION, AND CHECKOUT ...................................................................9-1

9.1 INTRODUCTION ................................................................................................................................9-1

9.2 SITE INFORMATION.........................................................................................................................9-1

9.2.1 Shelter Requirements............................................................................................................................9-1

vi Rev. - November, 2008

This document contains proprietary information and such information may not be disclosed

to others for any purposes without written permission from SELEX Sistemi Integrati Inc.

Model 1150A DVOR

TABLE OF CONTENTS (cont.)

ragraph

Pa

# Description Page #

9.3 UNPACKING AND REPACKING......................................................................................................9-1

9.3.1 Environmental Considerations..............................................................................................................9-1

9.4 INPUT Power REQUIREMENT SUMMARY.....................................................................................9-1

9.5 INSTALLATION PROCEDURES.......................................................................................................9-2

9.5.1 Tools and Test Equipment Required.....................................................................................................9-2

9.5.2 Counterpoise and Shelter Foundation Installation ................................................................................9-2

9.5.3 Shelter Installation................................................................................................................................9-4

9.5.4 Counterpoise Installation......................................................................................................................9-4

9.5.5 Initial Conditions ..................................................................................................................................9-5

9.5.6 Sideband Antenna Installation..............................................................................................................9-5

9.5.7 Carrier Antenna Installation..................................................................................................................9-5

9.5.8 Installation of Field Monitor Antenna...................................................................................................9-5

9.5.8.1 Installation of Obstruction Lights on Field Monitor Antenna Tower ...................................................9-5

9.5.9 Antenna Cable Exterior Cable Entrance Installation ............................................................................9-6

9.5.10 Air Conditioner Installation..................................................................................................................9-6

9.5.11 Transmitter Cabinet Installation............................................................................................................9-6

9.5.12 Battery Back Up Installation.................................................................................................................9-7

9.5.13 DC Voltage and Battery Installation.....................................................................................................9-7

9.5.14 AC Voltage Installation ........................................................................................................................9-7

9.5.15 Connecting DME Keyer Wiring...........................................................................................................9-8

9.5.16 RCSU and RMM Connections..............................................................................................................9-8

9.5.17 Obstruction Light Installation and Wiring............................................................................................9-9

9.5.18 Cutting Antenna Cables to Proper Electrical Length..........................................................................9-10

9.5.19 Tuning the Antennas...........................................................................................................................9-10

9.5.20 Sideband RF Feed Cables to Commutator Connections .....................................................................9-10

9.6 INSPECTION.....................................................................................................................................9-11

9.6.1 Visual Inspection ................................................................................................................................9-11

9.7 INITIAL STARTUP AND PRELIMINARY TESTING....................................................................9-12

9.7.1 Input Voltage Checks..........................................................................................................................9-12

9.7.2 Installing Modules in Transmitter Cabinet..........................................................................................9-12

9.7.3 Turn on Procedure...............................................................................................................................9-12

9.7.4 PMDT Hookup and Setup...................................................................................................................9-12

9.7.5 Site Adjustments and Configurations..................................................................................................9-13

9.7.6 DVOR Station Power-Up....................................................................................................................9-16

9.7.7 Log-On Procedure...............................................................................................................................9-16

9.7.8 Setting Date and Time.........................................................................................................................9-16

9.7.9 Setting Station's Descriptor.................................................................................................................9-16

9.7.10 Password Change................................................................................................................................9-16

9.7.11 Setting System Configuration.............................................................................................................9-16

9.7.12 Transmitter Tuning Procedures........................................................................................................... 9 -16

9.7.12.1 Checking Output Frequency of Frequency Synthesizer......................................................................9-16

9.7.12.2 Amplitude Adjustment........................................................................................................................9-16

9.7.12.3 Sideband Generator Phasing...............................................................................................................9-18

9.7.13 Setting Transmitter Operating Parameters..........................................................................................9 -19

9.7.13.1 Setting Transmitter Ident Code...........................................................................................................9-19

9.7.13.2 Setting Transmitter Voice Modulation................................................................................................9-19

9.7.13.3 Setting Transmitter Ident Modulation.................................................................................................9-19

9.7.13.4 Setting Transmitter Reference Modulation.........................................................................................9-20

9.7.13.5 Reference to Sideband Phasing...........................................................................................................9-20

9.7.13.6 Setting Transmitter SBO Modulation.................................................................................................9-21

9.7.13.7 Setting Transmitter Azimuth (Az) Index ............................................................................................9-21

Rev. - November, 2008

This document contains proprietary information and such information may not be disclosed

to others for any purposes without written permission from SELEX Sistemi Integrati Inc.

vii

Model 1150A DVOR

TABLE OF CONTENTS (cont.)

Paragraph

# Description Page #

9.7.13.8 Saving No. 1 Transmitter Operating Parameters.................................................................................9-21

9.7.14 Setting Monitor Alarm Limits.............................................................................................................9-21

9.7.14.1 Setting Monitor Az Angle Low Limit.................................................................................................9-21

9.7.14.2 Setting Monitor Az Angle High Limit................................................................................................9-22

9.7.14.3 Setting High Monitor 30 Hz Mod Low Limit.....................................................................................9-22

9.7.14.4 Setting Monitor 30 Hz Mod High Limit.............................................................................................9-22

9.7.14.5 Setting Monitor 9960 Hz Mod Low Limit..........................................................................................9-22

9.7.14.6 Setting Monitor 9960 Hz Mod High Limit.........................................................................................9-22

9.7.14.7 Setting Monitor 9960 Hz Dev Low Limit...........................................................................................9-22

9.7.14.8 Setting Monitor 9960 Hz Dev High Limit..........................................................................................9-23

9.7.14.9 Setting Monitor Field Intensity Low Limit.........................................................................................9-23

9.7.14.10 Setting Monitor Field Intensity High Limits.......................................................................................9-23

9.7.15 Records ...............................................................................................................................................9-23

9.8 INSTALLATION VERIFICATION TEST........................................................................................9-23

9.8.1 Special Tests .......................................................................................................................................9-23

10 SOFTWARE.......................................................................................................................................10-1

10.1 INTRODUCTION ..............................................................................................................................10-1

11 TROUBLESHOOTING SUPPORT ...................................................................................................11-1

11.1 INTRODUCTION ..............................................................................................................................11-1

viii Rev. - November, 2008

This document contains proprietary information and such information may not be disclosed

to others for any purposes without written permission from SELEX Sistemi Integrati Inc.

Model 1150A DVOR

LIST OF FIGURES

gure #

Fi

Description Page #

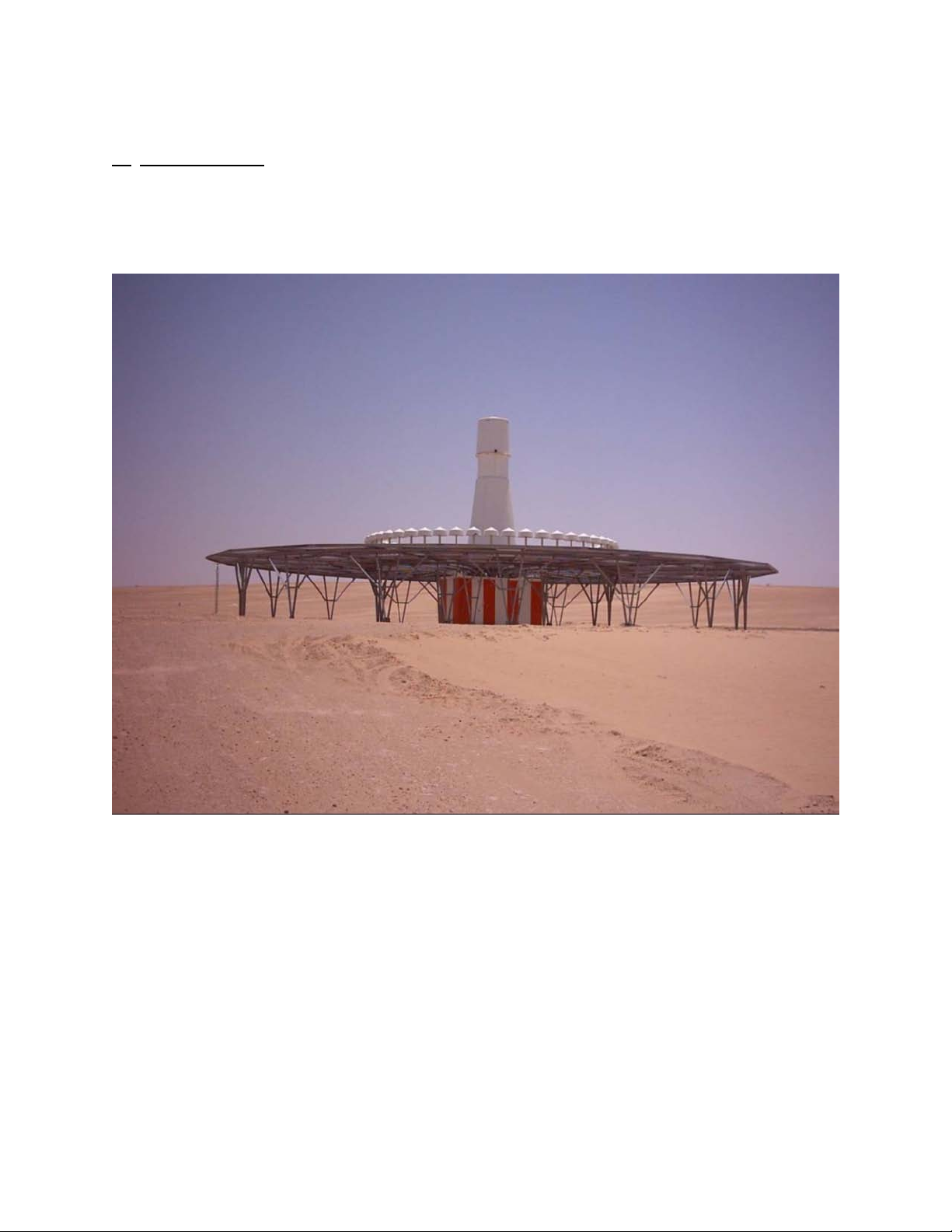

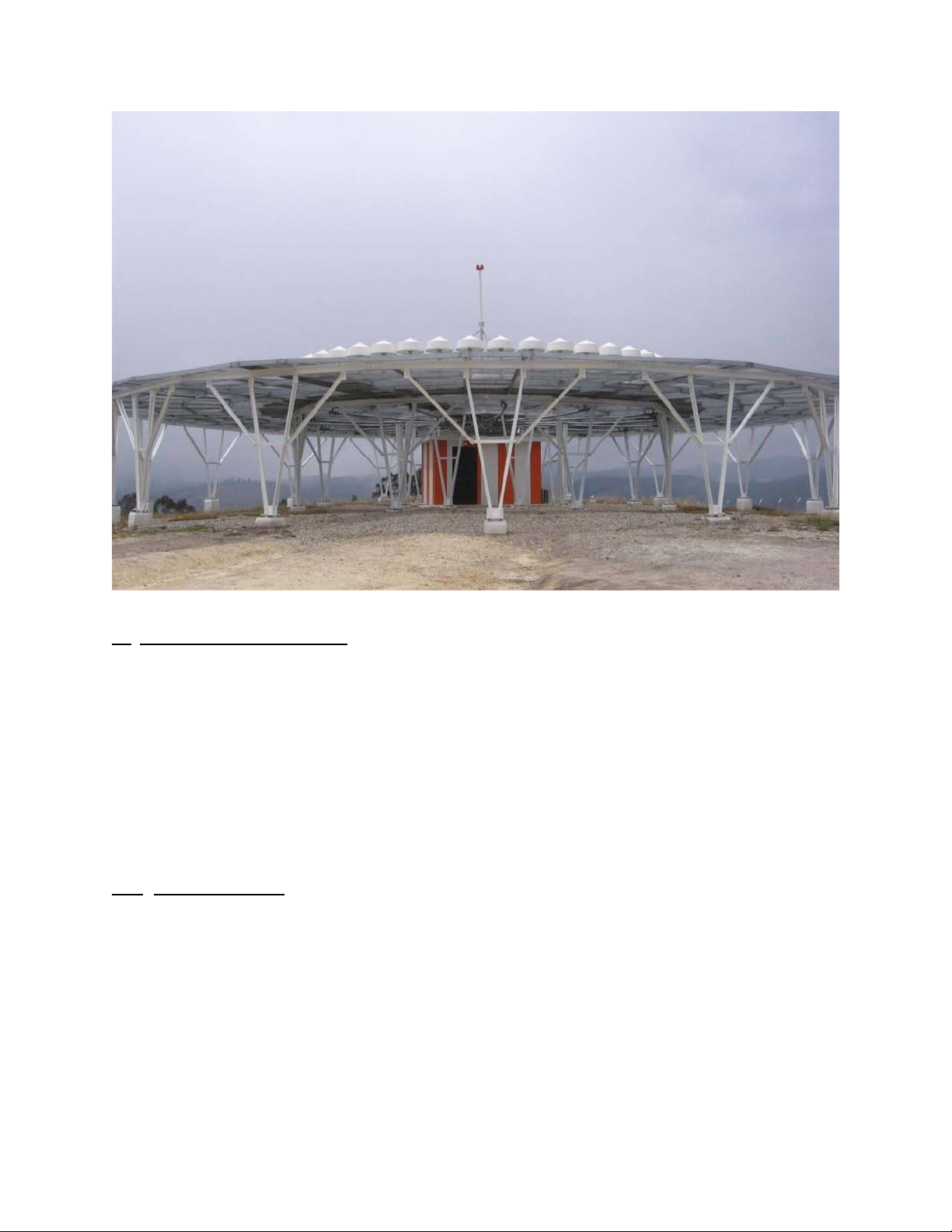

Figure 1-1 Dual Doppler VHF Omni-range (DVOR ) Station wi th TACAN..........................................................................1-1

Figure 1-2 Dual Doppler VHF Omni-range (DVOR ) Station wi th DME...............................................................................1-2

Figure 1-3 Location of Major Assem blies in th e Electroni cs Cabin et (Fron t View )...............................................................1-4

Figure 1-4 Location of Major Assem blies in th e Electroni cs Cabin et (Rea r View )................................................................1-5

Figure 1-5 Location of Commutator (1A10) A ss embly in th e Electron ics Cabine t (Lef t Side Vi ew)...................................1-6

Figure 1-6 Location of Commutator (1A11) A ss embly in th e Electron ics Cabine t (Rig ht S ide View).................................1-6

Figure 1-7 Carrier Antenna for collocati on w ith DME/ TACAN...........................................................................................1-10

Figure 1-8 Carrier Antenna without DM E/TACAN...............................................................................................................1-11

Figure 1-9 Sideband Antenna...................................................................................................................................................1-12

Figure 1-10 Balun, Tuning Stub, and Positioning Piece...........................................................................................................1-13

Figure 1-11 Antenna Pedestal and Radome Diagram...............................................................................................................1-14

Figure 1-12 DVOR Field Monitor Dipole Antenna..................................................................................................................1-15

Figure 2-1 RF Spectrum of a Doppler VOR........................................................................................................ ......................2-2

Figure 2-2 Simplified DVOR Control an d Monitorin g Block Di agram..................................................................................2-4

Figure 2-3 Simplified DVOR Transmitter Block Diag ram......................................................................................................2-5

Figure 2-4 Synthesizer Block Diagram......................................................................................................................................2-8

Figure 2-5 Carrier RF Generation Loop..................................................................................................................................2-10

Figure 2-6 Carrier Phase Control Loop....................................................................................................................................2-12

Figure 2-7 Sideband RF Generation Loop...............................................................................................................................2-14

Figure 2-8 Audio Generator CCA Block Dia gram.................................................................................................................2-17

Figure 2-9 Carrier Amplifier Assem bly Block D iagram........................................................................................................2-20

Figure 2-10 Sideband Generator Block Diagram......................................................................................................................2-23

Figure 2-11 RF Monitor Assembly Block Diagram .................................................................................................................2-28

Figure 2-12 RMS CCA Block Diagram....................................................................................................................................2-31

Figure 2-13 Facilities CCA Block Diagram..............................................................................................................................2-35

Figure 2-14 Interface CCA Block Diagram...............................................................................................................................2-39

Figure 2-15 AC Power Monitor Block Diagram.......................................................................................................................2-42

Figure 2-16 LCU Simplified Block Diagram............................................................................................................................2-43

Figure 2-17 LCU Block Diagram ..............................................................................................................................................2-44

Figure 2-18 Test Generator CCA Block Diagram.....................................................................................................................2-48

Figure 2-19 LVPS CCA Block Diagram...................................................................................................................................2-51

Figure 2-20 Monitor CCA, Block Diagram...............................................................................................................................2-54

Figure 2-21 Monitor Receiver, Block Diagram.........................................................................................................................2-55

Figure 2-22 Monitor DSP (U75) Signal Processing Diagram..................................................................................................2-58

Figure 2-23 Monitor DSP (U6) Signal Processing Diagram....................................................................................................2-60

Figure 2-24 Fanless BCPS CCA Block Diagram......................................................................................................................2-62

Figure 2-25 Extender Board.......................................................................................................................................................2-66

Figure 2-26 Commutator Control CCA, Block Diagram..........................................................................................................2-68

Figure 2-27 Commutator CCA, Block Diagram.......................................................................................................................2-74

Figure 3-1 PMDT Opening Screen with “Sidebar” Data................................................................................................ ..........3-4

Figure 3-2 PMDT Configuration Screen...................................................................................................................................3-6

Figure 3-3 PMDT System Directory..........................................................................................................................................3-7

Figure 3-4 PMDT Login Prompt...............................................................................................................................................3-8

Figure 3-5 VOR Status Screen...................................................................................................................................................3-9

Figure 3-6 Monitor/Transmitter Status Screen........................................................................................................................3-10

Figure 3-7 Software Revisions Screen.....................................................................................................................................3-11

Figure 3-8 Hardware Revisions Screen...................................................................................................................................3-12

Figure 3-9 RMS Maintenance Alerts/Al arms Screen.............................................................................................................3-13

Figure 3-10 RMS Power Supply Data Screen...........................................................................................................................3-14

Figure 3-11 RMS Digital I/O Data Screen ................................................................................................................................3-15

Figure 3-12 RMS Temperature Data Screen.............................................................................................................................3-16

Rev. - November, 2008

This document contains proprietary information and such information may not be disclosed

to others for any purposes without written permission from SELEX Sistemi Integrati Inc.

ix

Model 1150A DVOR

LIST OF FIGURES (cont.)

Figure #

Description Page #

Figure 3-13 RMS A/D Data Screen...........................................................................................................................................3-17