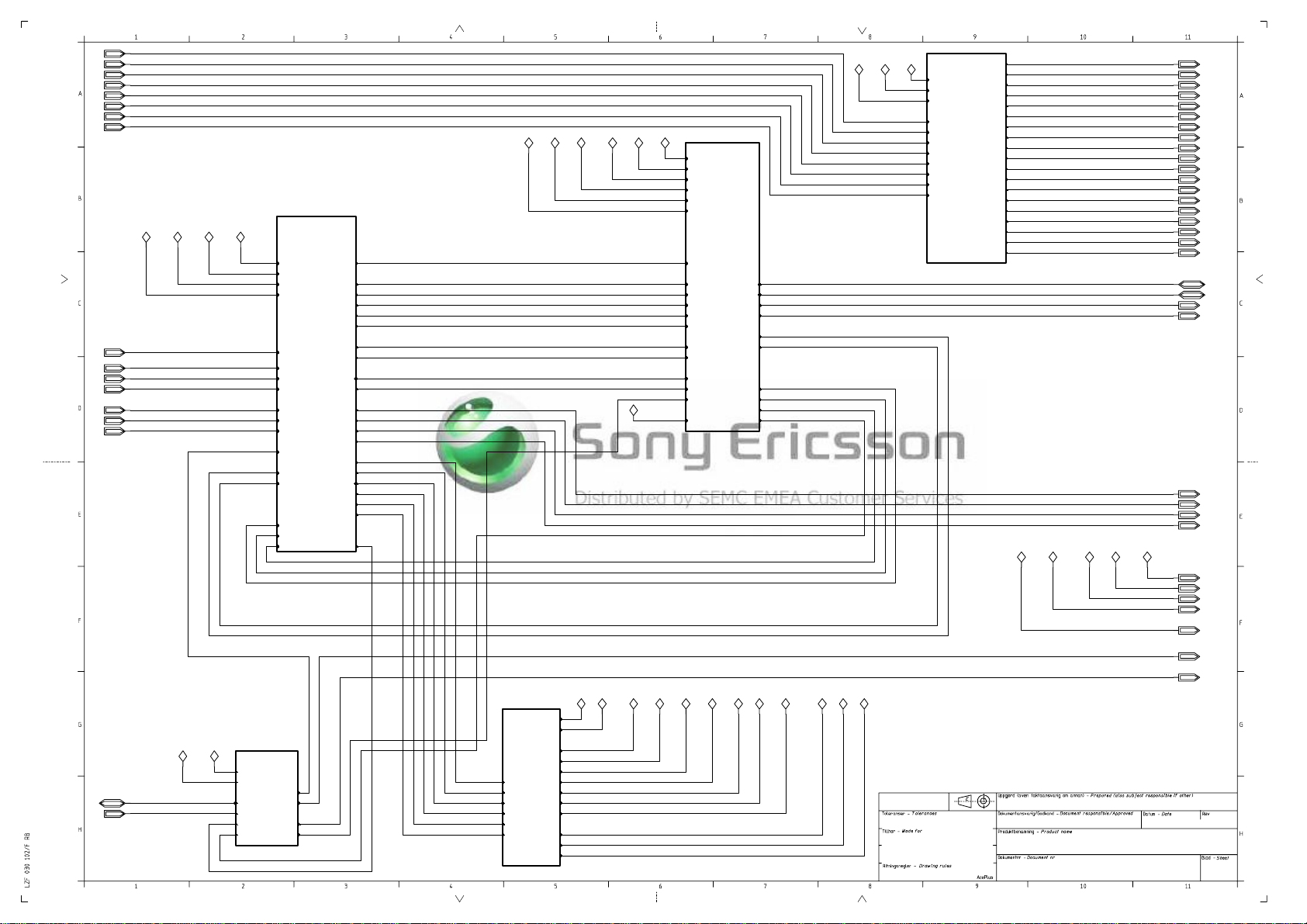

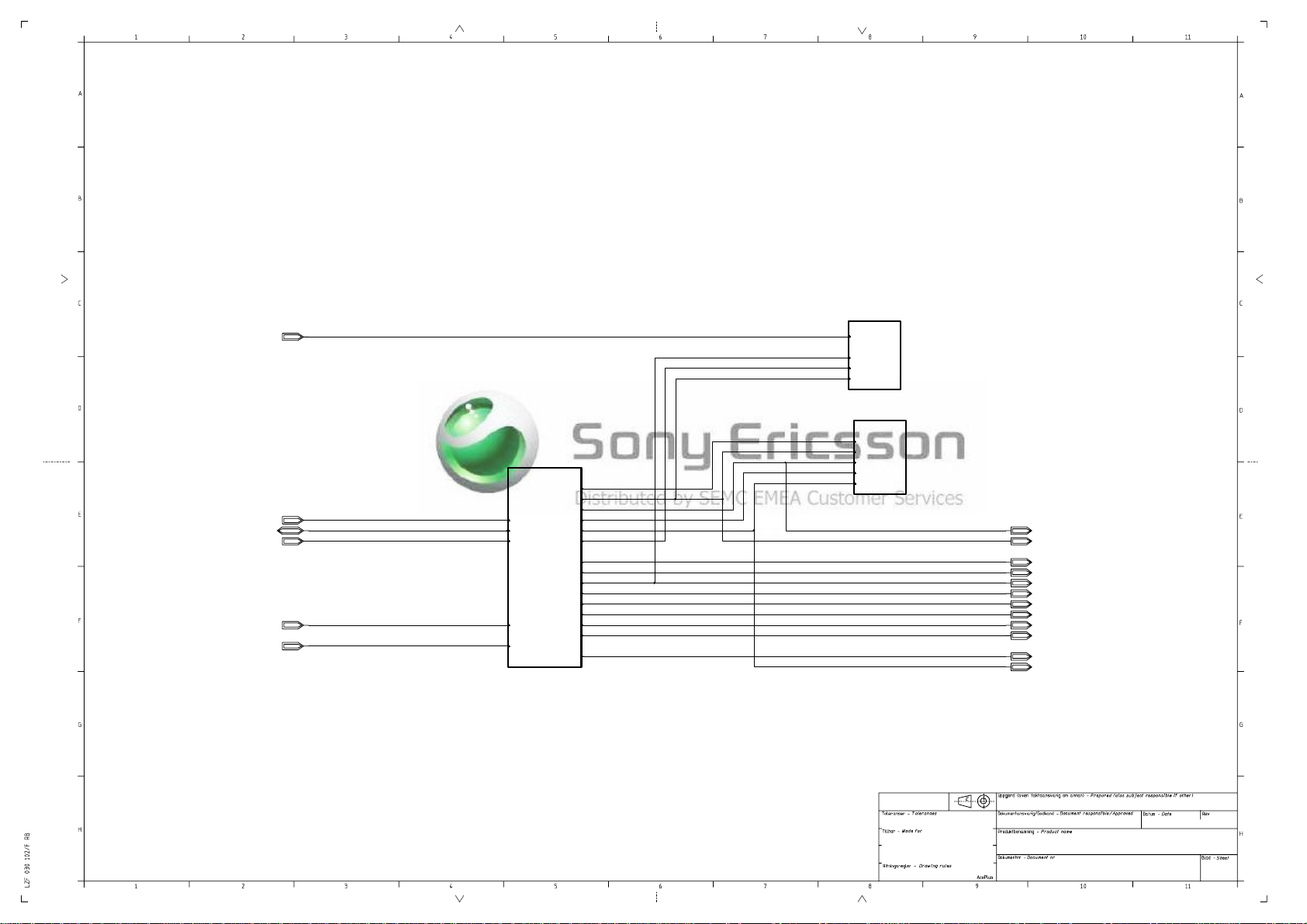

SE K610, V630 Schematic

RXQB

RXQA

RXIB

RXIA

IDATA

QDATA

DCLK

TESTOUT

BTAN T

VLOOP

RTEMP

WRFLOOP

BTCLKREQ

BTRX

BTCTS

CLKREQ

MCLK

RXQB

RXQA

RXIB

RXIA

IDATA

QDATA

DCLK

TESTOUT

VCAM12

VCAM18

VDIG

VDDE18

VMSPICO

VBACKUP

BTANT

VLOOP

RTEMP

WRFLOOP

BTCLKREQ

BTRX

BTCTS

MEMRESn

VAD

FLASH_STROBE

SPL

SPR

MIDREF

Operation & Services

Operation & Services

MEMRESn

BTRE Sn

RTCCLK

CAMSYSCL K

SERVICEn

Pages 9-14Pages 9-14

CAMSYSCLK

MPX1_RST

MPX1_OFF

VGA_OFF

KBDIM

NAVDIM

AMPCTRL

MICN/AUXinR

MICP/AUXinL

I2CDAT1

I2CCLK1

BTRTS

WPAREF

VCXOC ONT

VBUS

DCIO_O N

VBT_EN

CAM_27_EN

SERVICEn

BTTX

DCIO

MPX1_RST

MPX1_OFF

VGA_OFF

KBDIM

NAVDIM

AMPCTRL

MICN/AUXinR

MICP/A UXinL

I2CDAT1

I2CCLK1

BTTX

BTRTS

WPAREF

VCXOCONT

VPP

VBUS

DCIO

DCIO_ON

VBT_ EN

CAM_27_EN

CAMSYSCLK

Pages 5-8

Pages 5-8

VPP

VBUS

DCIO

DCIO_ON

VBT_EN

CAM_27_EN

Power

Power

VBATI VDIG VBT27 VDDE18 VBACKUP VCAM27 VMSPICO DCIOint VRTC13

VBATI

VDIG

VBT2 7

VDDE18

VBACKUP

VCAM27

VCAM12

VCAM18

VMSPICO

DCIOint

VRTC1 3

VCORE15

VPP

VDIGVDDE18VMSPICOVBACKUP

BTANT

VLOOP

RTEMP

WRFLOOP

BTCLKREQ

BTRX

BTCTS

VDDE18VCORE15

Pages 2-4Pages 2-4

VDDE18

VCORE15

CLKREQ

MCLK

SERVICEn

ONSWAn

System Control

System Control

DCIOint

VBATIVDIGVCAM27VDDE1 8

VBATI

VDIG

VCAM27

VCAM12

VCAM18

VDDE18

MPX1_RST

MPX1 _OFF

VGA_ OFF

KBDIM

NAVDIM

AMPCTRL

MICN/AUXinR

MICP/AUXinL

I2CDAT1

I2CCLK1

CAMSYSCLK

DCIOint

MMIMMI

FLASH_STROBE

BTRESn

RTCCLK

Pages 18-22

Pages 18-22

FLASH_STROBE

BTTX

BTRTS

WPAREF

VCXOCONT

ONSWA

MIDREF

SPR

SPL

VAD

PCMDAT A

PCMDAT B

PCMSYN

PCMCLK

MIDREF

ONSWA

VCAM12

VAD

SPL

SPR

VCAM18

VCORE15

VCORE15

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

Logic Top

Pages 1 5-17

Pages 1 5-17

VDIGVDDE1 8

VDIG

VDDE18

VCORE15

RXQB

RXQA

RXIB

RXIA

IDATA

QDATA

DCLK

TESTOUT

UMTS Ac cess

UMTS Ac cess

WSTR

WDAT

WCLK

TXQB

TXQA

RADSTR

RADDAT

RADCLK

TXON

MODA

MODB

MODC

MODD

ANTS W0

ANTS W1

ANTS W2

ANTS W3

TXIA

TXIB

PCMDATA

PCMDATB

PCMSYN

PCMCLK

VDDE1 8

WSTR

WDAT

WCLK

TXQB

TXQA

TXIA

TXIB

RADSTR

RADDAT

RADCLK

TXON

MODA

MODB

MODC

MODD

ANTSW0

ANTSW1

ANTSW2

ANTSW3

VRTC13

VDIGVBT27

RADSTR

RADDAT

RADCLK

ANTSW0

ANTSW1

ANTSW2

ANTSW3

PCMDAT A

PCMDAT B

PCMSYN

PCMCLK

WPAREF

VCXOCONT

VBATI

VRTC13

VDDE18

BTRE Sn

RTCCLK

WSTR

WDAT

WCLK

TXQB

TXQA

TXON

MODA

MODB

MODC

MODD

BTRTS

VBATI

VBT27

BTTX

VDIG

TXIA

TXIB

DIAGRAMSCHEMA

SEMCJ/ Kiyotaka Yamanoi

SEMCJ/ Daisuke Katayama

2006/06/09

E

THELMA

2/1911-ROA 128 1740/2

01 of 22

VDDE1 8

VCORE 15

CLKREQ

MCLK

SERVIC En

ONSWAn

VDDE18 V CORE15 VDDE18VCORE15

CLKREQ

MCLK

SERVIC En

ONSWAn

VDDE18

VCORE15

CLKREQ

MCLK

SERVICEn

ONSWAn

Clocks & Resets

Clocks & Resets

Page 4

Page 4

Test

Test

Page 3

Page 3

CAMSYSCLK

RTCCLK

MEMRESn

BTRESn

RTCCLK

CAMSYSCLK

MEMRESn

BTRESn

RTCCLK

CAMSYSCL K

MEMRESn

BTRE Sn

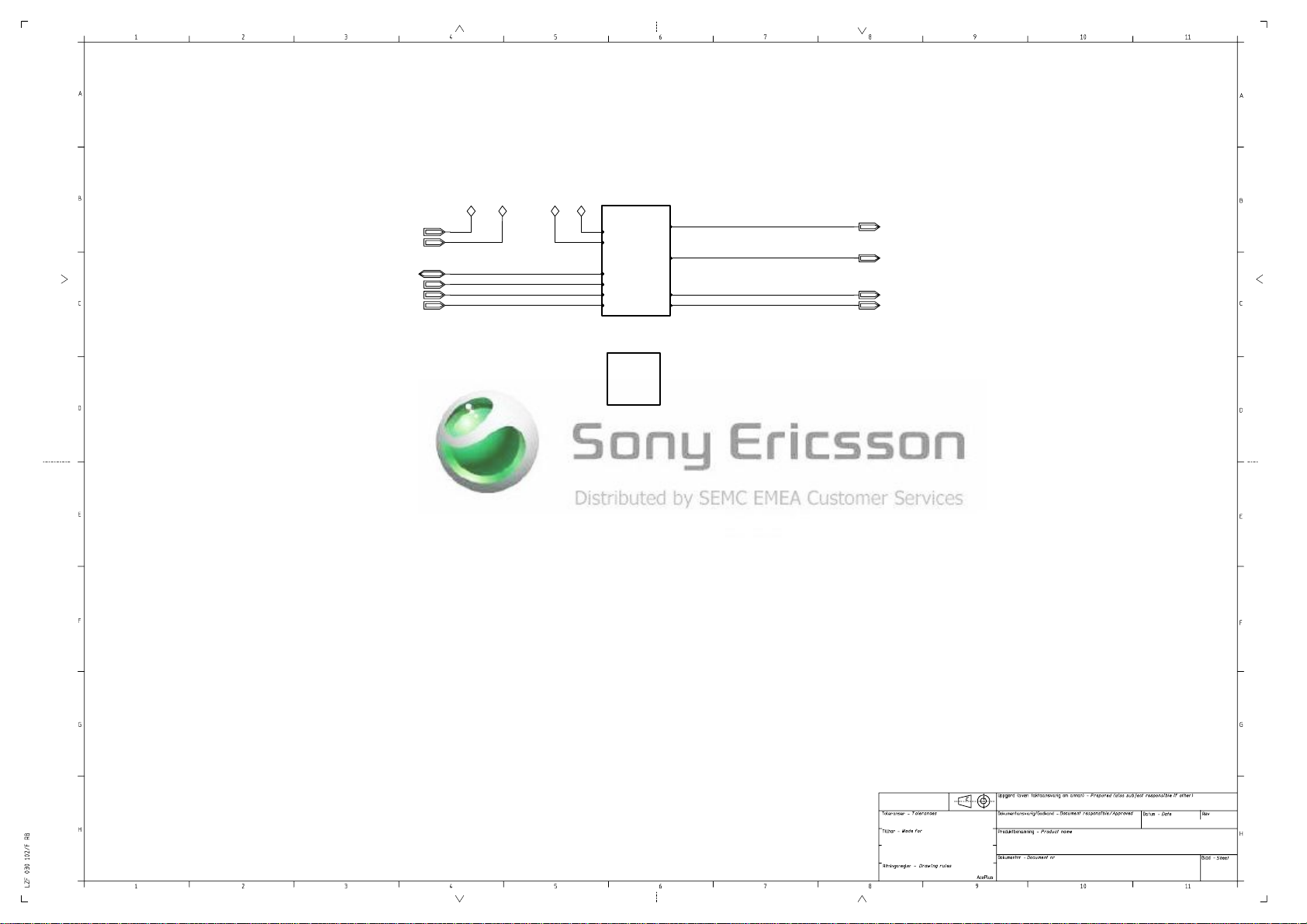

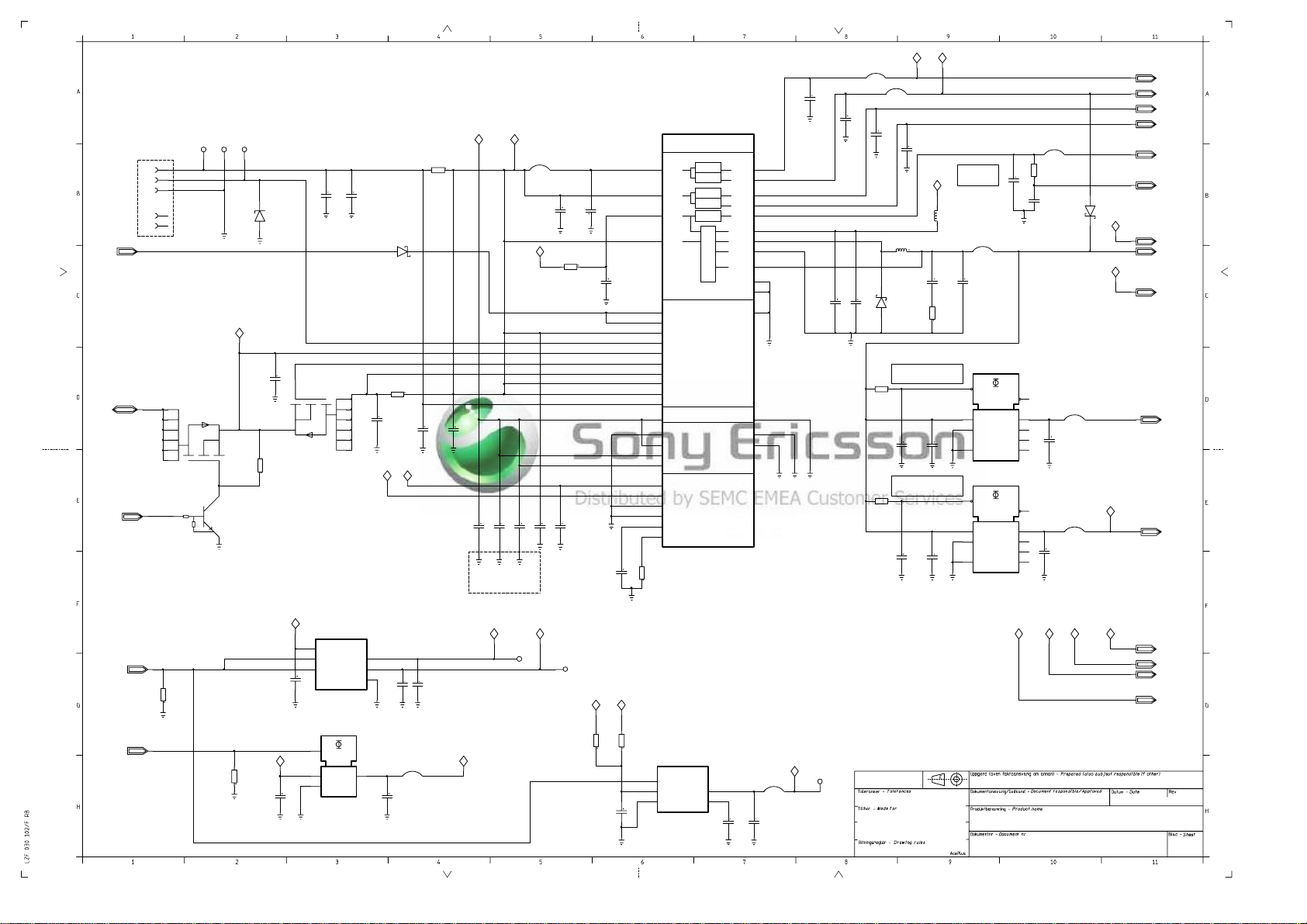

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

System Control

Top

SEMCJ/ Kiyotaka Yamanoi

SEMCJ/ Daisuke Katayama

THELMA

2/1911-ROA 128 1740/2

DIAGRAMSCHEMA

2006/06/09

E

02 of 22

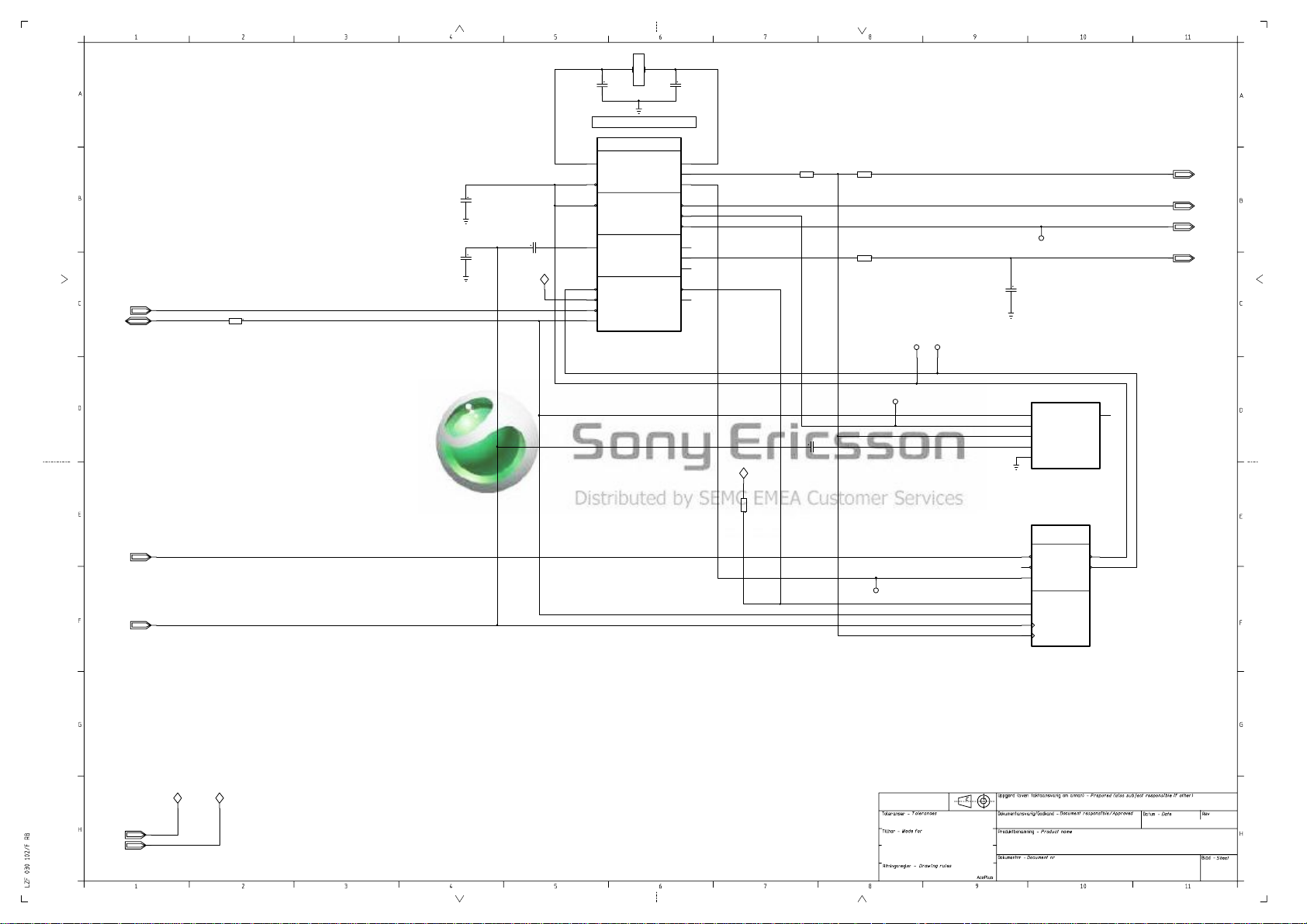

SERVI CEn

CLKREQ

ONSWAn

MCLK

Actual ne t on syst em

connect or page. . .

R2102

100ohms

B2100

RTM501911/ 2

R1A

C2C1

C2102

22pF

C2104

1nF

C2104 & C2106 mounted c l os e to D2000

C2106

NM

10pF

SERVIC En

CLKREQ_1

MCLK MCLK

C2100

1nF

AA15

VDDE1 8

32768k

Connect to ground pl ane in one s ingle point

D2000

MARIKA_SYSTEM_CONTROL

RTC

RTCIN

R14

RTCBDIS_ N

Y16

RESPOW_N

MCLK

J2

IRQ0_N

K4

IRQ1_N

J8

SERVIC E_N

V19

CLKREQ

DB2021_MARIKA_S ECURITY_EFUSE

ROP1013083/ 4

Reset s

Clocks

Control

RTCDCON

RESOUT0 _N

RESOUT1 _N

RESOUT2 _N

SYSCLK 0

SYSCLK 1

SYSCLK 2

PWRREQ0 _N

PWRREQ1

RTCOUT

RTCCLK

C2103

22pF

W17AA17

W15

R13

J7

W21

J1

V21

T19

R18

U19

W20

R2A

VCORE 15

R2101

100Kohms

R2100

0ohms

C2101

1nF

R2105

10Kohms

R2104

47ohms

R2104 moun ted

close to D2 000

SP2100

SP2101

SP2103SP 2102

RTCCLK

MEMRESn

BTRESn

CAMSYSCL K

PWR_ IRQ

PWRRST

CLKREQ_1

WANDARESn

RTCCLK_1

MCLK_WANDA

ONSWAnONSWAn

RTCDCON

PWRREQn

CLKR EQ_1

RTCCLK_1

C2105

15pF

<NM>

T15

N13

T16

U13

R15

C10

SP2105

D2001

EMP_WANDA_SYSTEM_IF

CLKRQ

RESET

CLK32

MCLK

HCLK

ROP1013044/ 4

N2000

ERICSSON AB 2010

SYSTEM CONTROL

POWER ON/RESET

C4

ONSWA

C5

ONSWB

A7

ONSWC

CONTROL

SLEEP

K3

CLKREQ

K9

MCLK

M1

XTAL1

ERICSSON_AB201 2

ROP1013066 /6

PWRRST

ID_BAL L

IRQ

R1A

RTCCLK

MEMRE Sn

BTRESn

CAMSYSCLK

D4

R1A

B8

C1

VDDE18

VCORE 15

VDDE18 VCORE15

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

System Control

Clocks & Resets

SEMCJ/ Kiyotaka Yamanoi

SEMCJ/ Daisuke Katayama

THELMA

2/1911-ROA 128 1740/2

DIAGRAMSCHEMA

2006/06/09

E

03 of 22

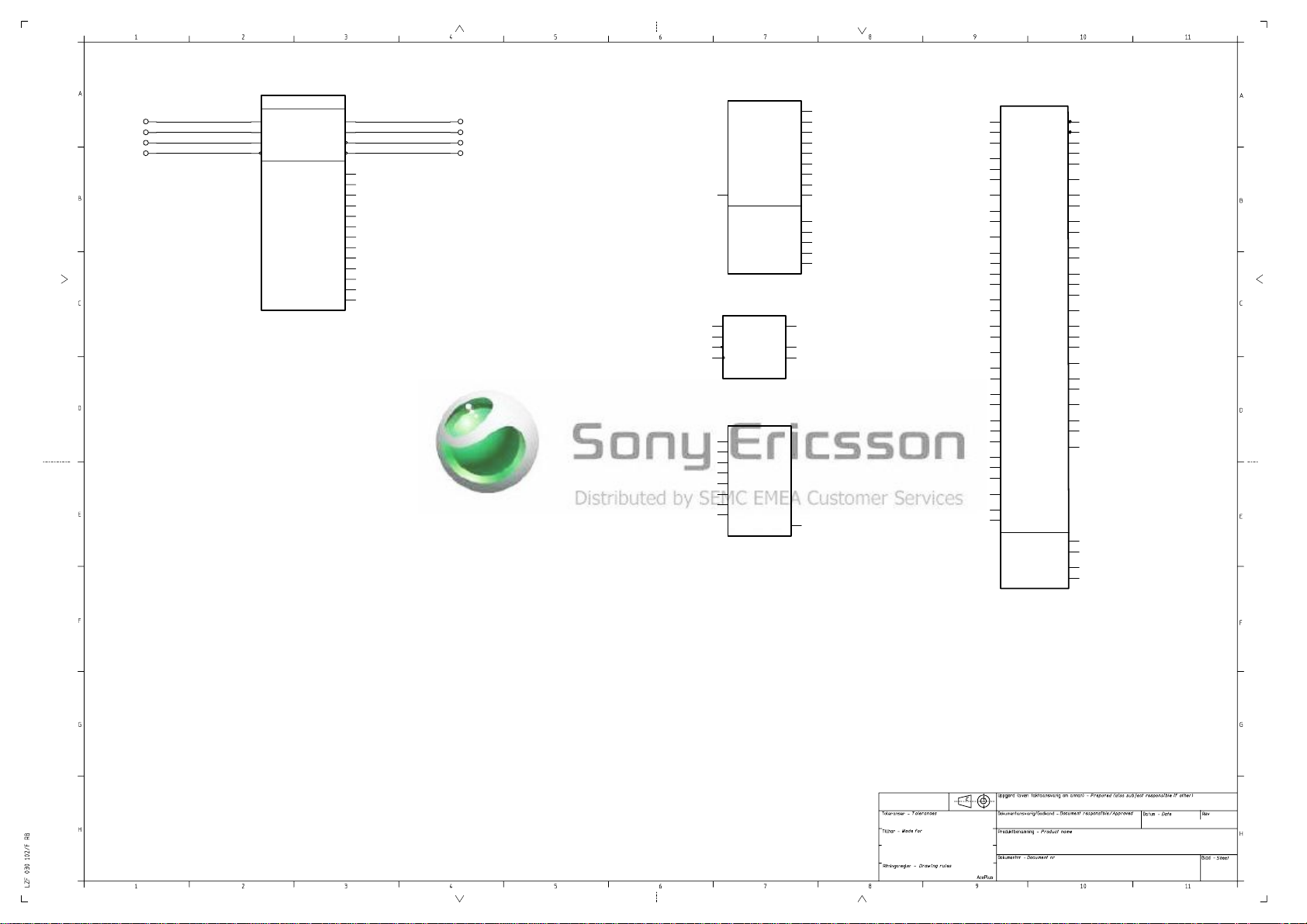

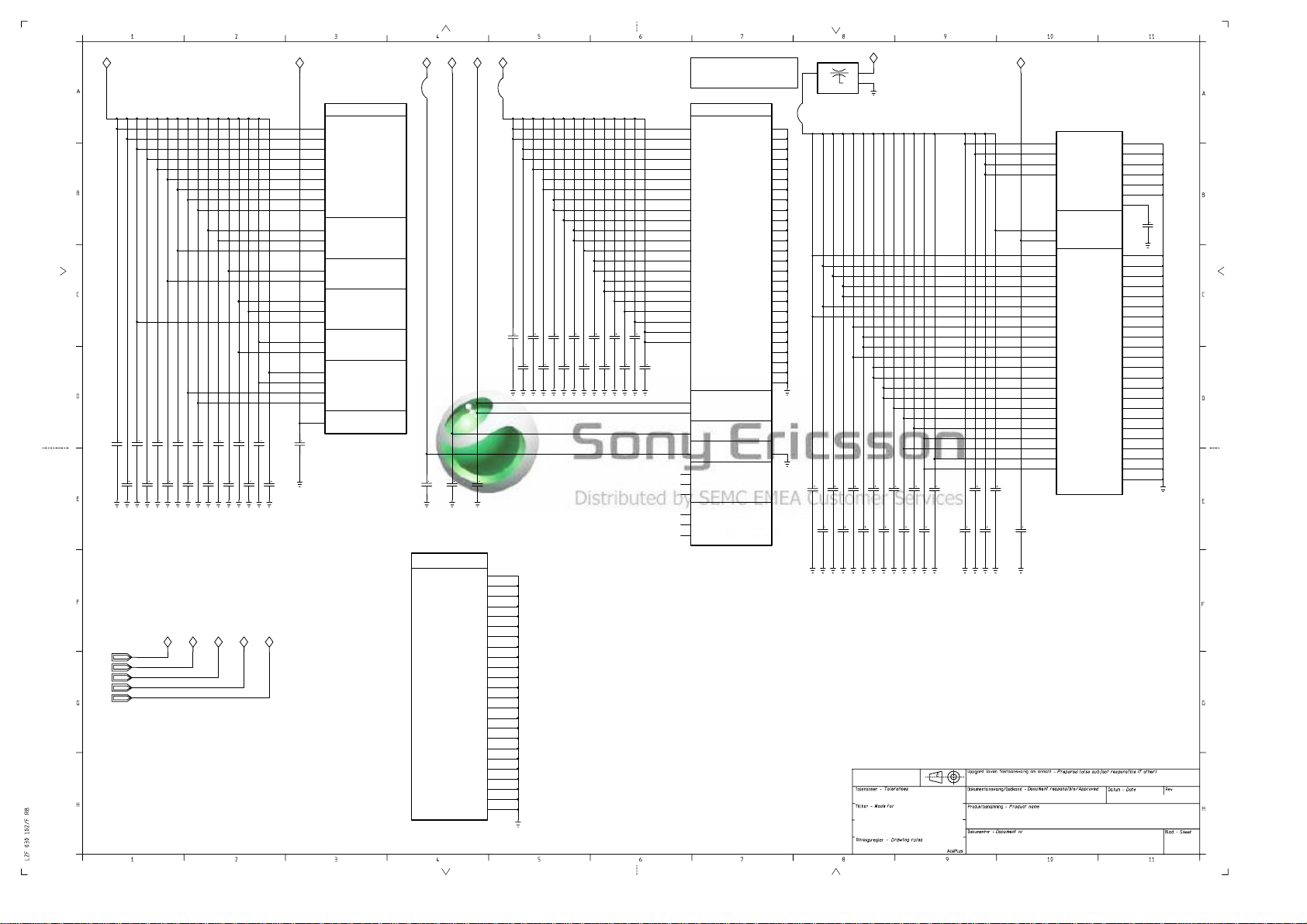

SP2106

SP2107

SP2108

SP2109

MARIKA_TDI

MARI KA_T MS

MARIKA_TCK

MARIKA_TRSTn

D2000

MARIKA _TEST_ AND_EMUL ATION

JTAG_IF

TDI

R19

TMS

V20

TCK

P18

TRST_N

ETM_IF

DB2021_ MARIKA_SECURITY_EFUSE

ROP1013083/ 4

RTCK

TEMU0_N

TEMU1_N

ETMPSTAT0

ETMPSTAT1

ETMPSTAT2

ETMTSYNC

ETMTCLK

ETMTPKT0

ETMTPKT1

ETMTPKT2

ETMTPKT3

ETMTPKT4

ETMTPKT5

ETMTPKT6

ETMTPKT7

D2001

TDO

R2A

MARI KA_R TCK

T21

MARIKA _TEM U0n

P19

MARIKA _TEM U1n

T20

M15

L19

M14

M20

L18

L15

L20

L14

K20

J20

K19

H20

K15

MARIKA_T DO

U20P14

SP2110

SP2111

SP2112

SP2113

EMP_WANDA_SWDEBUG

UART_RX

DSP INTERRU PT

ROP1013044/ 4

D2001

EMP_WANDA_TEST_IF

JTAG_TDI

JTAG_TMS

JTAG_TRSTN

JTAG_TCK

ROP1013044/ 4

D2001

EMP_W ANDA _MOD E_SEL

C17

BOOTMODE0

B17

BOOTMODE1

E13

BOOTMODE2

C15

BOOTMODE3

D15

TESTMODE

E11

ANALOG_ENABLE

C11

APLL_BYPASS

A11

CS_BYPASS

ROP1013044/ 4

JTAG_TDO

APLL_ATEST1

G15

G16

G17 E15

GPO0

GPO1

GPO2

GPO3

GPO4

GPO5

GPO6

GPO7

UART_T X

CPU_IACK

CPU_XF

CPU_IRQ1

CPU_IRQ0

CPU_CLKOUT

EMU0

EMU1

R1A

R1A

L17

K13

K15

K16

J15

J13

H15

H13

E12C13

N6

R5

N7

R6

M17

R1A

G13F16

F13

U12

D2001

Wanda_Ex ternal_ME M_IF

C2

EMIF_D0

C1

EMIF_D1

F5

EMIF_D2

E3

EMIF_D3

G5

EMIF_D4

E1

EMIF_D5

F2

EMIF_D6

F1

EMIF_D7

G3

EMIF_D8

G2

EMIF_D9

H5

EMIF_ D10

H1

EMIF_ D11

H2

EMIF_ D12

J2

EMIF_D13

J3

EMIF_D14

J5

EMIF_D15

K3

EMIF_D16

K5

EMIF_D17

K1

EMIF_D18

L1

EMIF_ D19

L3

EMIF_D20

M2

EMIF_D21

L5

EMIF_D22

N1

EMIF_D23

M3

EMIF_D24

M5

EMIF_ D25

P2

EMIF_D26

P3

EMIF_D27

R2

EMIF_D28

T1

EMIF_D29

N5

EMIF_D30

U1

EMIF_D31

ROP1013044 /4

EMIF_AWE

EMIF_ ARE

EMIF_ARE_ADY

EMIF_A1

EMIF_A2

EMIF_A3

EMIF_A4

EMIF_A5

EMIF_A6

EMIF_A7

EMIF_A8

EMIF_A9

EMIF_A10

EMIF_A11

EMIF_A12

EMIF_A13

EMIF_A14

EMIF_A15

EMIF_A16

EMIF_A17

EMIF_A18

EMIF_A19

EMIF_A20

EMIF_A21

EMIF_A22

EMIF_A23

EXT_MEM_ UBUS10

EXT_MEM_ UBUS11

EXT_MEM_ UBUS12

EXT_FRAME_STROBE

U3

T3

U2

E10

A10

C10

B9

C9

E9

C8

E8

A8

A7

C7

B6

E7

A5

C6

E6

B4

C4

B3

A2

A1

E5

B2

N12

T14

R14

E17

R1A

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

SEMCJ/ Kiyotaka Yamanoi

BASEBAND

System Control

Test

THELMA

2/1911-ROA 128 1740/2

DIAGRAMSCHEMA

2006/06/09SEMCJ/ Daisuke Katayama

E

04 of 22

VPP

VPPVPP

VBATI

VCORE18

VDDE18

VPP

VBATI

VCORE 18

VDDE1 8

Memories

Memories

Page 8P age 8

VBUS

DCIO

DCIO_O N

CAM_27_EN

VBT_E N

VBUS

DCIO

DCIO_ON

CAM_27_EN

VBT_EN

Page 6

Page 6

VBUS

DCIO_O N

CAM_27_EN

VBT_ EN

Regulat or s & Chargi ng

Regulat or s & Chargi ng

VDDF13

VDDE1 8

VRTC13

VCORE13

VCORE15DCIO

VCORE18

VBT27

VBACKUP

VBATI

VCAM27

VCAM12

VCAM18

VMSPICO

DCIOint

VDDF13

VDDE1 8

VRTC13

VCORE 13

VCORE 15

VDDE1 8

VBT27

VBACKUP

VBATI

VDIG

VDIG

VCAM27

VCAM12

VCAM18

VMSPICO

DCIOint

Page 7Page 7

VDDF13

VDDE18

VRTC13

VCORE13

VCORE15

Power Asi c s

Power Asi c s

Confidential

Approved according to 00021-LXE 107 42/1

Sony Ericsson

BASEBAND

Power

Top

VRTC13

VDDE1 8

VBT2 7

VBACKUP

VBATI

VDIG

VCAM27

VCAM12

VCAM18

VMSPICO

DCIOint

VCORE15

SEMCJ/ Yoshikazu Sakamoto

SEMCJ/ Daisuke Katayama

THELMA

2/1911-ROA 128 1740/2

DIAGRAMSCHEMA

2006/06/09

E

05 of 22

VBUS

DCIO

DCIO_ON

SXA1096431

R1A

X2200

1

2

3

NC

4

NC

5

VBUS

Charge sense lines, pin D2 and D3 on

N2000, should be routed toget her and

connected directly to pads f or R2201

(no current conduct in g via al low ed

between connection po int and pad ).

V2203

8

RYN122684/2

7

6

3

2

1

1

TP2220 TP2221 TP2222

DCIOint

5

100Kohms

R2202

4

3

V2210

RN1102

RYN121919/2

2

12

AC

V2200

C2201

1uF

NM

DCIOint

VDDE18

VDIG

ST5005

21

ST5006

12

C2213

4.7uF

C2220

100nF

VCORE18

C2214

4.7uF

C2219

10uF

V2205

R2212

1.8Kohms

R2213

4.7Kohms

C2216

1uF

C22105

100nF

C22106

100nF

C2215

4.7uF

VBATI

L2000

22uH

C2222

10uF

RKZ123905/ 2

220mohms

Solder EP to a large pad or

circuit board ground plane.

C2223

1uF

Solder EP to a large pad or

circuit board ground plane.

C2280

1uF

C2218 close

to N200 0

L2201

ST5010

21

C2221

100nF

R2205

N2200

6

SHDN

1.3V

RESET

81

OUT

IN

9

EP

5

GND

MAX1976AETA-130

RYT1137810/1

N2201

6

SHDN

1.5V

RESET

81

OUT

IN

9

EP

5

GND

MAX1976AETA-150

RYT1137810/2

Name changed acc to J Lindell

ST5009

12

R2204

4.7Kohms

C2218

1uF

+

C2217

4

7

NC

2

NC

3

I.C

4

7

NC

2

NC

3

I.C

70mF

VCORE18

C2281

4.7uF

ST5011

21

C2224

4.7uF

ST5012

NM

V220 8

VBATI

RKZ123905 /2

DCIOint

VCORE15

12

VDIG

FG sense lines, pin F11 and F12 on N2000,

should be routed toget her an d connected

directly to pads for R2200 (n o

current conducting v ia allowed between

connection point and pad) .

R2200

25mohms

C2211

C2212

22pF

3.3pF

Mount C2211 and C2212

close to battery c onnector

DF2S6.8FS

RKZ223911/1

4

V2202

RYN122684/2

1

2

5

3

6

7

8

NM

C2111

VCORE15

RKZ123911/1

R2201

100mohms

VDDE18

V2201

C2206

47pF

Place C2206 and C2207

close to N2000

C2207

47pF

VBATI

VBATI

C2202

C2205

100nF

22pF

C2203

100nF

Should be separated

fr om surf ace GN D

ST5002

100nF

C2209

C2210

100nF

12

C2200

4.7uF

R2215

0ohms

C2110

100nF

C2204

100nF

C2208

100nF

N2000

ERICSSO N AB 2 0 10

POWER

BASEBAND REGULATO RS

M12

A8

A3

E9

F2

F3

E1

B11

E2

D1

D3

D2

F11

F12

M9

H9

J8

M5

M3

M10

C3

D10

D4

J12

H12

R2203

100Kohms

LDO_D

VBATB

LDO_E

LDO_F

LDO_G

VBATC

LPREG

MOD1

CONVERTER

BATTERY MANAGEMENT

VBUS

USBMOD

VBATD

BDATA

VDCIO

CHREG

CHSENSE+

CHSENSEFGSEN SE+

FGSEN SE-

ANALOG BLOCK SUPPLY

VDDADC VSSADC

AUDIO BLOCK SUPPLY

DIGVSS

DIGVDD

VDDCODEC

VDDBEAR

REF

VDDIO_1 8

VDDIO

SUB

TEST

VREF

IREF

ERICSSON_AB2012

ROP1013066/6

N2000 reference.

Mount close to N2000

M11

VDDD

L12

VDDE

B7

VDDFVBATF

A9

VDDG

L2

VDDLP

A2

VDDBUCK

A1

SWBUC K

SWBUCK

B1

VSSBUCK

BUCK

VSSCODEC

VBUCK

VSSB

VSSC

VSSD

VSSBEA R

B2

G3

C6

E3

K8

K5

K4

R1A

VBUCK

Local ground plane

Connect local ground plane to

main ground plane in one point only

VDIG

VDDE18

VDDF13

VMSPICO

VRTC13

VBACKUP

VBATI

VCORE18

DCIOint

VCORE13

VCORE15

CAM_27_EN

VBT_EN

R2207

100Kohms

CAM_27_EN

VBT_EN

VBATI

N2202

2

VDD

6

CE1 VOUT1

4

CE2 VOUT2

C2290

1uF

R5323Z022B_TR_FD

RYT113997/4

N2204

2

VBATI

NM

R2209

100Kohms

C2297

2.2uF

CE

IN

3

GND

R1115Z-281B-TR

RYT113993/1

1

3

5

GND

41

OUT

C2293

C2292

2.2uF

2.2uF

ST5001

12

C2296

4.7uF

VBT27

VCAM27

TP2200

VCAM18

CAM_27_EN

TP22000

VDIG VBA TI

0ohms

NM

R2225

C2299

2.2uF

0ohms

R2226

N2205

LDO REGULATOR

A1

EN

C3 C1

IN OUT

B2

GND NR

TPS799 13YZU

RYT1137816/3

VCAM12

1.3

A3

C2295

10nF

ST501 3

21

C2294

NM

2.2uF

Confidential

Approved accord in g to 00021-LXE 107 42/1

TP2202

Sony Ericsson

BASEBAND

Regulators & Charging

Power

VCAM18

VCAM27VBT27

SCHEMA DIAGRAM

SEMCJ/ Yoshikazu Sakamoto

SEMCJ/ Daisuke Katayama

THELMA

2/1911-ROA 128 1740/2

VCAM12

2006/06/09

VCAM12

VCAM27

VBT27

VCAM18

E

06 of 22

VDDE18

VDDF13

VRTC13

VCORE13

VCORE15

VCORE13

C2225

C2229

100nF

100nF

100nF C2231

100nF C2227

C2228

100nF C 2230

100nF C 2226

100nF

VDDE18 VDDF13 VRTC13 VCORE 13V CORE15

VRTC13

VCORE15

VDDF13

2

ST5014

R2A

N2000

ERICSSON_AB2012

ROP1013066/6

1

C2256

100nF

ERICSSON AB 2010

POWER

THERMAL GROUNDS

D2000

MARIKA_POWER_CORE

Core-1.3V

M1

VDDC0

T1

VDDC1

AA11

VDDC2

AA16

VDDC3

U21

VDDC4

K21

VDDC5

A12

VDDC6

A10

VDDC7

A6

VDDC8

ARMCore-1.3V

H21

VDDCARM0

A17

VDDCARM1

A13

VDDCARM2

TCMCore-1.3V

P21

VDDCTCM0

L21

VDDCTCM1

GSMCore-1.3V

U1

VDDCGSM0

AA4

VDDCGSM1

AA10

VDDCGSM2

RAMCore-1.3V

N1

VDDCRAM0

R1

VDDCRAM1

UMACore-1.3V

F1

VDDCUMA0

L1

VDDCUMA1

A9

VDDCUMA2

A5

VDDCUMA3

DPLL-1.3V

AA19

VDDCPLL

C2235

100nF

100nF C2233

100nF C2234

100nF C223 2

100nF C2239

100nF C22 37

100nF C223 6

100nF C2238

100nF C22 40

DB2021_MARIKA_SECURITY_E FUSE

ROP1013083/4

100nF C2241

VDDE18

ST5015

12

C2246

100nF C2242

100nF C2244

100nF C2248

100nF C2250

100nF

C2243

C2247

100nF

100nF C2 245

100nF

100nF C225 7

100nF C225 8

F7

VSSTH1

G7

VSSTH2

G6

VSSTH3

E5

VSSTH4

E6

VSSTH5

E7

VSSTH6

E8

VSSTH7

F8

VSSTH8

G8

VSSTH9

H8

VSSTH10

H7

VSSTH11

H6

VSSTH12

H5

VSSTH13

G5

VSSTH14

F5

VSSTH15

D6

VSSTH17

D7

VSSTH18

D8

VSSTH19

F9

VSSTH21

G9

VSSTH22

J7

VSSTH25

J6

VSSTH26

J5

VSSTH27

F4

VSSTH30

R1A

100nF C225 2

100nF C2254

C2253

100nF C2249

100nF C2251

100nF

100nF C22 55

The tunnel capacitor C2278 is int ended for

decoupling of a solid power s upply plan,

preferably on layer 2. This plan shall be f ed

from ST5016 in a single point.

D2000

MARIKA_POWER_OTHER

I/O-1.8V

C1

VDDEE00

D1

VDDEE01

G1

VDDEE02

K1

VDDEE03

P1

VDDEE04

V1

VDDEE05

AA3

VDDEE06

AA6

VDDEE07

AA9

VDDEE08

AA14

VDDEE09

R21

VDDEE10

N21

VDDEE11

J21

VDDEE12

G21

VDDEE13

D21

VDDEE14

A20

VDDEE15

A18

VDDEE16

A15

VDDEE17

A11

VDDEE18

A8

VDDEE19

A4

VDDEE20

A3

VDDEE21

I/O-1.5/1.8V

AA18

VDDEWL0

Y21

VDDEWL1

RTC-1.3V

Y17

VDDRTC

Analog-1.3V

V13

VDDA

Efuse

V16

VPPSTD0

AA21

VPPSTD1

W18

VPPSTDSENSE

NotConnected_Balls

AA1

NC_RSV0

A21

NC_RSV1

A1

NC_RSV2

DB2021_MARIKA_SECURITY_ EFUSE

ROP1013083/4

VSS00

VSS01

VSS02

VSS03

VSS04

VSS05

VSS06

VSS07

VSS08

VSS09

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSSA

REV501107/201

2

ST5016

1

G4

J4

L4

M4

P4

T4

V5

V6

V9

V11

W14

V14

V18

T18

N18

M18

K18

H18

E18

D17

D14

D12

D10

D9

D7

D5

Y15

C2260

100nF

R2A

VCORE15

C2278

23

IN

OUT

1

GND

1uF

C2262

100nF

100nF C2264

100nF C2 268

100nF C2 270

100nF C2266

C2263

C2267

C2269

100nF C226 1

100nF

100nF C22 65

100nF

100nF

Confidential

Approved according to 00021-L X E 107 42/1

Sony Ericsson

BASEBAND

Power

ASICs

100nF C2272

100nF C2271

100nF C2273

VRTC13VDDF13

D2001

U6

U10

R11

R12

L15

T17

A3

A6

A12

A17

B14

B8

B1

D2

D16

F17

G1

H17

K17

K2

M1

N17

R1

R13

R16

T2

U5

U16

100nF C2274

100nF C2 276

100nF C227 5

ROP1013044/4

C2277

100nF

SEMCJ/ Yoshikazu Sakamoto

SEMCJ/ Daisuke Katayama

THELMA

2/1911 -ROA 128 1740 /2

EMP_WAN DA_POW ER

VDD_TX

VDD_RX

VDD_BG

VSS_CS_ ADPLL

VDD_CS_ADPLL

VSSCOMPLEX_IO1

VSSCOMPLEX_IO2

DIGITAL SUPPLY

VDD_DPLL

VDD_CLK32

VDD_1

VDD_2

VDD_3

VDD_4

VDD_5

VDD_6

VDD_7

VDD_8

VDD_9

VDD_10

VDD_11

VDD_12

VDD_13

VDD_14

VDD_15

VDD_16

VDD_17

VDD_18

VDD_19

VDD_20

VDD_21

VDD_22

VSS_TX

VSS_RX

VSS_BG

BG_REF

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

R1A

2006/06/09

R8

T8

T11

N11

T6

T12

U11

100nF C2279

B15

B11

B10

B7

C3

C5

C12

C16

D3

F3

F15

H3

H16

J16

L2

L16

N3

P16

R3

R4

T4

U15

U17

DIAGRAMSCHEMA

E

07 of 22

Loading...

Loading...