Page 1

HighWire HW400c/2 User Reference Guide Rev 1.0

___________________HighWire

HW400c/2

User Reference Guide

October 10, 2006 Copyright 2006, SBE, Inc. Page i

M8275, Rev 1.0

Page 2

HighWire HW400c/2 User Reference Guide Rev 1.0

Copyright ©2006 by SBE, Inc. All rights reserved.

No part of this manual may be reproduced by any means without written

permission from SBE, Inc., except that the purchaser may copy necessary

portions for internal use only.

While every effort has been made to ensure the accuracy of this manual, SBE

cannot be held responsible for damage resulting from information herein. All

specifications are subject to change without notice.

SBE, Inc. and the SBE logo are trademarks of SBE, Inc.

All other trademarks and copyrights are owned by their respective companies.

About SBE, Inc. SBE designs and provides IP-based networking solutions for

an extensive range of applied computing applications. SBE delivers a portfolio

of scalable, standards-based hardware and software products, including iSCSI

and VoIP, designed to enable optimal performance and rapid deployment

across a wide range of next generation communications and storage systems.

SBE is based in San Ramon, California, and can be reached at 925-355-2000

or online at http://www.sbei.com.

October 10, 2006 Copyright 2006, SBE, Inc. Page ii

Page 3

HighWire HW400c/2 User Reference Guide Rev 1.0

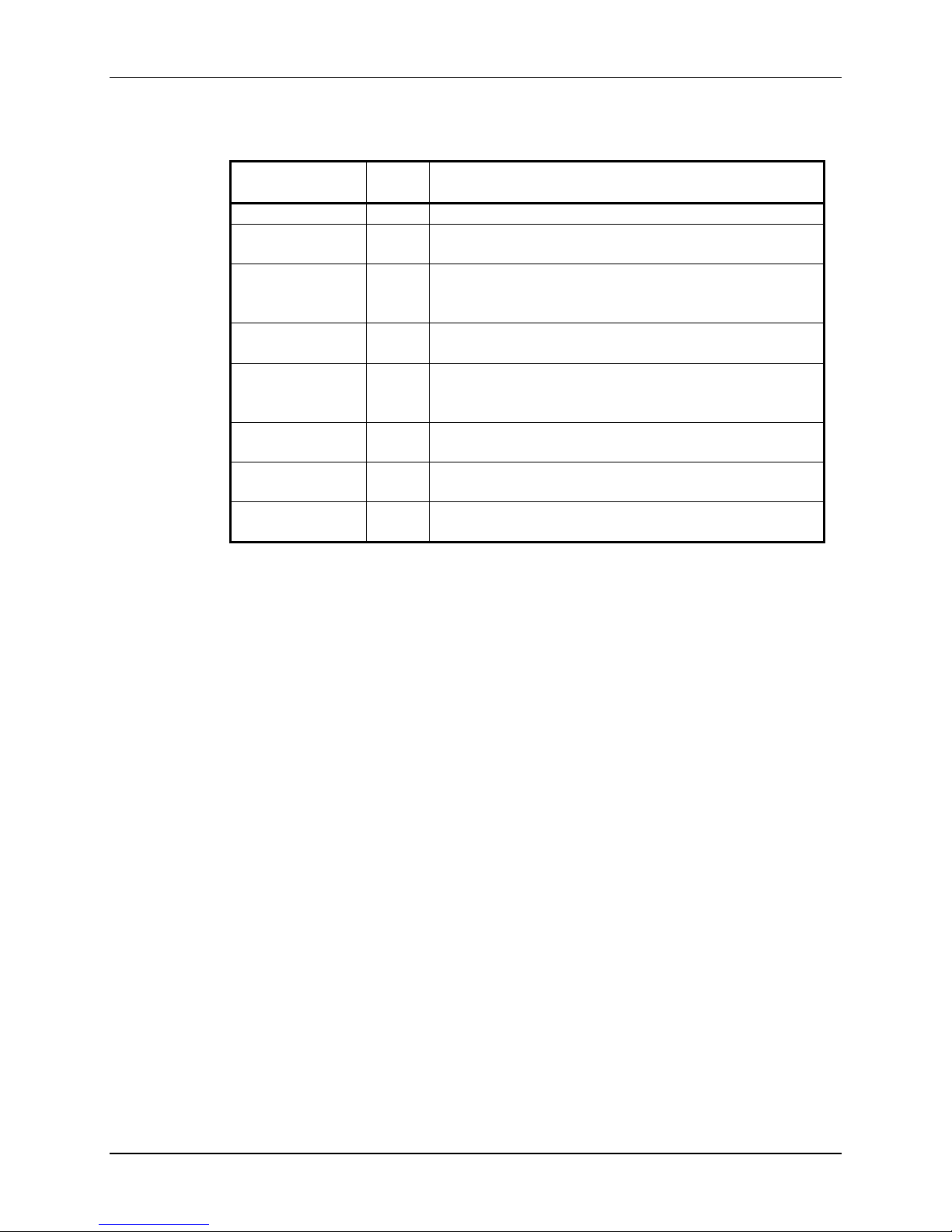

Revision History

Revision Date Changes

1.0 October 10, 2006 Initial Release

October 10, 2006 Copyright 2006, SBE, Inc. Page iii

Page 4

HighWire HW400c/2 User Reference Guide Rev 1.0

THIS PAGE IS INTENTIONALLY LEFT BLANK

October 10, 2006 Copyright 2006, SBE, Inc. Page iv

Page 5

HighWire HW400c/2 User Reference Guide Rev 1.0

Table of Contents

Revision History............................................................................................................................iii

Table of Contents..........................................................................................................................v

List of Figures ...............................................................................................................................ix

List of Tables.................................................................................................................................ix

Conventions .................................................................................................................................xii

1 About This Manual......................................................................................................................1

2 Introduction .................................................................................................................................2

2.1 Product Description...............................................................................................................2

2.2 Unpacking Instructions.........................................................................................................3

2.3 Handling Procedures.............................................................................................................4

2.4 Hardware Installation of the HW400c/2...............................................................................4

2.5 Returns/Service.....................................................................................................................5

2.6 Operating Environment.........................................................................................................5

2.7 Mean Time Between Failures (MTBF).................................................................................6

2.8 Regulatory Agency Certifications.........................................................................................7

2.8.1 Safety...........................................................................................................................7

2.8.2 US and Canadian Emissions........................................................................................7

2.8.3 European Emissions and Immunity.............................................................................7

2.9 Agency Compliance..............................................................................................................7

2.10 Physical Properties..............................................................................................................8

2.10.1 HW400c/2 Front Panel..............................................................................................9

2.10.2 Part number and serial number................................................................................10

2.10.3 Bus Keying..............................................................................................................10

2.10.3.1 Compact PCI ........................................................................................................10

2.10.3.2 PTMC Site............................................................................................................10

2.10.4 Power Requirements................................................................................................11

2.10.5 Switches...................................................................................................................12

2.10.6 Product Configurations............................................................................................12

3 Functional Blocks......................................................................................................................13

3.1 PowerPC Processor.............................................................................................................13

3.1.1 MPC744X Development/Debug Support..................................................................13

3.1.2 Console port...............................................................................................................14

3.1.3 Pushbutton Reset / Interrupt......................................................................................14

3.1.4 COP/JTAG Port.........................................................................................................16

3.1.5 Special Purpose Jumper Block..................................................................................16

3.1.5.1 Jumper Pins ............................................................................................................17

October 10, 2006 Copyright 2006, SBE, Inc. Page v

Page 6

HighWire HW400c/2 User Reference Guide Rev 1.0

3.2 MV64462 System Controller..............................................................................................17

3.2.1 System Bus................................................................................................................17

3.2.2 Dual Data Rate (DDR) SDRAM...............................................................................17

3.2.3 Host PCI Bus.............................................................................................................18

3.2.3.1 Operation Without CompactPCI Bus.....................................................................18

3.2.4 Local PCI Bus............................................................................................................18

3.2.5 Serial EEPROM.........................................................................................................19

3.2.6 MV64462 Ethernet Interface.....................................................................................22

3.2.7 MV64462 Device Interface.......................................................................................22

3.2.7.1 SRAM Device ........................................................................................................22

3.2.7.2 Boot PROM............................................................................................................22

3.2.7.3 Disk-on-Chip..........................................................................................................22

3.2.7.4 CT Bus Controller ..................................................................................................23

3.2.7.5 CPLD......................................................................................................................23

3.2.8 Watchdog Timer........................................................................................................23

3.2.9 Reset..........................................................................................................................23

3.2.10 Multi-Purpose Port (MPP) Usage............................................................................24

3.3 Computer Telephony Bus Controller..................................................................................25

3.3.1 H.110 Interface (T8110L)..........................................................................................25

3.3.2 T8110L Clocking Interface (T8110L).......................................................................25

3.3.3 Operation in Non-H.110 Backplane..........................................................................27

3.4 Layer 2 Ethernet Switch......................................................................................................27

3.4.1 Switch Registers Initialization and Monitoring.........................................................28

3.4.2 MV64462 System Controller Ethernet Interface.......................................................28

3.4.3 Front Panel (RJ-45) Ethernet Interface......................................................................28

3.4.4 PT5MC Ethernet Ports ..............................................................................................29

3.4.5 CompactPCI Packet Switch Backplane (cPSB) Ports ...............................................29

3.4.5.1 CompactPCI Connector J3, power and ground......................................................29

3.4.6 On-board Ethernet Indicator LEDs............................................................................30

3.5 Mezzanine Card Sites..........................................................................................................32

3.5.1 PT5MC Type Mezzanine Cards ................................................................................32

3.5.2 PT2MC Type Mezzanine Cards ................................................................................32

3.5.3 PMC Type Mezzanine Cards.....................................................................................32

3.5.4 Mezzanine Card Power..............................................................................................33

3.5.5 PTMC/PMC Connector Summary.............................................................................33

3.5.6 PTMC Jn1 and Jn2 PCI Connectors..........................................................................34

3.5.7 PTMC Jn3 CT Bus Connector...................................................................................35

3.5.8 PTMC Jn4 LAN/User I/O Connector........................................................................36

3.5.8.1 PTMC Site A Jn4....................................................................................................36

3.5.8.2 PTMC Site B Pn4...................................................................................................38

3.5.9 PTMC Site Voltage Keying.......................................................................................39

3.6 IPMI System Management..................................................................................................39

3.6.1 IPMI Controller.........................................................................................................39

3.6.2 Temperature and Voltage Monitor............................................................................40

3.6.3 Hot Swap Ejector Latch Detection............................................................................41

3.6.4 Blue (Hot Swap) LED Control..................................................................................41

3.6.5 Boot Status Monitor ..................................................................................................41

3.6.6 Board Reset via IPMI................................................................................................42

October 10, 2006 Copyright 2006, SBE, Inc. Page vi

Page 7

HighWire HW400c/2 User Reference Guide Rev 1.0

3.6.7 IPMI System Power Supply ......................................................................................42

3.6.8 IPMI Firmware EEPROMs .......................................................................................42

3.6.9 Zircon PM Reset........................................................................................................43

3.6.10 IMPI Get Device ID ................................................................................................43

3.7 Hot Swap Support...............................................................................................................44

3.7.1 Hot Swap on J1 and J2 ..............................................................................................44

3.7.2 Hot Swap on J3..........................................................................................................44

3.7.3 Hot Swap on J4..........................................................................................................44

3.7.4 Hot Swap on J5..........................................................................................................44

3.7.5 Hot Swap Sequence...................................................................................................45

4 Programming Information.........................................................................................................46

4.1 HW400c/2 Memory Map....................................................................................................46

4.2 CPLD Registers ..................................................................................................................47

4.2.1 Clock Select Register (CSR).....................................................................................48

4.2.2 Board Status Register (BSR).....................................................................................49

4.2.3 LED Register A (LEDA)...........................................................................................49

4.2.4 Memory Option Register (MOR)..............................................................................50

4.2.5 Geographic Addressing Register (GAR)...................................................................50

4.2.6 PTMC Reset Register (PRR).....................................................................................51

4.2.7 PTMC Control Register (PCR)..................................................................................51

4.2.8 Board Option Register (BOR)...................................................................................52

4.2.9 General Purpose Register (GPR)...............................................................................52

4.2.10 PCI Status Register (PSR).......................................................................................53

4.2.11 Extended Type Register (ETR) ...............................................................................53

4.2.12 Hardware Revision Register (HRR)........................................................................54

4.2.13 PLL Configuration Register A (PLLA)...................................................................54

4.2.14 PLL Configuration Register B (PLLB)...................................................................55

4.2.15 LED Register B (LEDB) .........................................................................................56

4.2.16 Device Control Register (DCR) ..............................................................................57

4.2.17 CPU Timer Register (CTR).....................................................................................57

4.2.18 Warm Reset Register (WRR)..................................................................................58

4.2.19 SPI Page Register (SPR) .........................................................................................58

4.2.20 SPI Address Register (SAR)....................................................................................58

4.2.21 SPI Read Byte Offset Register (SOR).....................................................................59

4.2.22 Read Byte Count Register (RBC)............................................................................59

4.2.23 Write Byte Count Register (WBC)..........................................................................60

4.2.24 SPI Data Registers (SDR0 – SDR7)........................................................................60

4.2.25 SPI Error and Status Register (SESR).....................................................................61

4.2.26 EEPROM Address Register (EAR).........................................................................61

4.2.27 EEPROM Operation/Status Register (EOSR).........................................................62

4.2.28 EEPROM Data Registers (EDR0 – EDR1).............................................................63

4.3 Accessing the Serial EEPROM...........................................................................................63

4.3.1 Reading an EEPROM Address..................................................................................63

4.3.2 Writing an EEPROM Address...................................................................................64

4.4 Accessing the SPI Interface ................................................................................................64

4.4.1 Registers in the CPLD...............................................................................................64

4.4.2 BCM5388 Registers Access Rules............................................................................64

October 10, 2006 Copyright 2006, SBE, Inc. Page vii

Page 8

HighWire HW400c/2 User Reference Guide Rev 1.0

4.4.3 Reading BCM5388 Register......................................................................................65

4.4.4 Writing a BCM5388 Register....................................................................................65

5 Linux on the HW400c/2 and Host system.................................................................................67

5.1 Host Hardware and Software Requirements.......................................................................67

5.2 Network and System Configuration....................................................................................68

5.3 Installing Linux on your host system..................................................................................68

5.4 Configuring the Host System..............................................................................................69

5.4.1 Modifying the Host Path ...........................................................................................69

5.4.2 Configuring the Host NFS Server .............................................................................69

5.4.3 Configuring Host tftp services...................................................................................70

5.4.4 Configuring tftp with inetd........................................................................................71

5.4.5 Configuring tftp with xinetd......................................................................................73

5.4.6 Configuring a bootp Server.......................................................................................74

5.5 Booting the HW400c/2 .......................................................................................................75

5.5.1 U-boot, Universal Bootloader....................................................................................76

5.5.1.1 U-boot commands ..................................................................................................76

5.5.1.2 U-boot environment variables................................................................................77

5.5.1.3 Power up call trace .................................................................................................79

5.5.2 Booting with tftp........................................................................................................80

5.5.2.1 U-boot parameters for tftp with bootp....................................................................80

5.5.2.2 U-boot parameters for tftp with static IP address...................................................81

5.5.2.3 Boot console...........................................................................................................81

5.5.3 Booting with Disk on Chip........................................................................................84

5.5.3.1 Loading the Disk on Chip.......................................................................................84

5.5.3.2 Creating a uRamdisk Image ...................................................................................85

5.5.3.3 Booting from DoC..................................................................................................85

5.6 Compiling the Kernel (uImage)..........................................................................................86

5.6.1 Gentoo Application Packages Management..............................................................87

5.6.1.1 Emerge....................................................................................................................87

5.6.1.2 Enable remote login with ssh ...............................................................................88

5.6.1.3 Starting network services; xinetd.......................................................................88

5.6.1.4 Starting ftp services; vsftpd.............................................................................88

5.7 Linux Device Drivers..........................................................................................................89

Appendix A IPMI GetDeviceID........................................................................................90

Appendix B U-Boot Environment variables......................................................................91

October 10, 2006 Copyright 2006, SBE, Inc. Page viii

Page 9

HighWire HW400c/2 User Reference Guide Rev 1.0

List of Figures

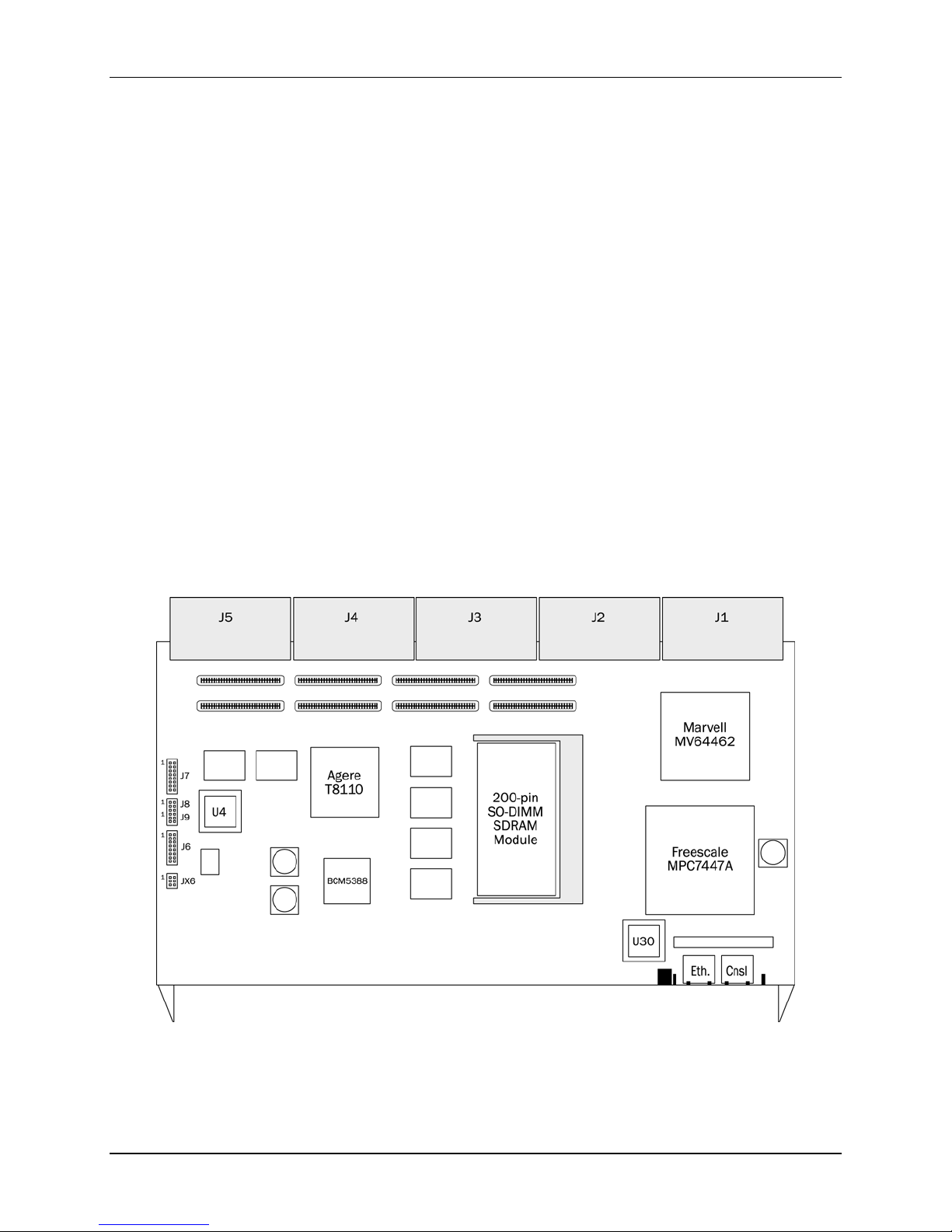

Figure 1. HW400c/2 Block Diagram...........................................................................................................3

Figure 2. The HW400c/2 PTMC Processing Platform ................................................................................8

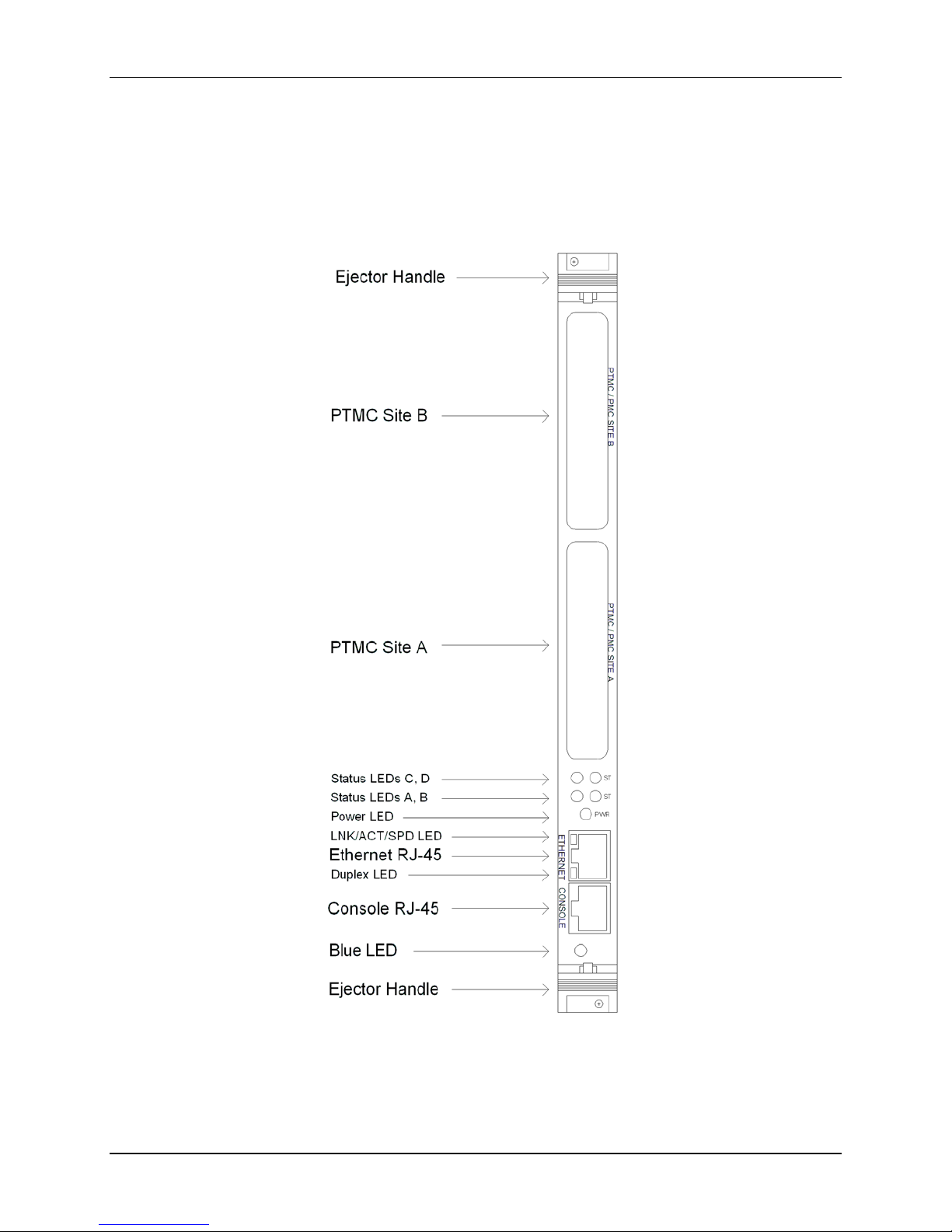

Figure 3. HW400c/2 Front Panel.................................................................................................................9

Figure 4. Console port pin out ....................................................................................................................14

Figure 5. J8, J9 Reset/NMI header.............................................................................................................14

Figure 6. J8 and J9 with optional Reset/NMI cable...................................................................................15

Figure 7. Optional Reset/NMI switch........................................................................................................16

Figure 8. COP/JTAG Pinout......................................................................................................................16

Figure 9. J7 Special purpose jumper block................................................................................................16

Figure 10. Local CT Bus Clocking Block Diagram...................................................................................26

Figure 11. Local CT Bus Clock Generation ..............................................................................................26

Figure 12. Front panel Ethernet RJ-45 LEDs .............................................................................................28

Figure 13. IPMI Block Diagram................................................................................................................40

Figure 14. HW400c/2 Network and System environment..........................................................................67

List of Tables

Table 1. HW400c/2 Operating Environment...............................................................................................5

Table 2. HW400c/2 Physical Dimensions ...................................................................................................8

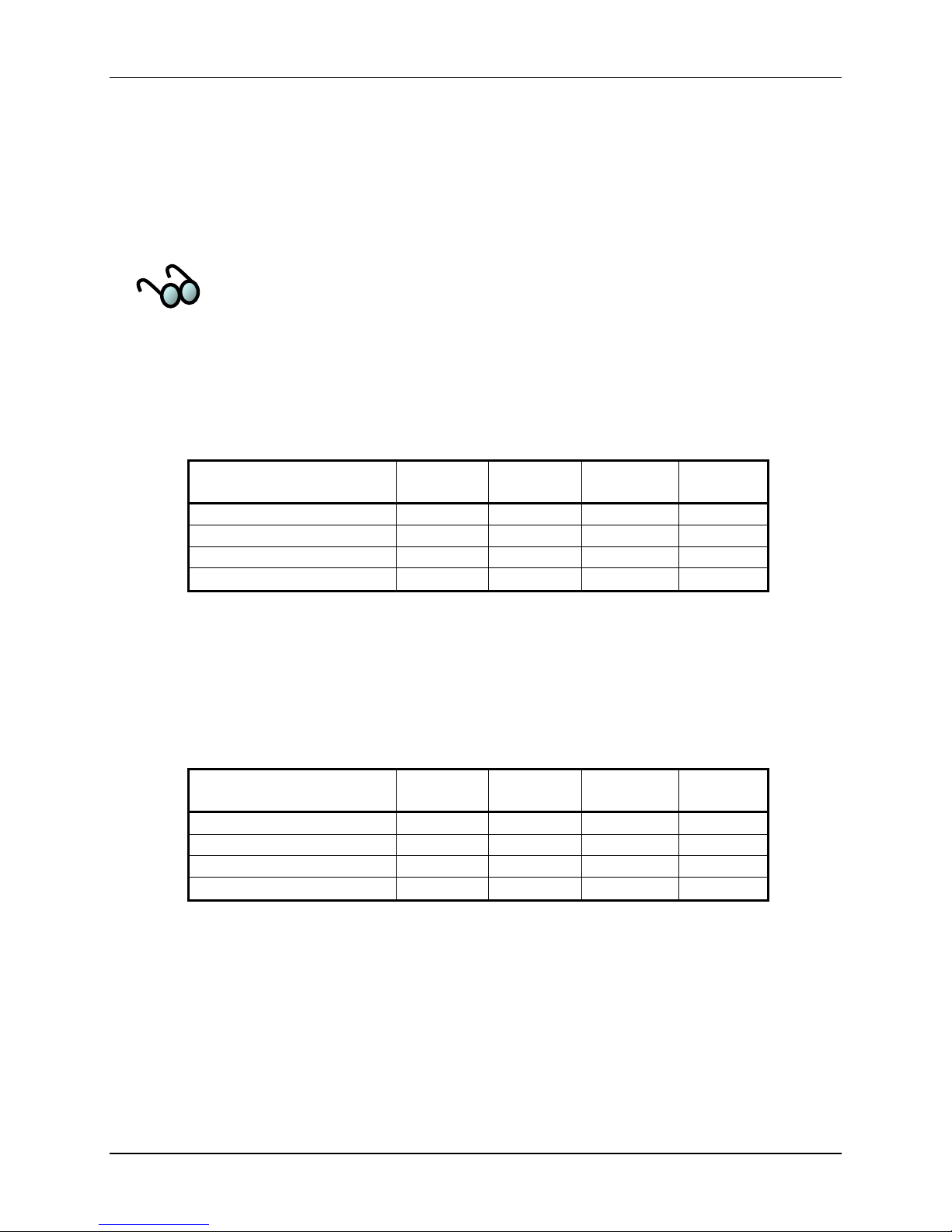

Table 3. HW400c/2 power requirements VIO = 5.0V...............................................................................11

Table 4. HW400c/2 power requirements VIO = 3.3V...............................................................................11

Table 5. HW400c/2 Order time options......................................................................................................12

Table 6. HW400c/2 Processor Options......................................................................................................13

Table 7. J8 and J9 pin out ..........................................................................................................................15

Table 8. J7 pin functions.............................................................................................................................17

Table 9. Microwire EEPROM Contents, Factory Area .............................................................................20

Table 10. Microwire EEPROM Contents, Uboot Area...............................................................................21

Table 11. MV64462 Multi-Purpose Port Assignments..............................................................................24

Table 12. LSC Assignments ......................................................................................................................25

Table 13. LREF [3:2] Assignments...........................................................................................................27

October 10, 2006 Copyright 2006, SBE, Inc. Page ix

Page 10

HighWire HW400c/2 User Reference Guide Rev 1.0

Table 14. Layer 2 Switch Port Assignments..............................................................................................27

Table 15. Compact PCI connector J3 pin out .............................................................................................30

Table 16. Mezzanine Card Power Budget .................................................................................................33

Table 17. PTMC/PMC Connector Summary.............................................................................................33

Table 18. PTMC Jn1 and Jn2 Connector Pin Assignments.......................................................................34

Table 19. PTMC Configuration #2/#5 Pn3 Connector Pin Assignment....................................................35

Table 20. PTMC Site A Configuration #2/#5 Pn4 Connector Pin Assignment.........................................37

Table 21. PTMC Site B Configuration #2/#5 Pn4 Connector Pin Assignment.........................................38

Table 22. GPIO Port Assignments for IPMI..............................................................................................40

Table 23. Voltage Monitor A/D Port Assignments for IPMI.....................................................................41

Table 24. HW400c/2 Temperature Sensor Locations................................................................................41

Table 25. Firmware EEPROM Addresses .................................................................................................42

Table 26. Product ID number.....................................................................................................................43

Table 27. Overview of Hot Swap Insertion/Extraction Sequences............................................................45

Table 28. HW400c/2 Memory Map...........................................................................................................46

Table 29. CPLD Registers .........................................................................................................................47

Table 30. Clock Select Register (CSR) Offset Address 0x04....................................................................48

Table 31. Board Select Register (BSR) Offset Address 0x05 ...................................................................49

Table 32. LED Register A (LEDA) Offset Address 0x06 .........................................................................49

Table 33. Memory Option Register (MOR) Offset Address 0x07.............................................................50

Table 34. Geographic Addressing Register (CSR) Offset Address 0x08..................................................50

Table 35. PTMC Reset Register (PRR) Offset Address 0x09...................................................................51

Table 36. PTMC Control Register (PCR) Offset Address 0x0A...............................................................51

Table 37. Board Option Register (BOR) Offset Address 0x0D.................................................................52

Table 38. General Purpose Register (GPR) Offset Address 0x0E.............................................................52

Table 39. PCI Status Register (PSR) Offset Address 0x0F .......................................................................53

Table 40. Extended Type Register (ETR) Offset Address 0x10................................................................53

Table 41. Hardware Revision Register (HRR) Offset Address .................................................................54

Table 42. PLL Configuration Register A (PLLA) Offset Address 0x12...................................................54

Table 43. PLL Configuration Register B (PLLB) Offset Address 0x13....................................................55

Table 44. LED Register B (LEDB) Offset Address 0x14..........................................................................56

Table 45. On-board LED functions as determined by LEDB [1:0]...........................................................56

Table 46. Device Control Register (CSR) Offset Address 0x15 ...............................................................57

Table 47. CPU Timer Register (CTR) Offset Address 0x16 .....................................................................57

October 10, 2006 Copyright 2006, SBE, Inc. Page x

Page 11

HighWire HW400c/2 User Reference Guide Rev 1.0

Table 48. Warm Reset Register (WRR) Offset address 0x17.....................................................................58

Table 49. SPI Page Register (SPR) Offset Address 0x1A.........................................................................58

Table 50. SPI Address Register (SAR) Offset Address 0x1B ...................................................................58

Table 51. SPI Read Byte Offset Select Register (SOR) Offset Address 0x1C..........................................59

Table 52. Read Byte Count Register (RBC) Offset Address 0x1D...........................................................59

Table 53. Write Byte Count Register (WBC) Offset Address 0x1E..........................................................60

Table 54. SPI Data Registers (SDRn) Offset Address 0x20-0x27.............................................................60

Table 55. SPI Error and Status Register (SESR) Offset Address 0x1F.....................................................61

Table 56. EEPROM Address Register (EAR) Offset Address 0x28 .........................................................61

Table 57. EEPROM Operation/Status Register (EOSR) Offset Address 0x29 .........................................62

Table 58. EEPROM Data Registers (EDRn) Offset Address 0x2A-0x2B ................................................63

October 10, 2006 Copyright 2006, SBE, Inc. Page xi

Page 12

HighWire HW400c/2 User Reference Guide Rev 1.0

Conventions

The following conventions are used in this document:

A # following a signal name, e.g., INTA#, represents an active low signal.

A / preceding a signal name, e.g., /INTA represents an active low signal.

0x preceding a number represents a Hexadecimal value.

A number in “ ” preceded by H represents a Hexadecimal value.

A number in “ ” preceded by B represents a Binary value.

A register or bit name that ends with _EN indicates an enable function

A register or bit name that ends with _N indicates an asserted low function

Typeface courier is used to designate code and/or terminal input.

Draws attention to important information related to the nearby text.

Refers to information about potential hazards to equipment or personnel.

!

October 10, 2006 Copyright 2006, SBE, Inc. Page xii

Page 13

HighWire HW400c/2 User Reference Guide Rev 1.0

1 ABOUT THIS MANUAL

This manual is technical reference for the HighWire HW400c/2 Gigabit Switched

PTMC Processing Platform for CompactPCI. This manual is intended for those who

are installing the HW400c/2 into a system.

The HighWire HW400c/2 User Reference Manual includes the following:

• Introduction and background on the HighWire HW400c/2

• Hardware reference material

• Hardware installation instructions

• Programming information

• Physical characteristics and specifications

• Operating System Software environment and installation

October 10, 2006 Copyright 2006, SBE, Inc. Page 1

Page 14

HighWire HW400c/2 User Reference Guide Rev 1.0

2 INTRODUCTION

The HW400c/2 is a flexible high-performance core processing platform for building

powerful processor enabled CompactPCI (CPCI) telephony and data communications

I/O solutions. Advanced features on the HW400c/2 include two PCI Telecom

Mezzanine Card (PTMC) sites for CT Bus enabled I/O interfaces that are

interconnected through a high-speed Layer 2 Gigabit Ethernet switch to the dual node

CompactPCI Packet Switched Backplane (cPSB). The HighWire core architecture

utilizes the Freescale MPC7447A PowerPC processor and Marvell Discovery™ III

system controller to provide a powerful computing environment for addressing a

wide range of communications applications.

The HW400c/2 is optimized for packet-based switch fabric system architectures and

is fully compliant with the PICMG 2.16 cPSB specification. The cPSB standard

provides a switched fabric backplane interconnection using Ethernet technology

overlaid on the standard CPCI J3 connector. Dual Gigabit Ethernet interfaces are

provided on the HW400c/2 cPSB interface to support both the high availability dual

node and reduced cost single node configurations.

Full CPCI compliance and interoperability are maintained including Hot Swap,

H.110 CT Bus and rear I/O support.

2.1 Product Description

The HW400c/2 is built on SBE’s advanced HighWire core architecture, and features

the MPC7447A PowerPC processor, Marvell Discovery III system controller, up to

1GB DDR SDRAM and Disk-on-Chip flash file system storage to meet the

demanding needs of today’s telecom and datacom applications. Additional developer

features including a serial console port and a COP emulator port help speed code

development. The HW400c/2 also fully supports the Intelligent Platform

Management Interface (IPMI) standard (PICMG 2.9) for system management.

The two expansion sites accept both CT Bus enabled PTMC modules and standard

PMC modules. PT2MC modules have access to the on-board local CT Bus and

timeslot interchange fabric allowing flexible routing of TDM timeslots both between

the PTMC sites and the H.110 backplane CT Bus. PT5MC modules also include

Gigabit Ethernet connectivity to platform resources. The HW400c/2 automatically

detects each module type to provide full mix and match support for using PT2MC,

PT5MC or PMC modules in either site.

The 32-bit 33-133 MHz PCI/PCI-X interface supports 3.3V signaling modules with

full support for both front and rear I/O access per PICMG 2.3 mapping.

In addition, a 10/100/1000 Ethernet port for system management and application

flexibility is included through a front panel RJ45 connector on the board.

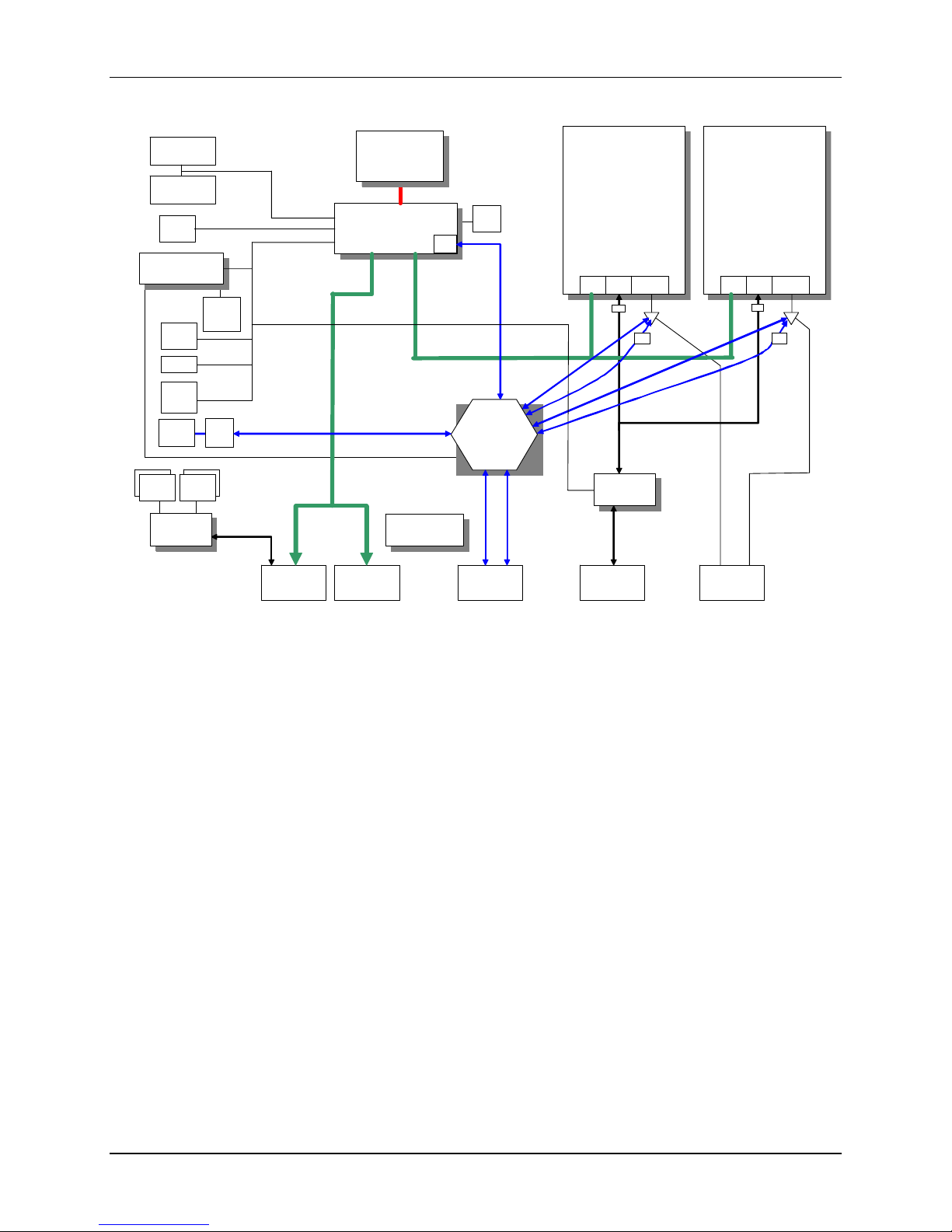

Figure 1 shows the block diagram of the HW400c/2.

October 10, 2006 Copyright 2006, SBE, Inc. Page 2

Page 15

HighWire HW400c/2 User Reference Guide Rev 1.0

r

L

r

Temp

Temp

Sens ors

Sensors

SDRAM

SDRAM

Console

RJ45

CPLD

Boot

ROM

SRAM

Disk on

Chip

Ene t

RJ45

Flash

Flash

Memor

Memory

IPMI

Controller

Microwire

Ser ia l

EEPROM

10/100/

1000

Phy

Processo

Motorola

MPC7447A

System Controlle

Discovery III

Enet

MAC

I2C

Config.

ROM

Layer 2

Ethernet

PTMC Site A

Config #2 or #5

GigE o r

TDMPCI-X

Rear I /O

Phy Phy

PTMC Site B

Config #2 or #5

GigE or

TDMPCI-X

Rear I/O

Switch

H.110

Controller

Hot S wap

J1

PCI

J2

PCI-64

Controller

J3

PSB

J4

H.110

J5

Rear I/ O

Figure 1. HW400c/2 Block Diagram

2.2 Unpacking Instructions

• If the carton is damaged when you receive it, request that the carrier's agent be

present when you unpack and inspect the equipment.

• After unpacking, verify that all items listed in the packing list are present.

• Inspect the equipment for shipping damage.

• Save all packing material for storage or return shipment of the equipment.

• For repairs or replacement of equipment damaged during shipment, contact SBE,

Inc. to obtain a Return Materials Authorization (RMA) number and further

shipping instructions.

October 10, 2006 Copyright 2006, SBE, Inc. Page 3

Page 16

HighWire HW400c/2 User Reference Guide Rev 1.0

2.3 Handling Procedures

The HW400c/2 board uses CMOS components that can be easily damaged by static

electrical discharge. To avoid damage, familiarize yourself with electrostatic

discharge (ESD) procedures, which include the following precautions:

• The board should be handled only by trained service personnel at an approved

ESD workstation.

• Refer to ANSI/IPC-A-610 developed by the Institute for Interconnecting and

Packaging Electronic Circuits (IPC).

• Keep the board in a sealed conductive plastic bag while in transit.

• When installing the board in the field, ground yourself to the system chassis

before removing the board from the sealed conductive plastic bag (the power

plug must be installed on the system for this to be effective).

• Any equipment used to work on the board must be grounded. Any person

handling the board must be grounded.

• Check alignment and polarization of cables and connectors before applying

power.

• Do not apply external voltages to any devices on the board with power removed

from the board.

• Do not attempt to straighten any part soldered to the board, as pin breakage or

internal damage could occur.

2.4 Hardware Installation of the HW400c/2

The HW400c/2 is designed for use in a 6U CompactPCI enclosure.

Be sure to follow safe ESD procedures when handling electronic hardware.

!

• Remove the HW400c/2 from the protective bag.

• Slide the HW400c/2 into an available peripheral board slot in the CompactPCI

chassis. Check that the board is aligned properly on the card guides.

• Completely insert the board until the top and bottom board ejectors lock into

place. If chassis power is on the blue hot swap LED will blink and turn off.

• Tighten top and bottom screws to secure the HW400c/2 in place.

October 10, 2006 Copyright 2006, SBE, Inc. Page 4

Page 17

HighWire HW400c/2 User Reference Guide Rev 1.0

2.5 Returns/Service

Before returning any equipment for service, you must obtain a Return Material

Authorization (RMA) number from SBE:

TEL: 800-925-2666 (Toll free, USA)

TEL: +925-355-2000 (Outside of USA)

FAX: +925-355-2020

Ship all returns to SBE’s USA service center:

SBE, Inc.

4000 Executive Parkway, Suite 200

San Ramon, CA 94583

SBE’s Technical Support Department can be reached at 800-444-0990.

2.6 Operating Environment

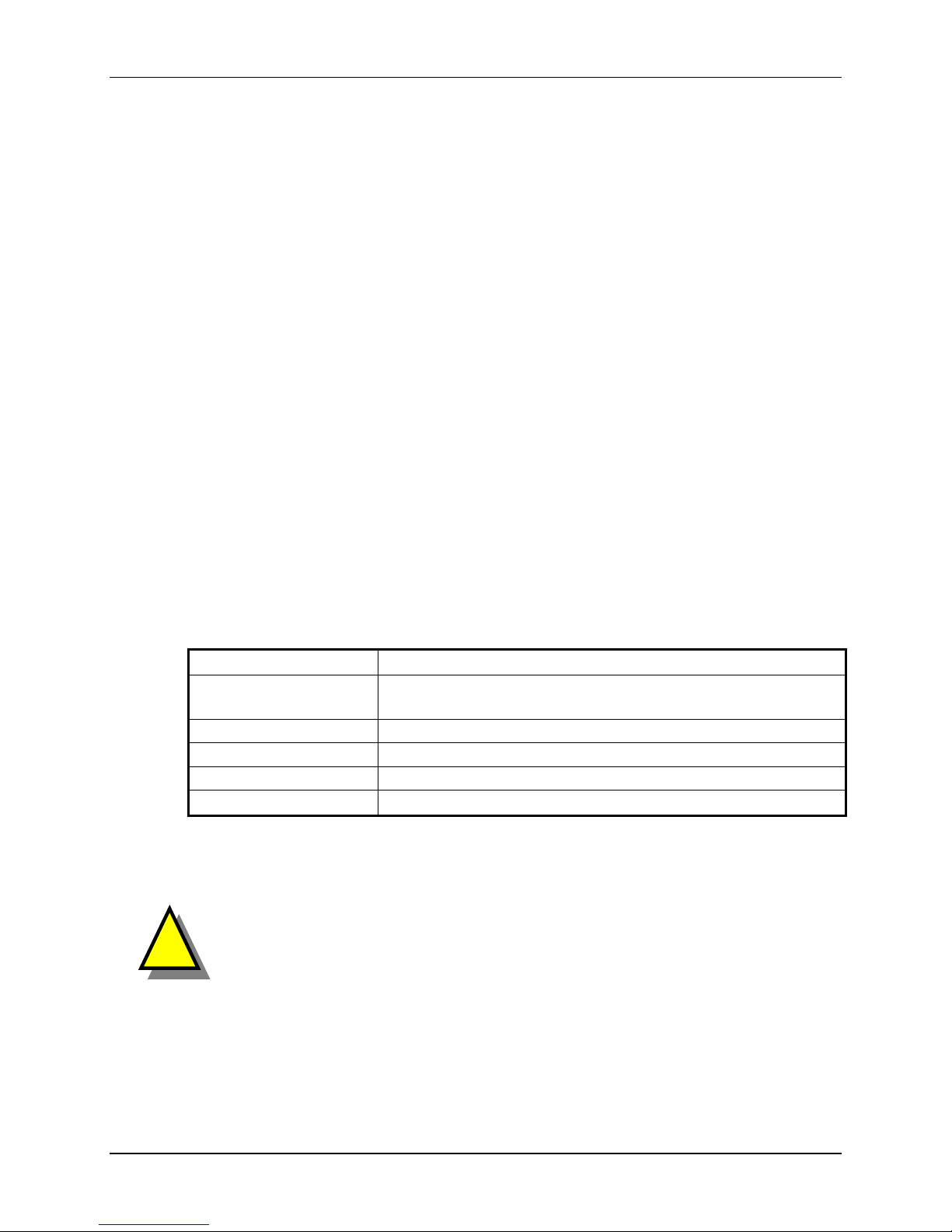

The HW400c/2 is designed to function within the environment shown in Table 1.

Table 1. HW400c/2 Operating Environment

Storage temperature

Operating temperature:

Operating humidity: 10% to 90% non-condensing

Storage humidity: 5% to 95% non-condensing

Power requirements: 36.5 Watts max. (estimated, basic configuration)

Voltages:

Bring the HW400c/2 board to operating temperature in a non-condensing

!

environment. The rate of change in board temperature should not exceed

2 °C (35.6 °F) per minute.

-40 to +85 C (-40 to +185 °F)

0 to 55 °C (32 to 131 °F) ambient temperature with a minimum

of 200 LFM airflow (basic configuration)

5V +5%/-3%, 3.3V +5%/-3%, 12V ±5% (all required)

October 10, 2006 Copyright 2006, SBE, Inc. Page 5

Page 18

HighWire HW400c/2 User Reference Guide Rev 1.0

2.7 Mean Time Between Failures (MTBF)

The Mean Time Between Failure (MTBF) of SBE, Inc’s HW400c/2 was

calculated per Telcordia Technical Reference TR-332 Issue 6, December

1997.

The following specific parameters were used:

Prediction method: Method I (Parts count procedure)

Application conditions: Case 1 (<1 hr burn-in, 50% electrical stress)

Environment:

Component quality factors:

Ambient temperature:

Calculated MTBF:

Controlled, fixed, ground (mult. factor = 1.0)

Quality level II parts (level I on Rs, Cs and LEDs)

50 C

>150,000 hours (not including installed PMC or PTMC modules)

October 10, 2006 Copyright 2006, SBE, Inc. Page 6

Page 19

HighWire HW400c/2 User Reference Guide Rev 1.0

2.8 Regulatory Agency Certifications

The HW400c/2 complies with the requirements listed below.

2.8.1 Safety

• IEC60950 International product safety pending

• IEC60950 pending

• UL60950 pending

• Certified Body (CB) Report pending

2.8.2 US and Canadian Emissions

• FCC Part 15 Class B pending

• Industry Canada CS-003 pending

2.8.3 European Emissions and Immunity

• EN 50082-1 pending

• EN 300386-2 (supercedes EN55022)

to include EN61000-4-6: 10kHz-80MHz, 80%AM 1kHz

pending

CE Mark approval is included.

2.9 Agency Compliance

The HW400c/2 is designed to comply with the following agency requirements.

• NEBS

• VCC

October 10, 2006 Copyright 2006, SBE, Inc. Page 7

Page 20

HighWire HW400c/2 User Reference Guide Rev 1.0

2.10 Physical Properties

The Highwire 400c/2 is compliant with the mechanical specifications of PCMIG 2.0.

Table 2 lists the physical dimensions of the HW400c/2 product. Figure 2 shows the

physical profile of the HW400c/2 board.

Table 2. HW400c/2 Physical Dimensions

Length: 9.2 inches (233.68 mm)

Width: 6.3 inches (160.02 mm)

Maximum component height (front): 0.540 inches (13.72 mm)

Maximum component height (back): 0.079 inches (2 mm)

Board thickness: 0.062 inches (1.57 mm)

Figure 2. The HW400c/2 PTMC Processing Platform

October 10, 2006 Copyright 2006, SBE, Inc. Page 8

Page 21

HighWire HW400c/2 User Reference Guide Rev 1.0

2.10.1 HW400c/2 Front Panel

The HW400c/2 CompactPCI front panel has custom cut outs with the appropriate

thickness to accommodate two PTMC bezels (with EMC gaskets), two RJ-45

connectors, blue Hot Swap LED, green power LED, and status LEDs. Figure 3

below shows an illustration of the front panel.

October 10, 2006 Copyright 2006, SBE, Inc. Page 9

Figure 3. HW400c/2 Front Panel

Page 22

HighWire HW400c/2 User Reference Guide Rev 1.0

2.10.2 Part number and serial number

oards are marked with the manufacturing part number and assembly revision.

All b

This is marked on a label and affixed to the top of the board.

All boards are serialized physically with a bar code serial number label and affixe

e secondary side of the board.

th

.10.3 Bus Keying

2

d to

Keying on the HW400c/2 is used to prevent damage to the card and/or the backplane.

There are two keying systems used on the HW400c/2, CompactPCI and P

2.10.3.1 Compact PC

2.10.3.2 PTMC Site

!

The host PCI bus (CompactPCI) and local PCI bus (PTMC Sites) are independent of one another, and

I

As defined in PICMG 2.10, the HW400c/2 has a Strawberry Red key, RAL # 3018,

installed in J4 signifying the existence of the H.110 Computer Telephony bus on J4.

There is no key installed in J1, signifying universal PCI signaling levels.

The PTMC Sites are capable of 3.3v signaling only. Therefore cards with 5v only IO

signals will be prevented from installation by the presence o

e HW400c/2. The key posts are located at each PTMC site, with the location

th

efined in IEEE 1386.

d

The key posts must not be removed, or damage could result from

incompatible PMC or PTMC card with 5v only IO signals.

may operate at different speeds and bus widths (see Sections 3.2.3 and 3.2.4).

f key posts installed on

installation of an

TMC.

October 10, 2006 Copyright 2006, SBE, Inc. Page 10

Page 23

HighWire HW400c/2 User Reference Guide Rev 1.0

2.10.4 Power Requirements

The power requirements of the HW400c/2 are defined for two environments:

• CompactPCI VIO of 5.0v (see Table 3)

• CompactPCI VIO set 3.3v (see Table 4).

1. All voltages are required.

2. The CompactPCI VIO has no effect on the local PCI bus VIO (PTMC sites), which is fixed at 3.3v.

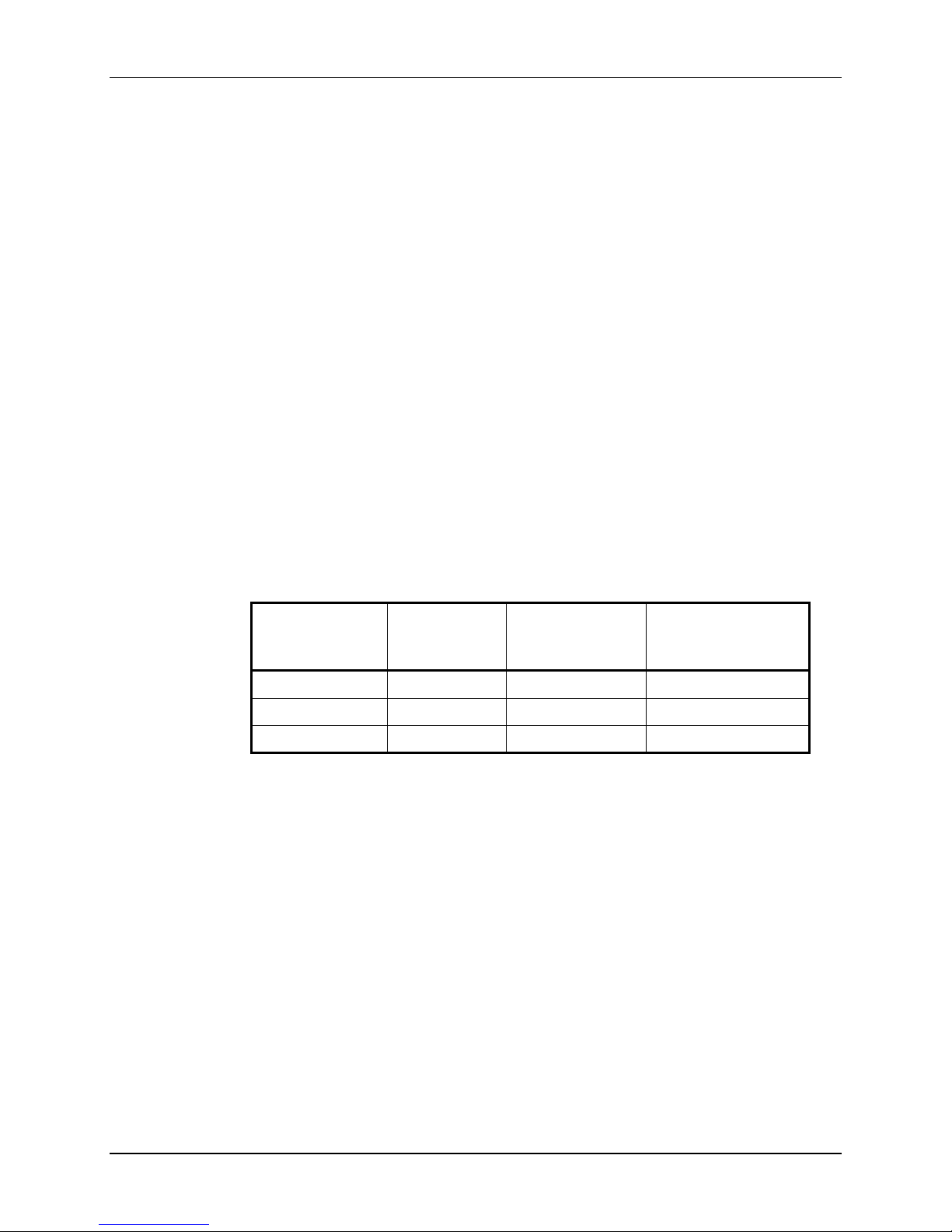

Table 3. HW400c/2 power requirements VIO = 5.0V

HW400c/2 alone

PTMC site A capacity

PTMC site B capacity

HW400c/2 with PTMC A&B

3.3V

Current (A)

2.26 6.135 0.05 38.73

4.54 2.8 0.92 40.02

4.54 2.8 0.92 40.02

11.34 11.735 1.89 118.78

5.0V

Current (A)

12V

Current (A)

Total

Power (W)

Table 4. HW400c/2 power requirements VIO = 3.3V

HW400c/2 alone

PTMC site A capacity

PTMC site B capacity

HW400c/2 with PTMC A&B

3.3V

Current (A)

5.04 4.3 0.05 38.73

4.54 2.8 0.92 40.02

4.54 2.8 0.92 40.02

14.12 9.9 1.89 118.78

5.0V

Current (A)

12V

Current (A)

Total

Power (W)

October 10, 2006 Copyright 2006, SBE, Inc. Page 11

Page 24

HighWire HW400c/2 User Reference Guide Rev 1.0

2.10.5 Switches

The HW400c/2 contains single switch that is necessary for normal operation. The

switch is an integral part of the lower ejector handle inside the front panel, and is

used along with the blue LED (see Figure 3) and the Linear Systems LTC1644, for

hot swap. The switch is connected to the PC board at J10 near the lower ejector

handle.

For debugging purposes an optional reset/NMI toggle switch and cable is available

(see Section 3.1.3). Please contact SBE Technical Support for details.

2.10.6 Product Configurations

The HW400c/2 can be manufactured with several configuration options. Specific

options include processor type and speed, memory amount, and CompactPCI

connector configuration. See Table 6, Table 16, and Section 3.2.3 for related

information.

Table 5. HW400c/2 Order time options

Standard Configuration Options

CPU Speed 1.0 GHz 1.4 Ghz, 1.7Ghz

DDR RAM 256MB 512MB, 1GB

H.110 CT bus Installed Uninstalled (see Section 3.3.3)

CompactPCI bus Installed Uninstalled (See Section 3.2.3)

Options or modifications are available upon request. Please call SBE Sales for option

availability, and/or modification requests.

Build options have significant impact on power consumption.

(see Section 3.1)

(see Section 3.2.2)

October 10, 2006 Copyright 2006, SBE, Inc. Page 12

Page 25

HighWire HW400c/2 User Reference Guide Rev 1.0

3 FUNCTIONAL BLOCKS

The HW400c/2 has six major functional blocks – the PowerPC processor, system

controller, CT Bus interface, Ethernet switch, PTMC expansion sites, and the IPMI

controller. The following sections describe these functional blocks in greater detail.

Additional features such as the connector pin outs and JTAG development support

are also described.

3.1 PowerPC Processor

The standard configuration for the HW400c/2 includes the Freescale MPC7447A

PowerPC Processor running at 1000 MHz (1 GHz) with a corresponding system bus

speed of 166 MHz. There are two additional processor variants available for the

board, which utilize the Freescale MPC7448 PowerPC Processor with a 200 MHz

system bus speed.

The operating frequency and power consumption for each processor variant is shown

in Table 6.

Table 6. HW400c/2 Processor Options

Operating

Frequency

Processor Type

MPC7447A

MPC7448

MPC7448

(Maximum)

1.0 GHz

1.4 GHz

1.7 GHz

3.1.1 MPC744X Development/Debug Support

The HW400c/2 provides external access to the MPC744X processor COP port, reset

and interrupt signals at headers J6, Jx6, J7, J8, and J9 (See Figure 2). A console port

is also provided on the front panel of the board though an RJ45 modular connector

(see Figure 4, and Section 3.1.2).

System Bus

Frequency

(Maximum)

166 MHz 8.0 / 11.5 W

200 MHz 8.0 / 15.9 W

200 MHz 21 / 29.8 W

Core Power

Consumption

(Typical/Maximum)

October 10, 2006 Copyright 2006, SBE, Inc. Page 13

Page 26

HighWire HW400c/2 User Reference Guide Rev 1.0

(-)

3.1.2 Console port

The front panel console port is connected through the MV64462 via a Linear Systems

LTC1386 EIA-562 (low voltage EIA-232) transceiver. The console port is an RJ45

modular connector mounted on the front panel using three wire (Tx, Rx, GND) EIA232 at 9600 baud, 8N1 (8 bits, No parity, 1 stop bit). Figure 4 shows the console port

pin out.

Tx

Rx

1

2

3

4

5

6

7

Shield

CONSOLE

Pin 1

Figure 4. Console port pin out

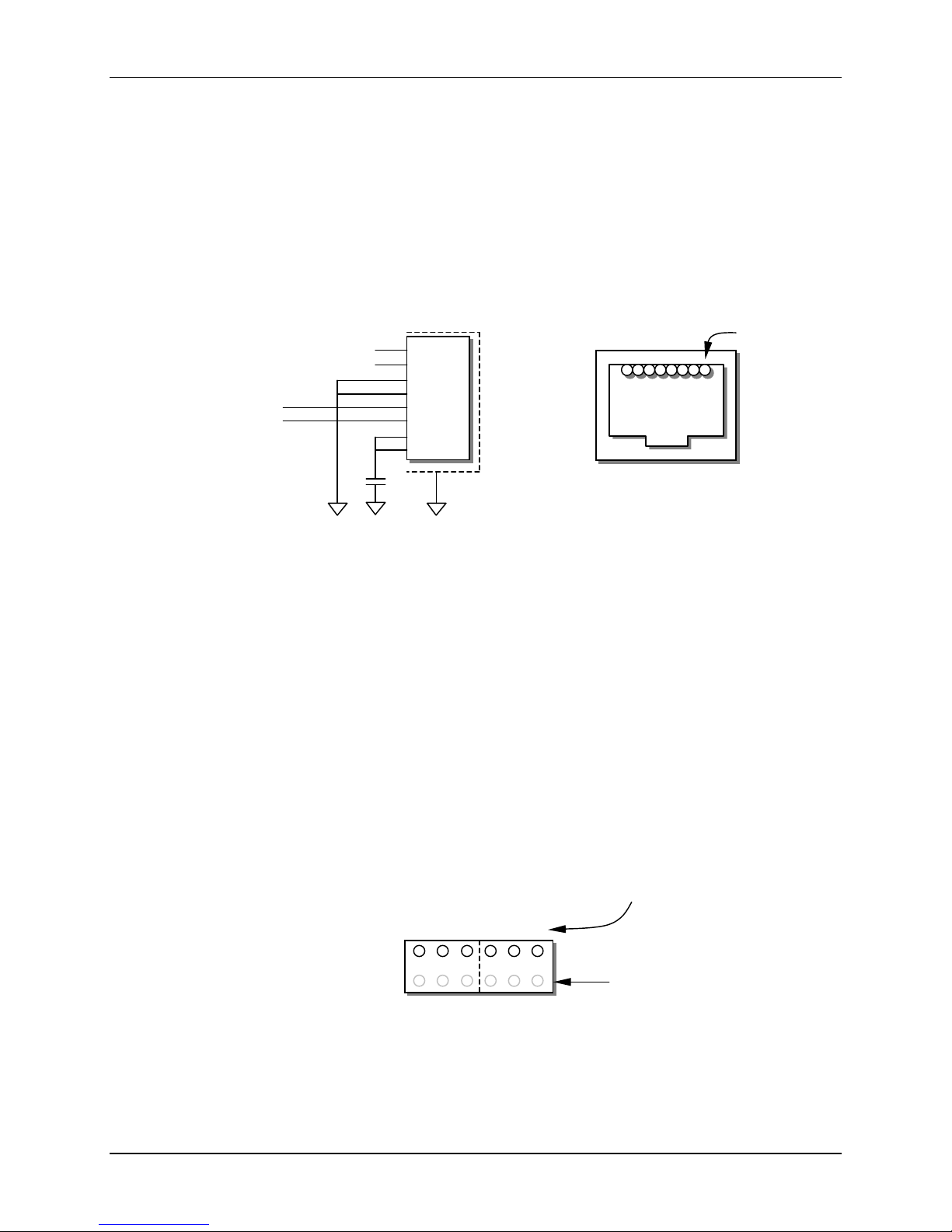

3.1.3 Pushbutton Reset / Interrupt

An optional external pushbutton reset is provided as a 6-pin header (part of J8, J9, see

Figure 2, Figure 5, and Table 7) on the board that accepts the standard SBE

developer’s debug cable with toggle switch. Contact SBE Technical Support for

additional details on obtaining a developer’s debug cable.

The same toggle switch is also used to generate a non-maskable interrupt (NMI), by

pushing it in the opposite direction. The pushbutton interrupt signal is connected to a

GPIO port of the Marvell Discovery III System Controller, which can be configured

to route it to the MPC744X if desired. See Table 11 for the GPIO port number.

J9 J8

RST O O

NMI

I2C2 I2C2

SDA SCL

Indicates location of Pin 1

This row (even numbered pins)

reserved for factory use

October 10, 2006 Copyright 2006, SBE, Inc. Page 14

Figure 5. J8, J9 Reset/NMI header

Page 27

HighWire HW400c/2 User Reference Guide Rev 1.0

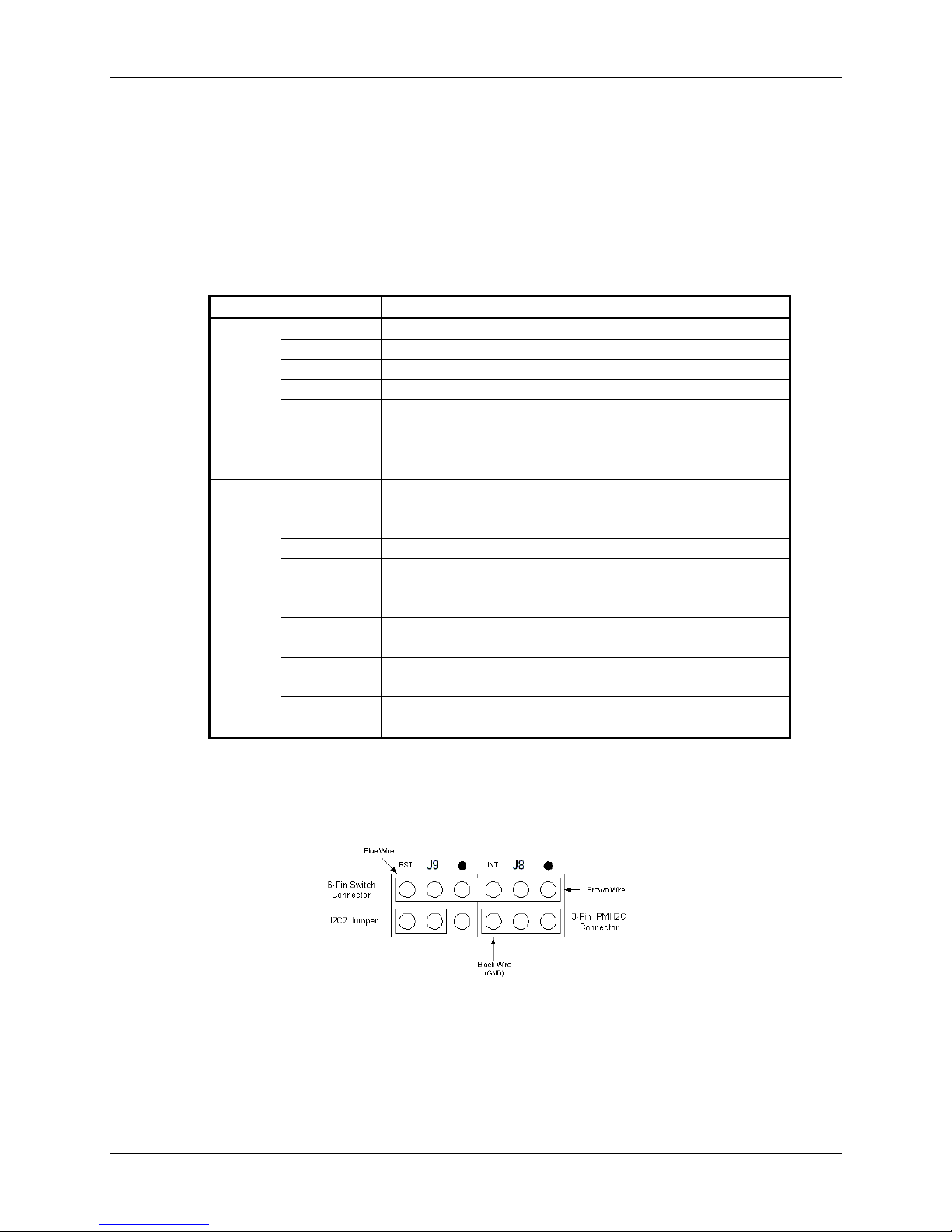

Table 7 describes the pin out of J8 and J9. Some of the pins listed are for Factory use

only.

Table 7. J8 and J9 pin out

Header Pin Label Usage

J8

1 O N/C. The “o” indicates pin one

2 SCL TWSI IPMB SCL, for Factory use only

3 none N/C. Just below the “J8” header title.

4 SDA TWSI IPMB SDA, for Factory use only

5 NMI Ground. Used in conjunction with J9, 1, holds

microprocessor Non Maskable Interrupt (NMI) active.

When used with optional reset/NMI cable toggles NMI.

6 (-) Ground. Used with TWSI cable, for Factory use only

J9

1 O Non Maskable Interrupt (NMI). The “o” indicates pin

one. Used in conjunction with J8, 5, holds

microprocessor Non Maskable Interrupt (NMI) active.

2 none N/C

3 none Reset to the microprocessor. Used in conjunction with

J9, 5, holds microprocessor in reset. When used with

optional reset/NMI cable toggles reset line.

4 I2C2 Select I2C2, Used with J9-6 to select I2C3 mode. For

Factory use only.

5 RST Ground. In conjunction with J9-3 to hold microprocessor

in reset.

6 I2C2 Ground. Used with J9-4 to select I2C3 mode. For

Factory use only.

Bottom row of J8 and J9 reserved for Factory use only.

Figure 6. J8 and J9 with optional Reset/NMI cable

October 10, 2006 Copyright 2006, SBE, Inc. Page 15

Page 28

HighWire HW400c/2 User Reference Guide Rev 1.0

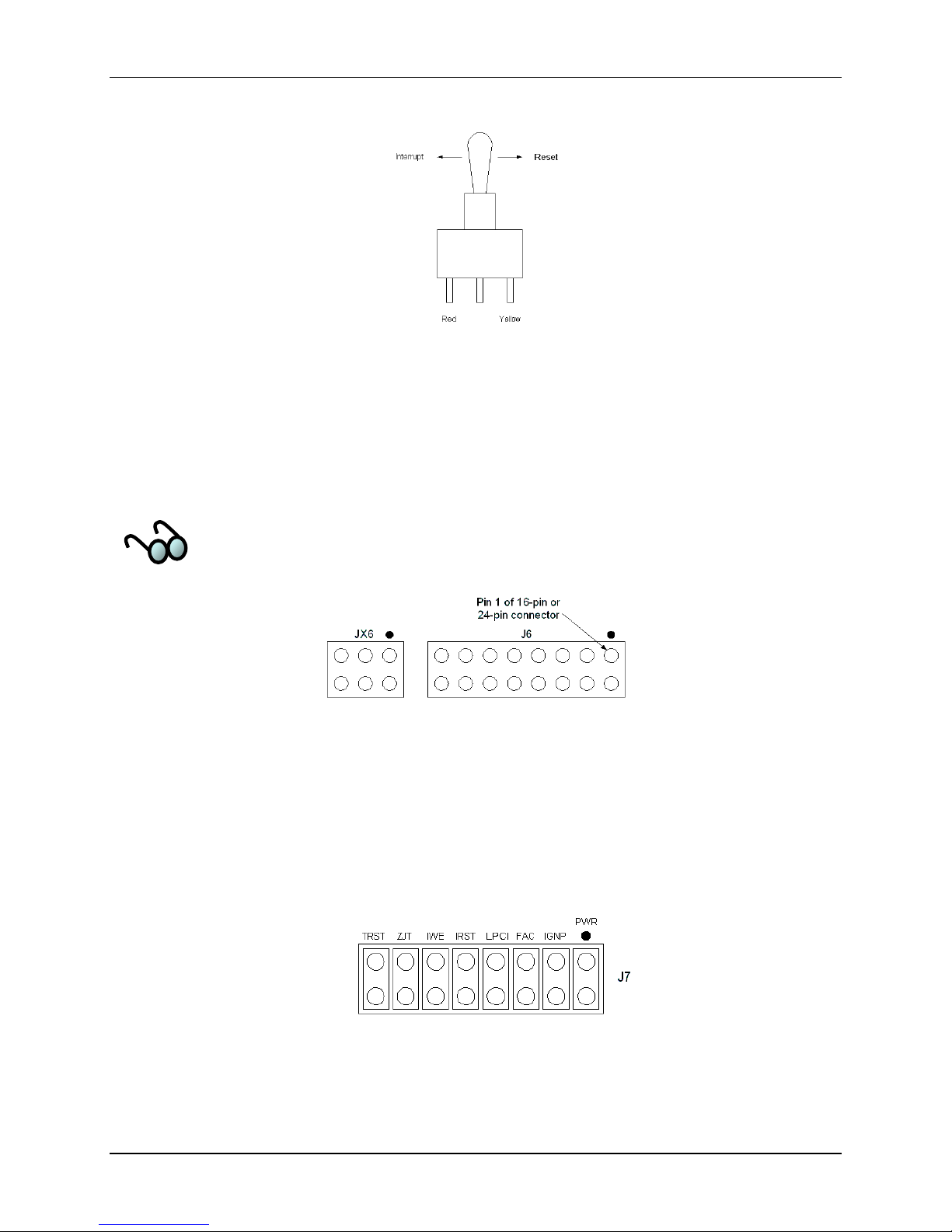

Figure 7. Optional Reset/NMI switch

3.1.4 COP/JTAG Port

A 16-pin header (J6, see Figure 2, and Figure 8) and a 6-pin header (JX6) are

provided on the HW400c/2 board for connecting to the processor’s COP (Common

On-chip Processor) port for factory development purpose

e used to access the JTAG chain for the entire board.

b

The COP/JTAG port uses 3.3V signaling.

s. The J6 header can also

3.1.5 Special Pu

Figure 8. COP/JTAG Pinout

rpose Jumper Block

Jumper block J7, located along the top of the board, is used for diagnostic and other

special purposes. Under normal operating circumstances these jumpers will remain

uninstalled. The IGNP jumper is necessary when in standalone test mode (no PCI

bus is present, or no PCI Slot One Master installed). See Figure 9 and Table 8, below.

Pin 1

Figure 9. J7 Special purpose jumper block

October 10, 2006 Copyright 2006, SBE, Inc. Page 16

Page 29

HighWire HW400c/2 User Reference Guide Rev 1.0

Table functions

.1 Jumper

3.1.5

Pins

1-2 PWR Forces board “late power” to switch “ON” at power-up

3-4 IGNP Forces board to operate as if no Host PCI bus is

5-6 FAC a) Sets “FACT” bit in BSR register for use by so

7-8 LPCI Limits Local PCI bus (PTMC sites) to 100MHz

9-10 IRST Holds IPMI Controller (U92) in reset state. (Required

11-12 IWE Enables writes to the I2C Configuration ROM (U30)

13-14 ZJT Connects only IPMI Controller (U92) to JTAG/COP

15-16 TRST Forces JTAG Reset signal inactive (Required when

Label Usage

8. J7 pin

present

b) Enables writes to Microwire EEPROM lower

addresses

maximum frequency

hen programming IPMI EEPROMs on-board via the

w

System Controller TWSI interface, see Table 7).

header (J6/JX6)

using Altera ByteBlaster)

ftware

3.2 MV64462 Sy

3.2.1 System Bu

3.2.2 Dual Data

stem Controller

The HW400c/2 uses the Marvell Discovery III (MV64462) PowerPC System

ontroller, which acts as the C

evice busses (see Figure 1). This section outlines the devices and functions

d

rfaced to the MV64462.

inte

interface between the processor, memory, PCI and

s

he system bus interface between the Freescale MPC744X processor aT

V64462 system controller is a 64-bit bus, operating at a speed of 166 MHz or 200

M

MHz depending on the pro

cessor system bus frequency (see Table 6).

nd Marvell

Rate (DDR) SDRAM

One 200-pin SODIMM module is used for the DDR SDRAM. The module is located

under one of the PTMC mezzanine cards using a low-profile SODIMM socket.

The HW400c/2 supports DDR SDRAM densities of 256 MB, 512 MB, and 1 GB as

order time options. Memory speeds of up to 200 MHz are supported for MPC7448

rocessors. Thp

e memory speed for the standard MPC7447A (1 GHz) configuration is 166 MHz

th

(see Table 6).

e memory speed is the same as the processor bus speed, and therefore

October 10, 2006 Copyright 2006, SBE, Inc. Page 17

Page 30

HighWire HW400c/2 User Reference Guide Rev 1.0

3.2.3 Host PCI B

3.2.3.1 Operation

us

The Marvell Discovery III (MV64462) host PCI bus (PCI bus 0) provides an

interface between the process

ites and the CompactPCI host. The MV64462 device acts as a PCI-to-PCI bridge

s

between the two PCI buses.

he HW400c/2 supports a 64-bit-wide bus operating at 33 or 66 MHz. PCI-X

T

operation at 66 MHz is supporte

Without CompactPCI Bus

The HW400c/2 supports the PICMG 2.16 R1.0 specification’s requirement that a

PICMG 2.16 compliant node card must have the ability to operate without the

presence of the CPCI bus. CPCI connectors J1 and J2 are present as they provide

power and geographic addressing information; however pin B6 of J1 is redefined a

signal PCI_PRSNT# in PICMG 2.16. When the PCI bus is prese

is pin is defined as GND. If the PCI bus is not present on the backplane, then it

th

must leave this pin floating (there is a 10K pull-up on the node).

The state of the PCI_PRSNT# signal is sensed at power-up (or hot-swap) and, if

inactive, the backplane PCI signals are ignored, enabling the board to boot up

normally. The primary PCI signals from the MV64462 are tri-stated in this case

the precharge voltage is switched from 1.0V to VIO (3.3V or 5V) to prevent floating

signals. The PCI Status Register (PSR) provides the status o

ection 4.2.10). The software must read this register to determine whether the PCI

S

bus is present or not and configure the board appropriately.

The HW400c/2 can also boot up without the slot 1 card in a CompactPCI chassis. A

jumper enables this feature, regardless of the state of the PCI_PRSNT# pin on

his jumper is labeled IGNP (part of J7, see Section 3.1.5), and when installed, the

T

CI reset and clock signals for MV64462 PCI bus 0 are generated internally.

P

If a Slot 1 card is present and the IGNP jumper is installed, the HW400c/2 will not be

able to communicate with the Slot 1 card.

or and CompactPCI host, as well as between the PTMC

d; however 100/133 MHz operation is not supported.

s

nt on the backplane,

, and

f the PCI bus (see

J1.

3.2.4 Local PCI

October 10, 2006 Copyright 2006, SBE, Inc. Page 18

Bus

The Marvell Discovery III (MV64462) local PCI bus (PCI bus 1) provides an

terface between the processor and the two PTMC sites. The local PCI bus is 32-

in

bits wide and operates in PCI mode at 33-66 MHz, or PCI-X mode at 66-133 MHz.

The PCI-X 133 MHz speed is allowed when only one PTMC module is installed,

it must be in

apable module is installed at Site A, the bus frequency is automatically forced to

c

100 MHz.

nd

a!

stalled at Site B. If two PCI-X capable modules are installed, or a PCI-X

Page 31

HighWire HW400c/2 User Reference Guide Rev 1.0

If a PCI-X 133 card is installed in Site B, it may be forced to 100 MHz, by installing the LPCI jumper at

(see Section 3.1.5).

J7

Module presence is detected by the state of the BUSMODE1 pin. Interrupts from

either of the two sites are fed through the MV64462 GPIO pins, and can be routed t

either the on-board processor or through the host PCI bus to the CompactPCI host

processor. The local PCI bus is independent of the ho

uses can operate at different speeds and bus widths.

b

st PCI bus, that is, the two

The local PCI Bus I/O voltage is connected to 3.3 volts only. Therefore, PTMC

modules with 5-volt only I/O signals cannot be used on the HW400c/2, and are

!

prevented

.10.3).

2

from being installed by a voltage key residing at each site (see Section

3.2.5 Serial EEPROM

o

The HW400c/2 includes a 4 K-bit non-volatile EEPROM for storing small items s

uch

as IP addresses and board serial numbers. This device is the Atmel AT93C66A,

which is organized in a 256 x 16-bit format. The EEPROM is accessed through

CPLD registers, which control a read/write state machine within

ections 4.2.25 to 4.2.28 for details on accessing the EEPROM.

S

the CPLD. See

Table 9 and Table 10 summarize the contents of the EEPROM. The first 16

addresses (0x00-0x0F) are written by SBE when the boards are manufactured, and

must not be modified. Space is reserved in the next 32 addresses (0x10-0x2F) for a

total of 16 IP Addresses, beginning with the board IP address and the Gateway I

ddress. U-boot use the remaining addresses (0x30-0xFF) for boot parameters.

a

P

Boot software must read the MAC address from the serial EEPROM and subsequently assign the value

to the MV64462 Ethernet Por

number 00:A0:D6:12:34:56.

t 0 registers. In Table 9, the MAC address is represented by the sample

October 10, 2006 Copyright 2006, SBE, Inc. Page 19

Page 32

HighWire HW400c/2 User Reference Guide Rev 1.0

Table 9. Microwire EEPROM Contents, Factory Area

Word

Address

0x00 Payload Length (words) 0x20 Format 0x03

0x01 CRC32 Byte 2 0xCC CRC32 for address 0x00

0x02 CRC32 Byte 4 0xCC CRC32 Byte 3 0xCC

0x03 Subsystem Vendor ID 0x76 Subsystem Vendor ID 0x11

0x04 Subsystem ID 0x01 Subsystem ID 0x0D

0x05 SBE MAC Address

0x06 Board Serial Number

0x07 Board Serial Number

0x08 Reserved 0x01 Reserved 0x43

0x09 Reserved 0x40 Reserved 0xD5

0x0A Reserved 0x00 Reserved 0x00

0x0B Reserved 0x00 Reserved 0x00

0x0C Reserved 0x00 Reserved 0x00

0x0D Reserved 0x00 Reserved 0x00

0x0E Reserved 0x00 Reserved 0x00

0x0F Reserved 0x00 Reserved 0x00

Bits 15-8 (MSB)

Header Byte 2

(BCD) Byte 1

(BCD) Byte 3

Typical

Value

0xA0 SBE MAC Address

0x12 SBE MAC Address

0x56 Board Serial Number

Bits 7-0 (LSB)

and 0x02-0x0F

Header Byte 1

Header Byte 3

(BCD) Byte 2

Typical

Value

0xCC

0x00

0xD6

0x34

Shaded areas indicate addresses reserved for programming by SBE at the time the boards are

manufactured.

October 10, 2006 Copyright 2006, SBE, Inc. Page 20

Page 33

HighWire HW400c/2 User Reference Guide Rev 1.0

Table 10. Microwire EEPROM Contents, Uboot Area

Word

Address

0x10 Board IP Address byte 1 0xA8 Board IP Address byte 0 0xC0

0x11 Board IP Address byte 3 0x0A Board IP Address byte 2 0x01

0x12 Gateway IP Address byte 1 0xA8 Gateway IP Address byte 0 0xC0

0x13 Gateway IP Address byte 3 0x0A Gateway IP Address byte 2 0x01

0x14 Server IP Address byte 1 0xA8 Server IP Address byte 0 0xC0

0x15 Server IP Address byte 3 0x0A Server IP Address byte 2 0x01

0x16 –

0x2D

0x2E Netmask byte 1 0xFF Netmask byte 0 0xFF

0x2F Netmask byte 3 0x00 Netmask byte 2 0xFF

0x30 Baud byte 1 0x36 Baud byte 0 0x39

0x31 Baud byte 3 0x30 Baud byte 2 0x30

0x32 Baud byte 1 0x30 Baud byte 0 0x00

0x33 CRC32 byte 3 N/A CRC32 byte 2 N/A

0x34 CRC32 byte 1 N/A CRC32 byte 0 N/A

0x35 –

0x3A

0x3B Load Address byte 1

0x3C Load Address byte 3

0x3D Load Address byte 5

0x3E Load Address byte 7

0x3F Boot Delay byte 1

0x40 –

0x5F

0x60 –

0xAF

0xB0 –

0xFF

Bits 15-8 (MSB)

Reserved for other

IP Addresses

Reserved

Boot Filename (32 bytes) N/A Boot Filename (32 bytes) N/A

Boot Arguments (80 bytes) N/A Boot Arguments (80 bytes) N/A

Boot Command (80 bytes) N/A Boot Command (80 bytes) N/A

Typical

Value

0xFF

0xFF Reserved 0xFF

0xFF

0xFF

0xFF

0xFF

0x00

Bits 7-0 (LSB)

Reserved for other

IP Addresses

Load Address byte 0

Load Address byte 2

Load Address byte 4

Load Address byte 6

Boot Delay byte 0

Addresses are typically modified by the user through the U-boot software.

Typical

Value

0xFF

0xFF

0xFF

0xFF

0xFF

0x35

October 10, 2006 Copyright 2006, SBE, Inc. Page 21

Page 34

HighWire HW400c/2 User Reference Guide Rev 1.0

3.2.6 MV64462 Ethernet Interface

The MV64462 contains an Ethernet MAC, which provides a MAC-to-MAC

connection to port 7 of the on-board Broadcom BMC5388 layer 2 Ethernet switch

(see Table 14). The connection is made via the RGMII ports on each device. The

operating speed of the RGMII port is 125 MHz.

3.2.7 MV64462 Device Interface

The Discovery III Device Interface connects the following functional elements:

• SRAM Device

• Boot PROM

• Disk-on-Chip

• CT Bus Controller

• CPLD

The device bus is a 32-bit interface with a default operating frequency of 100 MHz.

The following sections provide additional detail for each of the functional elements.

3.2.7.1 SRAM Device

The HW400c/2 includes a 512 KB SRAM device with a 32-bit wide data bus

necessary for the processor to boot. The device supports burst reads and writes.

3.2.7.2 Boot PROM

A 4 Mbit (512 KB) Boot PROM device is supported in a PLCC socket (XU4) that is

located underneath PTMC site B. The device allows for easy upgrade of boot and/or

diagnostic code. The socket also accepts most EPROM emulator cables. Burst

reads/writes to the boot ROM are not supported.

3.2.7.3 Disk-on-Chip

A Disk-on-Chip (DoC) flash file system device is used on the HW400c/2 for data

storage. DoC is a high-density flash device manufactured by M-Systems

Incorporated, with a data bus width of 16 bits. The 128 MB device is standard on the

HW400c/2, with the option of populating other devices for OEM configurations.

Burst reads/writes to the DoC are not possible due to the maximum input clock

frequency of the device (33 MHz) being slower than the 100 MHz device bus clock.

October 10, 2006 Copyright 2006, SBE, Inc. Page 22

Page 35

HighWire HW400c/2 User Reference Guide Rev 1.0

3.2.7.4 CT Bus Controller

The Agere T8110L CT bus controller on the HW400c/2 board is accessed and

programmed via the device bus. It also has a data bus width of 16 bits. Burst

reads/writes are not supported by the T8110L. See Section 3.3 for details about the

CT Bus Controller functions.

3.2.7.5 CPLD

The Complex Programmable Logic Device (CPLD) registers are also accessed via

the device bus, using an 8-bit data bus width. Miscellaneous signals such as resets

and mezzanine card selection logic are monitored and controlled by the CPLD

registers. The CPLD supports burst reads and writes. See Section 4.2 for details

about CPLD register functions.

3.2.8 Watchdog Timer

3.2.9 Reset

The Marvell MV64462 Discovery III system controller contains an internal 32-bit

Watchdog Timer that can be configured as a source of interrupt to either the

MPC744X processor or to the CompactPCI host through the PCI interrupt output.

The IPMI controller can also detect a Watchdog timeout by checking the appropriate

GPIO bit (see Table 22 in Section 3.6).

The following types of reset are available:

• Power–on reset. Resets the entire board during hot-swap or power-up.

• Optional external pushbutton reset. See Section 3.2.9 for details.

• Host PCI reset. This reset is routed through the Early Power CPLD, allowing

the host on the CompactPCI bus to reset all devices on the HW400c/2 board.

• Individual device reset. The PTMC sites, the T8110L, the Ethernet Switch

and PHYs and the Disk on Chip can all be individually reset via the CPLD

register bits (see Section 4.2.16)

• Software reset (warm reset). Initiated by writing to the CPLD’s Warm Reset

Register (WRR, see Section 4.2.18), resets the CPU, System Controller, and

all on board devices. Host PCI reset signal is not affected by warm reset.

October 10, 2006 Copyright 2006, SBE, Inc. Page 23

Page 36

HighWire HW400c/2 User Reference Guide Rev 1.0

3.2.10 Multi-Purpose Port (MPP) Usage

The MV64462 Discovery III includes a 32-bit Multi-Purpose Port (MPP) that can be

used for a variety of possible functions. The HW400c/2 board uses the MPP for the

serial Console Port signals (front-panel RJ-45), REQ and GNT signals for the local

PCI bus, I2C EEPROM activity indicator (used during boot*), and as a detector for

the various on-board interrupt sources.

Interrupts from the PTMC sites, the T8110L, the Ethernet PHYs, the Disk-on-Chip,

and the optional external pushbutton are connected individually to GPIO ports of the

Discovery III, which can then be configured to route them either to the MPC744X, or

to the host through the PCI interrupt output.

Table 11 lists the MV64462 MPP pin connections on the HW400c/2 board.

Table 11. MV64462 Multi-Purpose Port Assignments

MPP

Pin

MPP0 0x2 S0_TXD Out High Console Port (RJ-45) TXD

MPP1 0x2 S0_RXD In High Console Port (RJ-45) RXD

MPP2 0x1 PCI1_GNTn[0] Out Low GNT to PTMC Site A

MPP3 0x1 PCI1_REQn[0] In Low REQ from PTMC Site A

MPP4 0x1 PCI1_GNTn[1] Out Low GNT to PTMC Site B

MPP5 0x1 PCI1_REQn[1] In Low REQ from PTMC Site B

MPP6 0x0 GPIO6 Out Low Disk-on-Chip Lock

MPP7 0x4 INITACT Out High I2C EEPROM Active*

MPP14 0x0 GPIO14 In Low Pushbutton Interrupt

MPP15 0x0 GPIO15 In Low CPU Temp Sensor TCRIT

MPP16 0x4 WD_NMIn Out Low Watchdog Signal to IPMI

MPP17 0x0 GPIO17 In Low INTA from PTMC site A

MPP18 0x0 GPIO18 In Low INTB from PTMC site A

MPP19 0x0 GPIO19 In Low INTC from PTMC site A

MPP20 0x0 GPIO20 In Low INTD from PTMC site A

MPP21 0x0 GPIO21 In Low INTA from PTMC site B

MPP22 0x0 GPIO22 In Low INTB from PTMC site B

MPP23 0x0 GPIO23 In Low INTC from PTMC site B

MPP24 0x0 GPIO24 In Low INTD from PTMC site B

MPP25 0x0 GPIO25 In High T8110L Clock Error

MPP26 0x0 GPIO26 In High T8110L System Error

MPP27 0x0 GPIO27 In Low PHY A Interrupt

MPP28 0x0 GPIO28 In Low PHY B Interrupt

MPP29 0x0 GPIO29 In Low PHY R Interrupt (RJ-45)

MPP30 0x0 GPIO30 In Low Disk-on-Chip Interrupt

MPP31 0x0 GPIO31 In Low Disk-on-Chip Busy Signal

Multiplex

Number

Pin Function

In/Out of

Disco III

Active

High/Low

Signal Description

* By default, the HW400c/2 uses the I2C EEPROM during boot. The EEPROM

must contain the appropriate register setting to configure MPP7 as the INITACT

output. This signal is then pulled low after the EEPROM loads to initiate the

processor boot

October 10, 2006 Copyright 2006, SBE, Inc. Page 24

Page 37

HighWire HW400c/2 User Reference Guide Rev 1.0

3.3 Computer Telephony Bus Controller

The HW400c/2 includes the Agere T8110L CT Bus Controller to control TDM bus

switching between the backplane (CompactPCI J4 connector) and the local bus,

which is connected to the JN3 connector on each of the two PTMC sites.

3.3.1 H.110 Interface (T8110L)

The Agere T8110L is a H.110 CT Bus controller that provides a complete interface

between the backplane H.110 CT bus and local PTMC CT bus through a dynamically

controllable switching fabric. The H.110 interface connects to all 32 bi-directional

TDM streams of the backplane H.110 bus via the CPCI J4 connector using the

PICMG 2.5 R1.0 standard mapping. It can access any of the 4096 time slots carried

on the H.110 bus.

The local CT bus, with 32 bi-directional TDM connections, can be programmed for

data rates of 2.048Mb/s, 4.092Mb/s or 8.192Mb/s. The local CT bus of the T8110L

is connected to each of the PTMC sites via the JN3 connectors.

The PTMC configuration 2 (PT2MC) type modules only support 20 CT bus streams, while PTMC

configuration 5 (PT5MC) modules support all 32 CT bus streams.

3.3.2 T8110L Clocking Interface (T8110L)

The T8110L LSC [3:0] output pins are connected to the PTMC Output Clock Drivers

located in the CPLD. The LSC[3:0] pins are programmed as shown in Table 6.

Table 12. LSC Assignments

LSC output Signal Assignment

LSC0 CT_C8

LSC1 CT Frame

LSC2 NETREF1

LSC3 NETREF2

Figure 10 shows the local CT Bus clocking signals and how they are routed.

October 10, 2006 Copyright 2006, SBE, Inc. Page 25

Page 38

HighWire HW400c/2 User Reference Guide Rev 1.0

Figure 10. Local CT Bus Clocking Block Diagram

Control for the local “A” and “B” bus drivers is provided by bits 4, 5, 6, and 7 in the

Clock Select Register (CSR). Refer to Section 4.2.1 for further details. Figure 11

shows the implementation.

October 10, 2006 Copyright 2006, SBE, Inc. Page 26

Figure 11. Local CT Bus Clock Generation

Page 39

HighWire HW400c/2 User Reference Guide Rev 1.0

The T8110L can be programmed such that its local frame reference (LREF [3:2])

puts are used to generate all of the TDM bus clocks and syncs. The T8110L Local

in

Clock Reference Inputs have been assigned to the PTMC JN3 H.110 clock pins as

shown in Table 13.

ble 13. LREF [3:2] Assignments

Ta

LREF input Assigned to Clock

LREF2 PT_NETREF1

LREF3 PT_NETREF2

3.3.3 Operation in Non-H.110 Backplane

The defau

lt HW400c/2 configuration has the H.110 interface installed. However, in

the event that the HW400c

have an H.110 bus or the H.110 interface is not installed, the CT_EN pin on J4 (pin

) The state of the C red D

C23 is not grounded. T_EN pin is sto in bit 7 of the CPL

BSR r (see 4.2.2). If H.110 is not present, the H.110

egister for access by software

interfa abled.

ce should not be en

Even ble on the ctPCI b al CT

if the H.110 bus is not availa Compa ackplane, the loc

Bus connections are still valid and therefore PTMC Site A and PTMC Site B can

comm is local to 400c/2

unicate via the CT Bus that the HW board.

3.4 Layer 2 Ethernet Switch

The Broadcom BCM5388 Layer 2 Ethernet sw

the HW400c/2 board. The BCM5388 has four

MAC/PHYs, and four additional Gigabit MACs with external RGMII connections.

Three of the additional MACs are connected to Broadcom BCM5461S external

PHYs, and one is connected directly to the MV64462 MAC port as shown in Table

14.

Table 14. Layer 2 Switch Port Assig

Switch P

ort Device or Port PHY Address Connection Type

7 MV64462 System Controller N/A MAC-to-MAC RGMII

6 Front Panel RJ-45 00110 1 External PHY

2 PT5MC Slot A, Link Port A N/A 1 Integral PHY

4 Y PT5MC Slot A, Link Port B 00100 1 External PH

3 PT5MC Slot B, Link Port A N/A 1 Integral PHY

5 PT5MC Slot B, Link Port B 00101 1 External PHY

0 PSB Link Port A N/A 1 Integral PHY

1 PSB Link Port B N/A 1 Integral PHY

/2 board is used in a PICMG 2.16 chassis that does not

itch connects to the various devices on

Gigabit Ethernet ports with integral

nments

October 10, 2006 Copyright 2006, SBE, Inc. Page 27

Page 40

HighWire HW400c/2 User Reference Guide Rev 1.0

3.4.1 Switch Re

3.4.2 MV64462 S s

gisters Initialization and Monitoring

The switch is initialized and its registers polled by utilizing its SPI bus interface.

This interface is connected through the CPLD. For a description of how to access the

SPI interface, please refer to Section 4.4.

y tem Controller Ethernet Interface

The Marvell MV64462 System Controller on

BCM5388 Ethernet switch. The connection speed must be set to 1

MAC-to-MAC connection with the clock sou

transmitter signals from the switch are connected to