FILE No. K-14-21

SERVICE MANUAL

MULTI VIDEO PROCESSOR COLOUR

QUAD COMPRESSOR

VQC-800 (EUROPE)

PRODUCT CODE No. 144 024 72 (U.S.A) 144 024 73 (EUROPE)

MVP-8 (U.S.A.)

Specifications

| Signal system | Based on NTSC color standard (in U.S.A.) | Video alarm sensor | Built-in, ON/OFF mode setting per one camera screen |

|---|---|---|---|

| Video camera input |

Based on PAL colour standard (in Europe)

8 inputs, color cameras Video signal : VBS (Video/Burst/Composite sync) or VS (Video/ Composite sync) 1.0 Vp-p, 75 Q, CAMERA |

External alarm input |

8 inputs, one per camera, activated by

contact closure (LOW input, normally open), supplied through CONTROL female receptacle (15-pin) Adjustable alarm active time : 10, 20, 30 or 60 sec. |

| VCR input |

IN BNC connector × 8

Video signal : VBS, 1.0 Vp-p, 75 g, VCR IN BNC connector × 1 |

External alarm output |

1 output, activated by contact closure

(LOW output, normally open), supplied through CONTROL female receptacle |

| Video output |

2 channels

Quad Only : VBS, 1.0 Vp-p, 75 Q, QUAD ONLY BNC |

Buzzer

Remote input |

(15- pin)

Built -in, ON/OFF setting Added the exclusive remote control circuit activated by contact closure |

|

Quad/Full : VBS, 1.0 Vp-p, 75 Q,

QUAD/FULL BNC connector x 1 |

(LOW input, normally open), supplied

through CONTROL female receptacle (15- pin) |

||

| Camera sync | Built-in sync circuit | Switching input (SW IN) | Activated by contact closure (LOW input, |

| Disates a second 1 to 1 is suid | CONTROL fomale recontacle (15 pin) | ||

| Quad A picture | Displays cameras 1 to 4 in quad | Manus annon cottings | |

|

Quad B picture

Quad A/B picture |

Displays cameras 5 to 8 in quad

Displays alternately between Quad A and Quad B Adjustable switching time : 1, 2 or 4 sec. |

menu screen settings |

QUAD MODE : ON/OFF, video alarm

sensor : ON/OFF and sensitivity level, video alarm sensor position, zoom |

| Full screen picture | Allows full screen display of selected camera or camera triggering alarm |

position, ZOOM : ON/OFF, STILL : ON/

OFF and alarm TIME, BUZZER ON/OFF |

|

| Still picture | Possible (while displaying quad, zoom or | and QUAD A/B switching TIME | |

|

(Memory-lock function)

Sequential picture |

VCR playback zoom pictures)

Displays cameras 1 to 8 sequentially in full |

Power requirement |

120 VAC ± 10 V, 60 Hz (in U.S.A.)

220-240VAC, 50Hz (in Europe) |

| (Auto switcher function) |

screen format

Adjustable switching time : External or O |

Power consumption | 11 W (approx., when connected 8 cameras) |

| Zoom function |

to 10 sec.

Possible (in quad only) Enlarges quad pictures 1 to 8 to full screen |

Operating temperature

Operating humidity Dimensions |

10 to 75 %

420 (W) × 44 (H) × 320 (D) mm |

| VCR playback function | Possible (both quad and full) | Weight | 3.3 kg (approx.) |

| VCR playback zooming | Possible (in quad only) | Accessories | AC power cord × 1 |

| Power failure recovery | Possible, returns to the original operation |

DIN plug with 15-pin × 1

Fixer × 1 |

*Specifications subject to change without notice.

L8QQ5/US, EX

REFERENCE No. SM 541010

PRODUCT SAFETY NOTICE

Product safety should be considered when a component replacement is made in any area of this unit. Components indicated by the symbol A in the parts list and the schematic diagram designate components in which safety can be of special significance. It is particularly recommended that only parts designated on the parts list in this manual be used for component replacement designated by the symbol. No deviations from resistance, wattage or voltage ratings may be made for replacement items designated by the symbol.

TABLE OF CONTENTS

| 1. Overall Principles | 2 |

|---|---|

| 2. Block Diagram | 5 |

| 3. Explanation of Operation of Circuits | 7 |

| 3-1. Analog Circuits | 7 |

| 3-1-1. Power circuit (PW-1) ····· | 7 |

| 3-1-2. Switcher circuit (VD-1) | 9 |

| 3-1-3. Decoder circuit (VD-1) ······ | 14 |

| 3-1-4. Encoder circuit (VD-1) ······ | 19 |

| 3-1-5. On-screen circuit (VD-1) | 25 |

| 3-2. Control Circuits | 33 |

| 3-2-1. Buzzer circuit (VD-1) ····· | 33 |

| 3-2-2. Reset circuit (VD-1) ····· | 34 |

| 3-2-3. EEPROM circuit (VD-1) ······ | 35 |

| 3-2-4. Remote control circuit (VD-1) ····· | 37 |

| 3-2-5. Interface circuit (VD-1) ····· | 40 |

| 3-2-6. System control circuit (VD-1) ····· | 42 |

| 3-2-7. Key input and LED display circuit (SY-1, 2) | 48 |

| 3-3. Digital Circuits ····· | 50 |

| 3-3-1. A/D converter circuit (IC211,IC221, IC231, IC241) (VD-1) | 50 |

| 3-3-2. D/A converter circuit (IC251) (VD-1) | 52 |

| 3-3-3. Gate array circuit (VD-1) | 54 |

| 3-3-4. Memory circuit (VD-1) | 74 |

| 3-3-5. Oscillator circuit (VD-1) ······ | 83 |

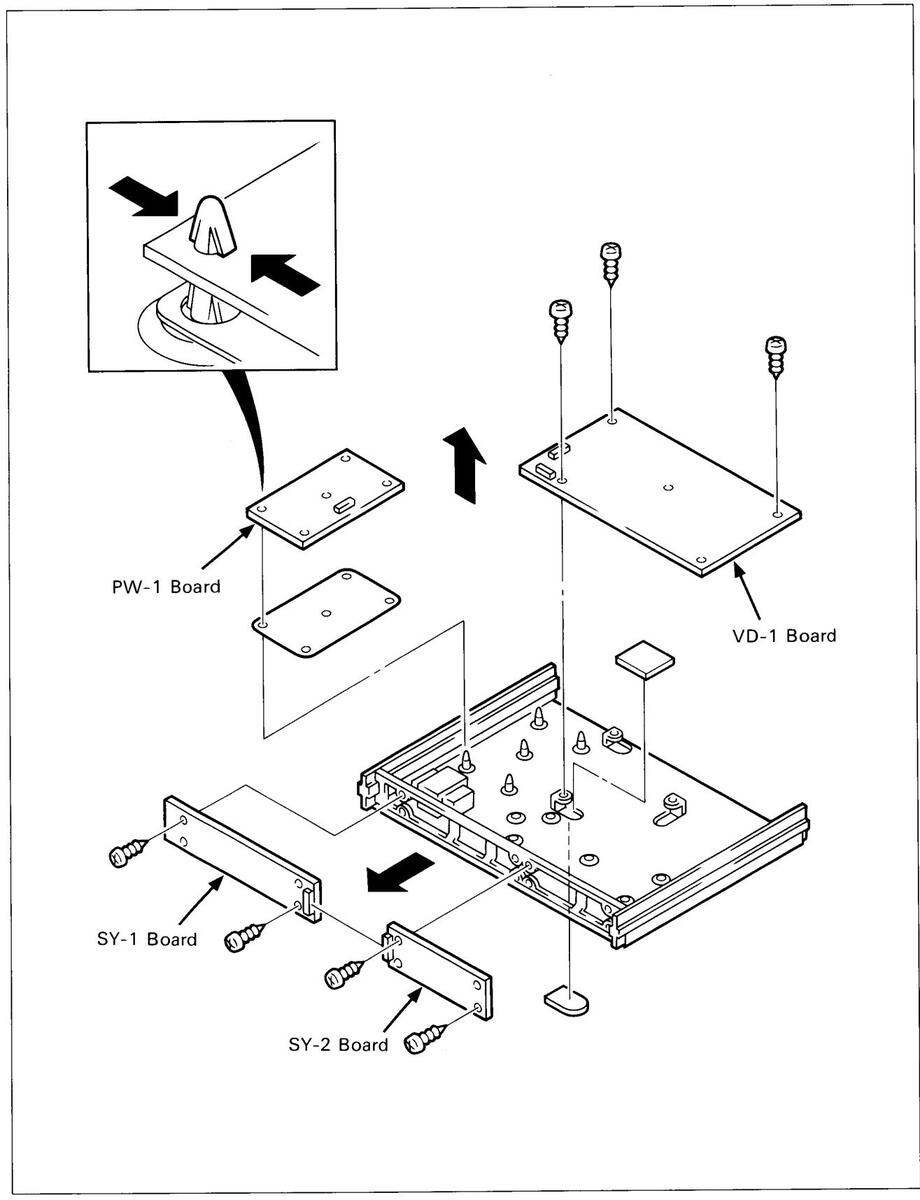

| 4. Cabinet Removal | 84 |

| 5. Circuit Board Locations | 85 |

| 6. Circuit Board Removal | 86 |

| 7. Adjustments | 87 |

| 7-1. Standard settings | 87 |

| 7-2. Gate array adj. | 87 |

| 7-3. Decoder VCXO adj. | 87 |

| 7-4. Encoder VCXO adj. | 88 |

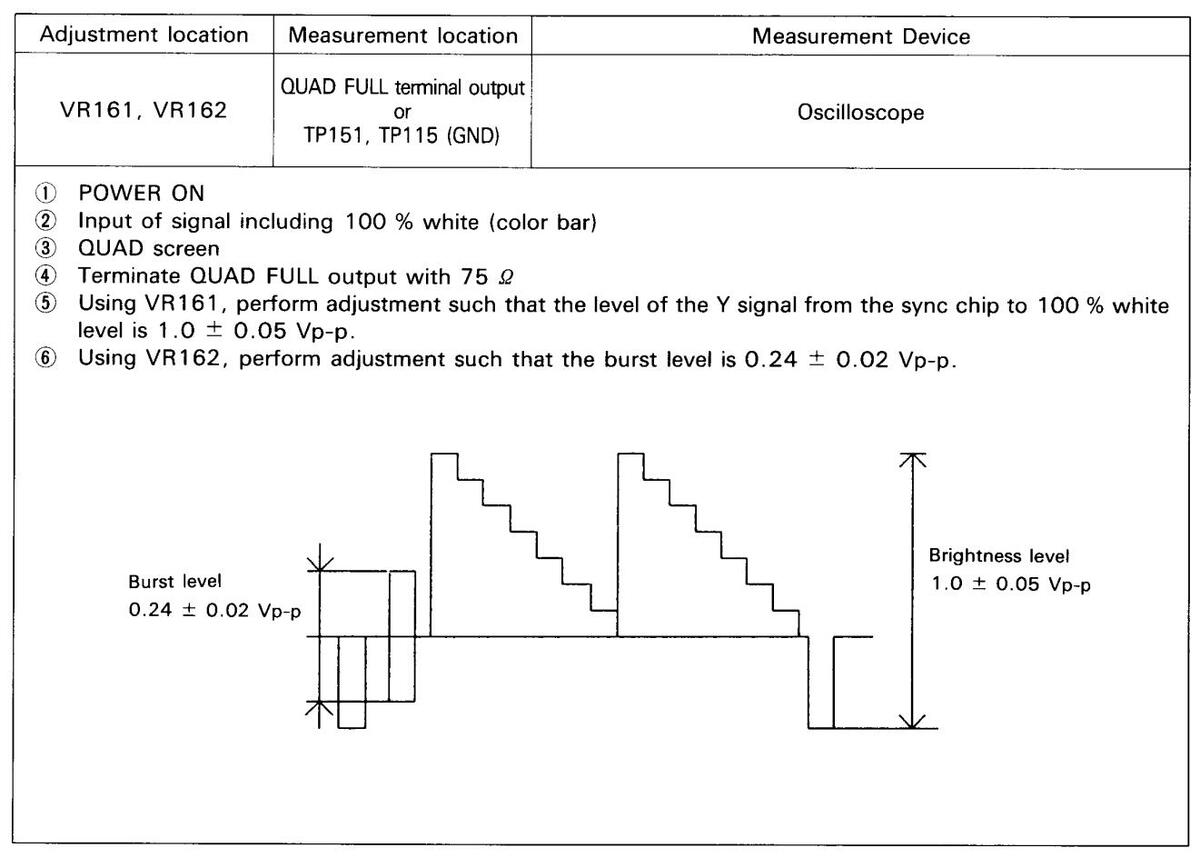

| 7-5. Brightness and burst level adj. | 88 |

| 7-6. Tint adj. | 89 |

| 7-7. Character width adj. 1 (Full screen) | 90 |

| 7-8. Character width adj. 2 (Quad screen) | 90 |

| 7-9. Bit-drop check | 91 |

| 7-10. V. adj. check ····· | 91 |

| 7-11. Image sensor check | 92 |

| 7-12. Alarm IN/OUT check | 92 |

| 7-13. SW. IN check | 93 |

| 7-14. Clearing the E 2 PROM | 93 |

| 7-15. TP, VR, VC locations | 94 |

1. Overall Principles

This color quad compressor, operating in component form, takes in eight input picture signals and separates each into its three component signals (Y, R-Y, and B-Y) and its synchronization signals (VD, HD). The unit then performs A/D conversion on only the three component signals, performs thinning compression on the quantized data based on the synchronization signals, and writes the result to memory. Finally, it reconciles the synchronization signals based on a reference signal, performs D/A conversion on the component signals, and creates a picture signal from the component signals and synchronization signals. The digital processing from A/D through D/A for each one of the four respective screens is performed by a single gate array.

1-1. Block Diagram

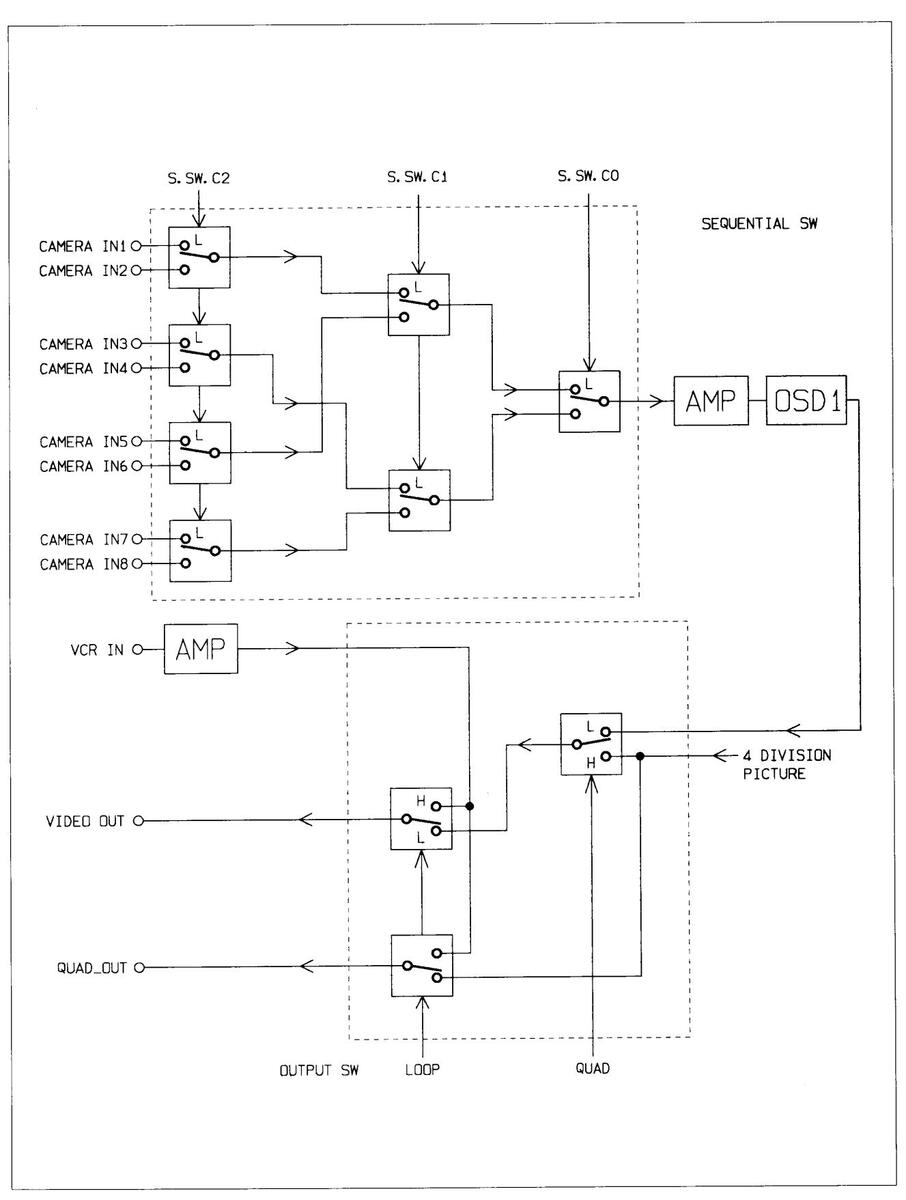

The block diagram for this unit is shown in diagram 2-1, and the function and circuit board configuration of each component is explained below.

| 1 | Analog processing circu | uits |

|---|---|---|

| Power circuit (PW1) : | Conversion of the | |

| for this set | ||

| Folgation of one output | ||

|

from among eight input

camera signals. Quad screen input switching. |

||

| Decoder circuit(VD1) : | Color signal demodulation and intensity extraction. | |

| Encoder circuit (VD1) : |

Color signal modulation

and picture signal creation from the intensity signal. |

|

| On-screen circuit (VD1) | Character insertion. | |

| 0 | ||

| C | Buzzer circuit (VD1) | Oscillation and switching |

| Buzzon on ball (1917) | for buzzer indicator. | |

| Reset circuit (VD1) | Reset of microcomputer | |

| and on-screen IC. | ||

| EEPBOM circuit(VD1) : | Data storage. | |

| Bemote control circuit (VD1) : | Decoding of wired remote | |

| control. | ||

| Interface circuit(VD1) : | Alarm signal I/O and SW IN. | |

| System control circuit(VD1) : | Central control of this set. | |

| Key input circuit (SY1, 2) : | Key input read-in. | |

| LED display circuit (SY1, 2) : | Mode display. | |

| 3 | Digital circuits | |

| 9 | A/D circuit (VD1) : | Digital conversion of decoder output. |

| D/A circuit (VD1) : | Analog conversion of | |

| digital output. | ||

| Gate array circuit (VD1) : | All digital processing. |

Memory circuit (VD1) : Field and line memory. Oscillator circuit (VD1) : Reference oscillator.

1-2. Signal Flow

The flow of signals, from input in each mode through dual output (QUAD OUT, VIDEO OUT), is explained below.

-

1. QUAD A OR B Mode

- (1) QUAD OUT ... The input signals from cameras 1 to 4 or cameras 5 to 8 enter decoders 1 to 4, and analog processing is performed. Then digital conversion is carried out by the A/D converter and, using digital processing in the gate arrays and memory, the data is thinned out to compress and reduce it. Finally, analog conversion is carried out by the D/A converter, a composite picture signal is created by the encoder, characters are inserted by the OSD, and output is performed.

- VIDEO OUT … Output is performed to the VIDEO OUT terminal via the switch for the composite picture signal output produced in ①.

-

2. QUAD A/B Mode

- (1) QUAD OUT ... Mode in which, based on the input selection switch in 1-(1), decoder input switches alternately between cameras 1 to 4 and cameras 5 to 8.

- VIDEO OUT … Output is performed to the VIDEO OUT terminal based on the switch for the composite picture signal output produced in ①.

-

3. Full Screen or Switcher Mode

- (1) QUAD OUT … 1-(1) or 2-(1).

- VIDEO OUT ... Switching and output of input from cameras 1 to 8 are performed according to the program specified from the menu.

-

4. 1:1 Zoom Mode (1) OUAD OUT ··· Follows The sme process as

- 1-① or 2-①, but performs 1:1 output without reduction

being performed by the digital processing component.

- (2) VIDEO OUT ... Output is performed to the VIDEO OUT terminal via the switch for the composite picture signal output produced in (1).

-

5. VCR Playback Mode

-

1 QUAD OUT ... The VCR IN signal enters decoder 4 via a switch, undergoes four-fold zoom processing, and is output to the D/A for analog conversion. A composite picture signal is then created by the encoder, and output is performed. One of four locations to zoom can be selected via key input.

- (2) VIDEO OUT ... Output is performed to the VIDEO OUT terminal via the switch for the composite picture signal output produced in ①.

-

1 QUAD OUT ... The VCR IN signal enters decoder 4 via a switch, undergoes four-fold zoom processing, and is output to the D/A for analog conversion. A composite picture signal is then created by the encoder, and output is performed. One of four locations to zoom can be selected via key input.

-

6. Menu Mode

- QUAD OUT ··· Normally, in QUAD A OR B and QUAD A/B, menu characters are only output when using the quad screen with the menu screen.

- (2) VIDEO OUT ··· Based on the menu, either the full screen or the quad screen is output.

-

7. Alarm Mode

- QUAD OUT ··· Based on the program selected from the menu, either the display switches to 1:1 zoom or alarm display is performed.

- (2) VIDEO OUT ... From the menu, when zoom or full screen is specified for alarms, the display switches to zoom or full screen upon alarm input.

3. Explanation of Operation of Circuits

3-1. Analog Circuits

3-1-1. Power Circuit (PW1)

This unit utilizes a switching method-chopper switching-in its power supply.

The power supply circuit is shown in figure 3-1.

Primary input of AC 120 V in North America, AC 220-240 V in Europe from the power cord passes through FU501 and the power switch (dual-trip type), and is then connected with the power supply transformer. The AC power is stepped down by the transformer, full-wave rectified by bridge diode D5101, and input to pin 1 of IC511 (L4962E/A) as DC 17 V.

A switching voltage as illustrated in figure 3-2 is output from pin 7 of IC511, then becomes a DC voltage of approximately 5.1 V via L5101, and is

finally supplied to VD-1 (the main circuit board) from CN511.

The IC511 switching regulator sets soft starts via C5103, and sets switching frequency via R5101 (3.9 kΩ and C5104 (2200 pF). The block diagram for this IC is shown in figure 3-3. The frequency for this unit is approximately 97 kHz. The waveforms for pin 5 and pin 7 of this IC511 are shown in figure 3-2.

In response to variations in the voltage of the input to IC511, as shown in figure 3-2, constant voltage output from CN511 is facilitated by shortening the t on interval when the voltage is high and, conversely, lengthening the t on interval when the voltage is low, such that the area of t on is constant during period T. This switching regulator can supply a current of 1.5

A within an output voltage range of 5.1-40 V.

Fig. 3-1. Power Supply Circuit Diagram

Fig. 3-2. Switching Frequency and Switching Voltage

Fig. 3-3. IC511 Block Diagram

3-1-2. Switcher Circuit (VD1)

This switcher circuit is configured to utilize five ICBA7603F units, as shown below.

«Explanation of BA7603F»

Function Contains three video signal (picture signal) switching circuits, each of which is configured with two input terminals (IN 1 and IN 2), one output terminal (OUT), and one input switching control terminal (CTL). The input terminal is a so-called sync chip clamping input type in which the sync edge of the video signal (picture signal) is adjusted to a constant potential.

Electrical Characteristics

| - | |||||

|---|---|---|---|---|---|

| ltem | Minimum | Standard | Maximum | Units |

Measurement

Conditions |

| Operating voltage range | 4.5 | 5.0 | 5.5 | v | |

| Circuit current | 13.0 | 20.0 | mA | ||

|

Maximum

output level |

2.6 | 2.9 | - | Vpp |

f=1 kHz

THD =0.5% |

| Voltage gain | -0.5 | 0 | +0.5 | dB |

f=1 MHz

Vin=1 Vpp |

|

Inter-channel

crosstalk |

- | -65 | - | dB |

f=4.43 MHz

Vin=1 Vpp |

|

Frequency

characteristics |

-3 | 0 | +1 | dB |

10MHz/1MHz

Vin=1 Vpp |

| CTL terminal switching level | 2.0 | 2.5 | 3.0 | V |

Figures 3-4. and 3-5. present a switching operation description and an equivalent IC circuit.

As shown in figure 3-4, using the sync chip clamping circuit, the sync edge voltage is nearly constant even upon switching to a signal with a varying average DC level.

This switching circuit is divided functionally into the following three parts.

- ① QUAD decoder input switching

- 2 Sequential switching and amplification

- 3 Output switching

- (1) QUAD decoder input switching

QUAD decoder input switching is used during QUAD A/B mode. The switch signal is output from microcomputer to G.A to switch.

The relationship between the switch control signal and the decoder input video signal is as shown below (figure 3-6.)

|

Control

Signal |

Decoder

Input |

|

|---|---|---|

| L | Camera 1 | |

| QUAD SVV I | н | Camera 5 |

| L | Camera 2 | |

| UUAD SVV 2 | н | Camera 6 |

| L | Camera 3 | |

| UUAD SW S | н | Camera 7 |

| L | Camera 4 | |

| 10AD 5W 4 | н | Camera 8 |

(2) Sequential Switching and Amplification The switch circuit in figure 3-7 (a) controls output via microcomputer output sequential switches CO to C2.

| S. | SW. | со | S. SW. | C 1 | S. 5 | SW. | C 2 | OUT | ||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| L | L | L | Camera 1 | |||||||||

| L | L | н | Camera 2 | |||||||||

| L | н | L | Camera 3 | |||||||||

| Ĺ | Н | Н | Camera 4 | |||||||||

| Н | L L | Camera 5 | ||||||||||

| Н | L | L H | Camera 6 | |||||||||

| Н | Н | L | Camera 7 | |||||||||

| Н | Н | н | Camera 8 | |||||||||

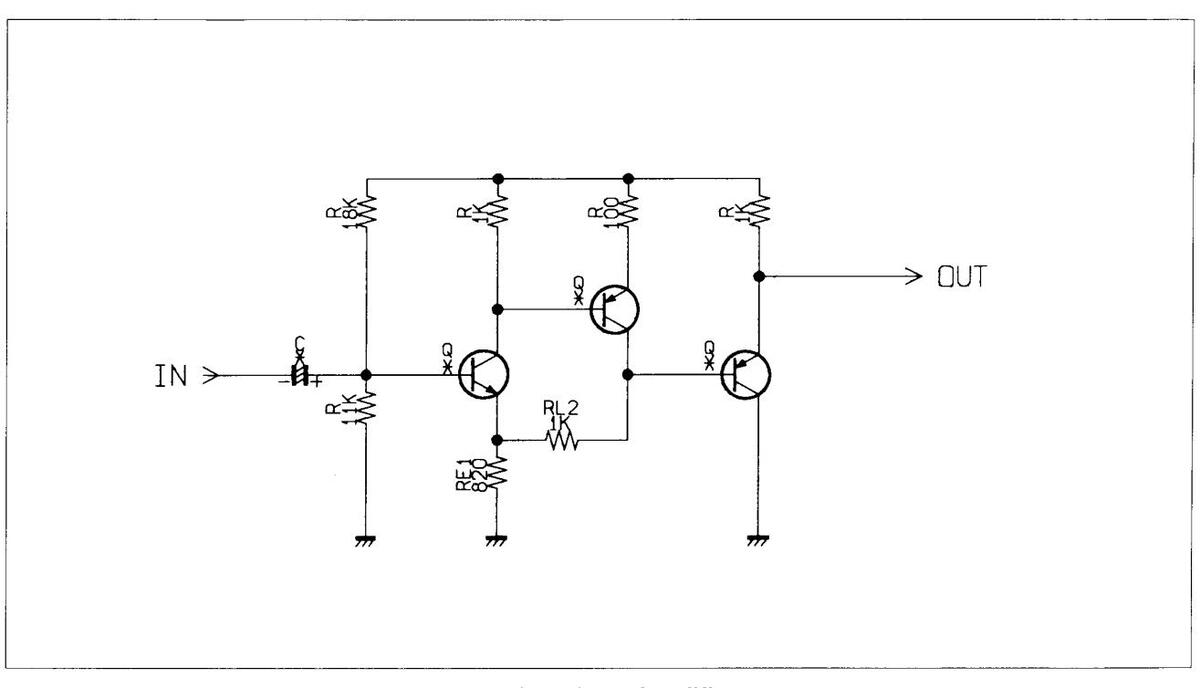

Amplifier This is a +6 dB video amp which takes a 1.0 Vpp video level which has been terminated with 75 Q and makes it 2.0 Vpp again. (Used for amplification of the VCR IN signal after the switcher.) This circuit utilizes negative feedback, so it offers high stability and achieves excellent frequency characteristics (figure 3-8). Amplification factor ANF=1 + R1.2/

Amplification factor ANF=1 + R1.2/ RE1=2 (6 dB)

(3) Output switching

The output switch circuit is as shown in figure 3-7 (b). When the VCR playback key input goes on, LOOP "H" is output from the microcomputer, and V.OUT and QUAD OUT both output the VCR IN input signal. L is output to the QUAD signal during either sequential or full screen output.

Control Signal

| QUAD | LOOP | V. OUT | QUAD. OUT |

|---|---|---|---|

| L | L | Sequential and full screen | Quad screen |

| L | Н | VCR IN screen | VCR IN screen |

| н | L | Quad screen | Quad screen |

| н | н | VCR IN screen | VCR IN screen |

Fig. 3-4. Description of Operation

Fig. 3-5. Block Diagram

Fig. 3-6.

Fig. 3-7.

Fig. 3-8. 6 dB Amplifier

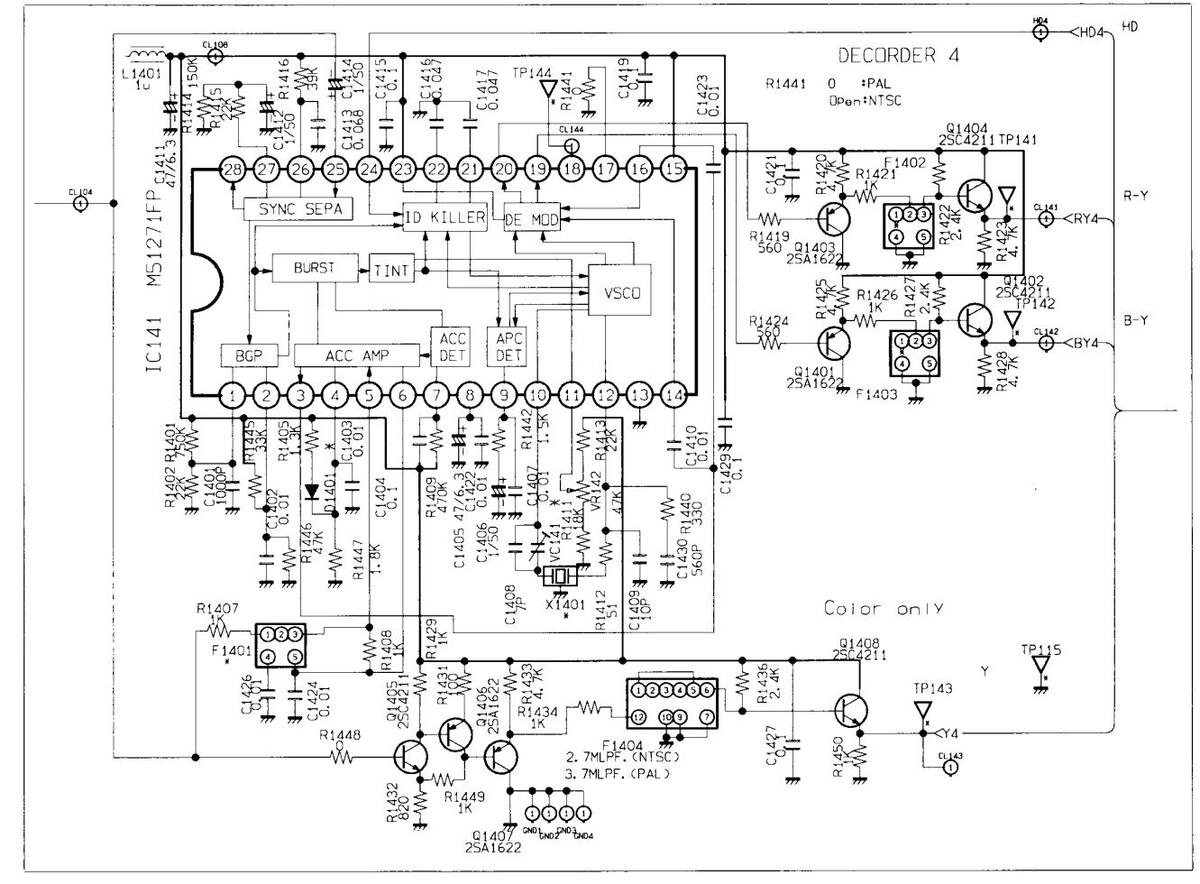

3-1-3. Decoder Circuit (VD1)

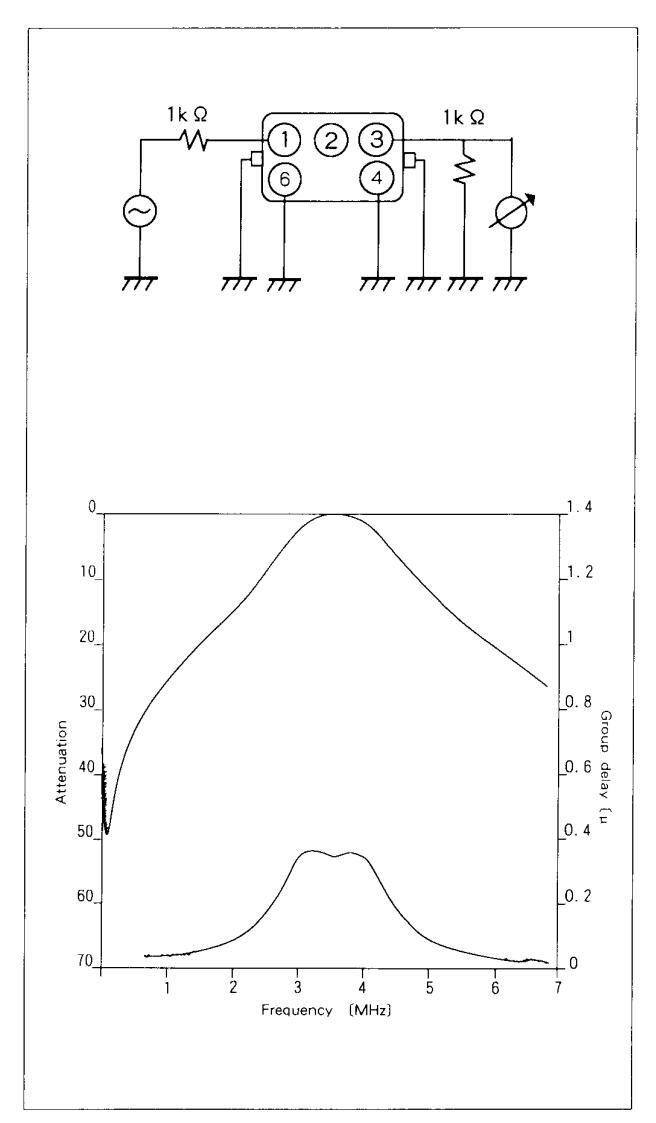

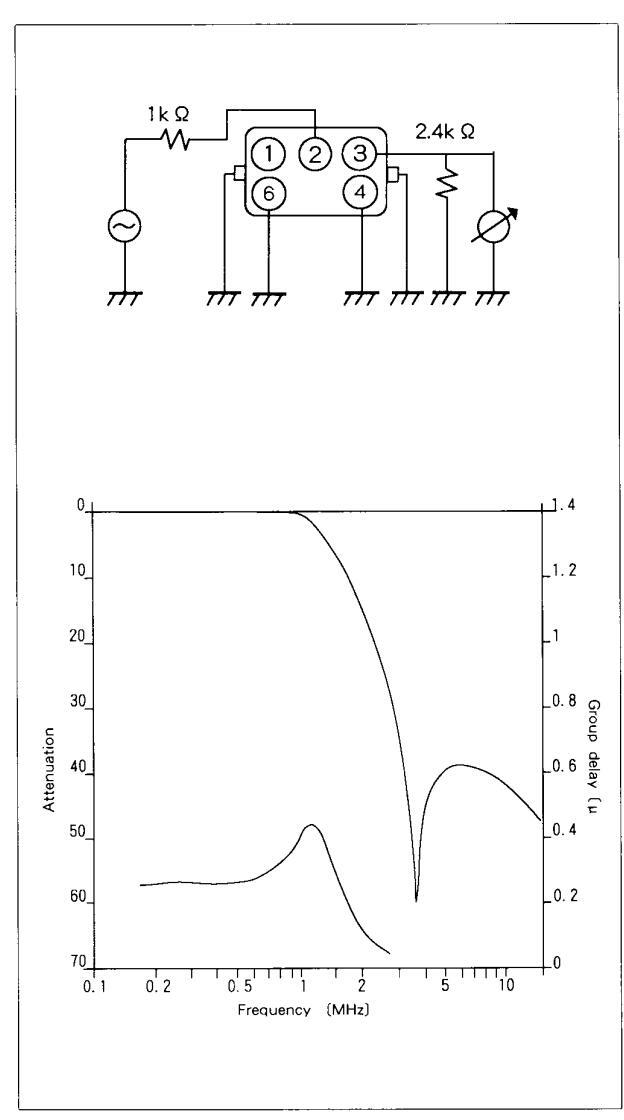

The circuit diagram, IC block diagram, terminal explanation, key signal waveforms, and filter characteristics of the decoder are shown in figures 3-9, 3-10, 3-11, 3-12, and 3-13.

«Signal Flow»

The flow of signals in the decoder are divided into the Y and C2 systems and explained below.

The picture signal, after flowing from the immediately previous switch and through the buffer, branches off in three directions.

- (1) It is amplified to 2 Vpp by the intensity system's 6 dB amplifier, the color signal is removed by the LPF, and it is passed through the buffer and output to the A D. The Y level at this point is approximately 1.3 Vpp (fig. 3-12 (b)).

- It enters pin 25 of the IC, the horizontal sync is separated, and it is output to pin 28. Based on this, the BGP is produced from pins 1 and 2. BGP width is determined by the potential at pin 2.

3 The chroma components alone are retrieved via the BGP and input into pin 6.

At that point, the burst is extracted based on the BGP, wave detection is carried out, and then amplification (ACC) is performed so that the chroma signal's level becomes constant. This ACC level is determined by the potential at pin 4. This amplified chroma signal is output from pin 3. enters pins 14 and 16. and is synchronized with the burst via VCXO. Then, based on 4Fsc from the oscillator. Fsc signals differing by 90 and 180 degrees are created, and the chroma signal is demodulated into the coloration signal. Harmonics are then removed from the separated coloring signal using the LPF, and the signal is output to the A/D via the buffer. The coloring signal level at this point is approximately 0.6-0.9 Vpp. Tint adjustment is carried out according to the potential at pin 11.

To adjust the sub-carrier, the Fsc frequency at pin 18 is regulated by turning the trimmer at pin 10.

Fig. 3-9 Decoder Circuit Diagram

Fig. 3-10. Block Diagram (M51271FP)

| Pin No. | Function |

|---|---|

| 1 | Burst gate pulse position |

| 2 | Burst gate pule width adjustment (DC) |

| 3 | Color signal output |

| 4 | ACC level adjustment (DC) |

| 5 | Color signal input |

| 6 | Input bypass capacity |

| 7 | ACC filter |

| 8 | Reference potential |

| 9 | APC filter |

| 10 | VCXO output adjustment (size) |

| 11 | Tint adjustment (DC) |

| 12 | VCXO input |

| 13 | GND |

| 14 | B-Y input (before demodulation) |

| 15 | VDD |

| 16 | R-Y input (before demodulation) |

| 17 | NTSC/PAL switch - NTSC:OPEN; PAL:GND |

| 18 | Sub-carrier output |

| 19 | B-Y output |

| 20 | R-Y output |

| 21 | Killer filter capacity |

| 22 | Killer reference filter capacity |

| 23 | BLK pulse input |

| 24 | HD pulse input |

| 25 | Sync separation video signal input |

| 26 | Sync separation feedback capacity |

| 27 | Sync separation slice level adjustment (DC) |

| 28 | Sync separation output UNUSED |

Fig. 3-11. Description of Terminals

Fig. 3-12. Component Waveforms

Fig. 3-13. (b) Effect of Decoder Y LPF

Fig. 3-13. (c) Chroma BPF 3.58 MHz ±0.5 MHz

Fig. 3-13. (d) Effect of Decoder BPF

Fig. 3-13. (e) Chroma LPF 1.3 MHz (NTSC)

Fig. 3-13. (f) Effect of Decoder C LPF

3-1-4. Encoder Circuit (VD1)

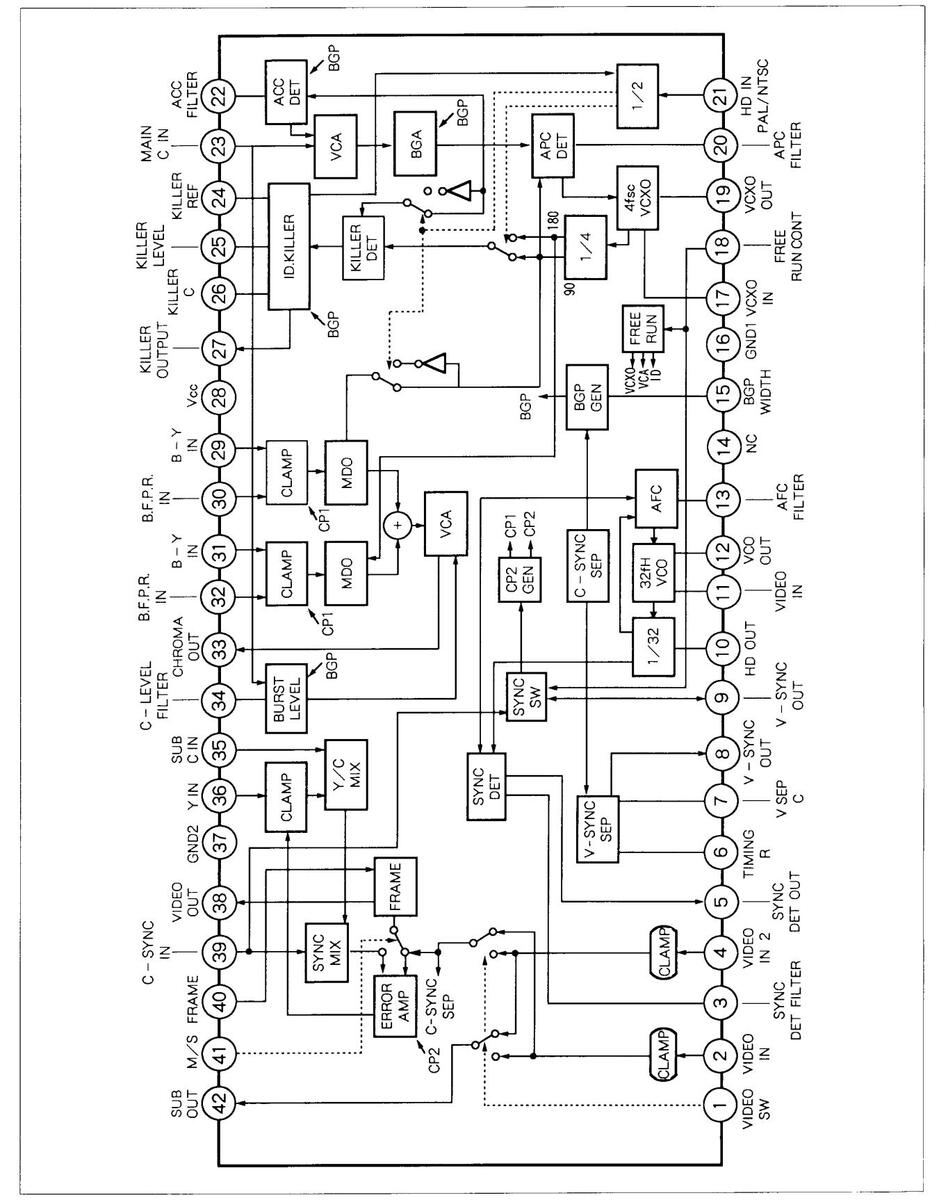

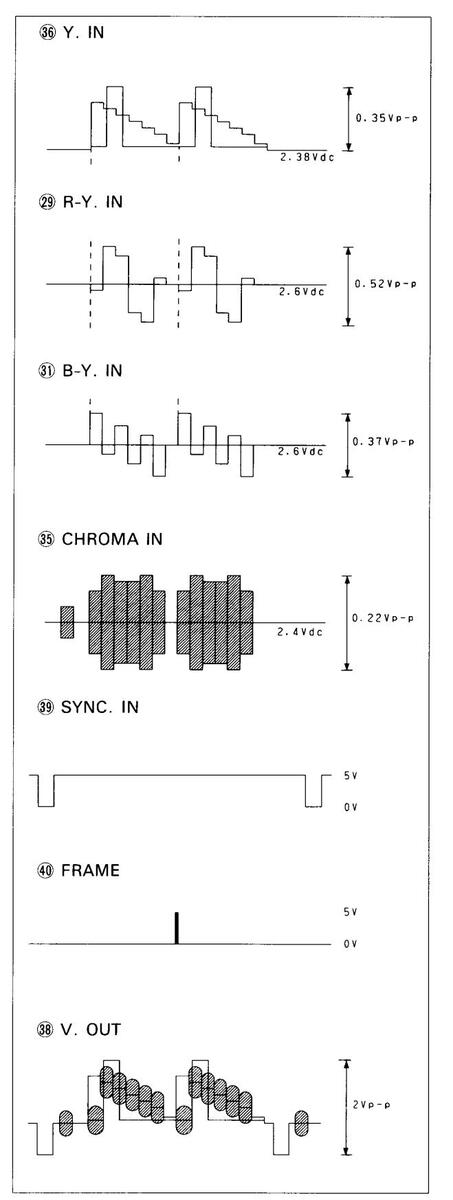

The circuit diagram, IC block diagram, terminal explanation, key signal waveforms, and filter characteristics of the encoder are shown in figures 3-14, 3-15, 3-16, 3-17, and 3-18.

«Signal Flow »

The flow of signals in the encoder are divided into the Y and C2 systems and explained below.

The paths of Y, R-Y, and B-Y, after being converted to analog signals by the immediately previous D A, are described below.

- 1 The intensity system Y signal is digitized by the equalizer and the LPF, its noise is removed, its level is adjusted using the volume, and it enters pin 36 via a coupling capacitor.

- (2) Coloration signals R-Y and B-Y are digitized by the LPF, their noise is removed, and they enter pins 29 and 31 via coupling capacitors. The signals are clamped by the pulse which regulated the horizontal sync signal input to pin 39. Fsc signals of 90 and 180 degrees are created from the free-running 4Fsc and, by AM modulating and adding these signals, an orthogonal-balance modulated chroma signal is obtained. The burst signal is then added to this, and the resulting signal is amplified, output from pin 33. It flows through the BPF, its harmonics are removed, and it is input into pin 35.

Meanwhile, the Y signal enters pin 36, its pedestal is clamped, and it is Y/C mixed. Then the C-SYNC signal which entered pin 39 is added, a center frame based on the FRAME signal from pin 40 is added, and the resulting signal is output to pin 38. From there, it passes through a buffer and is output to the OSD.

3 Meanwhile, the switcher output picture signal input into pin 2 is separated into horizontal sync and vertical sync by the sync separation circuit, and output from pin 5 and pin 8 to OSD 1.

The AFC circuit and the ACC circuit are not utilized in this configuration.

«Y-C Time Difference

Since this color quad compressor operates in component form, it requires a signal separation filter, so time reconciliation of the intensity signal and the chroma signal must be performed. Delay times are adjusted as shown below.

| Dec | oder | Digital | Enc | (Units : | |||

|---|---|---|---|---|---|---|---|

| BPF | LPF | GΑ | LPF | BPF | Total | ||

|

Chroma

signal |

350 260 | О | 260 | 350 | 1220 | ||

|

Intensity

signal |

_ | 210 | 800 | 210 | _ | 1220 | |

Fig. 3-14. Encoder Circuit Diagram

Fig. 3-15. Block Diagram

| 1 Video switch control | |||||||

| 2 Video input 1 | |||||||

| 3 Sync separation filter | |||||||

| 4 Video input 2 | Video input 2 | ||||||

| 5 Sync separation output | Sync separation output | ||||||

| 6 Timing filter | |||||||

| 7 Vertical sync separation capacitor | |||||||

| 8 Vertical sync output | |||||||

| 9 Composite sync signal output | |||||||

| 10 Horizontal sync output UNUSED | |||||||

| 11 VCO input UNUSED | |||||||

| 12 VCO output UNUSED | |||||||

| 13 AFC filter UNUSED | |||||||

| 14 NC | |||||||

| 15 Burst gate width UNUSED | |||||||

| 16 Ground 1 | |||||||

| 17 VCXO input | |||||||

| 18 Free-running control | |||||||

| 19 VCXO output | |||||||

| 20 APC filter UNUSED | |||||||

| 21 HD input NTSC PAL switch | HD input NTSC PAL switch | ||||||

| 22 ACC filter | |||||||

| 23 Main chroma input UNUSED | |||||||

| 24 Killer reference UNUSED | |||||||

| 25 Killer level UNUSED | |||||||

| 26 Killer capacitor UNUSED | |||||||

| 27 Killer output | |||||||

| 28 Power supply voltage | |||||||

| 29 R-Y input | |||||||

| 30 BFP R-Y input | |||||||

| 31 B-Y input | |||||||

| 32 BFP B-Y input | |||||||

| 33 Chroma output | |||||||

| 34 Chroma level filter | |||||||

| 35 Auxiliary chroma input | |||||||

| 36 Intensity input | |||||||

| 3/ Ground 2 | |||||||

| 38 D video output | |||||||

| 39 Composite sync signal input | |||||||

| 40 Frame insertion signal input | |||||||

| 41 Main auxiliary switch control | |||||||

| 42 Auxiliary video signal output | |||||||

Fig. 3-17. Signal Waveforms

Figure 3-18 (f) Effect of Chroma BPF

START 0. 0 MHz

Minim

₩

WHEN

SWP 30 ms

VBW 300 KH:

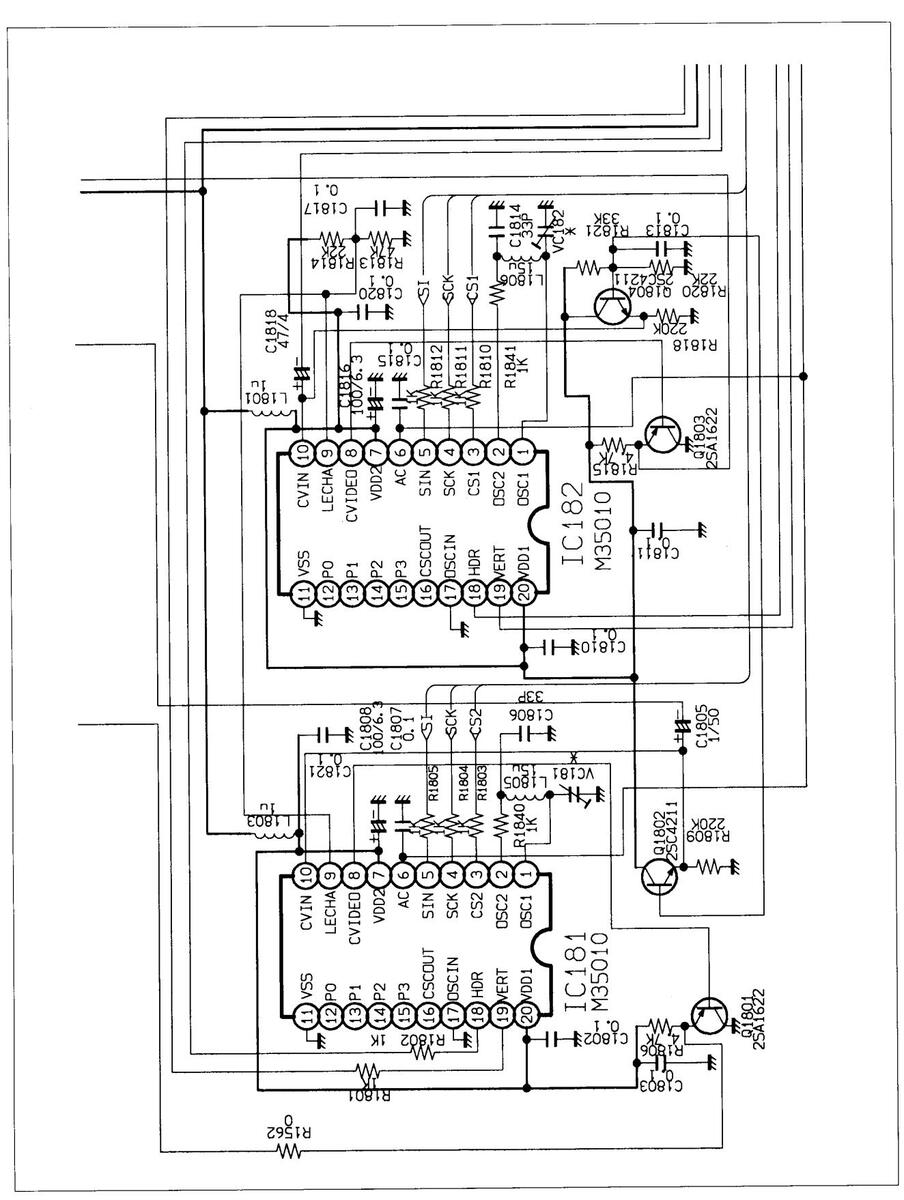

3-1-5 . On-screen Circuit (VD1)

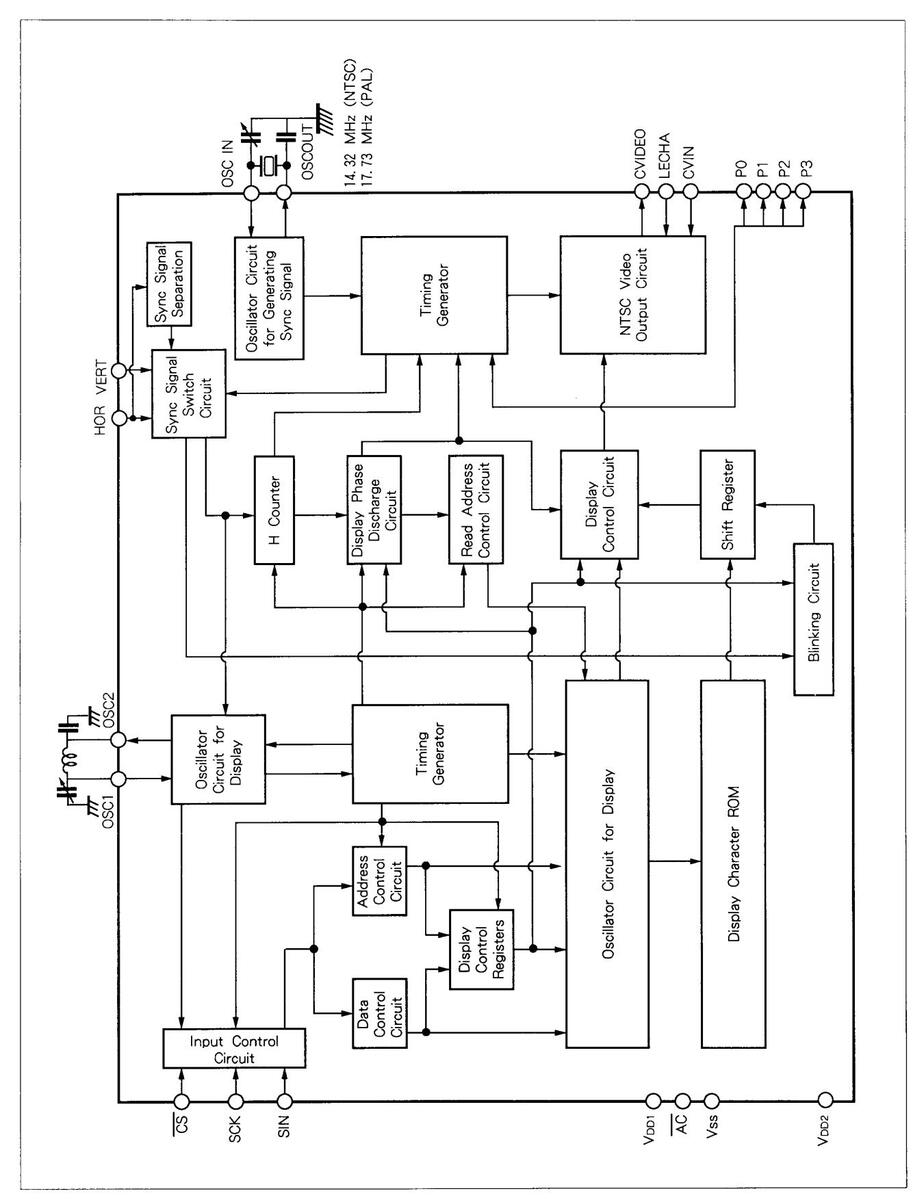

As shown in diagram 3-19, this set's on-screen circuit utilizes two OSD IC M35010SP components.

OSD 1 is the component which inserts characters into digitally processed picture signals which are output from the gate array, D/A, and encoder; i.e., characters on the quad screen. The sync signals for this on-screen circuit, VD OSD and HD OSD, are created in gate array 4. In order for this HD OSD signal to compress the characters inserted on the quad screen in the vertical direction, an extra sync is inserted before the horizontal sync, as shown in figure 3-20, thus incrementing the OSDIC vertical counter and cutting the number of dots in characters in the vertical direction by half. As a result, characters with a vertical height of 16 dots are reduced to 8 dots.

OSD 2 is the component which inserts characters into full screen signals. The sync signal from the camera signal entering via the switcher is separated by the encoder's sync separation circuit, and is then used as OSD 2's external sync signal. The camera signal entering via the switcher is 1 Vpp, so it is amplified to 2 Vpp by the 6 dB amplifier, characters are inserted into it by OSD 2, and it is output.

- OSD 1 and OSD 2 functional differentiation OSD 1 … Quad screen titles and menus OSD 2 … Full screen titles and menus

- 2. Block diagram

The block diagram for the on-screen IC is shown in figure 3-21. The oscillator circuit which generates sync signals is not utilized.

The whiteness level of the insertion characters can be changed via the LECHA DC level.

HOR and VOR are negative, and AC is reset directly via the reset IC. P0 through P3 are not utilized.

The size of characters in the horizontal direction decreases when the frequency of the display's oscillator increases, and increases when this frequency decreases.

3. Microcomputer interface

This OSD IC is controlled by 8-bit serial data (CS 1, CS 2, CLK, DATA) from a microcomputer. Functional differentiation of the chip selects (CS 1 and CS 2) is as follows.

- CS 1 ... OSD 1

- CS 2 ... OSD 2

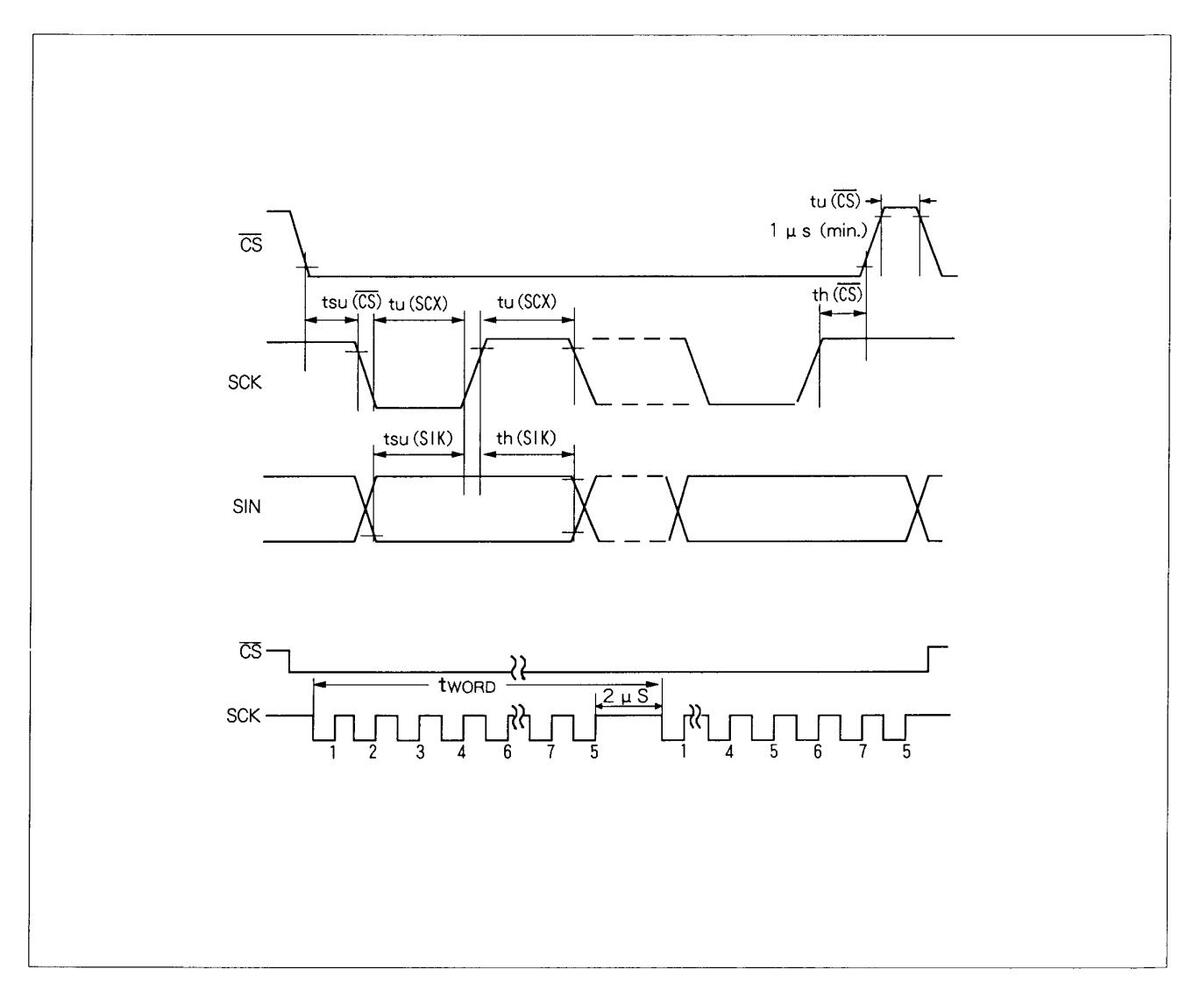

The timing of the serial data is shown in figures 3-22 and 3-23.

4. Character configuration

| Full Screen | Quad Screen | |

|---|---|---|

| Horizontal | 12 | 12 |

| Vertical | 18 | 9 (dots) |

5. Screen configuration

The screen is composed of 24 characters horizontally and 10 lines vertically, as shown in figure 3-24.

- 6. Memory configuration The configuration of the memory is as shown in figure 3-25.

- 7. Description of terminals

A description of the terminals is presented in table 3-1.

Fig. 3-19 On-Screen Circuit

Fig. 3-19. Block Diagram of Periphery of On-Screen Function

Fig. 3-20. HD Waveform for OSD IC

Fig. 3-21. Block Diagram (20 Pin)

Serial Data Input (Note: Timing conditions, when not specified, are Ta = -20 to + 70 °C, VDD = 5 ± 5.5 V)

| Course had a | Ratings | Linita | Natas | ||||

|---|---|---|---|---|---|---|---|

| Item | Symbols | Minimum | Standard | Maximum | Units | NOTES | |

| SCK width | t w (SCX) | 200 | _ | - | ns | ||

| CS set-up time | t su (CS) | 200 | _ | _ | ns | ||

| CS hold time | t h (CS) | 2 | - | μS | |||

| SIN set-up time | t su (SIN) | 200 | - | - | ns | ||

| SIN hold time | t n (SIN) | 200 | 200 — | ns | |||

| Single word write time | tword | 5 | - | _ | μs | ||

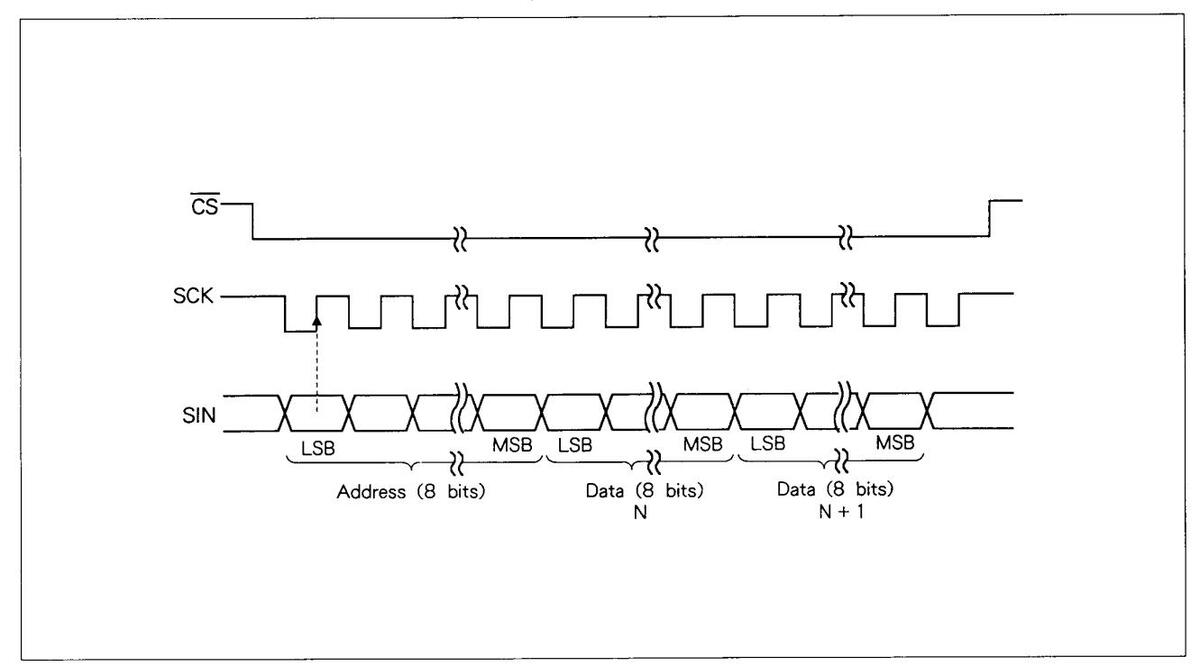

Fig. 3-22. Timing

Notes : (1) Addresses are comprised of 8 bits.

- (2) Data os cp, rosed pm 8 bits.

- (3) The 8 bits of SCK following the trailing edge of CS are taken to be the address, and this address is incremented for each 8 bits of input data thereafter.

Fig. 3-23. Timing

| - Line | ə 1 | 01 | 6 JC | quen | ||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 0 | Т | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | П | 12 | 13 | 14 | 15 | 16 | 17 | 8 | | 19 | 20 | 21 | 22 | 23 |

| 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | |

| 48 | 49 | 50 | 51 | 52 | 53 | 54 | 55 | 56 | 57 | 58 | 59 | 60 | 61 | 62 | 63 | 64 | 65 | 66 | 67 | 68 | 69 | 70 | 71 | |

| 72 | 73 | 74 | 75 | 76 | 77 | 78 | 79 | 80 | 81 | 82 | 83 | 84 | 85 | 86 | 87 | 88 | 89 | 90 | 91 | 92 | 93 | 94 | 95 | |

| 96 | 97 | 98 | 99 | 100 | 101 | 102 | 103 | 104 | 105 | 106 | |07 | 108 | 109 | 110 | ш | 112 | 113 | ||4 | 115 | 116 | 117 | 118 | 119 | |

| Lines 2 to 10 | 120 | 121 | 122 | 123 | 124 | 125 | 126 | 127 | 128 | 129 | 130 | |3| | 132 | 133 | 134 | 135 | 136 | 137 | 138 | 139 | 140 | |41 | 142 | |43 |

| 144 | 145 | |46 | |47 | 148 | 149 | 150 | 151 | 152 | 153 | 154 | 155 | |56 | 157 | 158 | 159 | 160 | 161 | 162 | 163 | 164 | 165 | 166 | 167 | |

| 168 | 169 | 170 | 171 | 172 | 173 | 174 | 175 | 176 | 177 | 178 | 179 | 180 | 181 | 182 | 183 | 184 | 185 | 186 | 187 | 188 | 189 | 190 | 191 | |

| 192 | 193 | 194 | 195 | 196 | 197 | 198 | 199 | 200 | 201 | 202 | 203 | 204 | 205 | 206 | 207 | 208 | 209 | 210 | 211 | 212 | 213 | 214 | 215 | |

| 216 | 217 | 218 | 219 | 220 | 221 | 222 | 223 | 224 | 225 | 226 | 227 | 228 | 229 | 230 | 231 | 232 | 233 | 234 | 235 | 236 | 237 | 238 | 239 |

Fig. 3-24. Screen Configuration

Description of Terminals

| Pin No. | Symbol | Terminal Name | Functional Description |

|---|---|---|---|

|

1

2 |

OSC 1

OSC 2 |

External oscillator circuit connection terminal |

External connection terminal for screen oscillator circuit.

Reference oscillator frequency is approximately 7 MHz. The horizontal display position and character width on the television screen are determined by this oscillator frequency. |

| 3 | CS | Chip select input |

Chip select terminal.

Put in 'L' state during serial data transfers. Hysteresis input. Includes pull-up resistor. |

| 4 | SCK | Serial clock input |

When the CS terminal is 'L', SIN serial data is retrieved on the leading edge of SCK.

Hysteresis input. Includes pull-up resistor. |

| 5 | SIN | Serial data input |

Display control registers, along with display data memory addresses

and data, are input serially. Hysteresis input. Includes pull-up resistor. |

| 6 | AC | Auto clear input |

In the 'L' state, resets the IC's internal circuits.

Hysteresis input. Includes pull-up resistor. |

| 7 | V DD2 | Power supply terminal | Analog-type power supply terminal. Connect to +5 V. |

| 8 | C VIDEO |

Composite video signal

output |

Terminal for output of the composite video signal.

Outputs a 2 Vpp composite video signal. When superimposing, characters are overlaid onto the composite video signal which is input from the CVIN terminal. |

| 9 | LECHA | Character level input |

Input terminal which determines the level of output characters within the composite video signal.

Character color is white. |

| 10 | CVIN | Video input |

Input terminal for external composite video signal.

When superimposing, characters are overlaid onto this external composite video signal. |

| 11 | Vss | Ground terminal | Terminal for grounding. Connect to GND. |

| 12 | PO | Port 0 output | Outputs port terminal output or character background signal (BLNK 1*). Polarity can be selected when the font ROM is specified. |

| 13 | P1 | Port 1 output |

Outputs port terminal output or character signal (CO 1*).

Polarity can be selected when the font ROM is specified. |

| 14 | P2 | Port 2 output | Outputs port terminal output or character background signal (BLNK 2*). Polarity can be selected when the font ROM is specified. |

| 15 | Р3 | Port 3 output | Outputs port terminal output or character background signal (CO 2*). Polarity can be selected when the font ROM is specified. |

|

16

17 |

OSC OUT

OSC IN |

Oscillator circuit for

sync signal |

Terminal for connection of external oscillator circuit for sync signal.

Oscillation frequency utilized is 14.32 MHz for NTSC format and 17.73 MHz for PAL format. |

| 18 | HOR* |

Horizontal sync signal

input |

Inputs the horizontal sync signal. Hysteresis input.

Polarity can be selected when the font ROM is specified. |

| 19 | VERT* | Vertical sync signal input |

Inputs the vertical sync signal. Hysteresis input.

Polarity can be selected when the font ROM is specified. |

| 20 | V DD1 | Power supply terminal | Digital-type power supply terminal. Connect to +5 V. |

Table 3-1. Description of Terminals

Memory Configuration

| DA | DA | DA | DA | DA | DA | DA | DA | Damanlar | |

|---|---|---|---|---|---|---|---|---|---|

| 7 | 6 | 5 | 4 | 3 | 2 | I | 0 | Remarks | |

| 0 | EXP | C 6 | C 5 | C4 | C 3 | C 2 | C1 | Co | |

|

Expansion

Bit |

Display RAM | ||||||||

| 239 | EXP | C 6 | C 5 | C4 | C 3 | C 2 | C1 | Co | |

| 240 | PTD | PTD | PTD | PTD | PTC | PTC | PTC | PTC | Port output |

| 3 | 2 | I | 0 | 3 | 2 | I | 0 | setting | |

| 241 | TBASE | TBASE | HP | HP | HP | HP | HP | HP | Horizontal display |

| I | 0 | 5 | 4 | 3 | 2 | I | 0 | position setting | |

| 242 | INT | SEPV | VP | VP | VP | VP | VP | VP | Vertical display |

| NON | 5 | 4 | 3 | 2 | I | 0 | position setting | ||

| 243 | VSZ | VSZ | VSZ | VSZ | HSZ | HSZ | HSZ | HSZ | Character size |

| 21 | 20 | 11 | 10 | 21 | 20 | 11 | 10 | setting | |

| 244 | DSP | DSP | DSP | DSP | DSP | DSP | DSP | DSP | Display format |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | setting | |

| 245 | N | TEST | TEST | TEST | EXP | EXP | DSP | DSP | Expansion display |

| P | 2 | Ι | 0 | 1 | 0 | 9 | 8 | setting | |

| 246 | EQP | PAL | PAL | ALL | FSC | BLINK | BLINK | BLINK | Blinking setting |

| н | 25 | 24 | 2 | I | 0 | ||||

| 247 | BLKHF | BB | BG | BR | LEVEL | PHASE | PHASE | PHASE | Raster color |

| 3 | 2 | ł | 0 | setting | |||||

| 248 | OSP | CONT | STOP | STOP | RAM | EX | BLK | BLK | Control display |

| ON | 7 F | I | IN | ERS | I | 0 |

*Upon resetting via the AC terminal, display control registers are all set to "0".

Fig. 3-25. Memory Configuration

3-2 Control Circuits

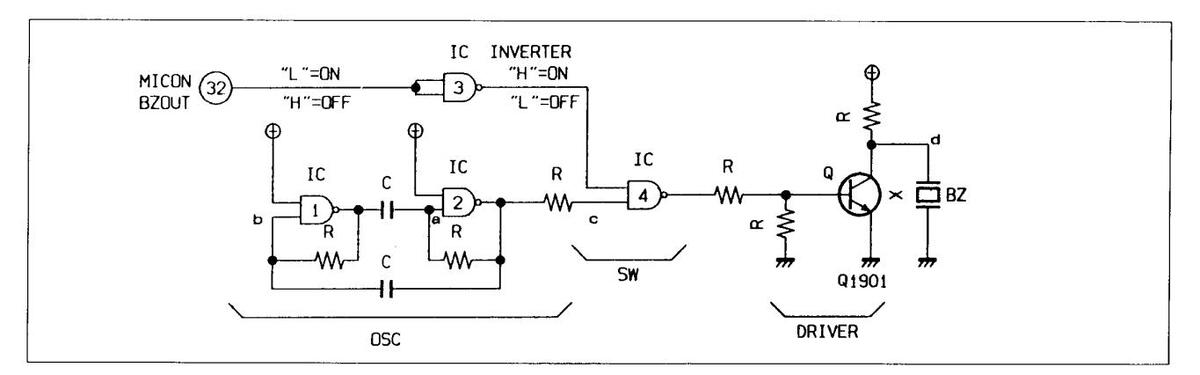

3-2-1. Buzzer Circuit (VD1)

This buzzer circuit, which utilizes as an oscillator a floating-gate-type astable multivibrator employing a CMOS NAND circuit, drives a buzzer by adding the oscillator signal to it in response to an ON signal from the microcomputer. The circuit diagram and its various waveforms are shown in figures 3-26 and 3-27. The period of the waveforms in this circuit is T = 1.38CB = 0.19 msec.

but in actuality it is approximately 0.25 msec.

When the buzzer is not being used voltage is not applied to it, and transistor 01901 is turned on (If direct voltage is continuously applied to the buzzer the possibility exists that niezoelectric elements will polarize.)

In order that the buzzer does not go on when microcomputer output is reset (when power is turned on), even if a high level is output to NAND3, this is

made a low-active output which is inverted so that the output to SW (NAND4) is high-active

As shown in the table, when IN 1 is low, the output of NAND4 is normally high and 01901 is turned on When IN 1 is low, the input to IN 2 is inverted and output. This means that 01901 is turned off and voltage is applied to the buzzer only when IN 1 and IN 2 are both high. This IN 2 input signal goes on and off every 0.125 msec. Accordingly, a frequency of approximately 4KHz is imparted on the buzzer, and the buzzer sounds

| SW ( | NAND4) | Operation |

|---|

| (NAND 3 OUT) | (OSC OUT) | OUT | BZIN |

|---|---|---|---|

| L | L | н | L |

| L | Н | Н | L |

| Н | L | Н | L |

| н | н | L | Н |

Fig. 3-26. Buzzer Circuit Diagram

Fig. 3-27. Buzzer Waveform Diagram

3-2-2. Reset Circuit (VD1)

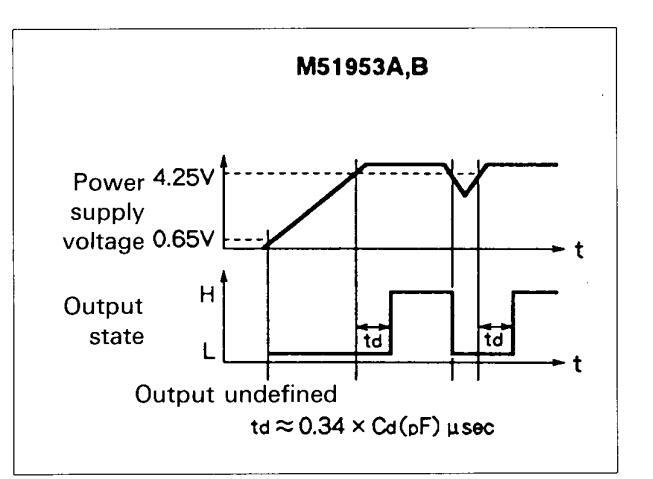

The reset circuit for the microcomputer and the on-screen IC is implemented using an M51953A resetting IC. Its external appearance, block diagram, and operating waveform diagram are shown in figures 3-28, 3-29, and 3-30. The detection voltage for this IC is : minimum 4.05 V, standard 4.25 V, maximum 4.45 V.

《Principles of Operation》

The reference voltage (1.25 V) and the value of VDD when voltage-divided by R 1 and R 2 are compared by the hysteresis comparator and reverse-output by the output comparator. By turning off a transistor which was on, the delay capacity starts to charge to 5µA, so the voltage traces up the charging curve.

This voltage and the internal reference voltage are compared and reverse-output by the subsequent hysteresis comparator, which, by turning on the subsequent transistor, causes a low reset pulse to be output.

Fig. 3-28. External Appearance Diagram

Fig. 3-29. Block Diagram

Fig. 3-30. Operating Waveform Diagram

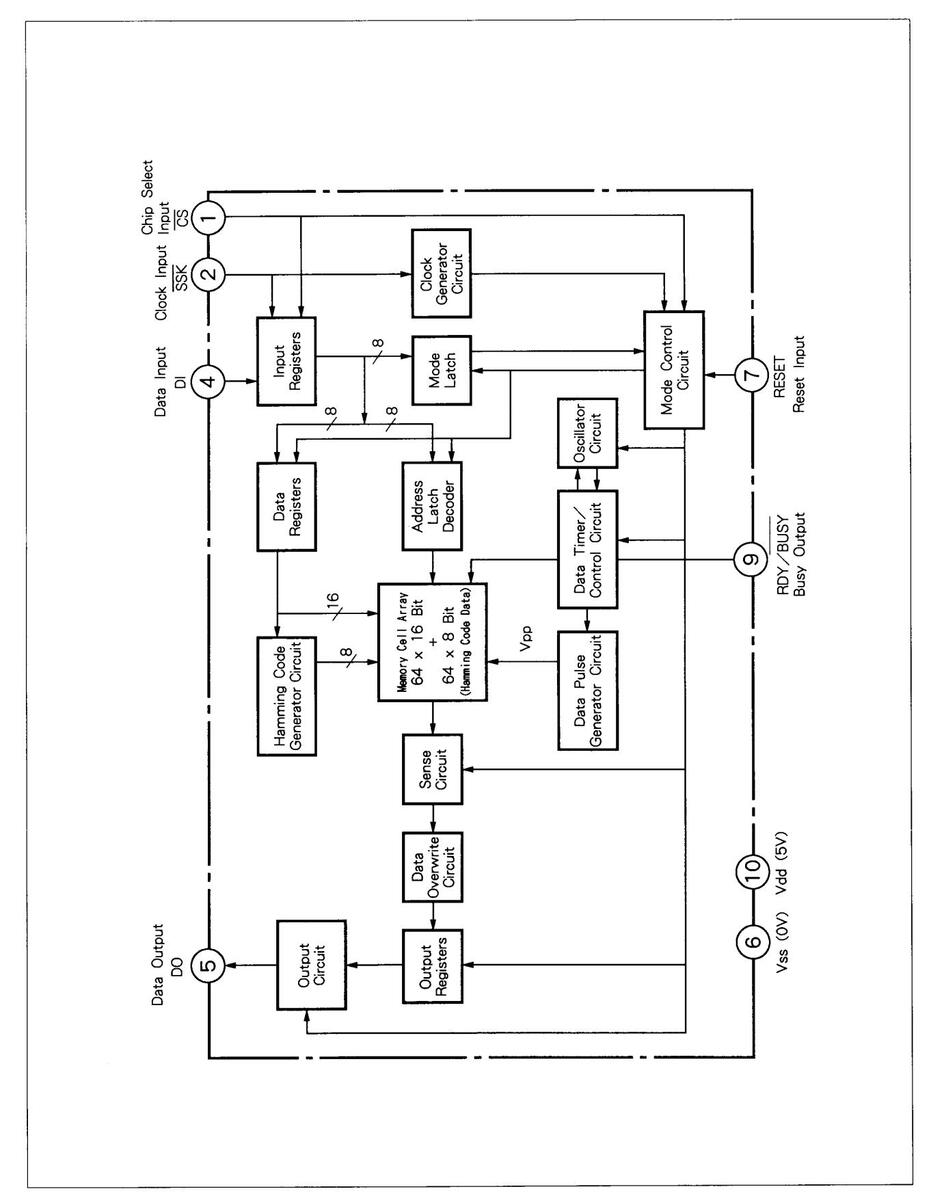

3-2-3. EEPROM Circuit (VD1)

This memory utilizes the M6M80011AFP. The specifications for this IC are as follows. Appearance : 10-pin plastic-mold SOP IC Type : 1024-bit non-volatile memory Overwrites : 105 Data retention : 10 years A terminal description (table 3-2), block diagram (fig. 3-31.), and memory map are presented below.

(MEMORY MAP)

| 00~03 | CAMERA 1 TITLE |

|---|---|

| 04~07 | CAMERA 2 TITLE |

| 08~0B | CAMERA 3 TITLE |

| 0C~0F | CAMERA 4 TITLE |

| 10~13 | CAMERA 5 TITLE |

| 14~17 | CAMERA 6 TITLE |

| 18~1B | CAMERA 7 TITLE |

| 1C~1F | CAMERA 8 TITLE | |

|---|---|---|

| 20~21 | SEQUENTIAL SW TIME | |

| 22~23 | ZOOM POSITION | |

| 24~27 | SENSOR HORIZONTAL POSITION | |

| 28~2B | SENSOR VERTICAL POSITION | |

| 2C~2D | SENSOR LEVEL | |

| 2E | SENSOR DISPLAY BIT 4 BIT A SCREEN | |

| SENSOR DISPLAY BIT 4 BIT B SCREEN | ||

| SENSOR ON/OFF BIT 8 BIT | ||

| 2F | QUAD MODE ON A 4 BIT | |

| QUAD MODE ON B 4 BIT | ||

| ALARM MENU DATA 4 BIT | ||

| QUAD SW TIME 4 BIT | ||

| 30 | MODE 4 BIT | |

| QUAD VERTICAL POSITION | ||

| 31~3E | NO USE | |

| 3F | MEMORY OVERWRITE COMPLETION CODE | |

| ł |

Description of Terminals

| Terminal Name | Symbol | Functions |

|---|---|---|

| Chip Select Input | CS |

|

| Clock Input | SCK |

|

| Data Input | DI | • Data input is performed from this terminal. |

| Data Output | DO |

|

| Reset Input | RESET |

|

| Busy Output |

RDY/

BUSY |

|

Fig. 3-2. Description of Terminals

Fig. 3-31. Block Diagram

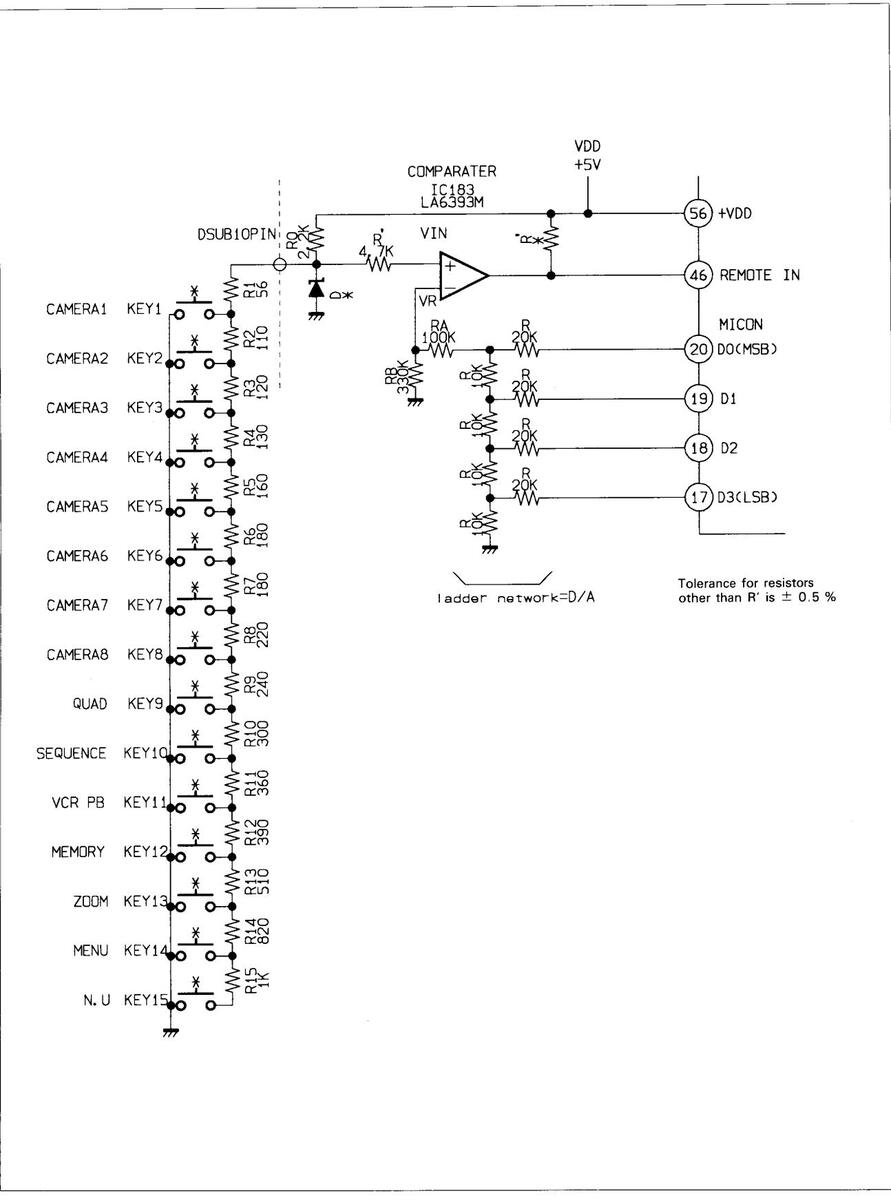

3-2-4. Remote Control Circuit (VD1)

This remote control circuit is a dual-line wired remote control of the voltage comparison variety. The circuit diagram is as shown in figure 3-33, and its various waveforms are shown in figure 3-34.

The principles of operation for this circuit are as follows. The voltage produced by the comparator is voltage-divided by the unit's resistance R0 and the external encoder resistance

The resulting voltage is compared with reference voltage Vr, which is the 4-bit up-counter output in the microcomputer after being digital/ analog-converted by an R-2R ladder network. Based on this comparison, microcomputer output bits at points of comparator output variation are determined to be encoder input, and are subsequently decoded. Normally, in this circuit, when there is no input, 4.2 V DC is output, data output from the microcomputer is periodically counted up, and input is continually compared via the comparator.

When there is a key input, the comparator produces a corresponding voltage Vin, which is compared with reference voltage Vr, and REMOTE IN goes low upon detection of the variation point. When this occurs the data is latched, and if it matches two times then it is taken to be an input.

With the remote control operation component (encoder), if the SWn key is pressed, the comparator in-phase input Vin is indicated as :

Vin = RSUM * VDD/(RSUM + R0).

When power supply voltage VDD is 5 V, this Vin's reference voltage Vr (comparator in-phase input voltage) must be made smaller than its maximum value of VDD - 1.5 V = 3.5 V. Thus, the voltage range achieved by voltage-dividing via R0 and the encoder resistance is :

0 < Vin < 3.5 V

Consequently, comparator reference voltage Vr must also be within this range.

Normally, the voltage at point R is 15 * VDD/16, and since this exceeds the above range, it must be voltage-divided by RA and RB. For RA and RB, resistors with a tolerance of 0.5 % are used. In addition, encoder resistance Ri is selected to realize a potential of between Vri and Vri + 1.

Input Voltage and Reference Voltage Vr for Keys

| KEY ON | Vin |

Reference

Voltage Vr |

D 0 | D1 | D 2 | D 3 |

|---|---|---|---|---|---|---|

| 1 | 0.124 | 0.000 | L | L | L | L |

| 2 | 0.350 | 0.232 | L | L | L | Н |

| 3 | 0.575 | 0.462 | L | L | н | L |

| 4 | 0.795 | 0.694 | L | L | н | н |

| 5 | 1.036 | 0.918 | L | Н | L | L |

| 6 | 1.280 | 1.150 | L | Н | L | Н |

| 7 | 1.493 | 1.380 | L | Н | Н | L |

| 8 | 1.719 | 1.613 | L | Н | Н | Н |

| 9 | 1.940 | 1.827 | н | L | L | L |

| 10 | 2.173 | 2.059 | н | L | L | н |

| 11 | 2.410 | 2.290 | н | L | Н | L |

| 12 | 2.622 | 2.523 | н | L | Н | н |

| 13 | 2.846 | 2.748 | н | Н | L | L |

| 14 | 3.109 | 2.981 | н | Н | L | н |

| 15 | 3.328 | 3.213 | Н | Н | Н | L |

| 3.446 | н | Н | Н | Н | ||

| OPEN | 4.12(V) | (V) |

Since resistors used for resistances R0-15 here have tolerances of ± 0.5%, a discrepancy of approximately 1% is possible for Vin and Vr above. However, since there is no area of overlap between respective Vin and Vr values, they can be adequately identified. In addition, when the remote control cable is long and its impedance is consequently high, adjust R 1 such that the combined resistance of R 1 and the circuit line is 56 Q .

Fig. 3-33. Remote Control Circuit Diagram

Fig. 3-34. Remote Control Waveform Diagram

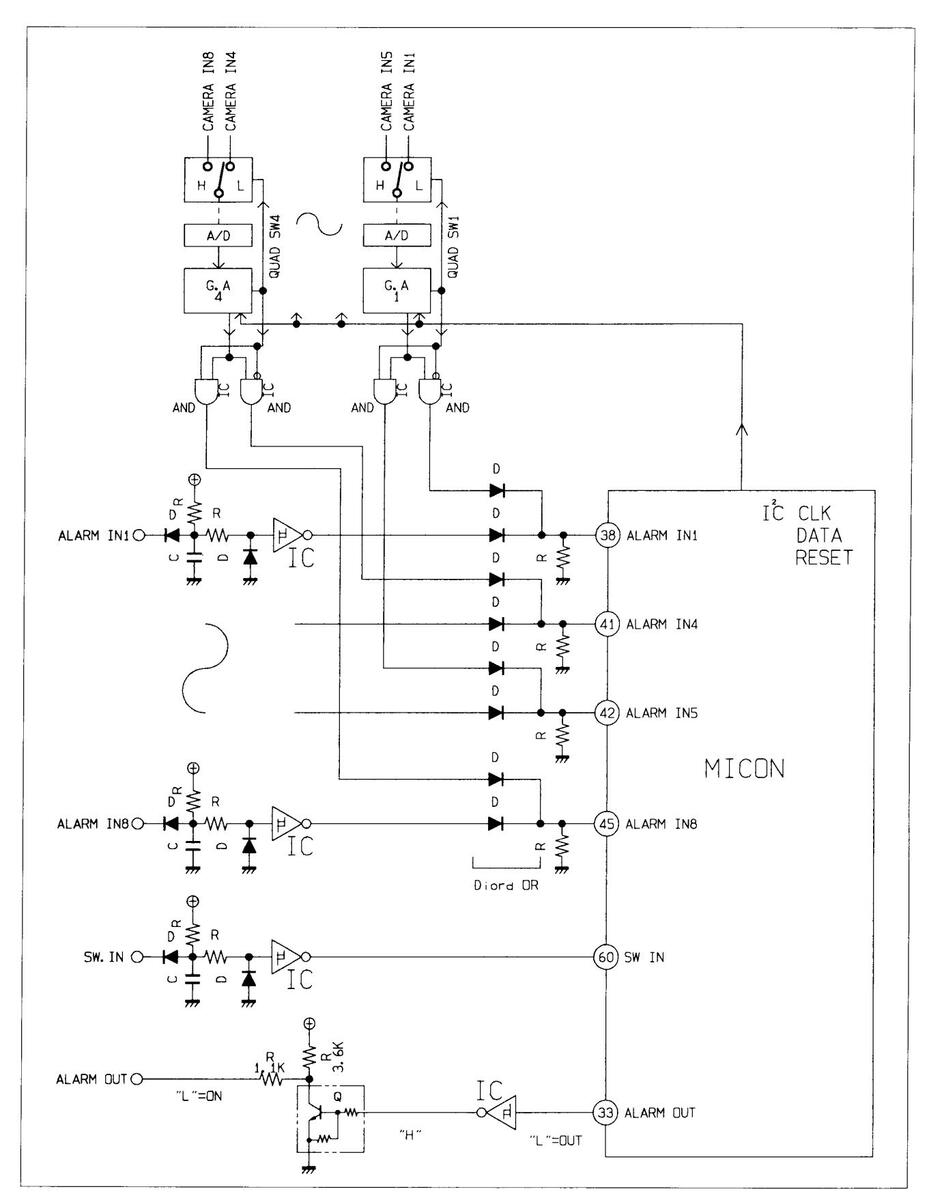

3-2-5. Interface Circuit (VD1)

The microcomputer interface circuit is as shown in figure 3-35.

The breakdown is :

| Alarm Input Circuit | ••• | External input : No-voltage contacts 8 |

|---|---|---|

| Internal input : Picture sensor inputs 4 | ||

| (minimum output period for | ||

| high output upon detection : 1 | ||

| field) | ||

| Switch Input Circuit | External input : No-voltage contacts 1 | |

| Alarm Output Circuit | ••• | Low output during alarms |

| Output INP 5.7 K Q (5 V) | ||

| 1.0 KΩ (0 V) |

(1) Alarm Input Circuit

For external input, a no-voltage contact is provided for each camera. When there is a low input, it is inverted to high by an inverter, passes through a diode, and enters the corresponding input port of the microcomputer. To prevent chattering on this inverted signal, a Schmidt trigger inverter is utilized. At the point of input, the two diodes are for static protection, and the capacitor is for noise cutting.

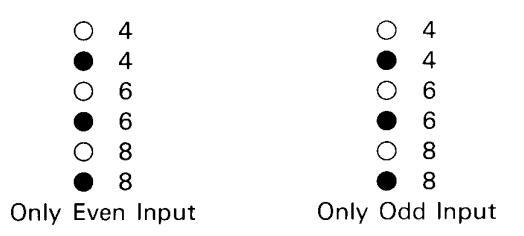

There is one internal picture sensor output for each gate array, so when using QUAD A/B mode, it is not possible to determine whether output is from cameras 1 to 4 or cameras 5 to 8. Consequently, using AND circuits, a separator divides the 4 inputs into 8 outputs. That is, using two-input one-output AND gates as shown in the truth table below, if IN 1 is high then IN 2 is output as is, and if IN 1 is low then output is low, so this effectively functions as a switch operating as an IN 1 control terminal. From a gate array, if a QUADSW input switching signal is low, cameras 1 to 4 are input, so IN 1 of AND 1 goes high, so output from AND 1 becomes active and is input to the supporting microcomputer.

| IN 1 | IN 2 | Ουτ |

|---|---|---|

| L | L | L |

| L | К | L |

| н | L | L |

| н | Н | Н |

Alarm signals from a gate array are divided from four signals to eight to realize a one-to-one correspondence with the camera signals. Subsequently, the eight internal alarm signals and the direct external alarm signals are ORed together with diodes and input to the microcomputer's respective alarm input ports. Microcomputer input is active high.

|

G.A

Output |

t |

Quad Screen

Input |

Sensor

Output |

Separator

(Microcomputer Input) |

|---|---|---|---|---|

| QUAD | L | 1 | Н | 1 |

| SW 1 | Н | 5 | 5 | |

| QUAD | L | 2 | Н | 2 |

| SW 2 | н | 6 | 6 | |

| QUAD | L | 3 | Н | 3 |

| SW 3 | н | 7 | 7 | |

| QUAD | L | 4 | Н | 4 |

| SW 4 | Н | 8 | 8 |

(2) Switching Signal Input Circuit

This switching signal circuit accepts control signals from time-lapse VTRs and the like which regulate the switch timing of sequential signals. The minimum width for switching input is one vertical interval, and switching control is performed on the falling edge of the input signal.

(3) Alarm Output Circuit

When there is an alarm input (both internal and external), during the alarm period (set by the microcomputer), an alarm out signal is output from pin 33 of the microcomputer. Microcomputer output is active low, so that alarms are not output during set start-up.

When there is a low output from the microcomputer, it is inverted to high by an inverter, and a low output is then performed by a transistor.

Fig. 3-35. I/O Circuit

3-2-6. System Control Circuit (VD1) «Overview»

This system controller is comprised of a single 64-pin QIP, 4-bit/chip LC66516B microcomputer with a clock frequency of 4 MHz.

Overview of Processing Functions

- Sequential switcher control

- Video output control

- Buzzer on/off control

- Remote control input decoding

- Key input control

• LED display control

- On-screen control

- EEPROM control

- Gate array control

- Switch input retrieval

- Alarm signal retrieval and output

- Signal presence/absence determination

A pin configuration diagram and a terminal description are presented in figure 3-36 and table 3-3.

《Description of Functions》

1. Sequential switcher control

This function creates and outputs a switch change-over signal which changes the input signals from among cameras 1 to 8 in accordance with the specified time and outputs them to VIDEO OUT.

Output Terminals

| Pin 21 : Seq. switch C0 (MSB) | L | L | L | L | Н | Н | Н | н | |

|---|---|---|---|---|---|---|---|---|---|

| Pin 27 : Seq. switch C1 | L | L | н | Н | L | L | Н | Н | |

| Pin 28 : Seq. switch C2 (LSB) | L | н | L | Н | L | Н | L | н | |

| Output is switched based on these 3 bits | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | CAMERA |

2. Video output control

This function creates and outputs a signal which controls the two outputs VIDEO OUT and QUAD ONLY OUT (see switch circuit).

Output Terminals

| VIDEO OUT | Sequential and full screen | Quad screen | VCR IN screen | VCR IN screen |

| QUAD OUT | Quad screen | Quad screen | VCR IN screen | VCR IN screen |

3. Buzzer on/off control (see buzzer circuit)

Pin 32 BZ "H" : Sound buzzer

"L" : Stop buzzer

4. Remote control input decoding

Compares the external remote control voltage with the voltage obtained by D/A conversion of count-up signals REMOTE 0-3. When the external voltage is exceeded, the REMOTE IN signal present at that time is taken as the 4-bit output to decode (see remote control circuit).

| Pin 17 REMOTE 0 (LSB) | Output |

|---|---|

| Pin 18 REMOTE 1 | Output |

| Pin 19 REMOTE 2 | Output |

| Pin 20 REMOTE 3 (MSB) | Output |

| Pin 46 REMOTE IN | Input |

5. Key input and LED display control

Mode retrieval from the front switches, and LED control. Retrieves key input status via the key matrix, and carries out dynamic pulse lighting of the LEDs via the diode matrix (see key input and LED display circuit).

- Pin 13 DIG 0 Pulse output

- Pin 14 DIG 1 Pulse output

- Pin 15 DIG 2 Pulse output

- Pin 16 DIG 3 Pulse output

- Pin 1 KEYIN 1 Key input 1

- Pin 2 KEYIN 2 Key input 2

- Pin 3 KEYIN 3 Key input 3

- Pin 4 KEYIN 4 Key input 4

- Pin 5 SEG 1 Pulse output for LED lighting

- Pin 6 SEG 2 Pulse output for LED lighting

- Pin 7 SEG 3 Pulse output for LED lighting

- Pin 8 SEG 4 Pulse output for LED lighting

6. On-screen and EEPROM control

Controls the two on-screen systems and the EEPROMs (see on-screen and EEPROM circuits).

| Pin 48 | CS 0 | Chip select for EEPROMs |

| Pin 49 | CS 1 | Chip select for on-screen ? |

| Pin 50 | CS 2 | Chip select for on-screen 2 |

| Pin 51 | CS 3 | 3 |

| Pin 9 | S. 1 | Serial input data |

| Pin 10 | S. 0 | Serial input data |

| Pin 11 | S CLK | Serial clock |

7. Gate array control and signal presence/absence determination

Carries out gate array control via l2C. A timing diagram for these signals is shown in figure 3-37, and a command list is presented in table 3-4.

Pin 57 I2C DATA IN : I2C DATA input Pin 58 I2C DATA OUT : I2C DATA output Pin 59 I2C CLK OUT : I2C clock Pin 62 I2C RESET : I2C reset Pin 53 S/N 1 : Gate array 1 signal presence/absence signal "H" : signal present Pin 53 S/N 2 : Gate array 2 signal presence/absence signal "H" : signal present Pin 54 S/N 3 : Gate array 3 signal presence/absence signal "H" : signal present Pin 55 S/N 4 : Gate array 4 signal presence/absence signal "H" : signal present

8. Switch signal and alarm signal retrieval, and alarm output

| Pin 38 | ALARM IN 1 | : Alarm signal retrieval "H" : signal present Re | cognized as camera 1 alarm |

|---|---|---|---|

| Pin 39 | ALARM IN 2 | : Alarm signal retrieval "H" : signal present Re | cognized as camera 2 alarm |

| Pin 40 | ALARM IN 3 | : Alarm signal retrieval "H" : signal present Re | cognized as camera 3 alarm |

| Pin 41 | ALARM IN 4 | : Alarm signal retrieval "H" : signal present Re | cognized as camera 4 alarm |

| Pin 42 | ALARM IN 5 | : Alarm signal retrieval "H" : signal present Re | cognized as camera 5 alarm |

| Pin 43 | ALARM IN 6 | : Alarm signal retrieval "H" : signal present Re | cognized as camera 6 alarm |

| Pin 44 | ALARM IN 7 | : Alarm signal retrieval "H" : signal present Re | cognized as camera 7 alarm |

| Pin 45 | ALARM IN 8 | : Alarm signal retrieval "H" : signal present Re | cognized as camera 8 alarm |

| Pin 33 | ALARM OUT | : Outputs "L" during alarm period | |

| Pin 60 | SW IN | : External switcher change-over signal Detects | rising and falling edges t |

determine the presence or absence of a signal.

Performs switcher change-over on either

a rising or a falling edge.

Fig. 3-36. Pin Configuration Diagram

LC665 * * Pin Configuration (1)

| Pin No. | Terminal Name | 1/0 | Output Type | Signal Name | Remarks |

| 57 | SI0/P20 | 1/0 | CMOS | I 2 C DATA | 0D |

| 58 | S00/P21 | 1/0 | CMOS | I 2 C DATA | 0D |

| 59 | SCK0/P22 | 1/0 | CMOS | I 2 C CLK | |

| 60 | INTO/P23 | I/0 | CMOS | SW IN | |

| 61 | INT1/P30 | 1/0 | CMOS | VD IN | |

| 62 | POUT0/P31 | I/0 | CMOS | I 2 C RESET | |

| 63 | POUT1/P32 | I/0 | CMOS | SET UP 1 | |

| 64 | HOLD/P33 | 1 | |||

| 1 | P40 | I/0 | MOS | KEY IN 1 | |

| 2 | P41 | I/0 | MOS | KEY IN12 | |

| 3 | P42 | 1/0 | MOS | KEY IN3 | |

| 4 | P43 | I/0 | MOS | KEY IN4 | |

| 5 | P50 | 1/0 | MOS | SEG1 | |

| 6 | P51 | 1/0 | MOS | SEG2 | |

| 7 | P52 | 1/0 | MOS | SEG3 | |

| 8 | P53 | 1/0 | MOS | SEG4 | |

| 9 | SI1/P60 | 1/0 | CMOS | S.I/0 | 0D |

| 10 | SO1/P61 | 1/0 | CMOS | S.I/0 | OD |

| 11 | SCK1/P62 | 1/0 | CMOS | S.CLK | |

| 12 | PIN1/P63 | 1/0 | CMOS | ||

| 13 | P70 | 0 | MOS | DIG 0 | |

| 14 | P71 | 0 | MOS | DIG 1 | |

| 15 | P72 | 0 | MOS | DIG 2 | |

| 16 | P73 | 0 | MOS | DIG3 | |

| 17 | P80 | 0 | CMOS | REMOTEO | |

| 18 | P81 | 0 | CMOS | REMOTE1 | |

| 19 | P82 | 0 | CMOS | REMOTE2 | |

| 20 | P83 | 0 | CMOS | REMOTE3 | |

| 21 | INT2/P90 | 1/0 | CMOS | S.SW CO | |

| 22 | TEST | 1 | |||

| 23 | VSS | I | |||

| 24 | OSC1 | Ι | |||

| 25 | OSC2 | 1 | |||

| 26 | RES | 1 | |||

| 27 | INT3/P91 | 1/0 | CMOS | S.SW C1 | |

| 28 | INT4/P92 | 1/0 | CMOS | S.SW C2 | |

| 29 | INT5/P93 | I/0 | CMOS | ZOOM | |

| 30 | PAO | 0 | MOS | OUT CONT O | (LOOP) |

| 31 | PA1 | 0 | MOS | OUT CONT 1 | (QUAD) |

| 32 | PA2 | 0 | MOS | BUZZER | |

| 33 | PA3 | 0 | MOS | ALARM OUT | |

| 34 | PBO | 0 | MOS | QUAD SW 1 | |

| 35 | PB1 | 0 | MOS | QUAD SW 2 | |

| 36 | PB2 | 0 | MOS | QUAD SW 3 | |

| 37 | PB3 | 0 | MOS | QUAD SW 4 | |

| 38 | PCO | 1/0 | CMOS | ALARM IN 1 | |

| 39 | PC1 | 1/0 | CMOS | ALARM IN 2 | |

| , |

Table. 3-3 Description of Terminals (1)

| Pin No. | Terminal Name | I/0 | Output Type | Signal Name | Remarks |

| 40 | VREF0/PC2 | I/0 | CMOS | ALARM IN 3 | |

| 41 | VREF1/PC3 | I/0 | CMOS | ALARM IN 4 | |

| 42 | CMP0/PD0 | I | ALARM IN 5 | ||

| 43 | CMP1/PD1 | l | ALARM IN 6 | ||

| 44 | CMP2/PD2 | I | ALARM IN 7 | ||

| 45 | CMP3/PD3 | I | ALARM IN 8 | ||

| 46 | TRA/PE0 | I | REMOTE IN | ||

| 47 | TRB/PE1 | Ι | SETUP 2 | ||

| 48 | POO | I/0 | MOS | CS 0 | ROM |

| 49 | PO1 | 1/0 | MOS | CS 1 | OSD 2 |

| 50 | PO2 | I/0 | MOS | CS 2 | OSD 1 |

| 51 | PO3 | I/0 | MOS | CS 3 | |

| 52 | P10 | 1/0 | MOS | S/N 1 | |

| 53 | P11 | I/0 | MOS | S/N 2 | |

| 54 | P12 | I/0 | MOS | S/N 3 | |

| 55 | P13 | I/0 | MOS | S/N 4 | |

| 56 | VDD | - |

LC665 * * Pin Configuration (2)

Table. 3-3 Description of Terminals (2)

I2C Format

The format shown in figure 3-37 is utilized for data transfers. Following the start conditions, the slave address is transmitted. This address is 7 bits long; bit 8 is the data direction bit (R/W), with 0 indicating a transfer (write) and 1 indicating a data request (read). Data transfers are always terminated via stop conditions generated by the master. If, however, the master wishes to perform further communication on the bus, it can generate start conditions and specify another slave address even if it does not first generate stop conditions. With these types of transfers, a variety of format combinations for reads and writes is possible.

Fig. 3-37. A Complete Data Transfer

QUAD I2C Definition Table

| Sub-Address | Data 8 | Data 7 | Data 6 | Data 5 | Data 4 | Data 3 | Data 2 | Data 1 | |

| PLXNT | EXXIN | FRXPL | WBGXSM | RBGXSM | FLXQD | UXD | RXL | ||

| 0 |

PAL-NTS

"H"-"L" Switch |

Read Sync

Ext/Int "H"/"L" |

Read Sync

OSC/PLL "H"/"L" |

On Writes

Enlarge/Reduce "H"/"L" |

On Reads

Enlarge/Reduce "H"/"L" |

Output Screen

Full/Quarter "H"/"L" |

Output Position

Upper/Lower "H"/"L" |

Output Position

Right/Left "H"/"L" |

|

| FILONW | PAXCH | GSON | FULLON | FILONR | WB | PH1 | PH0 | ||

| 1 |

W Vert. Filter Read Sync Mark

OFF/ON Master/Slave ON "H"/"L" "H"/"L" "H |

Marker Disp.

ON/OFF "H"/"L" |

Full Screen Out

ON/OFF "H"/"L" |

R Vert. Filter

ON/OFF "H"/"L" |

B&W/Color

"H"/"L" |

PLL Ho

Phase Ac |

rizontal

djustment |

||

| NSTILL | FSTILL | P1WR | P2WR | P3WR | P1RD | P2RD | P3RD | ||

| 2 |

Normal Still

ON/OFF "H"/"L" |

Field Still

ON/OFF "H"/"L" |

Page 1 Write

ON/OFF "H"/"L" |

Page 2 Write

ON/OFF "H"/"L" |

Page 3 Write

ON/OFF "H"/"L" |

Page 1 Read

ON/OFF "H"/"L" |

Page 2 Read

ON/OFF "H"/"L" |

Page 3 Read

ON/OFF "H"/"L" |

|

| WSTH 8 | WSTH 7 | WSTH 6 | WSTH5 | WSTH4 | WSTH3 | WSTH2 | WSTH1 | ||

| 3 | H | orizontal Writ | e Start Positio | ิวท | |||||

| WSTV8 | WSTV 7 | WSTV6 | WSTV5 | WSTV4 | WSTV3 | WSTV2 | WSTV1 | ||

| 4 | Ň | Vertical Write | Start Positior | ١ | |||||

| RSTH8 | RSTH7 | RSTH6 | RSTH5 | RSTH4 | RSTH3 | RSTH2 | |||

| 5 | 5 Horizontal Read Start Position | ||||||||

| RSTV6 | RSTV5 | RSTV4 | RSTV3 | RSTV2 | RSTV1 | ||||

| 6 | Vertical Read | Start Positior | 1 | ||||||

| GSH8 | GSH7 | GSH6 | GSH5 | GSH4 | GSH3 | GSH2 | GSH1 | ||

| 7 | Picture Sensor Horizontal Position | ||||||||

| GSV8 | GSV7 | GSV6 | GSV5 | GSV4 | GSV3 | GSV2 | GSV1 | ||

| 8 | Pi | cture Sensor | Vertical Positi | on | |||||

| CHSIG | GSF6 | GSF5 | GSF4 | GSF3 | GSF2 | GSF1 | GSF0 | ||

| 9 |

Input

Switch |

Picture Se | ensor Sensitiv | ity Setting | |||||

| CKTST | DLOFF | GSM6 | GSM5 | GSM4 | GSM3 | GSM2 | GSM1 | ||

| 10 |

Clock Test

Normal: "L" |

For B&W

Delay Off |

Picture | Sensor Mark | er Brightness | Setting | |||

| OSHD8 | OSHD7 | OSHD6 | OSHD5 | OSHD4 | OSHD3 | OSHD2 | OSHD1 | ||

| 11 | HD Phase | e Adjustment | for On-Screer | 1 Function | |||||

| PHTST | PVTST | FHTST | FVTST | FATST | MTST | PV3TST | 1W/2R | ||

| 12 |

PLL System

Horiz. Test Normal : "L" |

PLL System

Vert. Test Normal : "L" |

Read System

Horiz. Test Normal :"L" |

Read System

Vert. Test Normal : "L" |

Memory Arbiter

System Test Normal: "L" |

Memory Data

System Test Normal :"L" |

PLL System

Vert. Test 3 Normal :"L" |

Test Mode

Setting Normal :"L" |

|

Table. 3-4

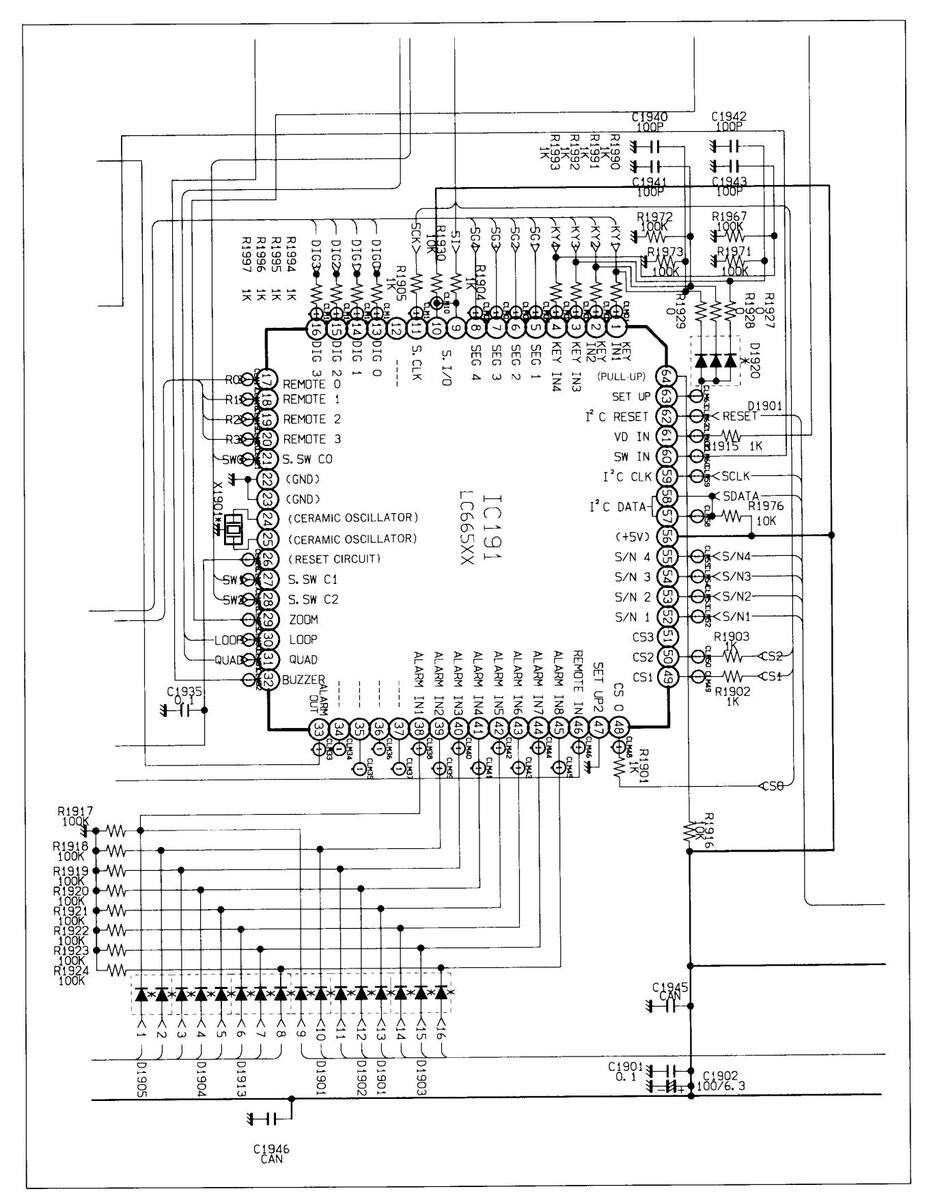

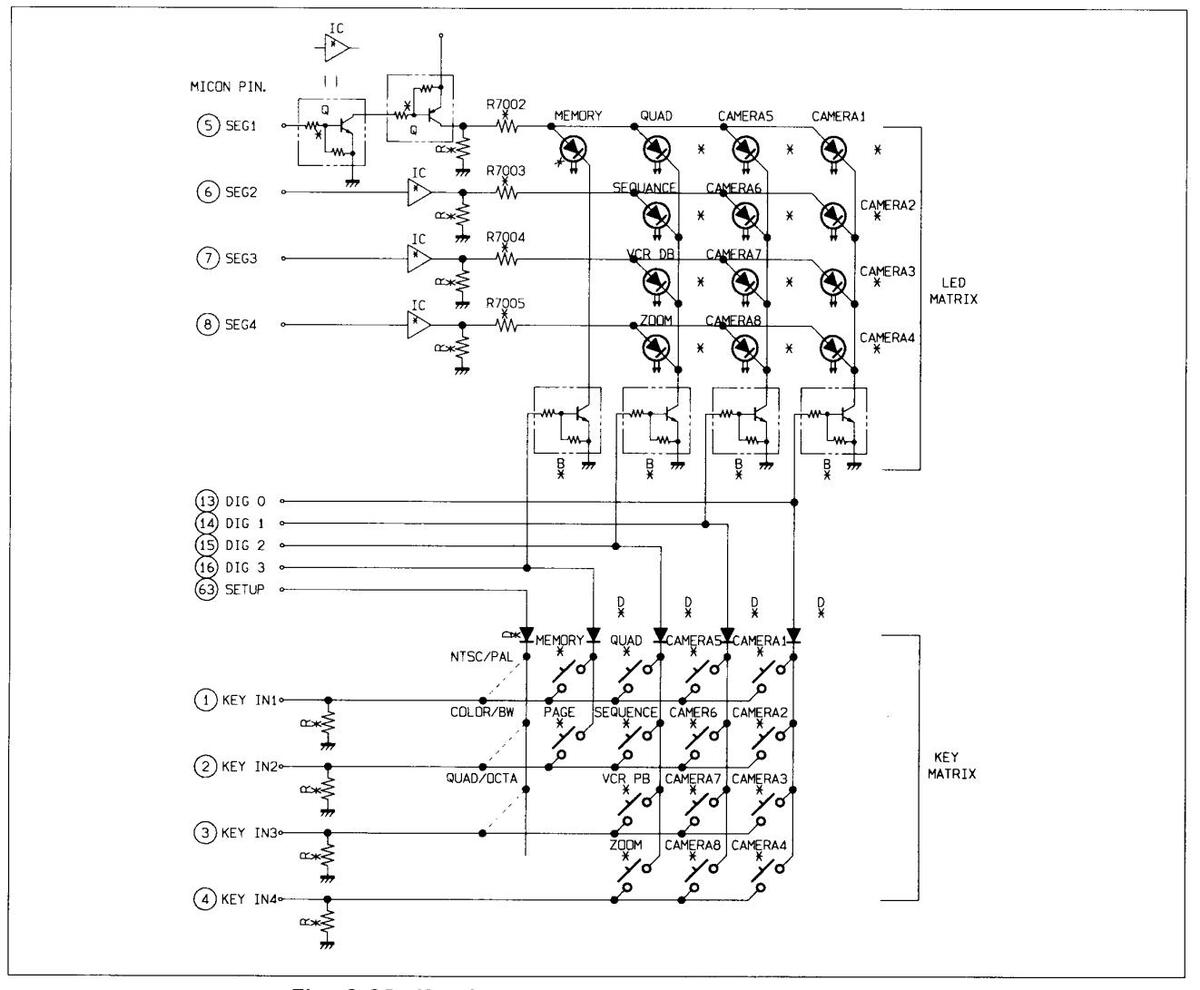

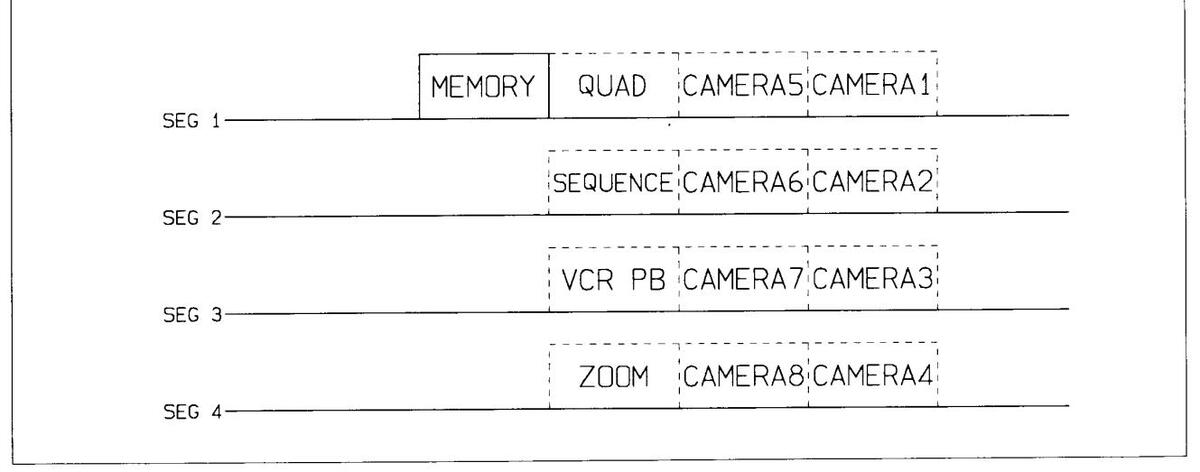

3-2-7. Key Input and LED Display Circuits (SY1, 2)

This unit's key input and LED display circuits are shown in figure 3-38. These circuits are operated via microcomputer input/output carried out from the front SY1, 2 circuit board.

1. Key Input

Pulses DIG 0-3, shown in figure 3-39 (a), are output to the key matrix in figure K-1. When a key switch goes on, the corresponding output is retrieved to KEY IN 1-4. Then, based on the timing of DIG 0-3 and the signals arriving at KEY IN 1-4, the key switch that went on is identified. For example, when the MEMORY switch is pressed, a DIG 3 pulse passes through a diode and through the MEMORY switch, and goes into KEY IN 1. If two DIG 3 pulses in a row go in, the MEMORY switch is identified as the key that was pressed.

Figure 3-39 (b) shows the identification of the key at the point when these pulses arrive at KEY IN

1-4. In addition, only immediately after the microcomputer is reset, the SETUP pulse at pin 63 is output and read-in of the initial settings is performed.

2. LED Driver Circuit

LEDs are driven using dynamic pulse lighting, and light up when both SEG 1-4 and DIG 0-3 are high.

If the positions representing SEG 1 and DIG 3 go on, for example, a pulse passes through a buffer and heads for four locations : CAMERA 1, CAMERA 5, QUAD, and MEMORY. Among transistors Q0-3, however, the only one which is on is Q3, so current flows to the MEMORY LED and this LED lights up. Figure 3-39 (c) shows the LED which lights up when the lighting pulse is output to SEG 1-4. When lighting is to be continuous, repeated output of these DIG and SEG pulses is performed periodically.

Fig. 3-38. Key Input and LED Display Circuit Diagram

Fig. 3-39. (b) KEY IN Input Waveforms and Read-In

Fig. 3-39. (c) SEG Output Waveforms and Lit LED

3-3. Digital Circuits

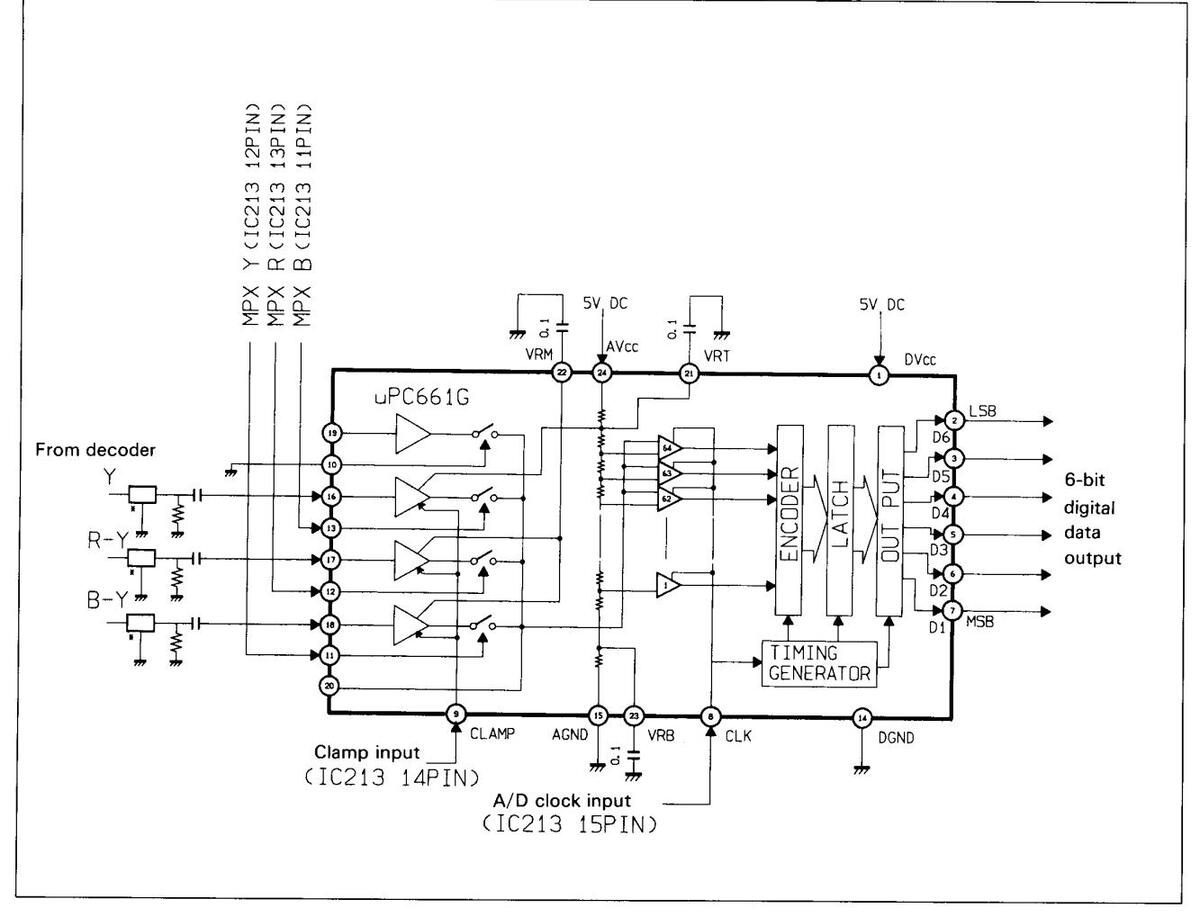

3-3-1. A/D Converter Circuit (IC211, IC221, IC231, IC231, IC241) (VD1)

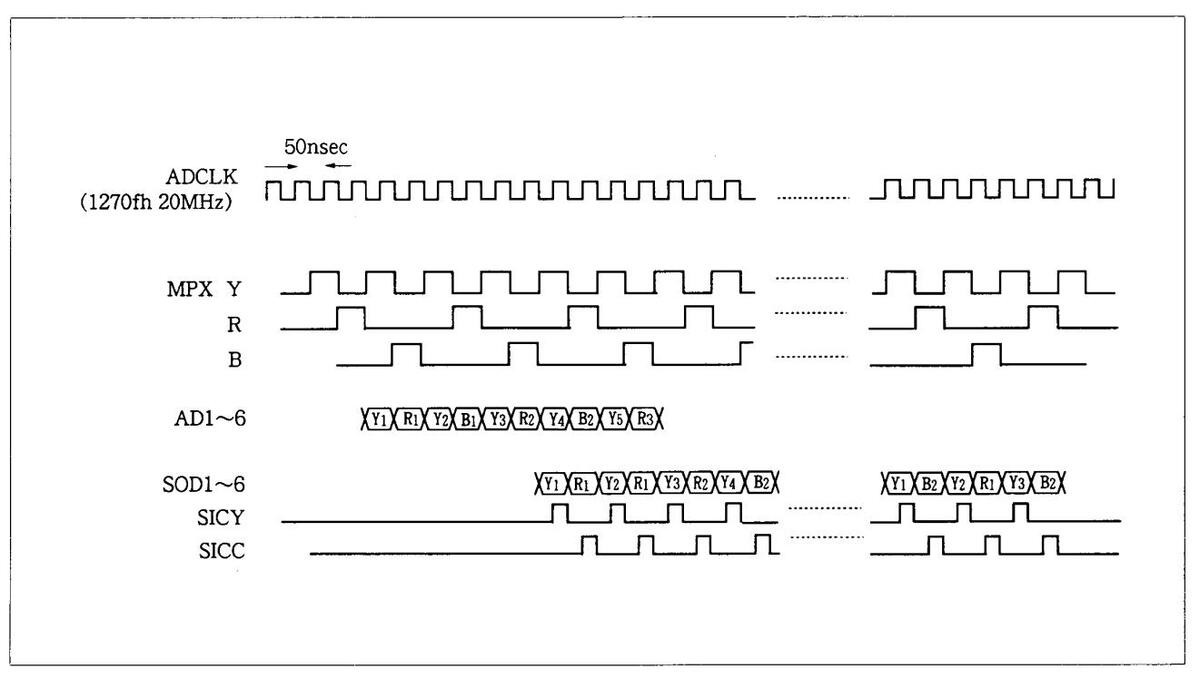

The intensity signal and coloration signals (R-Y, B-Y) from the decoder are A/D-converted by a 6-bit A/D converter (µPC 661 parallel-comparison A/D converter) which includes an internal analog multiplexer with clamping capability on each of its four inputs. A block diagram of this IC is presented in figure 3-40.

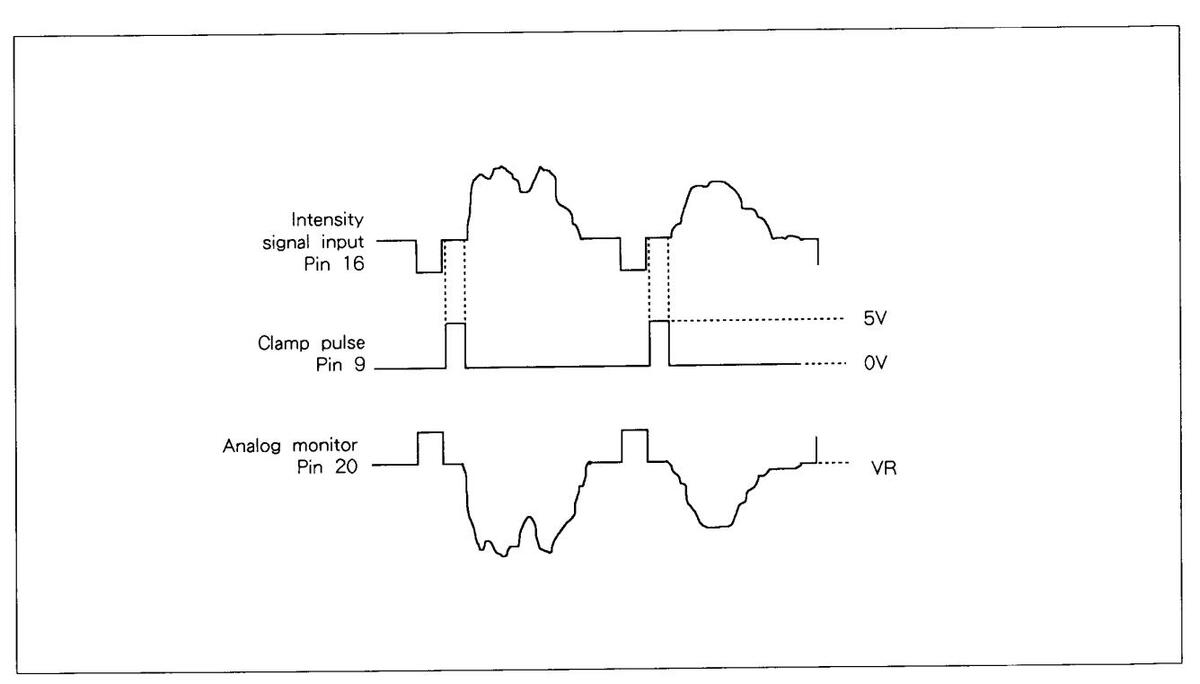

The intensity signal and coloration signals (R-Y, B-Y), which are respectively input to pins 16, 17, and 18, are first clamped by the clamp circuit.

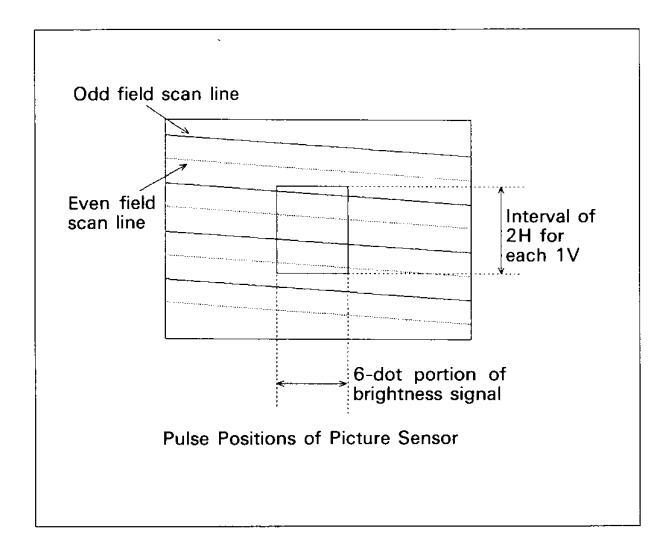

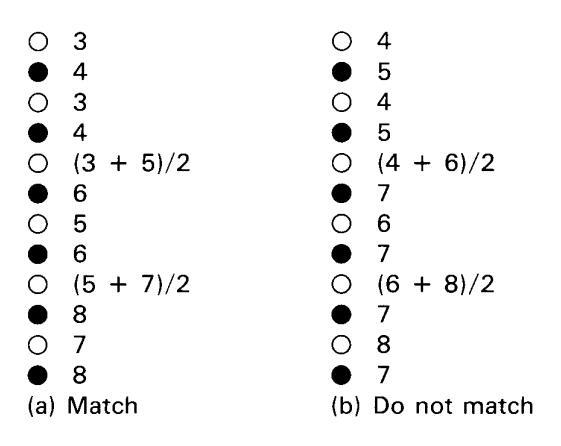

Multiplexing is then performed by the internal multiplexer in "Y, R-Y, Y, B-Y, Y,..." format. The timing chart for this is shown in figure 3-2.

The multiplexed signal is converted into digital data by the 6-bit A/D converter and output from pins 2 (LSB) to 7 (MSB).

Control of this multiplexer is carried out via pin 11 (MPX B), pin 12 (MPX R), and pin 13 (MPX Y).

Auxiliary clamping operations are also performed.

Firstly, for the intensity signal, while the clamp pulse at pin 9 is high, the signal voltage which has been input to pin 16 is clamped to make it equal to VRT (the reference top voltage) at pin 20. This is illustrated in figure 3-42. Next, similarly for the coloration signals as well, while the clamp pulse is high, the signals which have been input to pins 17 and 18 are clamped to make them equal to VRM (the reference midpoint voltage) at pin 20.

The A/D clock frequency in every mode is 20 MHz. For reduction, however, since the gate array data is thinned out, the effective frequency is as shown in table 3-5.

| Y Clock | R-Y Clock | B-Y Clock | |

|---|---|---|---|

| Reduction | 5MHz | 2.5MHz | 2.5MHz |

| 1:1 | 10MHz | 5MHz | 5MHz |

| ZOOM | 10MHz | 5MHz | 5MHz |

Table. 3-5

Fig. 3-40. A/D Converter Circuit

Fig. 3-41. A/D Converter Timing Chart

Fig. 3-42. Clamping at the Pedestal Level: Timing and Voltage Levels

3-3-2 D/A Converter Circuit (IC251) (VD1)

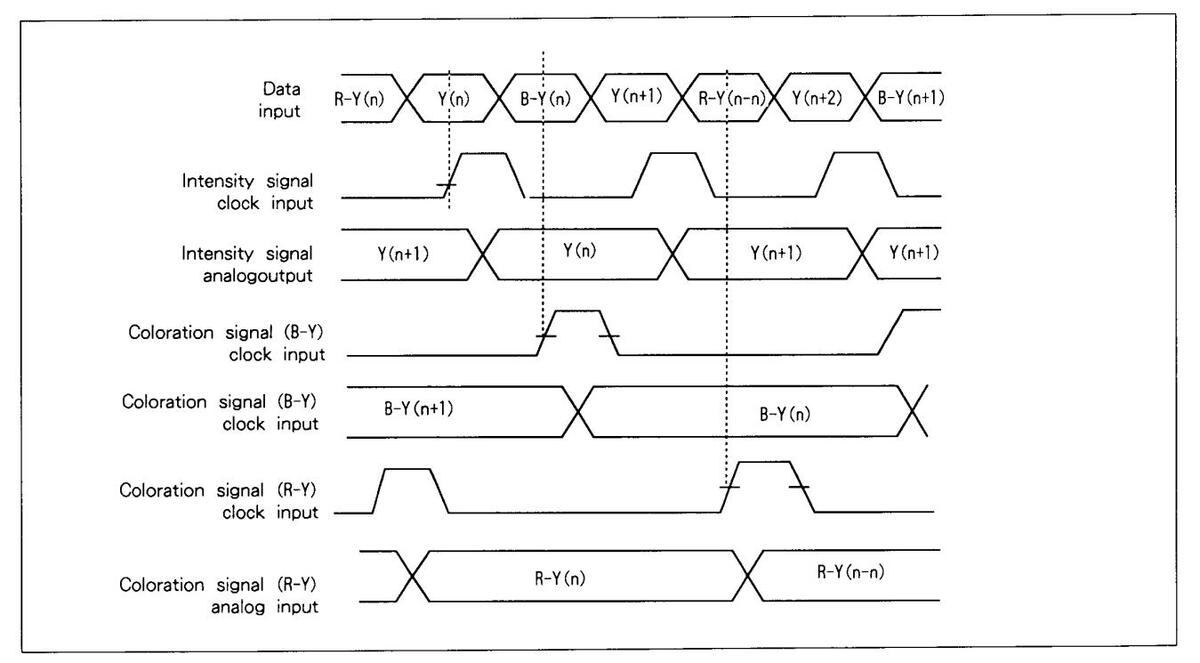

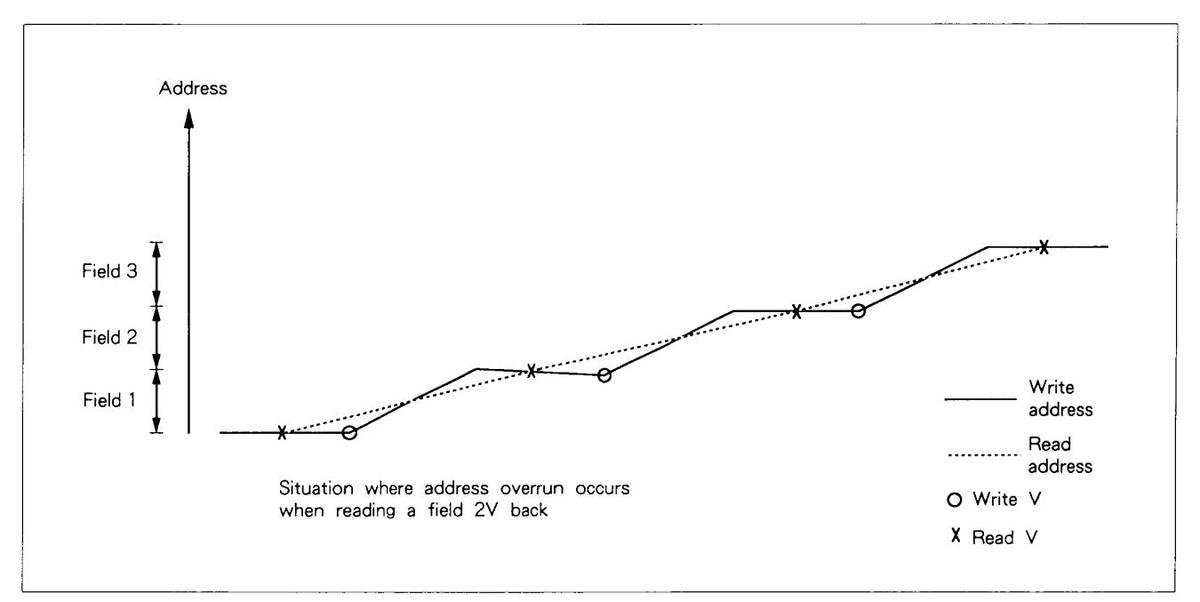

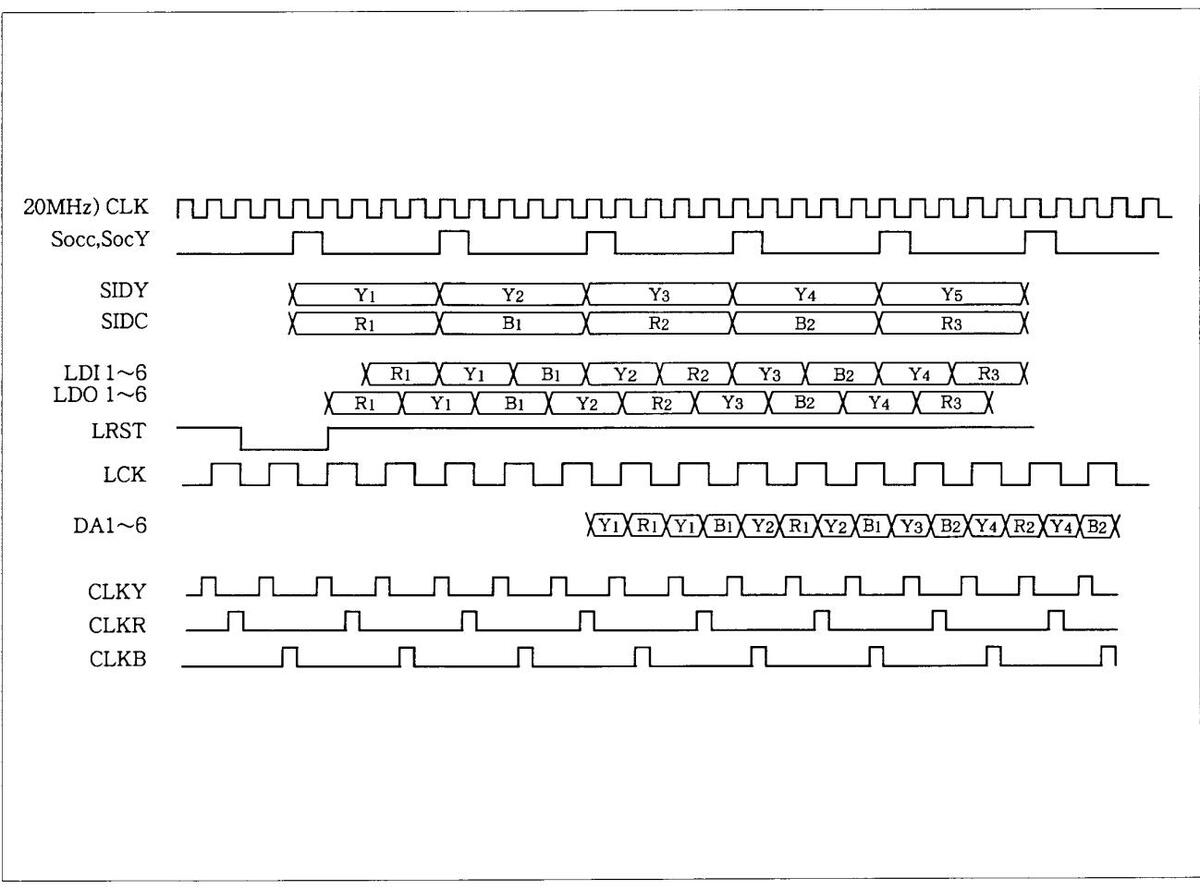

The 6-bit digital data from each of four respective gate arrays is sent on the same line utilizing time-division multiplexing. Synchronization thereof is performed based on the CLK, HD, and VD signals which are output from gate array IC243.

The 6-bit digital data sent in this fashion is D/ A-converted by a D/A converter unit (M52682FP, current-adding method) which contains three 6-bit high-speed D/A converters. A block diagram for this IC is shown in figure 3-43. The 6-bit digital data is input to pins 3 (LSB) to 8 (MSB).

Since there is a single common input for all three D/A converters, the multiplexed intensity signal and coloration signals (B-Y, R-Y) are separated by shifting the phase of the clock signals which are input to pin 10 (B-Y clock), pin 11 (R-Y clock), and pin 12 (intensity signal clock). Once converted to analog form, the respective signals are then output to pin 17 (intensity signal), pin 19 (B-Y), and pin 21 (R-Y).

The clock signals for pins 10 to 12 are output from IC243, while the blanking pulse for pin 15 is output

from IC233. The function of the blanking signal is to make the DC levels of Y, R-Y, and B-Y uniform by clamping them via the encoder. The various waveforms are illustrated in figure 3-44.

Figure 3-45 presents a timing chart of the conversion of the component signals. As shown in this figure, for the intensity signal and the coloration signals, the rising edge of the signals which are input to each of the respective clock input terminals is utilized to latch the digital data and convert it to analog data.

The D/A clock frequency in every mode is 20 MHz. For zooming, however, since the same data is output twice, the effective frequency is as shown in table 3-6.

| Y Clock | R-Y Clock | B-Y Clock | |

|---|---|---|---|

| Reduction | 10MHz | 5MHz | 5MHz |

| 1:1 | 10MHz | 5MHz | 5MHz |

| ZOOM | 5MHz | 2.5MHz | 2.5MHz |

Table. 3-6

Fig. 3-43. IC252 D/A Converter

Fig. 3-44. D/A Output

Fig. 3-45. D/A Converter Timing Chart

3-3-3. Gate Array Circuit (VD1)

1. Basic Features

Structure : 120-pin QFP, 7000 gates Process : 1.2 µm CMOS

Utilizes Seiko Epson gate array SLA860S

Supports PAL and NTSC

Digital control via I2C bus

Sync separation, built-in horizontal PLL and VCO System clock frequency : 1270 fH (approx. 20 MHz)

| Sampling Frequency | Samp | lina | Frequency |

|---|

| Normal | Enlarged | |

|---|---|---|

| Intensity signal | 5.0 MHz | 10.0 MHz |

| Coloration signal | 2.5 MHz | 5.0 MHz |

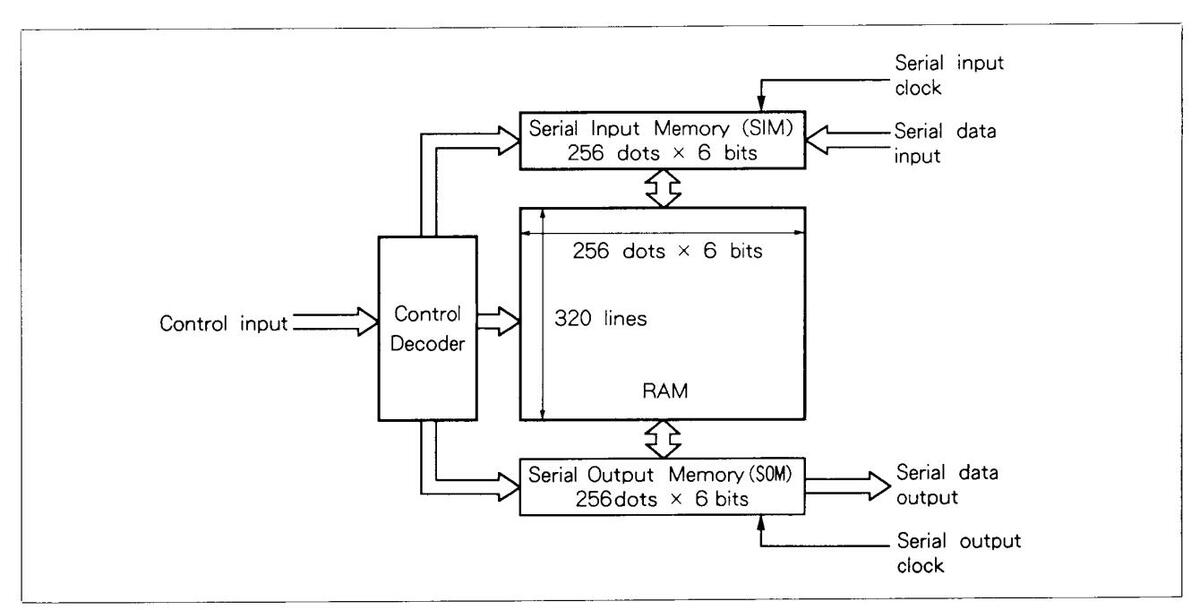

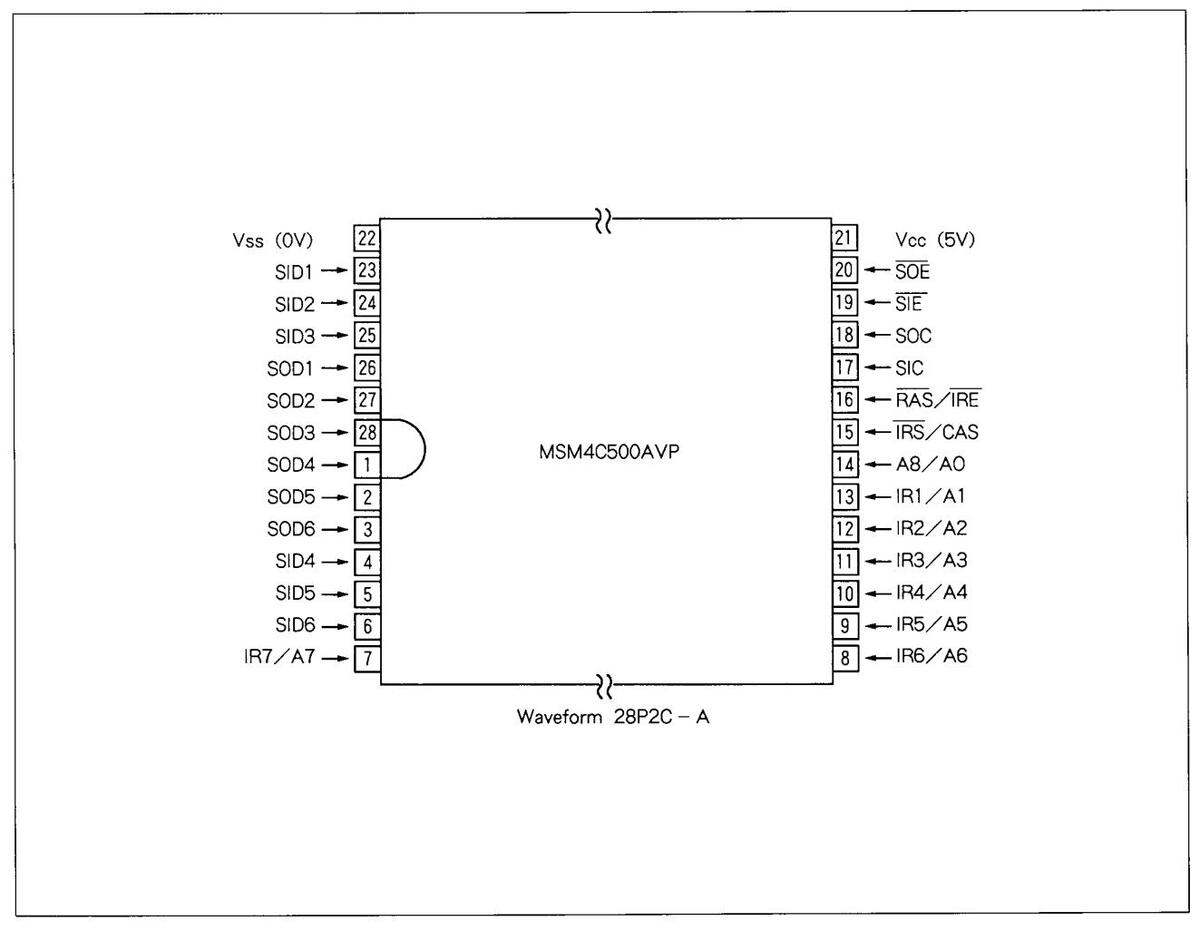

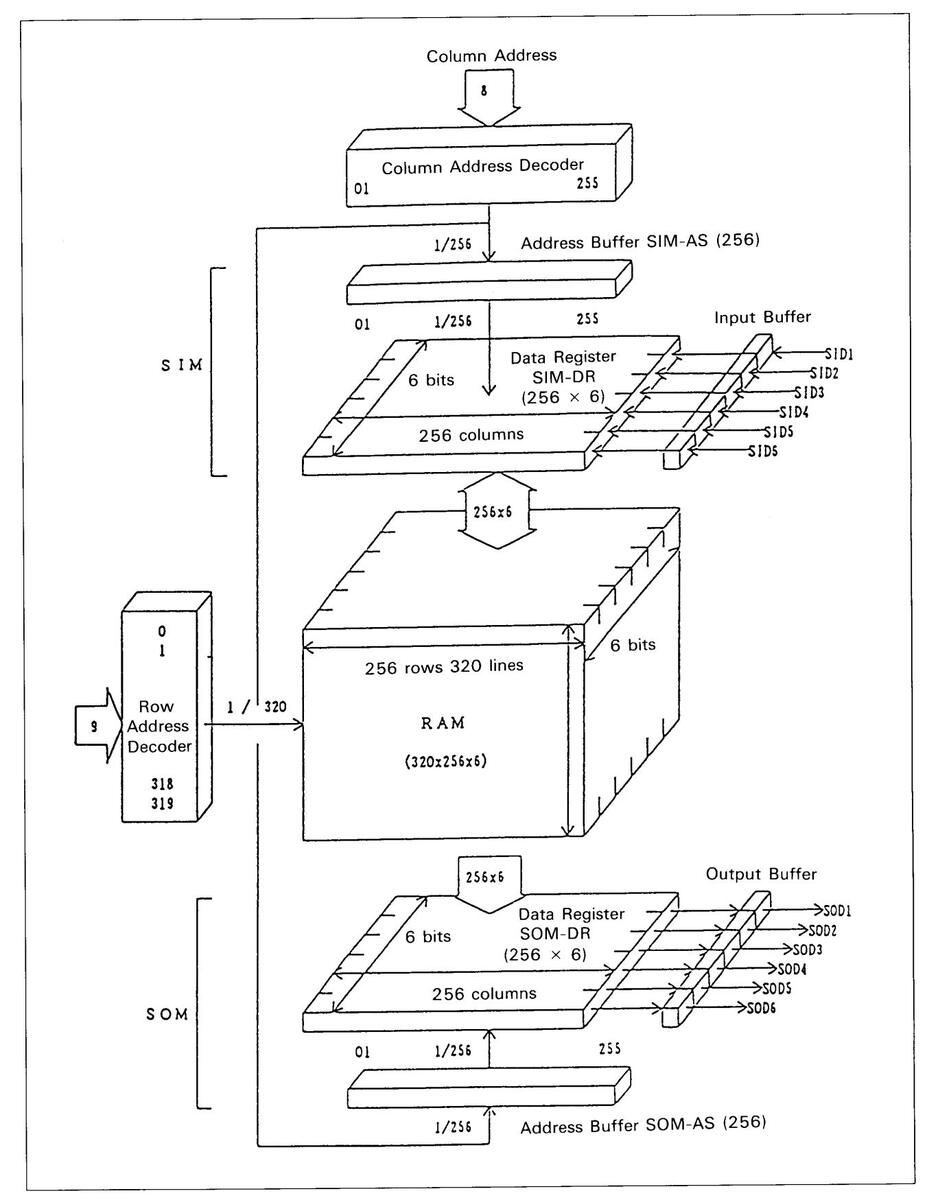

When supporting NTSC : 3-field recording method When supporting PAL : 2-field recording method Memory used : Mitsubishi M5M4C500AL (256 columns * 320 rows)

Recording Range :

| NTSC | PAL | |

|---|---|---|

| Horiz. direction | 256 dots | 256 dots |

| Vert. direction | 106 dots | 140 dots |

Contrast : 6 bits

Single-channel decoder output signals for both A/D (MPC661G) and D/A (M52682) :

HD pulse, clamp pulse

Encoder output signals :

HD pulse, composite sync signal, vertical sync signal, burst gate pulse, border pulse, blank pulse

Vertical LPF for line memory

Built-in phase reconciliation circuit for decoder and encoder intensity and coloration signals

Other features :

- (1) Enlargement during memory writes and memory reads

- (2) Horizontal write start position, vertical write start position, horizontal read start position and vertical read start position are all variable

- (3) Frame still and field still are possible Frame still ---- high resolution Field still --> page-by-page read and write are possible (3 pages for NTSC, 2 pages for PAL)

(4) Picture sensor utilizing frame correlation

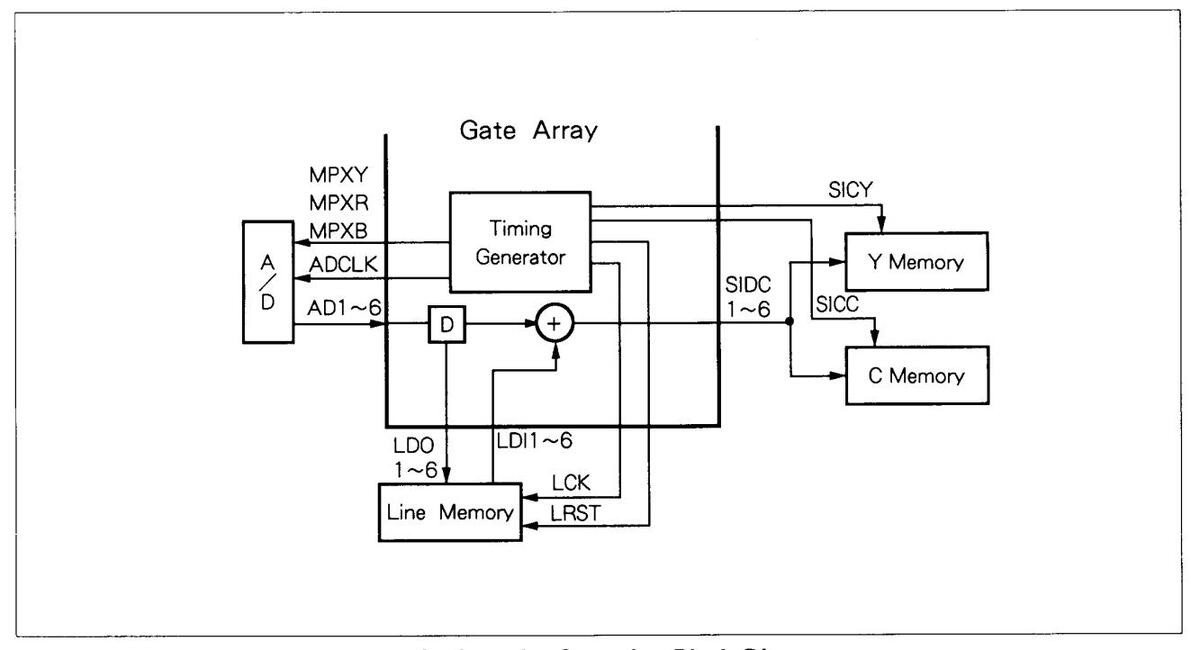

(Signal Flow)

In the A/D converter, the picture signal, which was digitized via the clock and locked onto the horizontal sync signal, is temporarily taken into the gate array. It is then written to memory after write vertical LPF. picture sensor, and other processing is performed. The picture signal written to the memory in this fashion is then retrieved in sync with the crystal oscillator used for data read-out, and input to the gate array. Within the gate array, the read vertical LPF phase reconciliation, multiplexing, and other processing is performed, and the signal is input to the D/A converter.

During exchanges of data between the various devices, the transfer rate differs according to the mode. The multiplexing method, however, is always the same, and is presented below.

● A/D → Gate Array

| Y R-Y Y B-Y Y R-Y | Υ | R-Y | Υ | B-Y | Y | R-Y |

|---|

● Gate Arrav → Memory

Y memory and C memory share a common data line, and write operations are divided using the clock

| Υ | R-Y | / Y B-Y | Y | R-Y | |

|---|---|---|---|---|---|

|

↑

Y memory write clock |

↑

G memory write |

↑

Y memory write |

↑

G memory write |

↑

Y memory write |

↑

G memory write |

● Memory --> Gate Array

| Y memory output | Υ | Υ | Υ | Υ | Υ |

|---|---|---|---|---|---|

| C memory output | R-Y | B-Y | R-Y | B-Y | R-Y |

• Gate Array D/A

The D/A has three channels sharing the same data line, with data separation performed via the clock signal.

This data line is also connected to four gate arrays, with tri-state control utilized to avoid data collisions

| Υ | R-Y | Υ | B-Y | Υ | R-Y |

|---|---|---|---|---|---|

| ↑ | ↑ | ↑ | ↑ | ↑ | ↑ |

| Y data | R-Y data | Y data | B-Y memory | Y data | R-Y data |

| clock | clock | clock | clock | clock | clock |

Fig. 3-46. Block Diagram of Digital Components

2. Pin Configuration Table

| Pin No. | Pin Name | PAD | I/0 | CELL | Remarks |

|---|---|---|---|---|---|

| 1 | HD | 1 | В | BC1 | Read horizontal sync input/output |

| 2 | VSS | 2 | GND | ||

| 3 | CLKOUT | 3 | 0 | TB2 | Read clock output |

| 4 | CLKIN | 4 | I | IBC | Read clock input |

| 5 | AD1 | 5 | |||

| S | S | S | IBT | A/D data input AD1 → MSB | |

| 10 | AD6 | 10 | |||

| 11 | MPXB | 11 | 0 | OB2 | A/D multiplexer B-Y select |

| 12 | MPXY | 12 | 0 | OB2 | A/D multiplexer Y select |

| 13 | MPXR | 13 | 0 | OB2 | A/D multiplexer R-Y select |

| 14 | CLMP | 14 | 0 | OB2 | Clamp output for A/D |

| 15 | ADCLK | 15 | 0 | OB2 | A/D clock output |

| 16 | HASY | 17 | 0 | TB2 | PLL phase comparison output |

| 17 | STSY | 18 | 0 | TB2 | PLL phase comparison output |

| 18 | VDD | 19 | POWER | ||

| 19 | PDO | 20 | 0 | INI. A | PLL integrator output |

| 20 | PDI | 21 | 1 | INI. XA | PLL integrator input |

| 21 | CMTEST | 22 | Ι | IBC | Comparator test (normal : "L") |

| 22 | HSEP 2 | 23 | 0 | SAN1.ZX | Horizontal sync separation recharge current output terminal |

| 23 | VIDI | 24 | 1 | SAN1.A | Horizontal sync separation input terminal |

| 24 | HSEP 1 | 25 | 0 | SAN1.XA | Horizontal sync separation LPF inverter amp output |

| 25 | SLO | 26 | 0 | IN1.XA | Slice level setting interter output |

| 26 | SLI | 27 | Ι | IN1.A | Slice level setting interter input |

| 27 | VSEP | 28 | 0 | SAN2.XA | Vertical sync separation LPF inverter amp output |

| 28 | VSYI1 | 29 | Ι | SAN2.A | Vertical sync separation input terminal |

| 29 | VSS | 30 | GND | ||

| 30 | KILJD | 31 | Ι | INI.A | Synchronous/asynchronous discrimination input |

| 31 | VDD | 33 | POWER | ||

| 32 | VSS | 34 | GND | ||

| 33 | VC00 | 35 | 0 | IN2.XA | Inverter amp output terminal for VCO |

| 34 | VCOI | 36 | I | IN2.A | Inverter amp input terminal for VCO |

| 35 | VSS | 37 | GND | ||

| 36 | VDD | 38 | POWER | ||

| 37 | HYS | 39 | 0 | TB2 | Output terminal for synchronous/asynchronous discrimination circuit |

| 38 | HILOF | 40 | 0 | TB2 | Output terminal for synchronous/asynchronous discrimination circuit |

| 39 | KILON | 41 | 0 | TB2 | Output terminal for synchronous/asynchronous discrimination circuit |

| 40 | CSY01 | 42 | 0 | OB2 | Horizontal sync signal output |

| 41 | HDDEC | 43 | 0 | OB2 | HD pulse output for decoder |

| 42 | CLKBY | 44 | 0 | TB2 | B-Y clock for D/A |

| 43 | CLKRY | 45 | 0 | TB2 | R-Y clock for D/A |

| 44 | CLKY | 46 | 0 | TB2 | Y clock for D/A |

| 45 | BLKXVD | 47 | 0 | OB2 | Main address 3 → read VD2 → read blank pulse |

| 46 | CSYXBG | 48 | 0 | OB2 | Main address 3 → read burst gate 2 → read CSYNC |

Fig. 3-7. Pin Configuration Table (1)

| Pin No. | Pin Name | PAD | 1/0 | CELL | Remarks |

|---|---|---|---|---|---|

| 47 | WKXOS | 49 | В | BC1 | Main address 3 → read clock input → read border |

| 48 | HENXHD | 50 | 0 | OB2 | Main address 3 → read on-screen HD2 → encoder HD |

| 49 | SDA | 51 | В | BC2 | I 2 C bus data line |

| 50 | VSS | 52 | GND | ||

| 51 | DA6 | 53 | |||

| S | S | S | 0 | TB2 | D/A input data DA6 → LSB |

| 53 | DA4 | 55 | |||

| 54 | VSS | 56 | GND | ||

| 55 | DA3 | 57 | |||

| 5 | Ś | S | 0 | TB2 | D/A input data DA1 → A MSB |

| 57 | DA1 | 59 | |||

| 58 | SOCC | 60 | 0 | OB2 | Memory output clock for coloration |

| 59 | VSS | 61 | GND | ||

| 60 | VDD | 62 | POWER | ||

| 61 | SCL | 64 | I | IBS | I 2 C bus clock line |

| 62 | RSTCK | 65 | 1 | IBC | Clock system reset input "H" to reset |

| 63 | RESET | 66 | I | IBS | Gate array reset "L" to reset |

| 64 | ADR2 | 67 | 1 2 C bug main address setting | ||

| S | S | S | IBC | ||

| 65 | ADR1 | 68 | |||

| 66 | SIDC1 | 69 | Coloration memory output data | ||

| 5 | IBC | SIDC 1 → MSB | |||

| SIDCO | 74 | ||||

| 12 | LDIT | /5 | Line memory output data | ||

| 75 |

)

78 |

вс | LDI 1 → MSB | ||

| 76 | 80 | ||||

| 1 | IBC | Line memory output data | |||

| 77 | LDI6 | 81 | LDI 6 → LSB | ||

| 78 | SIGNA | 82 | О | OB2 |

Input presence/absence determination output "L" → absent "H"

→ present |

| 79 | SENSO | 83 | 0 | OB2 | Picture sensor output "L" → not operating "H" → operating |

| 80 | SICC | 84 | 0 | OB2 | Coloration memory input clock |

| 81 | RAS | 85 | 0 | OB2 | Memory control output (common Y/C) |

| 82 | IRS | 86 | 0 | OB2 | Memory control output (common Y/C) |

| 83 | VSS | 87 | GND | ||

| 84 | LDO1 | 88 | |||

| S | S | S | 0 | OB2 | |

| 88 | LDO5 | 92 | |||

| 89 | VDD | 93 | POWER | ||

| 90 | LDO6 | 94 | 0 | OB2 | Line memory input data LSB |

| 91 | VSS | 96 | GND | ||

| 92 | VDD | 97 | POWER | ||

| 93 | IR7XA7 | 98 | |||

| S | S | S | 0 | OB2 | Memory control output (common Y/C) |

| 99 | IR1XA1 | 104 | |||

| 100 | A8XAOS | 105 | 0 | OB2 | Memory control output (common Y/C) |

| 101 | VDD | 106 | POWER |

Fig. 3-7. Pin Configuration Table (2)

| Pin No. | Pin Name | PAD | I/0 | CELL | Remarks | |

|---|---|---|---|---|---|---|

| 102 | LCK | 107 | 0 | OB2 | Clock for line memory | |

| 103 | LRST | 108 | 0 | OB2 | Line memory reset | |

| 104 | SICY | 109 | 0 | OB2 | Intensity memory input clock | |

| 105 | SOCY | 110 | 0 | OB2 | Intensity memory output clock | |

| 106 | SOD1 | 111 | Memory input data (common Y/C) | |||

| S | S | S | 0 | OB2 | SOD 1 → MSB | |

| 111 | SOD6 | 116 | ||||

| 112 | SIDY6 | 117 | Intensity memory output data | |||

| S | S | S | I | IBC | ||

| 117 | SIDY1 | 122 | ||||

| 118 | VD | 123 | В | BC1 | Read vertical sync input/output | |

| 119 | VDD | 124 | POWER | |||

| 120 | CHGO | 125 | 0 | Signal switch output | ||

Fig. 3-7. Pin Configuration Table (3)

Notes : Input/output cell functional description

©Bidirectional terminals

BC1 : CMOS level input/output cell

BC2 : CMOS level input/output cell (for l22C' SDA)

◎Input terminals

IBC : CMOS level input cell

IBT : TTL level input cell

IBS : Schmidt trigger input cell (for l22C' SCL)

Output terminals

OB2 : Output cell

TB2 : Tri-state output cell

QUAD I22C Definition Table

| Sub-Address | Data 8 | Data 7 | Data 6 | Data 5 | Data 4 | Data 3 | Data 2 | Data 1 | |

| PLXNT | EXXIN | FRXPL | WBGXSM | RBGXSM | FLXQD | UXD | RXL | ||

| 0 |

PAL-NTS

″H″-″L″ Switch |

Read Sync

Ext/Int "H"/"L" |

Read Sync

OSC/PLL "H"/"L" |

On Writes

Enlarge/Reduce "H"/"L" |

On Reads

Enlarge/Reduce "H"/"L" |

Output Screen

Full/Quarter "H"/"L" |

Output Position

Upper/Lower "H"/"L" |

Output Position

Right/Left "H"/"L" |

|

| FILONW | PAXCH | GSON | FULLON | FILONR | WB | PH1 | РНО | ||

| 1 |

W Vert. Filter

OFF/ON "H"/"L" |

Read Sync

Master/Slave "H"/"L" |

Marker Disp.

ON/OFF "H"/"L" |

Full Screen Out

ON/OFF "H"/"L" |

R Vert. Filter

ON/OFF "H"/"L" |

B & W/Color

"H"/"L" |

PLL Horizo

Position A |

ontal

djustment |

|

| NSTILL | FSTILL | P1WR | P2WR | P3WR | P1RD | P2RD | P3RD | ||

| 2 |

Normal Still

ON/OFF "H"/"L" |

Full Still

ON/OFF "H"/"L" |

Page 1 Write

ON/OFF "H"/"L" |

Page 2 Write

ON/OFF "H"/"L" |

Page 3 Write

ON/OFF "H"/"L" |

Page 1 Read

ON/OFF "H"/"L" |

Page 2 Read

ON/OFF "H"/"L" |

Page 3 Read

ON/OFF "H"/"L" |

|

| WSTH 8 | WSTH 7 | WSTH 6 | WSTH 5 | WSTH 4 | WSTH 3 | WSTH 2 | WSTH 1 | ||

| 3 | Horizontal Wri | te Start Positio | n | ||||||

| WSTV 8 | WSTV 7 | WSTV 6 | WSTV 5 | WSTV 4 | WSTV 3 | WSTV 2 | WSTV 1 | ||

| 4 | Vertical Write | Start Position | |||||||

| RSTH 8 | RSTH 7 | RSTH 6 | RSTH 5 | RSTH 4 | RSTH 3 | RSTH 2 | |||

| 5 | Horizor | ntal Read Start | Position | ||||||

| RSTV 6 | RSTV 5 | RSTV 4 | RSTV 3 | RSTV 2 | RSTV 1 | ||||

| 6 | Vertical Read Start Position | ||||||||

| GSH 8 | GSH 7 | GSH 6 | GSH 5 | GSH 4 | GSH 3 | GSH 2 | GSH 1 | ||

| 7 | Pi | cture Sensor H | orizontal Positi | on | J | ||||

| GSV 8 | GSV 7 | GSV 6 | GSV 5 | GSV 4 | GSV 3 | GSV 2 | GSV 1 | ||

| 8 | Picture Sensor Vertical Position | ||||||||

| CHSIG | GSF 6 | GSF 5 | GSF 4 | GSF 3 | GSF 2 | GSF 1 | GSF 0 | ||

| 9 | Input Switch | Picture S | ensor Sensitivi | ty Setting | J | ||||

| CKTST | DLOFF | GSM 6 | GSM 5 | GSM 4 | GSM 3 | GSM 2 | GSM 1 | ||

| 10 | Clock Test | For B & W | • | ······ | |||||

| Normal : "L" | Delay Off | Pictur | e Sensor Mark | er Brightness S | etting | ||||

| OSHD 8 | OSHD 7 | OSHD 6 | OSHD 5 | OSHD 4 | OSHD 3 | OSHD 2 | OSHD 1 | ||

| 11 | HD Phase Adjustment for On-Screen Function | ||||||||

| PHTST | PVTST | FHTST | FVTST | FATST | MTST | PV3TST | 1W/2R | ||

| 12 |

PLL System

Horiz. Test Normal : "L" |

PLL System

Vert. Test Normal : "L" |

Read System

Horiz . Test Normal : "L" |

Read System

Vert. Test Normal : "L" |

Memory Arbiter

System Test Normal : "L" |

Memory Data

System Test Normal : "L" |

PLL System

Vert. Test 3 Normal : "L" |

Test Mode

Setting Normal : "L" |

|

Table. 3-8. QUAD I2C Definition Table

3 Eunctional Description of I2C Bus

PLXNT ; Switches between PAL mode and NTSC mode

"H" for PAL mode

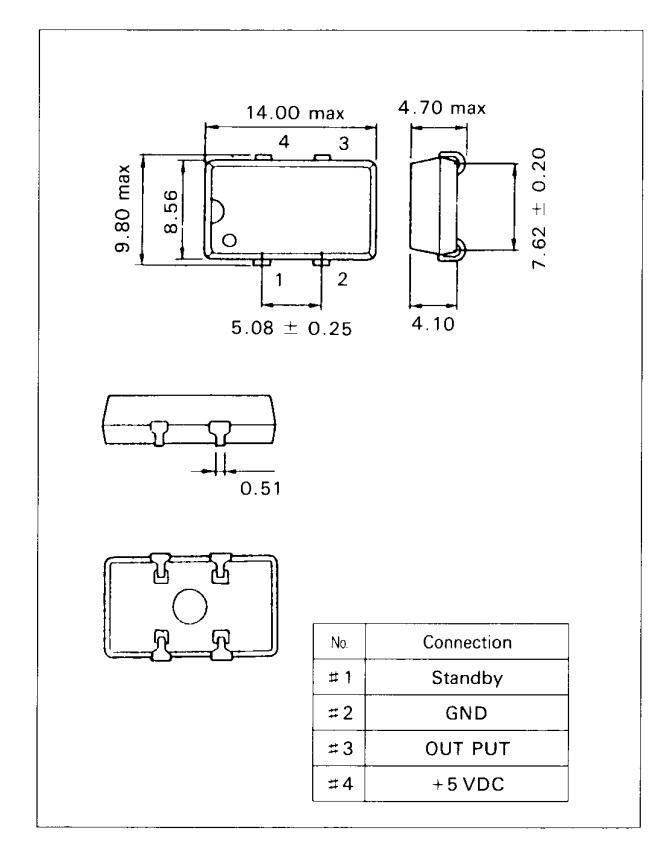

"L" for NTSC mode