Page 1

Ordering number : ENN*6614

82500RM (OT) No. 6614-1/12

Functions

• CD-ROM decoder/encoder functions

• CD decoder/encoder functions

• Pit and wobble CLV servo

• CAV audio functions

• SCSI interface (include the register block)

• Subcode encoder/decoder functions

• ATIP demodulator/ATIP decoder

• Write strategy function (CD-R/RW)

• CD-DSP function with built-in digital servo

Features

• ECC and EDC correction/addition (decoding/encoding)

for CD-ROM data.

• ECC error correction/addition (decoding/encoding) for

subcode data

• Servo control implemented in a digital servo system

(decoding/encoding)

• Wobble CLV servo control using ATIP data (encoding)

• ATIP decoding function and CRC check function

(decoding/encoding)

• CIRC code generation and addition and EFM

modulation (encoding)

• CAV audio functions

• Write strategy function supports 8× and 16× recording.

• Built-in SCSI interface (supports Ultra SCSI)

• Supports 40× decoding and 16× encoding.

Clock frequencies: CD-ROM block: 33.8688 MHz,

SCSI block: 20 MHz

• Ultra SCSI data transfer rate: 20 Mbyte/s (Maximum

synchronous transfer rate), Fast SCSI: 10 Mbyte/s

(Maximum synchronous transfer rate), 5 Mbyte/s

(Maximum asynchronous transfer rate)

Uses 16-bit data bus 50 ns EDO DRAM.

• From 1 to 64 Mbits of buffer RAM can be used. (16-bit

data bus EDO DRAM)

• The user can freely set up the CD main channel, C2 flag,

and subcode areas in buffer RAM.

• Batch transfer function (Function for transferring the CD

main channel, C2 flag, subcode, and other data in a

single operation)

• Multi-transfer function (Function for automatically

transferring multiple blocks to the host in a single

operation)

Package Dimensions

unit: mm

3210-SQFP208

28.0

(3.2)

30.6

0.15

0.2

0.35

3.8max

0.5

30.6

(0.5)

(1.25)

28.0

1

52

156 105

53

208

104

157

Preliminary

SANYO: SQFP208

[LC898023K]

LC898023K

SANYO Electric Co.,Ltd. Semiconductor Company

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

40× Playback/16× Write CD-R/RW Encoder/Decoder IC

with Built-in SCSI Interface

CMOS IC

Any and all SANYO products described or contained herein do not have specifications that can handle

applications that require extremely high levels of reliability, such as life-support systems, aircraft’s

control systems, or other applications whose failure can be reasonably expected to result in serious

physical and/or material damage. Consult with your SANYO representative nearest you before using

any SANYO products described or contained herein in such applications.

SANYO assumes no responsibility for equipment failures that result from using products at values that

exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other

parameters) listed in products specifications of any and all SANYO products described or contained

herein.

“BURN-Proof” stands for Proof against Buffer Under RuN

error, not for proof against burning.

“BURN-Proof” is a trademark of SANYO Electric Co.,Ltd.

Page 2

No. 6614-2/12

LC898023K

Parameter Symbol Conditions Ratings Unit

Supply voltage

V

DD

5 max Ta ≤ 25°C –0.3 to +6.0 V

V

DD

3 max Ta ≤ 25°C –0.3 to +4.6 V

I/O voltages

V

I

5, VO5 Ta ≤ 25°C –0.3 to VDD5 + 0.3 V

V

I

3, VO3 Ta ≤ 25°C –0.3 to VDD3 + 0.3 V

Allowable power dissipation Pd max Ta ≤ 70°C 750 mW

Operating temperature Topr –30 to +70 °C

Storage temperature Tstg –55 to +125 °C

Soldering conditions (pins only) 10 seconds 260 °C

Specifications

Absolute Maximum Ratings at VSS= 0 V

Parameter Symbol Conditions

Ratings

Unit

min typ max

[I/O cells, 5.0 V power supply]

Supply voltage V

DD

5 4.5 5.0 5.5 V

Input voltage range V

IN

0V

DD

5V

[Internal cells, 3.3 V power supply]

Supply voltage V

DD

3 3.0 3.3 3.6 V

Input voltage range V

IN

0V

DD

3V

Allowable Operating Ranges at Ta = –30 to +70°C, VSS= 0 V

Parameter Symbol Conditions

Ratings

Unit

min typ max

High-level input voltage V

IH

TTL level inputs: (2), (14)

2.2 V

Low-level input voltage V

IL

0.8 V

High-level input voltage V

IH

TTL level inputs with built-in pull-up resistors: (13)

2.2 V

Low-level input voltage V

IL

0.8 V

High-level input voltage V

IH

TTL level Schmitt trigger inputs: (1)

2.5 V

Low-level input voltage V

IL

0.6 V

High-level input voltage V

IH

(15)

2.0 V

Low-level input voltage V

IL

0.8 V

High-level input voltage V

IH

CMOS level Schmitt trigger inputs: (3)

0.8 V

DD

V

Low-level input voltage V

IL

0.2 V

DD

V

High-level input voltage V

IH

CMOS level inputs with built-in pull-up resistors: (4)

0.7 V

DD

V

Low-level input voltage V

IL

0.3 V

DD

V

Analog input voltage V

ANI

(5) 1/4 V

DD

3/4 V

DD

V

High-level output voltage V

OHIOH

= –12 mA: (8) VDD– 2.1 V

Low-level output voltage V

OLIOL

= 12 mA: (8) 0.4 V

High-level output voltage V

OHIOH

= –8 mA: (7) VDD– 2.1 V

Low-level output voltage V

OLIOL

= 8 mA: (7) 0.4 V

High-level output voltage V

OHIOH

= –2 mA: (6), (13), (14) VDD– 2.1 V

Low-level output voltage V

OLIOL

= 2 mA: (6), (13), (14) 0.4 V

Low-level output voltage V

OLIOL

= 48 mA: (15) 0.4 V

Low-level output voltage V

OLIOL

= 8 mA: (12) 0.4 V

Low-level output voltage V

OLIOL

= 1 mA: (9) 0.4 V

High-level output voltage V

OHIOH

= –4 mA: (11) VDD– 2.1 V

Low-level output voltage V

OLIOL

= 4 mA: (11) 0.4 V

Analog output voltage V

ANO

(10) 1/4 V

DD

3/4 V

DD

V

Input leakage current I

IL

VI= VSS, VDD: (1), (2), (14), (15) –10 +10 µA

Output leakage current I

OZ

In the high-impedance output state: (9), (11), (12) –10 +10 µA

Pull-up resistance R

UP

(12), (13) 40 80 160 kΩ

Pull-up resistance R

UP

(4) 50 100 200 kΩ

Electrical Characteristics at Ta = –30 to +70°C, VSS= 0 V, VDD= 4.5 to 5.5 V

The applicable pin groups are listed on the following page.

Page 3

Applicable Pins

[INPUT]

(1) · · · · · · WOBBLE, CS, RD, WR, DEF, HFL, TES

(2) · · · · · · SUA0 to SUA7, TEST0 to TEST4, RESET

(3) · · · · · · WRITE

(4) · · · · · · FG

(5) · · · · · AD0, AD1, RREC, FE, TE, VREF, FR, OPP, JITIN, PCKISTF, PCKISTP, EFMIN, EFMIN2, SLCIST1,

SLCIST2

[OUTPUT]

(6) · · · · · · LDON

(7) · · · · · EFMG, SHOCK, LOCK, EFMO, SSP2/1, RAPC, WAPC, H11TO, LDH, ATEST3, ATEST1, WDAT,

NWDAT

(8) · · · · · · PCK2, RA0 to RA9, CAS0 to CAS1, RAS0 to RAS2, LWE, UWE, OE, SUBSYNC

(9) · · · · · · PDS1 to PDS3

(10) · · · · · DA0 to DA2, TDO, FDO, SLDO, SPDO, JITC, LOUT, ROUT, PDO, RPO, SLDO, SLCO1 to SLCO3

(11) · · · · · DSLB

(12) · · · · · INT0, INT1, SWAIT

[INOUT]

(13) · · · · · D0 to D7, ID0 to ID15

(14) · · · · · ATIPSYNC, BICLK, BIDATA, ACRCNG

(15) · · · · · ACK, ATN, BSY, C/D, DB0 to DB7, DBP, I/O, MSG, REQ, RST, SEL

Note: The XTAL0, XTAL1, XTALCK0, and XTALCK1 are not included in the DC characteristics.

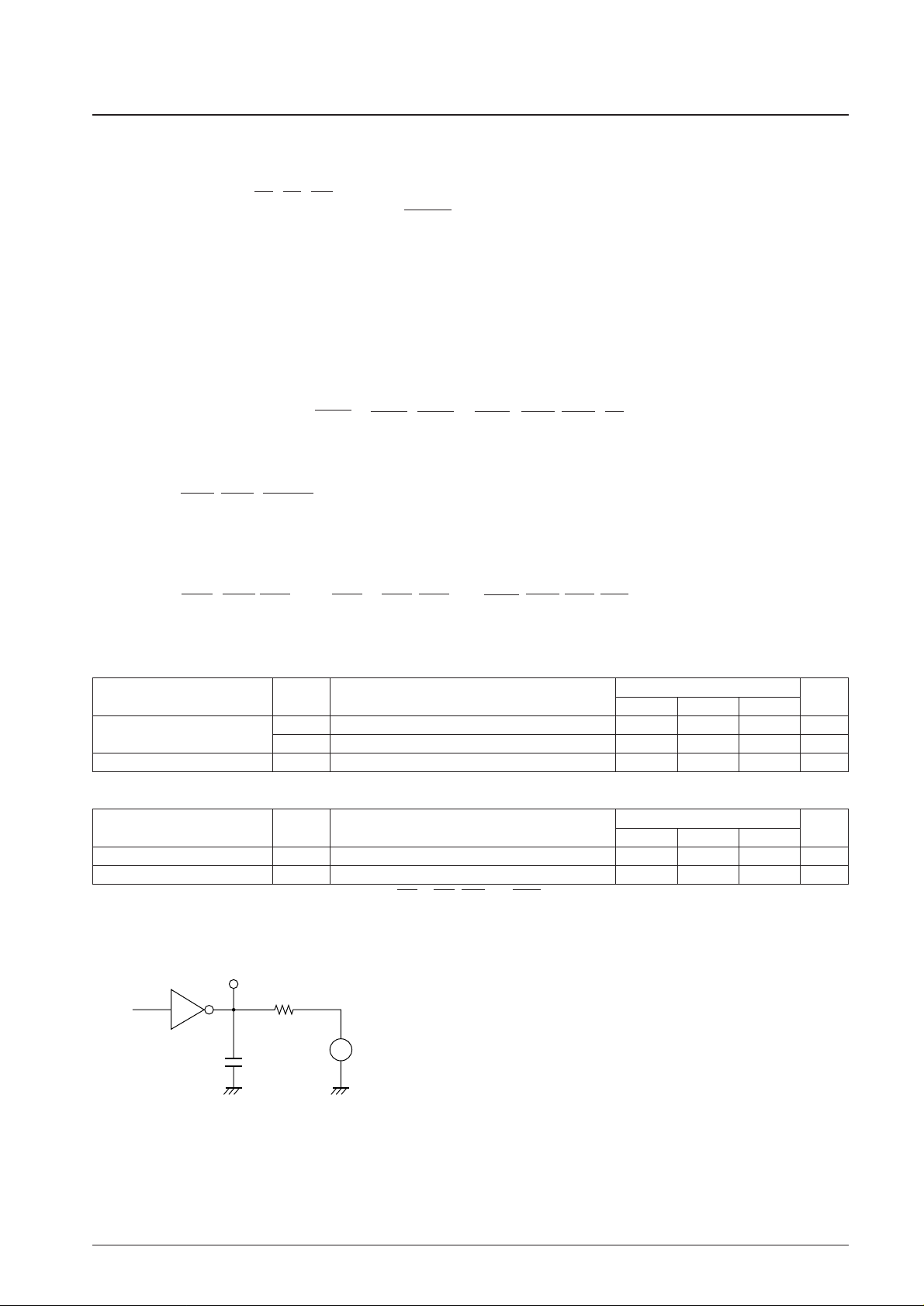

SCSI Pin Input Characteristics

Active Negation Output Characteristics

Note: The active negation output characteristics only applies to DB0 to DB7, REQ, and DBPB

Rise Time Test Circuit

No. 6614-3/12

LC898023K

SCSI

Driver

TP

47

Ω±

5%

15pF±5%

2.5V

+

–

A13188

Parameter Symbol Conditions

Ratings

Unit

min typ max

Input threshold voltage

V

t + t1

VDD= 4.50 to 5.50 V 1.60 2.00 V

V

t – t1

VDD= 4.50 to 5.50 V 0.80 1.10 V

Hysteresis width ∆V

tt1

VDD= 5.0 V 0.41 0.5

Parameter Symbol Conditions

Ratings

Unit

min typ max

Output high voltage V

OH

2.5 V

Output low voltage V

OL

0.4 V

Page 4

No. 6614-4/12

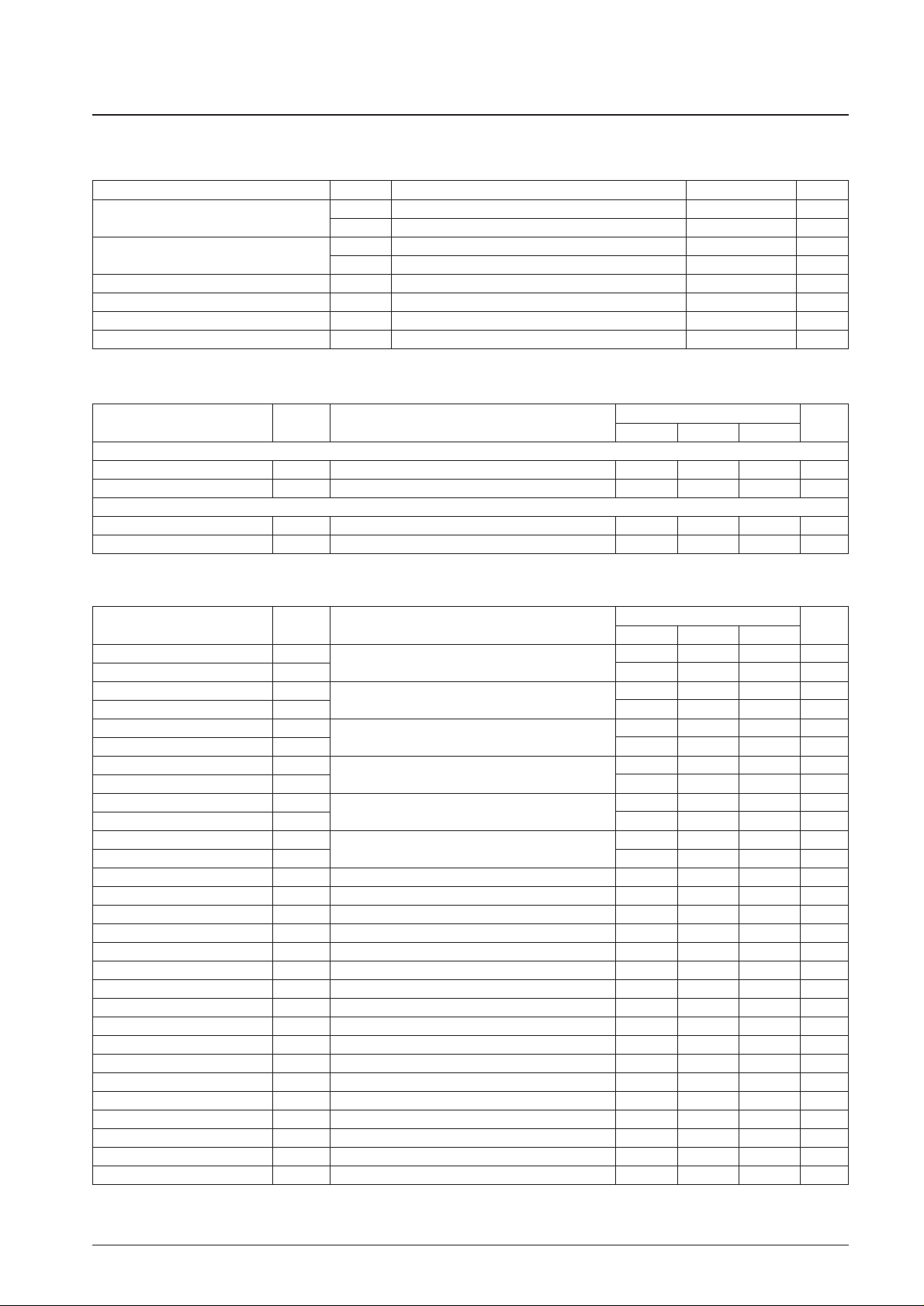

LC898023K

De-scramble &

Buffering

Address generator

Microcontroller

RAM access

Address generator

Address generator

ECC & EDC

SCSI I/F Block

Address generator

Data output input I/F

Bus

Arbiter

&

DRAM

controller

External

Buffer

DRAM

Each Block

Bus control

signal

Each Block

Register

R0-R87

CD-DSP I/F

& SYNC

Detector

Digital Servo

&

CIRC EnDec

HOST

Micro

controller

decoder

PLL

&

Clock

generator

*8

DAC

*9

TEST0 to 4

*13

*10

*6

*7

*3

*2

CAV-Audio

Sub-code ECC

Address generator

*1

Write Strategy

&

Link-position

*12

Sub-code I/F

de-interleve/interleve

Address generator

ATIP/CLV servo

ATIPSYNC

INT0, INT1

SWAIT

XTALCK0

XTAL0

XTALCK1

XTAL1

Each Block

SCSI Block

Data bus[0:7]

Address bus[0:21]

RAM

Data bus[0:15]

LC898023K

A13191

*1 DSLB (pin96) to FR (pin123), AD0 (pin127) to SPDO (pin142), SHOCK (pin147) to PCK2 (pin155)

*2 SUBSYNC

*3 DB0 to DB7, DBP, BSY, MSG, SEL, RST, REQ, I/O, C/D, ACK, ATN

*6 RD, WR, SUA0 to SUA7, CS

*7 D0 to D7

*8 IO0 to IO15

*9 RA0 to RA9, RAS0, RAS1, RAS2, CAS0, CAS1, OE, UWE, LWE

*10 WOBBLE, BIDATA, BICLK

*12 WRITE, SSP2/1, RAPC, WAPC, H11T0, LDH, TEST2/1, WDAT, NWDAT, EFMG

*13 LOUT, ROUT

Block Diagram

Page 5

Pin Functions

No. 6614-5/12

LC898023K

Pin type

I Input B Bidirectional pin NC Not connected

O Output P Power supply A Analog pin

Pin No. Pin name Type Pin function

1V

SS

P Digital system ground (VSS)

2 RA4 O

3 RA5 O

4 RA6 O

CD-ROM encoder/decoder DRAM address lines

5 RA7 O

6 RA8 O

7 RA9 O

8VDDP Digital system power supply (5 V)

9V

SS

P Digital system ground (VSS)

10 IO0 B

11 IO1 B

12 IO2 B CD-ROM encoder/decoder buffer RAM data lines

13 IO3 B These pins have built-in pull-up resistors.

14 IO4 B

15 IO5 B

16 V

DD

P Digital system power supply (3.3 V)

17 V

SS

P Digital system ground (VSS)

18 IO6 B

19 IO7 B

CD-ROM encoder/decoder buffer RAM data lines

20 IO8 B

These pins have built-in pull-up resistors.

21 IO9 B

22 IO10 B

23 V

SS

P Digital system ground (VSS)

24 V

DD

P Digital system power supply (3.3 V)

25 IO11 B

26 IO12 B

27 IO13 B CD-ROM encoder/decoder buffer RAM data lines

28 IO14 B

29 IO15 B

30 ATIPSYNC I ATIP SYNC detection signal

31 BIDATA B

32 BICLK B ATIP demodulator I/O signals

33 WOBBLE I

34 V

DD

P Digital system power supply (5 V)

35 V

SS

P Digital system ground (VSS)

36 ACRCNG O ATIP CRC error signal

37 WRITE I Write strategy signal control input

38 SSP2 O Servo sampling pulse output

39 SSP1 O Servo sampling pulse output

40 RAPC O Laser control sampling pulse output

41 WAPC O Laser control sampling pulse output

42 H11T0 O Running OPC sampling pulse

Continued on next page.

Page 6

No. 6614-6/12

LC898023K

Continued from preceding page.

Pin No. Pin name Type Pin function

43 LDH O Recording laser diode control signal output

44 V

DD

P Digital system power supply (3.3 V)

45 V

SS

P Digital system ground (VSS)

46 ATEST3 O Analog block test output

47 ATEST1 O Analog block test output

48 WDAT O Recording laser diode control signal output

49 NWDAT O Recording laser diode control signal output (WDAT inverted)

50 V

DD

P Analog system power supply (3.3 V)

51 V

SS

P Analog system ground (VSS)

52 V

DD

P Digital system power supply (5 V)

53 V

SS

P Digital system ground (VSS)

54 R1 I

55 VCNT1 I

Write strategy analog signals

56 MDC1 I

57 PD1 O

58 SWAIT O Wait signal to the microcontroller

59 INT0 O

Interrupt request signal outputs to the microcontroller

60 INT1 O

These are open-drain outputs with built-in pull-up resistors.

61 D0 B

62 D1 B

63 D2 B

Microcontroller data signal lines

64 D3 B

These pins have built-in pull-up resistors.

65 D4 B

66 D5 B

67 D6 B

68 V

DD

P Digital system power supply (5 V)

69 V

SS

P Digital system ground (VSS)

70 D7 B Microcontroller data signal line

71 SUA0 I

72 SUA1 I

73 SUA2 I

74 SUA3 I

Command register selection address

75 SUA4 I

76 SUA5 I

77 SUA6 I

78 SUA7 I

79 CS I Chip select signal input from the microcontroller

80 RD I Data read signal from the microcontroller

81 WR I Data write signal from the microcontroller

82 TEST0 I Test pin. This pin must be tied to V

SS

.

83 VCNT I VCO control voltage

84 R I VCO bias resistor connection

85 PD O Charge pump output

86 V

DD

P Analog system power supply (3.3 V)

87 V

SS

P Analog system ground (VSS)

88 TEST1 I Test pin. This pin must be tied to V

SS

.

89 RESET I Reset input

90 XTALCK0 I Crystal oscillator circuit input (33.8688 MHz)

Continued on next page.

Page 7

No. 6614-7/12

LC898023K

Continued from preceding page.

Pin No. Pin name Type Pin function

91 XTAL0 O Crystal oscillator circuit output

92 ROUT O D/A converter output

93 V

SS

P Analog system ground (VSS)

94 V

DD

P Analog system power supply (5 V)

95 LOUT O D/A converter output

96 DSLB O SLC PWM output

97 SLCIST1 I

EFM slice level setting input

98 SLCIST2 I

99 V

SS

P Analog system ground (VSS)

100 V

DD

P Analog system power supply (3.3 V)

101 SLCO0 O

102 SLCO1 O EFM slice level output

103 SLCO2 O

104 V

DD

P Digital system power supply (5 V)

105 V

SS

P Digital system ground (VSS)

106 SLCO3 O EFM slice level output

107 EFMIN I

EFM input

108 EFMIN2 I

109 TEST4 I Test pin. This pin must be tied to V

SS

.

110 JITC O Jitter output

111 RPO O

P/N balance adjustment

112 OPP I

113 PCKISTF I Frequency comparator charge pump

114 PCKISTP I Phase comparator charge pump

115 V

SS

P Analog system ground (VSS)

116 V

DD

P Analog system power supply (3.3 V)

117 PDO O Charge pump filter

118 PDS1 O

Charge pump selection

119 PDS2 O

120 V

DD

P Digital system power supply (3.3 V)

121 V

SS

P Digital system ground (VSS)

122 PDS3 O Charge pump selection

123 FR I VCO frequency setting

124 TEST2 I Test pin. This pin must be tied to V

SS

.

125 TEST3 I Test pin. This pin must be tied to V

SS

.

126 C

SS

I Center servo input pin

127 AD0 I AD input

128 RREC I Optical signal discrimination input

129 FE I FE input

130 TE I TE input

131 VREF I VREF input

132 AD1 I AD input

133 V

SS

P Analog system ground (VSS)

134 DA0 O DA output

135 DA1 O DA output

136 DA2 O DA output

137 TDO O Tracking output

Continued on next page.

Page 8

No. 6614-8/12

LC898023K

Continued from preceding page.

Pin No. Pin name Type Pin function

138 V

DD

P Analog system power supply (5 V)

139 V

SS

P Analog system ground (VSS)

140 FDO O Focus output

141 SLDO O Sled output

142 SPDO O Spindle output

143 V

SS

P Digital system ground (VSS)

144 V

DD

P Digital system power supply (3.3 V)

145 SUBSYNC O Subcode SYNC signal

146 EFMG O EFM gate signal

147 SHOCK O Shock detection signal output

148 LOCK O PLL lock state output

149 DEF I Defect detection signal input

150 HFL I Mirror detection signal input

151 TES I TES comparator input

152 EFMO O Post-binarization EFM signal output

153 LDON O Laser control

154 FG I FG input

155 PCK2 O PCK output

156 V

DD

P Digital system power supply (5 V)

157 V

SS

P Digital system ground (VSS)

158 XTALCK1 I SCSI interface crystal oscillator circuit input (20 MHz)

159 XTAL1 O SCSI interface crystal oscillator circuit output

160 DB0 B SCSI connection

161 V

SS

P Digital system ground (VSS)

162 DB1 B

SCSI connection

163 DB2 B

164 V

DD

P Digital system power supply (5 V)

165 DB3 B

SCSI connection

166 DB4 B

167 V

SS

P Digital system ground (VSS)

168 DB5 B

169 DB6 B SCSI connection

170 DB7 B

171 V

SS

P Digital system ground (VSS)

172 V

DD

P Digital system power supply (5 V)

173 V

SS

P Digital system ground (VSS)

174 DBP B

175 ATN B SCSI connection

176 BSY B

177 V

SS

P Digital system ground (VSS)

178 ACK B

SCSI connection

179 RST B

180 V

DD

P Digital system power supply (5 V)

181 MSG B

SCSI connection

182 SEL B

183 V

SS

P Digital system ground (VSS)

184 C/D B SCSI connection

Continued on next page.

Page 9

No. 6614-9/12

LC898023K

Continued from preceding page.

Pin No. Pin name Type Pin function

185 V

SS

P Digital system ground (VSS)

186 V

DD

P Digital system power supply (5 V)

187 REQ B

SCSI connections

188 I/O B

189 V

SS

P Digital system ground (VSS)

190 V

DD

P Digital system power supply (3.3 V)

191 V

SS

P Digital system ground (VSS)

192 NC Unused

193 NC Unused

194 RAS0 O

195 RAS1 O DRAM RAS signal outputs

196 RAS2 O

197 LWE O DRAM lower write enable

198 V

DD

P Digital system power supply (3.3 V)

199 V

SS

P Digital system ground (VSS)

200 UWE O DRAM upper write enable

201 CAS0 O

DRAM CAS signal output

202 CAS1 O

203 OE O DRAM output enable

204 RA0 O

205 RA1 O

CD-ROM encoder/decoder DRAM address lines

206 RA2 O

207 RA3 O

208 V

DD

P Digital system power supply (3.3 V)

Pin Functions

<SCSI Interface Pins>

BSY, ACK, MSG, SEL, REQ, ATN, RST, I/O, C/D (input/output)

SCIS bus control.

DB0 to DB7, DBP (input/output)

SCSI data bus.

<Microcontroller Interface Pins>

CS (input)

Chip select signal from the microcontroller. The microcontroller interface is active when this pin is low.

RD, WR (input)

Connect the microcontroller read and write lines to these inputs.

SWAIT (input)

Wait signal output to the microcontroller. When accessing buffer RAM, the microcontroller must wait if this pin is

low.

SUA0 to SUA7 (input)

Internal register address lines

D0 to D7 (input)

Microcontroller data bus. These pins have built-in pull-up resistors.

INT0, INT1 (output)

Interrupt request signals output to the microcontroller. INT1 can be set to output the ATAPI interrupt by setting

INT1EN (Conf-R11 bit 7)

These are open drain outputs with built-in 80 kΩ (at room temperature, 5 V) pull-up resistors.

<Buffer RAM Pins>

I/O0 to I/O15 (input/output)

Buffer RAM data bus. These pins have built-in pull-up resistors.

RA0 to RA9 (output)

Buffer RAM address lines.

Page 10

RAS0, RAS1, RAS2 (output)

Buffer DRAM RAS outputs. Normally, RAS0 is used. However, if two 16-Mbit DRAMs are used, connect the RAS0

and RAS1 lines to the RAS pins on the DRAMs. If four 16-Mbit DRAMs are used, connect the RAS0, RAS1, RAS2,

and LWE lines to the RAS pins on the DRAMs.

CAS0, CAS1 (output)

Buffer DRAM CAS outputs. Normally, CAS0 is used. However, if two 16-Mbit DRAMs are used, connect the CAS0

output to the CAS pins on the DRAMs. If 2-CAS type DRAMs are used, connect CAS0 to UCAS and CAS1 to

LCAS.

OE (output)

Buffer RAM read output.

UWE, LWE (output)

Buffer RAM write outputs. Connect these to the corresponding pins. If 2-CAS type DRAMs are used, UWE must be

connected. (Leave LWE open.)

1. Analog Interface Pins

RREC (input)

Optical discrimination input.

FE (input)

Focus error signal input.

TE (input)

Tracking error signal input.

VREF (input)

Input for the servo system reference voltage.

AD0, AD1, AD2 (input)

A/D converter auxiliary inputs.

DA0, DA1, DA2 (input)

D/A converter auxiliary inputs.

TES (input)

TES comparator input.

TDO (output)

Tracking control signal output.

FDO (output)

Focus control signal output.

SLDO (output)

Sled control signal output.

SPDO (output)

Spindle control signal output.

2. EFM Input Block Pins

EFMIN (input)

EFM signal input.

The high-frequency components of the RF signal acquired from the RF amplifier are cut with a capacitor, and this

pin inputs that signal biased by the value of the SLCO0 to SLCO3 outputs passed through a low-pass filter.

EFMIN2 (input)

Used to change the time constant of the low-pass filter.

SLCIST1, SLCIST2 (input)

Slice level controller charge pump bias resistor connection.

SLCO0, SLCO1, SLCO2, SLCO3 (output)

Slice level controller charge pump outputs.

These levels bias the RF signal input to the EFMIN pin after being passed through a low-pass filter.

DSLB (output)

Slice level control PWM output.

EFMO (output)

Post-binarization EFM signal output. (For monitoring)

No. 6614-10/12

LC898023K

Page 11

3. EFM Clock Generation Block Pins

FR (input)

EFM reproduction PLL VCO bias resistor connection.

PDO, PDS1, PDS2, PDS3 (output)

EFM reproduction PLL lag-lead filter connection.

PCKISTF (input)

EFM reproduction PLL frequency comparator charge pump bias resistor connection.

PCKISTP (input)

EFM reproduction PLL phase comparator charge pump bias resistor connection.

RPO (output)

P/N balance adjustment.

OPP (input)

P/N balance adjustment.

PCK2 (output)

EFM reproduction bit clock output.

4. Jitter Discrimination Pins

JITC (output)

Jitter output.

5. Spindle Speed Detection Pins

FG (input)

Input for the speed monitor signal from the spindle driver.

6. Audio Interface Pins

LOUT, ROUT (output)

Left and right channel audio signal outputs.

7. RF Amplifier Interface Pins

LDON (output)

RF amplifier interface.

8. Write Strategy Pins

WRITE, SSP2/1, RAPC, WAPC, H11T0, LDH, ATEST3, 1, WDAT, NWDAT (I/O)

Write strategy signal connections.

9. ATIP Decoder Related Pins

ATIPSYNC (output)

ATIP synchronization detection signal. (For monitoring)

BIDATA, BICLK (I/O)

Input mode: Input of the biphase data and biphase clock when an external ATIP demodulator is used.

Output mode: Output of the biphase data and biphase clock when the internal ATIP demodulator is used. (For

monitoring)

WOBBLE (input)

Wobble signal is input when the internal ATIP demodulator is used.

ACRCNG (output)

Outputs the result of the ATIP decoder CRC check. (For monitoring)

No. 6614-11/12

LC898023K

Page 12

PS No. 6614-12/12

LC898023K

<Other Pins>

RESET (input)

The LC898023K reset input. A low level input resets the LC898023K.

This pin must be held low for at least 1 µs when power is first applied.

TEST4 to TEST0 (input)

Test inputs. These pins must be connected to ground.

XTALCK0 (input), XTAL0 (output)

Drive these pins at 33.8688 MHz. This signal is used, without modification, as main clock for the CD-ROM encoder

and decoder blocks, including the DRAM interface.

XTALCK1 (input), XTAL1 (output)

Main clock for the SCSI block. The LC898023K is designed so that it can operate even when the ECC and SCSI

blocks are not synchronized. Providing a 20 MHz input to the XTALCK0 and XTALCK1 pins assures that correct,

synchronized transfer at 10 Mbyte/s (20 Mbyte/s for Ultra SCSI) can be achieved. The maximum frequency that can

be used is 20 MHz.

Since both edges of the clock signal are used by Ultra SCSI, the duty ratio must be correct. Add feedback resistors on

the XTALCK1 and XTAL1 pins and take other measures as required.

R, VCNT, PDO, R1, VCNT1, PD1, MDC1 (I/O)

Clock reproduction PLL circuit pins.

SUBSYNC (output)

Subcode SYNC output signal from the CIRC encoder during recording. (For monitoring)

EFMG (output)

Outputs a high level during recording.

SHOCK (output)

Outputs a high level when a mechanical shock is detected.

LOCK (output)

Outputs a high level when the PLL circuit is locked.

DEF (input)

Inputs the defect detection signal.

HFL (input)

Inputs the mirror detection signal.

This catalog provides information as of August, 2000. Specifications and information herein are subject to

change without notice.

Specifications of any and all SANYO products described or contained herein stipulate the performance,

characteristics, and functions of the described products in the independent state, and are not guarantees

of the performance, characteristics, and functions of the described products as mounted in the customer’s

products or equipment. To verify symptoms and states that cannot be evaluated in an independent device,

the customer should always evaluate and test devices mounted in the customer’s products or equipment.

SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all

semiconductor products fail with some probability. It is possible that these probabilistic failures could

give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire,

or that could cause damage to other property. When designing equipment, adopt safety measures so

that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective

circuits and error prevention circuits for safe design, redundant design, and structural design.

In the event that any or all SANYO products (including technical data, services) described or contained

herein are controlled under any of applicable local export control laws and regulations, such products must

not be exported without obtaining the export license from the authorities concerned in accordance with the

above law.

No part of this publication may be reproduced or transmitted in any form or by any means, electronic or

mechanical, including photocopying and recording, or any information storage or retrieval system,

or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

Any and all information described or contained herein are subject to change without notice due to

product/technology improvement, etc. When designing equipment, refer to the “Delivery Specification”

for the SANYO product that you intend to use.

Information (including circuit diagrams and circuit parameters) herein is for example only; it is not

guaranteed for volume production. SANYO believes information herein is accurate and reliable, but

no guarantees are made or implied regarding its use or any infringements of intellectual property rights

or other rights of third parties.

Loading...

Loading...