Page 1

Ordering number : ENN*6842

LC8772C8B/B2B/96B/80B

8-Bit Single-Chip Microcontroller

Preliminary

Overview

The LC8772C8B, LC8772B2B LC877296B and LC877280B are 8 bit single chip microcontrollers with the following

on-chip functional blocks :

- CPU: operable at a minimum bus cycle time of 100 ns

- On-chip ROM Maximum Capacity : LC8772C8B 128K bytes

LC8772B2B 112K bytes

LC877296B 96K bytes

LC877280B 80K bytes

- On-chip RAM capacity: 2048 bytes

- LCD controller / driver

- 16 bit timer / counter (can be divided into two 8 bit timers)

- 16 bit timer / PWM (can be divided into two 8 bit timers)

- Timer fo r use as date / time clock

- Synchronous serial I/O port (with automatic block transmit / receive function)

- Asynchronous / synchronous serial I/O port

- 12-channel × 8-bit AD converter

- Small signal detector

- 14-source 10-vectored interrupt system

All of the above functions are fabricated on a single chip.

Features

(1) Read-Only Memory (ROM)

- 131072 × 8bits (LC8772C8B)

- 114688 × 8bits (LC8772B2B)

- 98304 × 8bits (LC877296B)

- 81920 × 8bits (LC877280B)

(2) Random Access Memory (RAM): 2048 × 9 bits (LC8772C8B, LC8772B2B, LC877296B, LC877280B)

(3) Minimum Bus Cycle Time: 100 ns (10 MHz)

Note: The bus cycle time indicates ROM read time.

(4) Minimum Instruction Cycle Time: 300 ns (10MHz)

CMOS IC

Ver.1.00

N2599

11901 RM (IM) SK No.6842-1/24

Page 2

LC8772C8B/B2B/96B/80B

(5) Ports

- Input/output ports

Data direction programmable for each bit individually : 26 (P1n, P30-P35, P70-P7 3, P 8n)

Data direction programmable in nibble units : 8 (P0n)

(When N-channel open drain output is selected, data can be input in bit units.)

- Input ports : 2 (XT1,XT2)

- LCD ports

Segment output : 48 (S00-S47)

Common output : 4 (COM0-COM3)

Bias terminals for LCD driver 3 (V1-V3)

Other functions

Input/output ports : 48(PAn,PBn,PCn,PDn,P En,P Fn)

Input ports : 7 (PLn)

- Oscillator pins : 2 (CF1,CF2)

- Reset pin : 1 (

RES

)

- Power supply : 6 (VSS1-3,VDD1-3)

(6) LCD controller

- Seven display modes are available (static, 1/2, 1/3, 1/4 duty × 1/2, 1/3 bias)

- Segment output and common output can be switched to general purpose input/output ports.

(7) Small signal detection (MIC signals etc)

- Counts pulses with the level which is greater than a preset value

- 2 bit counter

(8) Timers

- Timer 0: 16 bit timer / counter with capture register

Mode 0: 2 channel 8-bit timer with programmable 8 bit prescaler and 8 bit capture register

Mode 1: 8 bit timer with 8 bit programmable prescaler and 8 bit capture register + 8 bit

Counter with 8-bit capture register

Mode 2: 16 bit timer with 8 bit programmable prescaler and 16 bit capture register

Mode 3: 16 bit counter with 16 bit capture register

- Timer 1: PWM / 16 bit timer with toggle output function

Mode 0: 2 channel 8 bit timer (with toggle output)

Mode 1: 2 channel 8 bit PWM

Mode 2: 16 bit timer (with toggle output) Toggle output from lower 8 bits is also possible.

Mode 3: 16 bit timer (with toggle output) Lower order 8 bits can be used as PWM.

- Base Timer

1) The clock signal can be selected from any of the following :

Sub-clock (32.768kHz crystal oscillator), system clock, and prescaler output from timer 0

2) Interrupts of five different time intervals are possible.

(9) Serial-interface

- SIO 0: 8 bit synchronous serial interface

1) LSB first / MSB first is selectable

2) Internal 8 bit baud-rate generator (fastest clock period 4 / 3 Tcyc)

3) Consecutive automatic data communication (1-256 bits)

- SIO 1: 8 bit asynchronous / synchronous serial interface

Mode 0: Synchronous 8 bit serial IO (2-wire or 3-wire, transmit clock 2–512 Tcyc)

Mode 1: Asynchronous serial IO (half duplex, 8 data bits, 1 stop bit, baud rate 8–2048Tcyc)

Mode 2: Bus mode 1 (start bit, 8 data bits, transmit clock 2–512 Tcyc)

Mode 3: Bus mode 2 (start detection, 8 data bits, stop detection)

(10) AD converter

-8 bits × 12 channels

No.6842-2/24

Page 3

LC8772C8B/B2B/96B/80B

(11) Re mo te control receiver circuit (connecte d to P73 / INT3 / T0IN termina l)

-Noise rejection function (noise rejection filter’s time constant can be selected from 1 / 32 / 128 Tcyc)

(12) Watchdog timer

- The watching time period is determined by an external RC.

- Watchdog timer can produce interrupt or system reset

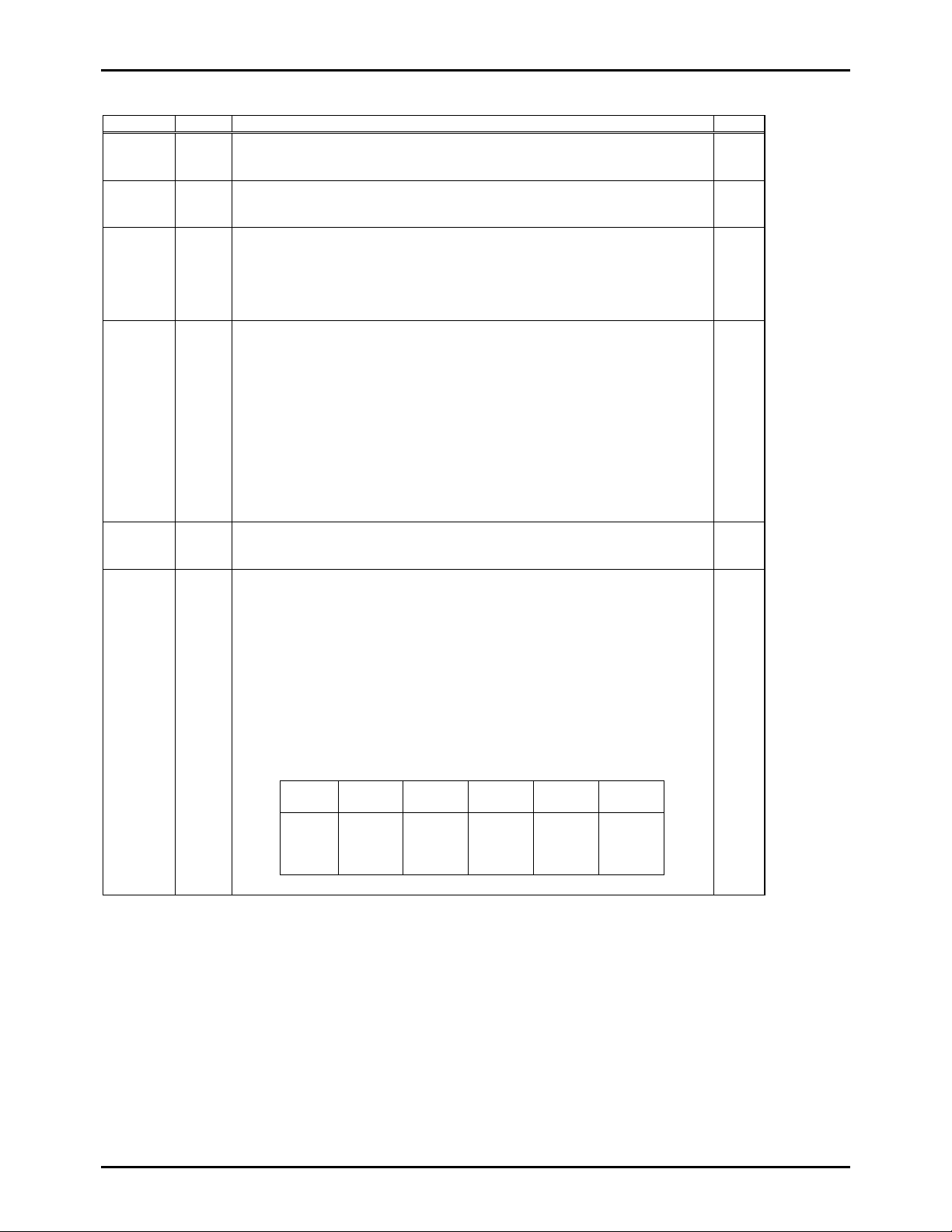

(13) Interrupts: 14 sources, 10 vectors

1) Three prior ity (low, high and highest) multiple interrupts are supported. During inte rrupt hand ling, an equal or

lower priority interrupt request is postponed.

2) If interrupt requests to two or more vector addresses occur at once, the higher priority interrupt takes precedence.

In the case of equal priority levels, the vector with the lowest address takes precedence.

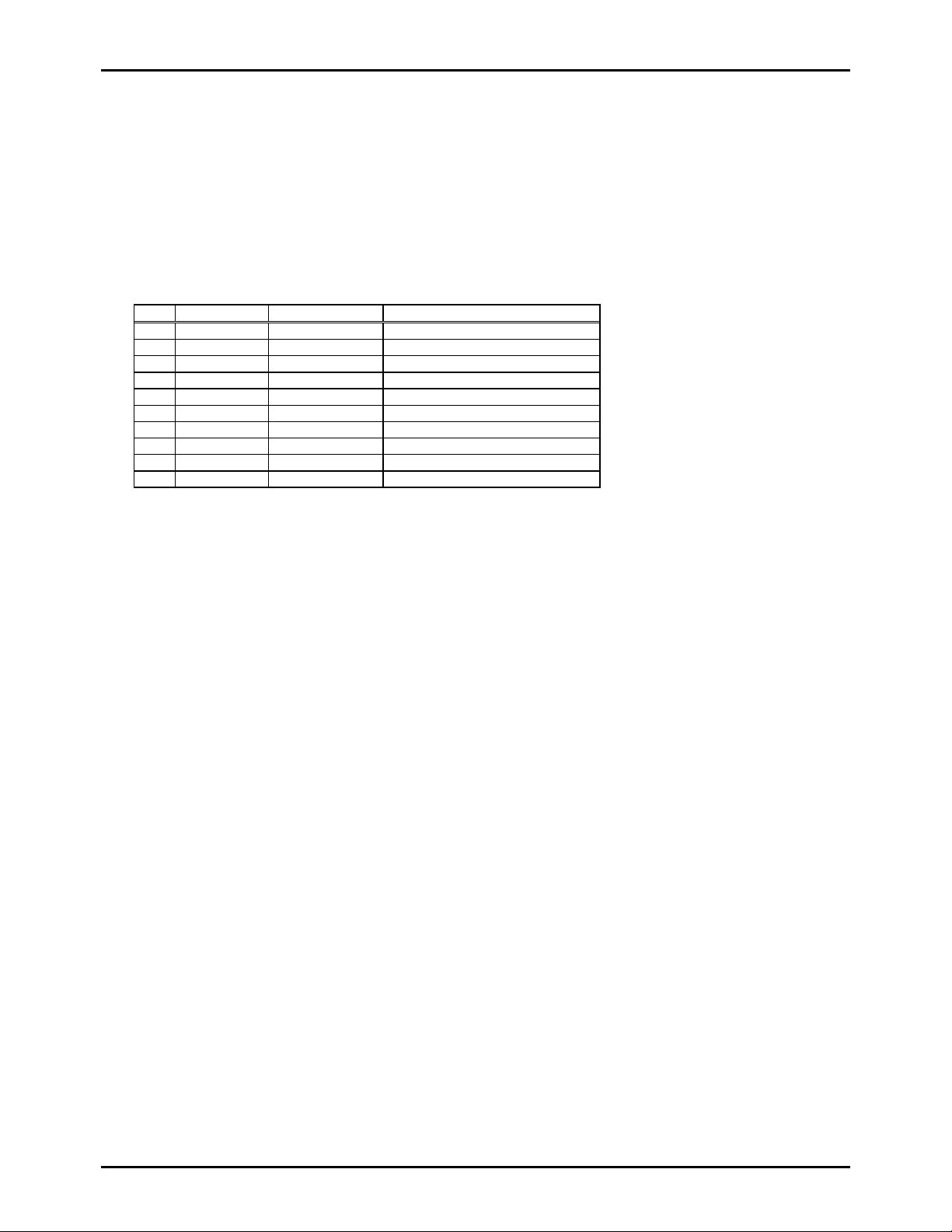

No. Vector Selectable Level Interrupt signal

1 00003H X or L INT0

2 0000BH X or L INT1

3 00013H H or L INT2/T0L

4 0001BH H or L INT3/Base timer

5 00023H H or L T0H

6 0002BH H or L T1L/T1H

7 00033H H or L SIO0

8 0003BH H or L SIO1

9 00043H H or L ADC/MIC

10 0004BH H or L Port 0

• Priority Level : X > H > L

• For equal priority levels, vector with lowest address takes precedence.

(14) Subroutine stack levels: 1024 levels max. Stack is located in RAM.

(15) Multiplication and division

- 16 bit × 8 bit (executed in 5 cycles)

- 24 bit × 16 bit (12 cycles)

- 16 bit ÷ 8 bit (8 cycles)

- 24 bit ÷ 16 bit (12 cycles)

(16) Oscillation circuits

- On-chip RC oscillation for system clock use.

- CF oscillation for system clock use. (Rf built in, Rd external)

- Crystal oscillation low speed system clock use. (Rf built in, Rd external)

(17) Standby function

- HALT mode

HALT mode is used to reduce power consumption. During the HALT mode, program execution is stopped but

peripheral circuits keep operating (some parts of serial transfer operation stop.)

1) Oscillation circuits are not stopped automatically.

2) Released by the system reset or interrupts.

-HOLD mode

HOLD mode is used to reduce power consumption. Program execution and peripheral circuits are stopped.

1) CF, RC and crystal oscillation circuits stop automatically.

2) Released by any of the following conditions.

(1) Low level input to the reset pin

(2) Specified level input to one of INT0, INT1, INT2

(3) Port 0 interrupt

No.6842-3/24

Page 4

LC8772C8B/B2B/96B/80B

-X’tal HOLD made

X’tal HOLD mode is used to reduce power consumption. Program execution is stopped.

All peripheral circuits except the base timer are stopped.

1) CF and RC oscillation circuits stop automatically.

2) Crystal oscillator operation is kept in its state at HOLD mode inception.

3) Released by any of the following conditions

(1) Low level input to the reset pin

(2) Specified level input to one of INT0, INT1, INT2

(3) Port 0 interrupt

(4) Base-timer interrupt

(18) Package

- QIP100E

- SQFP100

(19) Development tools

- Evaluation chip : LC876096

- Emulator: EVA62S + ECB876500 (Evaluation chip board) + SUB877200 + POD100QFP

or POD100SQFP (Type B)

- Flash ROM version: LC87F72C8A

No.6842-4/24

Page 5

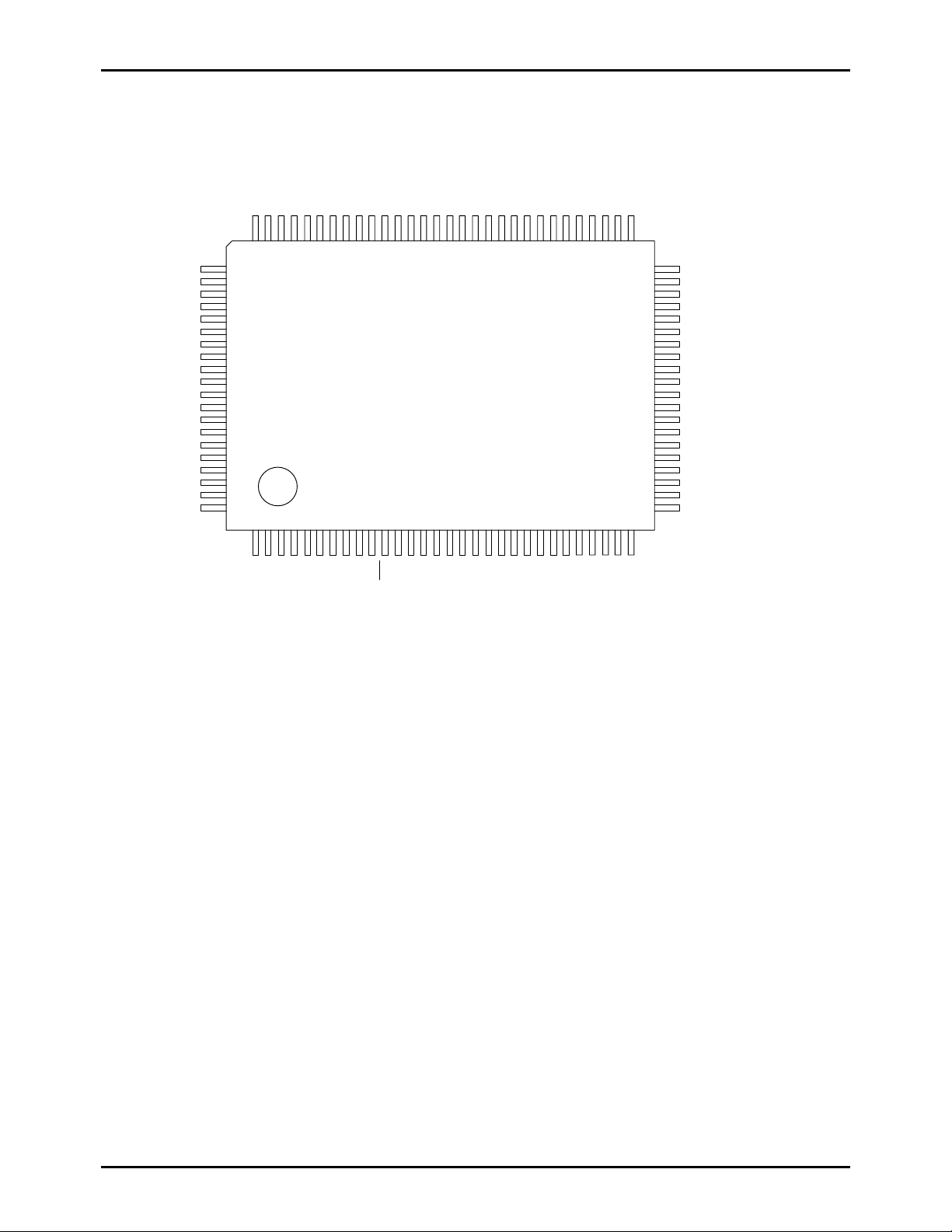

Pin Assignment

Z

V2/PL5

V1/PL4

COM0/PL0

COM1/PL1

COM2/PL2

COM3/PL3

P30

P31

VSS3

VDD3

P32

P33

P34

P35

P00

P01

P02

P03

P04

P05

LC8772C8B/B2B/96B/80B

V3/PL6

S47/PF7

S46/PF6

S45/PF5

S44/PF4

S43/PF3

S42/PF2

S41/PF1

S40/PF0

S39/PE7

S38/PE6

S37/PE5

S36/PE4

S35/PE3

S34/PE2

S33/PE1

S32/PE0

S31/PD7

S30/PD6

S29/PD5

S28/PD4

S27/PD3

S26/PD2

S25/PD1

8079787776757473727170696867666564636261605958575655545352

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

1 2 3 4 5 6 7 8 9

P06

P07

P13/SO1

P10/SO0

P12/SCK0

P11/SI0/SB0

P14/SI1/SB1

P15/SCK1

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

CF1

RES

XT1/AN10

P16/T1PWML

P17/T1PWMH/BU

CF2

VSS1

VDD1

P80/AN0

P81/AN1

P82/AN2

P83/AN3

P84/AN4

P85/AN5

XT2/AN11

P86/AN6

S24/PD0

25

P87/AN7/MICIN

VSS2

26

VDD2

S23/PC7

S22/PC6

S21/PC5

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

27

28

29

30

S0/PA0

P72/INT2/T0IN

P73/INT3/T0IN

P70/INT0/T0LCP/AN8

P71/INT1/T0HCP/AN9

S20/PC4

S19/PC3

S18/PC2

S17/PC1

S16/PC0

S15/PB7

S14/PB6

S13/PB5

S12/PB4

S11/PB3

S10/PB2

S9/PB1

S8/PB0

S7/PA7

S6/PA6

S5/PA5

S4/PA4

S3/PA3

S2/PA2

S1PA1

SANYO: QIP100E

No.6842-5/24

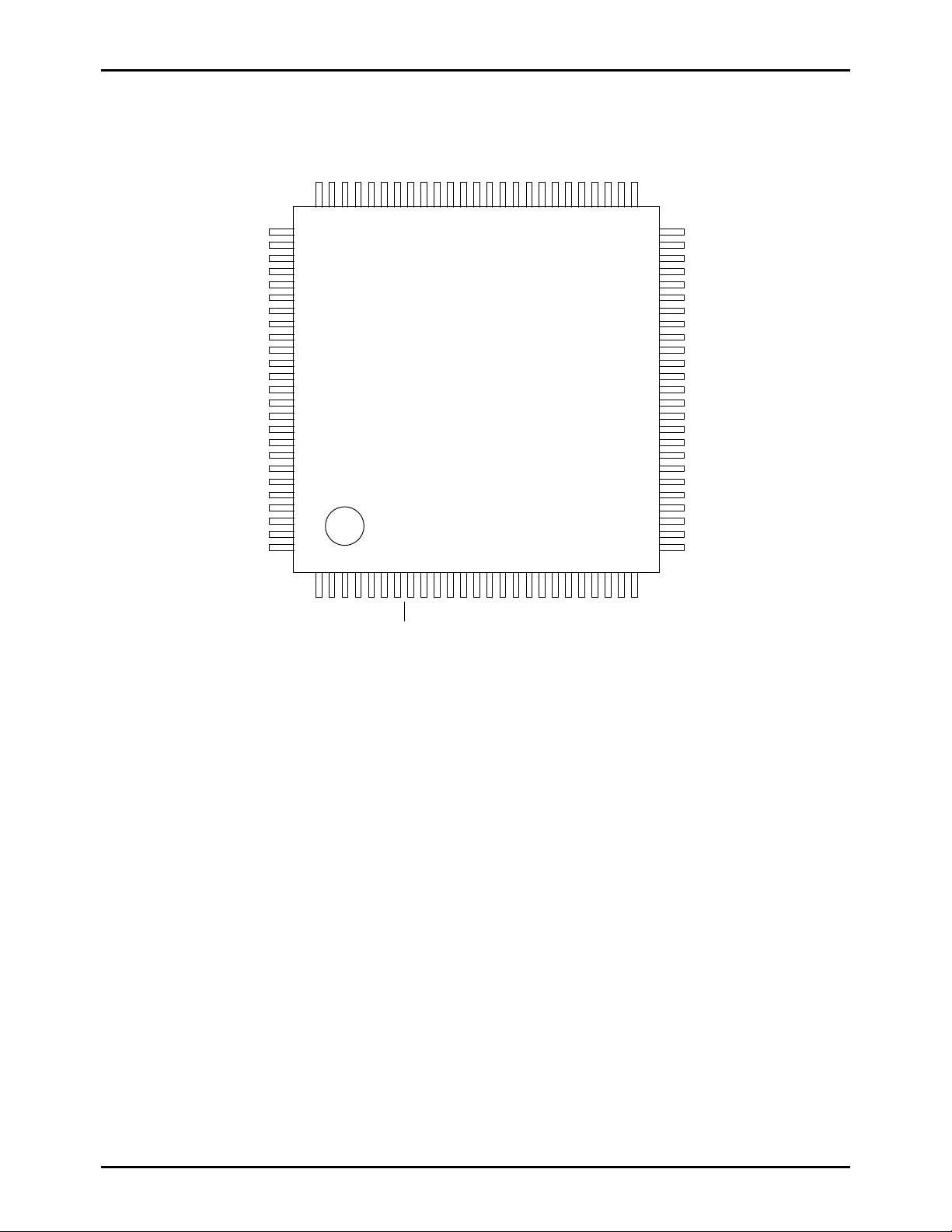

Page 6

LC8772C8B/B2B/96B/80B

L

Z

S46/PF6

S45/PF5

S44/PF4

S43/PF3

S42/PF2

S41/PF1

S40/PF0

S39/PE7

S38/PE6

S37/PE5

S36/PE4

S35/PE3

S34/PE2

S33/PE1

S32/PE0

S31/PD7

S30/PD6

S29/PD5

S28/PD4

S27/PD3

S26/PD2

S25/PD1

S24/PD0

VSS2

VDD2

S47/PF7

V3/PL6

V2/PL5

V1/PL4

COM0/PL0

COM1/PL1

COM2/PL2

COM3/PL3

P30

P31

VSS3

VDD3

P32

P33

P34

P35

P00

P01

P02

P03

P04

P05

P06

P07

P10/SO0

75747372717069686766656463626160595857565554535251

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

1 2 3 4 5 6 7 8 9

10

11

12

13

14

15

16

17

18

19

20

21

S23/PC7

50

S22/PC6

49

S21/PC5

48

S20/PC4

47

S19/PC3

46

S18/PC2

45

S17/PC1

44

S16/PC0

43

S15/PB7

42

S14/PB6

41

S13/PB5

40

S12/PB4

39

S11/PB3

38

S10/PB2

37

S9/PB1

36

S8/PB0

35

S7/PA7

34

S6/PA6

33

S5/PA5

32

S4/PA4

31

S3/PA3

30

S2/PA2

29

S1PA1

28

S0/PA0

27

P73/INT3/T0IN

26

22

23

24

25

CF1

CF2

VSS1

VDD1

P80/AN0

P81/AN1

P82/AN2

P83/AN3

P84/AN4

P85/AN5

XT2/AN11

P86/AN6

P72/INT2/T0IN

P87/AN7/MICIN

P70/INT0/T0LCP/AN8

P71/INT1/T0HCP/AN9

P15/SCK1

RES

XT1/AN10

P16/T1PWM

P17/T1PWMH/BU

P11/SI0/SB0

P12/SCK0

P13/SO1

P14/SI1/SB1

SANYO: SQFP100

No.6842-6/24

Page 7

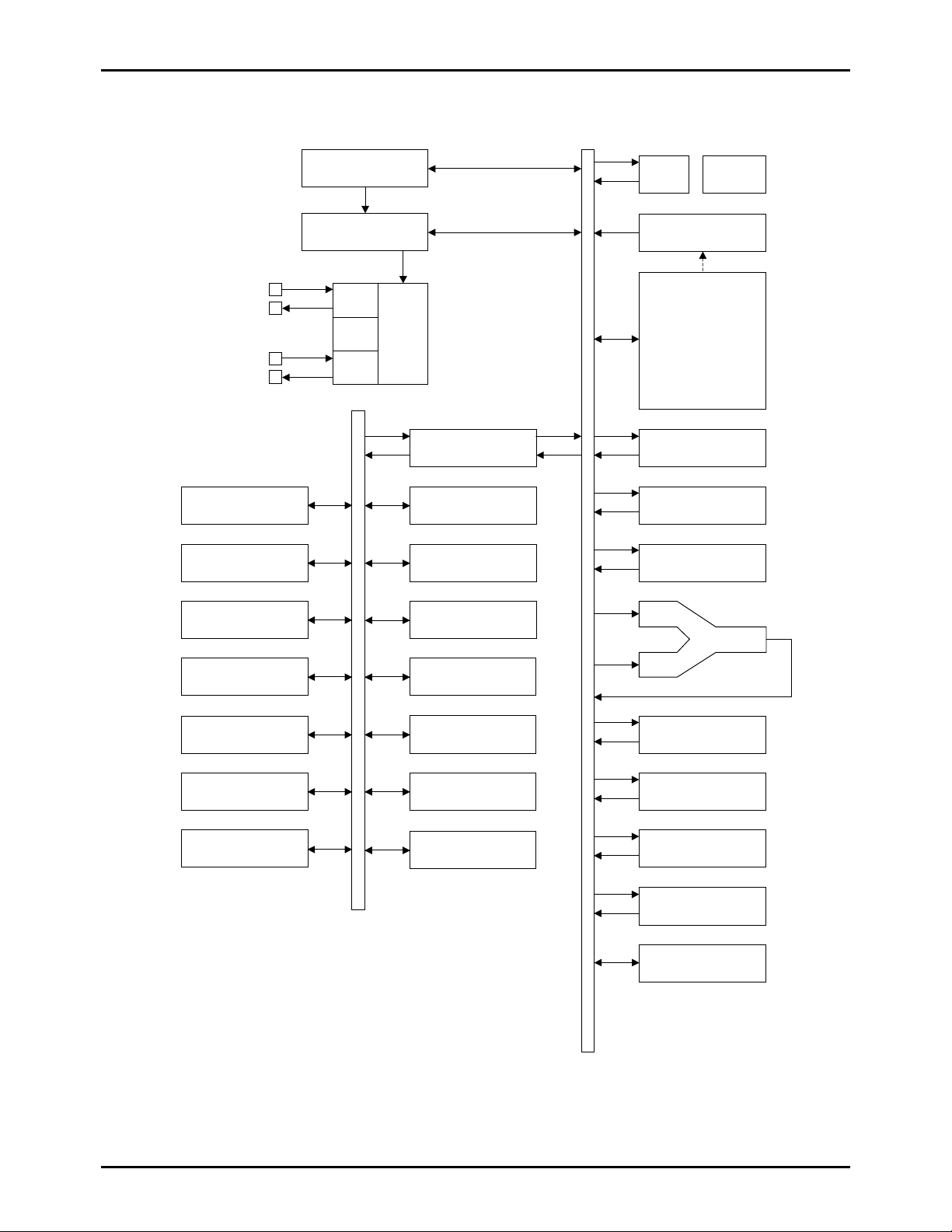

System Bl ock Diagram

j

LC8772C8B/B2B/96B/80B

Interrupt Control

IR PLA

SIO0

SIO1

Timer 0

Timer 1

Stand-by C ontr ol

CF

RC

X’tal

Clock

Generator

Bus Interface

Port 0

Port 1

Port 3

Port 7

ROM

PC

ACC

B Register

C Register

ALU

Base Timer

LCD Controller

INT0-3

Noise Re

ection Filter

Port 8

ADC

Weak Signa Detector

PSW

RAR

RAM

Stack Pointer

Watch Do g Timer

No.6842-7/24

Page 8

LC8772C8B/B2B/96B/80B

Pin Assignment

Pin name I/O Function Option

VSS1

VSS2

VSS3

VDD1

VDD2

VDD3

PORT0

P00 to P07

PORT1

P10 to P17

PORT3

P30 to P35

PORT7

P70 to P73

- • Power supply (-) No

- • Power supply (+) No

I/O • 8bit input/output port

• Data direction programmable in nibble units

• Use of pull-up resistor can be specified in nibble units

• Input for HOLD release

• Input for port 0 interrupt

I/O • 8bit input/output port

• Data direction pr ogrammable for each bit

• Use of pull-up resistor can be specified for each bit individ ually

• Other pin functions

P10 SIO0 data output

P11 SIO0 data input or bus input/output

P12 SIO0 clock input/output

P13 SIO1 data output

P14 SIO1 data input or bus input/output

P15 SIO1 clock input/output

P16: Timer 1 PWML output

P17: Timer 1 PWMH output/Buzzer output

I/O • 6bit Input/output port

• Data direction can b e specified for each bit

• Use of pull-up resistor can be specified for each bit individ ually

• 4bit Input/output port

I/O

• Data direction can be specified for each bit

• Use of pull-up resistor can be specified for each bit individ ually

• Other func tions

P70: INT0 input/HOLD release input/Timer0L capture input/output for watchdog

timer

P71: INT1 input/HOLD release input/Timer0H capture input

P72: INT2 input/HOLD release input/timer 0 event input/Timer0L capture input

P73: INT3 input(noise rejection filter attached)/timer 0 event input/Timer0H capture

input

AD input port: AN8(P70), AN9(P71)

• Interrupt detection selection

Yes

Yes

Yes

No

INT0

INT1

INT2

INT3

Rising Falling Rising and

Yes

Yes

Yes

Yes

Yes

Yes

Yes

Yes

falling

No

No

Yes

Yes

H level L level

Yes

Yes

No

No

Yes

Yes

No

No

No.6842-8/24

Page 9

LC8772C8B/B2B/96B/80B

Pin name I/O Function description Option

PORT8

P80 to P87

S0/PA0 to

S7/PA7

S8/PB0 to

S15/PB7

S16/PC0 to

S23/PC7

S24 /PD0to

S31/PD7

S32/PE0 to

S39/PE7

S40/PF0 to

COM0/PL0 to

V1/PL4 to

RES

XT1 I • Input for 32.768kHz crystal oscillation

XT2 I/O • Output for 32.768kHz crystal oscillation

CF1 I Input terminal for ceramic oscillator No

CF2 O Output terminal for ceramic oscillator No

S47/PF7

COM3/PL3

V3/PL6

I/O • 8bit Input/output port

• Input/out put can be specified for each bit individ ually

• Other func tions:

AD input port: AN0 to AN7

Small signal detector input port: MICIN(P87)

I/O • Seg ment output for LC D

• Can be used as general purpose input/output port (PA)

I/O • Seg ment output for LC D

• Can be used as general purpose input/output port (PB)

I/O • Seg ment output for LC D

• Can be used as general purpose input/output port (PC)

I/O • Seg ment output for LCD

• Can be used as general purpose input/output port (PD)

I/O • Seg ment output for LC D

• Can be used as general purpose input/output port (PE)

I/O • Seg ment output for LC D

• Can be used as general purpose input/output port (PF)

I/O • Com mon output for LCD

• Can be used as general purpose input port (PL)

I/O • LCD output bias power supply

• Can be used as general purpose input port (PL)

I Reset terminal No

• Other func tions:

General purpose input port

AD input port: AN10

• When not in use, connect to VDD1

• Other func tions:

General purpose input port

AD input port: AN11

• When not in use, set to oscillation mode and leave open

No

No

No

No

No

No

No

No

No

No

No

No.6842-9/24

Page 10

LC8772C8B/B2B/96B/80B

Port Configuration

Port form and pull-up resistor options are shown in the following table.

Port status can be read even when port is set to output mode.

Terminal Option applies to: Options Output Form Pull-up resistor

P00 to P07 each bit

P70 – None Nch-open drain Programmable

P71 to P73 – None CMOS Programmable

P80 to P87 – None Nch-open drain None

1 CMOS Programmable

2 Nch-open drain None

1 CMOS Programmable P10 to P17 each bit

2 Nch-open drain Programmable

1 CMOS Programmable P30 to P35 each bit

2 Nch-open drain None

(Note 1)

S0/PA0 to

S47/PF7

COM0/PL0 to

COM3/PL3

V1/PL4 to

V3/PL6

XT1 – None Input only None

XT2 – None Output for 32.768kHz crystal

– None CMOS Programmable

– None Input only None

– None Input only None

None

oscillation

Note 1 Attachment of Port0 programmable pull-up resistors is controllable in nibble units (P00-03, P04-07).

* Note 1: Connect as follows to reduce noise on VDD.

VSS1, VSS2 and VSS3 must be connected together and grounded.

*Note 2 : The power supply for the internal memory is VDD1 but it uses the VDD3 as the power supply for ports. When the

VDD3 is not backed up, the port level does not become “H” even if the port latch is in the “H” level. Therefore,

when the VDD3 is no t backed up and the p ort latc h is “H” level , the por t level is unstabl e in the HOLD mode, and

the back up time becomes shorter because the through current runs from VDD to GND in the input buffer.

If VDD3 is not backed up, output “L” by the program or pull the port to “L” by the external circuit in the HOLD

mode so that the port level becomes “L” level and unnecessary current consumption is prevented.

Power

supply

Back-up capacitors *2

LSI

VDD1

VDD2

VDD3

VSS3

VSS2 VSS1

No.6842-10/24

Page 11

LC8772C8B/B2B/96B/80B

V

1. Absolute Maximum Ratings at Ta=25°C and VSS1=VSS2=VSS3=0V

Parameter Symbol Pins Conditions

Supply voltage VDDMAX VDD1,VDD2,VDD3 VDD1=VDD2

Supply voltage

for LCD

Input voltage VI Port L

Input/Output

voltage

High

level

output

current

Low

level

output

current

consumption

Operating

temperature

range

Storage

temperature

range

Peak

output

current

Total

output

current

Peak

output

current

Total

output

current

VLCD V1/PL4, V2/PL5,

VI0(1) •Port0, 1, 3, 7, 8

IOPH(1) Port 0, 1, 3 •CMOS output

IOPH(2) Port 7 1 ,72,73 Current at each pin -3

IOPH(3) Port A, B, C, D, E, F Current at each pin -5

IOAH(1)

Σ

IOAH(2)

Σ

IOAH(3)

Σ

IOAH(4)

Σ

IOAH(5)

Σ

IOPL(1) Port 0, 1, 32-3 5 Current at each pin 20

IOPL(2) Port 30, 31 Current at each pin 30

IOPL(3) Port 7,8 Current at each pin 5

IOPL(4) Port A, B,C, D, E, F Current at each pin 15

IOAL(1)

Σ

IOAL(2)

Σ

IOAL(3)

Σ

IOAL(4)

Σ

IOAL(5)

Σ

Pdmax

Topg -30 70

Tstg -55 125

V3/PL6

XT1,XT2,CF1,

•Port A, B, C, D, E, F

Port 0, 1, 32, 33, 34, 35 Total of all pins -40

Port 30, 31 Total of all pins -10

Port 7 Total of all pins -5

Port A, B, C Total of all pins -25

Port D, E, F Total of all pins -25

Port 0, 1, 32, 33, 34, 35 Total of all pins 60

Port 30, 31 Total of all pins 60

Port 7,8 Total of all pins 20

Port A,B,C Total of all pins 40

Port D, E, F Total of all pins 40

QIP100E Maximum power

SQFP100

RES

=VDD3

VDD1=VDD2

=VDD3

-0.3 VDD+0.3

-0.3 VDD+0.3

selected

•Current at each pin

Ta = -30 to +70°C

Ratings

[V]

DD

min. typ. max.

-0.3 +7.0

-0.3 VDD

-10

unit

V

mA

mW

C

°

No.6842-11/24

Page 12

LC8772C8B/B2B/96B/80B

2. Recommended Operating Range at Ta=-30°C to +70°C, VSS1=VSS2=VSS3=0V

Parameter Symbol Pins Conditions

Operating

supply voltage

range

VDD(1)

VDD(2)

VDD1=VDD2=VDD3

0.294µs ≤ t

200µs

0.735µs ≤ t

CYC

CYC

200µs

Supply voltage

range in Hold

mode

Input high

voltage

VHD VDD1 Keep RAM and

register data in

HOLD mode.

VIH(1) •Port 0, 3, 8

Output disable 2.5 to 6.0 0.3VDD

•Port A,B,C,D,E,F,L

VIH(2) •Port 1

Output disable 2.5 to 6.0 0.3VDD

•Port 71,72, 73

•P70 port input/interrupt

VIH(3) P87 small signal input Output disable 2.5 to 6.0 0.75VDD VDD

VIH(4) Port 70

Output disable 2.5 to 6.0 0.9VDD VDD

Watchdog timer

Input low

voltage

VIH(5)

XT1, XT2, CF1,

VIL(1) •Port 0, 3, 8

•Port A,B,C,D,E,F,L

VIL(2) •Port 1

RES

2.5 to 6.0 0.75VDD VDD

Output disable 2.5 to 6.0 VSS 0.15VDD

Output disable 2.5 to 6.0 VSS 0.1VDD

•Port 71,72, 73

•P70 port input/interrupt

VIL(3) Port 87 small signal input Output disable 2.5 to 6.0 VSS 0.25VDD

VIL(4) Port 70

Output disable 2.5 to 6.0 VSS 0.8VDD

Watchdog timer

VIL(5)

CYC

t

XT1,XT2,CF1,

RES

2.5 to 6.0 VSS 0.25VDD

cycle time

External system

clock

frequency

FEXCF(1) CF1

•system clock

divider :1/1

•external clock

DUTY = 50±5%

≤

≤

Ratings

[V]

VDD

min. typ. max.

4.5 6.0

2.5 6.0

2.0 6.0

+0.7

+0.7

4.5 to 6.0 0.294 200 Operation

2.5 to 6.0 0.735 200

4.5 to 6.0 0.1 10 •CF2 open

2.5 to 6.0 0.1 4

VDD

VDD

+0.4

+0.4

-1.0

unit

V

s

µ

MHz

•CF2 open

4.5 to 6.0 0.2 20

•system clock

divider :1/2

2.5 to 6.0 0.2 8

Continued/

No.6842-12/24

Page 13

LC8772C8B/B2B/96B/80B

Parameter Symbol Pins Conditions

Oscillation

frequency

range

(Note 1)

FmCF(1) CF1, CF2 10MHz ceramic resonator

oscillation

Refer to figure 1

FmCF(2) CF1, CF2 4MHz ceramic resonator

oscillation

Refer to figure 1

FmRC RC oscillation 2.5 to 6.0 0.3 1.0 2.0

Ratings

VDD[V] min. typ. max.

4.5 to 6.0 10

2.5 to 6.0 4

unit

MHz

FsX’tal XT1, XT2 32.768kHz crystal resonator

oscillation

Refer to figure 2

2.5 to 6.0 32.768 kHz

(Note 1) The port value of oscillation circuit is shown in table 1 and table 2.

No.6842-13/24

Page 14

LC8772C8B/B2B/96B/80B

3. Electrical Characteristics at Ta=-30°C to +70°C, VSS1=VSS2=VSS3=0V

Parameter Symbol Pins Conditions

High level

input

current

IIH(1) •Port 0,1,3,7,8

•Port A,B,C,D,E,F,L

•Output disabled

•Pull-up resister OFF.

•VIN=VDD

(including OFF state leak

current of the output Tr.)

IIH(2)

RES

VIN=VDD 2.5 to 6.0 1

IIH(3) XT1,XT2 When configured as an input

port

VIN=VDD

IIH(4) CF1 VIN=VDD 2.5 to 6.0 15

Low level

input

current

IIH(5) P87/AN7/MICIN

small signal input

IIL(1) •Port 0,1,3,7,8

•Port A,B,C,D,E,F,L

VIN=V

(V

+0.5V

BIS

: Bias voltage)

BIS

•Output disabled

•Pull-up resister OFF.

•VIN=VSS

(including OFF state leak

current of the output Tr.)

IIL(2)

RES

VIN=VSS 2.5 to 6.0 -1

IIL(3) XT1,XT2 When configured as an input

port

VIN=VSS

IIL(4) CF1 VIN=VSS 2.5 to 6.0 -15

High level

output

voltage

Low level

output

voltage

LCD output

voltage

regulation

IIL(5) P87/AN7/MICIN

small signal input

VOH(1) IOH=-1.0mA 4.5 to 6.0 VDD-1

VOH(2)

Port 0,1,3: CMOS

output option

VOH(3) Port 7 IOH=-0.4mA 2.5 to 6.0 VDD-1

VOH(4) IOH=-1.0mA 4.5 to 6.0 VDD-1

Port A,B,C,D,E,F

VOH(5)

VOL(1) IOL=10mA 4.5 to 6.0 1.5

Port 0,1,3

VOL(2)

VOL(3) Port 30,31 IOL=30mA 4.5 to 6.0 1.5

VOL(4) IOL=1mA 4.5 to 6.0 0.4

Port 7,8

VOL(5)

VOL(6) IOL=8mA 4.5 to 6.0 1.5

Port A,B,C,D,E,F

VOL(7)

VODLS S0–S47 I0=0mA

VIN=V

(V

-0.5V

BIS

: Bias voltage)

BIS

IOH=-0.1mA 2.5 to 6.0 VDD-0.5

IOH=-0.1mA 2.5 to 6.0 VDD-0.5

IOL=1.6mA 2.5 to 6.0 0.4

IOL=0.5mA 2.5 to 6.0 0.4

IOL=1.4mA 2.5 to 6.0 0.4

VLCD, 2/3VLC D,

1/3VLCD level output

Refer to figure 8

VODLC COM0–COM3 I0=0mA

VLCD, 2/3VLC D, 1/2VLCD

1/3VLCD level output

Refer to figure 8

resistor

RLCD(1) Resistance per one

bias resistor

RLCD(2) •Resistance per one

Refer to figure 8 2.5 to 6.0 60 LCD bias

Refer to figure 8 2.5 to 6.0 30

bias resistor

•1/2R mode

Ratings

VDD[V] min. typ. max.

2.5 to 6.0 1

2.5 to 6.0 1

2.5 to 6.0 4.2 8.5 15

2.5 to 6.0 -1

2.5 to 6.0 -1

2.5 to 6.0 -15 -8.5 -4.2

2.5 to 6.0 0 ±0.2

2.5 to 6.0 0 ±0.2

Continued/

unit

A

µ

V

kΩ

No.6842-14/24

Page 15

LC8772C8B/B2B/96B/80B

Parameter Symbol Pins Conditions

pull-up

Rpu •Port 0,1,3,7

•Port A,B,C,D,E,F

VOH=0.9VDD

MOS Tr.

voltage

VHIS(1) •Port 1,7

•

RES

VHIS(2) Port 87 small signal

2.5 to 6.0

2.5 to 6.0

input

Pin

capacitance

CP All pins •All other terminals connected

to VSS.

•f=1MHz

•

=25°C

T

Input

sensitivity

Vsen Port 87 small signal

input

a

2.5 to 6.0 0.12VDD Vpp

Ratings

VDD[V] min. typ. max.

4.5 to 6.0 15 40 70 Resistance of

unit

kΩ

2.5 to 4.5 25 70 150

0.1VDD

0.1VDD

V

Hysterisis

2.5 to 6.0 10 pF

No.6842-15/24

Page 16

LC8772C8B/B2B/96B/80B

4. Serial Input/Output Characteristics at Ta=-30°C to +70°C, VSS1=VSS2=VSS3=0V

Parameter Symbol Pins Conditions

Cycle time tSCK(1) 4/3

SCK0(P12) Refer to figure 6 2.0 to 6.0

Ratings

VDD[V] min. typ. max.

unit

CYC

t

pulse width

pulse width

Input clock

Cycle time tSCK(2)

Low level

pulse width

High level

pulse width

Cycle time tSCK(3)

Serial clock

pulse width

pulse width

Output clock

Cycle time tSCK(4)

Low level

pulse width

High level

pulse width

Data set-up time

Data hold time t

Serial input

Output delay

time

Serial output

tSCKL(1)

tSCKLA(1)

tSCKH(1)

tSCKHA(1)

tSCKL(2)

tSCKH(2)

tSCKL(3)

tSCKLA(2)

tSCKH(3)

tSCKHA(2)

tSCKL(4)

tSCKH(4)

sDI

t

hDI

tdDO SO0(P12),

SCK1(P15) Refer to figure 6 2.5 t o 6.0

SCK0(P12) •CMOS output

SCK1(P15) •CMOS output

SI0(P10),

SI1(P13),

SB0(P11),

SB1(P14)

SO1(P15),

SB0(011),

SB1(P14)

•Refer to figure 6

•Refer to figure 6

•Measured with resp ect

to SI0CLK leading

edge.

•Refer to figure 6

•When Port is open

drain:

Time delay form

SIOCLK trailing edge

to the SO data chan ge

•Refer to figure 6

2/3 Low level

2/3

2/3 High level

3

2

1

1

2.5 to 6.0

2.5 to 6.0

4.5 to 6.0 0.03

2.5 to 6.0 0.1

4.5 to 6.0 0.03

2.5 to 6.0 0.1

4.5 to 6.0 1/3

2.5 to 6.0 1/3

4/3

1/2 Low level

3/4

1/2 High level

2

2 tCYC

1/2

1/2

tCYC

+0.05

tCYC

+0.25

tSCK

tSCK

s

µ

No.6842-16/24

Page 17

LC8772C8B/B2B/96B/80B

5. Pulse Input Conditions at Ta=-30°C to +70°C, VSS1=VSS2=VSS3=0V

Parameter Symbol Pins Conditions

pulse width

tPIH(1)

tPIL(1)

tPIH(2)

tPIL(2)

tPIH(3)

tPIL(3)

tPIH(4)

tPIL(4)

tPIL(5)

tPIL(5)

tPIL(6)

INT0(P70),

INT1(P71),

INT2(P72)

INT3(P73)

(Noise rejection ratio

is 1/1.)

INT3(P73)

(Noise rejection ratio

is 1/32.)

INT3(P73)

(Noise rejection ratio

is 1/128.)

MICIN(P87) •Condition that signal is

RES

•Condition that reset is

•Condition that interrupt is

accepted

•Condition that event input

to timer 0 is accepted

•Condition that interrupt is

accepted

•Condition that event input

to timer 0 is accepted

•Condition that interrupt is

accepted

•Condition that event input

to timer 0 is accepted

•Condition that interrupt is

accepted

•Condition that event input

to timer 0 is accepted

accepted to small signal

detection counter.

accepted

Ratings

VDD[V] min. typ. max.

2.5 to 6.0 1

2.5 to 6.0 2

2.5 to 6.0 64

2.5 to 6.0 256

2.5 to 6.0 1

2.5 to 6.0 200

unit

CYC

t

High/low level

s

µ

6. AD Converter Characteristics at Ta=-30°C to + 70°C, VSS1=VSS2=VSS3=0V

Parameter Symbol Pins Conditions

Resolution N 3.0 to 6.0 8 bit

Absolute precision ET (Note2) 3.0 to 6.0

Conversion time TCAD

Analog input

voltage range

current

VAIN 3.0 to 6.0 VSS VDD V

IAINH VAIN=VDD 3.0 to 6.0 1 Analog port input

IAINL

AN0(P80)

–AN7(P87)

AN8(P70)

AN9(P71)

AN10(XT1)

AN11(XT2)

AD conversion time

= 32 × tCYC

(ADCR2=0)

(Note 3)

AD conversion time

= 64 × tCYC

(ADCR2=1)

(Note 3)

VAIN=VSS 3.0 to 6.0 -1

Ratings

VDD[V] min. typ. max.

4.0 to 6.0 15.62

(tCYC=

0.488µs)

3.0 to 6.0 23.52

(tCYC=

0.735µs)

4.5 to 6.0 18.82

(tCYC=

0.294µs)

3.0 to 6.0 47.04

(tCYC=

0.735µs)

±

97.92

(tCYC=

3.06µs)

97.92

(tCYC=

3.06µs)

97.92

(tCYC=

1.53µs)

97.92

(tCYC=

1.53µs)

1.5

unit

LSB

µ

s

µ

A

(Note 2) Abso lute precision does not include quantizing error (±1/2 LSB).

(Note 3) Conversion time means time from executing AD conversion instruction to loading complete digital value to register.

No.6842-17/24

Page 18

LC8772C8B/B2B/96B/80B

7. Current Consumption Characteri stics at Ta=-30°C to +70°C, VSS1=VSS2=VSS3=0V

Parameter Symbol Pins Conditions

Current consumption

during normal

operation

(Note 4)

IDDOP(1) •FmCF=10MHz

IDDOP(2) •CF1=20MHz external

IDDOP(3) 4.5 to 6.0

IDDOP(4)

VDD1=

VDD2=

VDD3

Ceramic resonator

oscillation

•FsX’tal=32.768kHz

crystal oscillation

•System clock: CF

10MHz oscillation

•Internal RC oscillation

stopped.

•Divider : 1/1

clock

•FsX’tal=32.768kHz

crystal oscillation

•System clock: CF1

oscillation

•Internal RC oscillation

stopped.

•Divider :1/ 2

•FmCF=4M Hz Ceramic

resonator oscillation

•FsX’tal=32.768kHz

crystal oscillation

•System clock: CF

4MHz oscillation

•Internal RC oscillation

stopped.

•Divider :1/ 1

Ratings

VDD[V] min. typ. max

4.5 to 6.0

4.5 to 6.0

2.5 to 4.5

unit

mA

IDDOP(5) 4.5 to 6.0

IDDOP(6)

IDDOP(7) 4.5 to 6.0

IDDOP(8)

•FmCF=0Hz (No

oscillation)

•FsX’tal=32.768kHz

crystal oscillation

•System clock: RC

oscillation

•Divider :1/ 2

•FmCF=0Hz (No

oscillation)

•FsX’tal=32.768kHz

crystal oscillation

•System clock:

32.768kHz

•Internal RC oscillation

stopped.

•Divider :1/ 2

2.5 to 4.5

2.5 to 4.5

A

µ

Continued/

No.6842-18/24

Page 19

LC8772C8B/B2B/96B/80B

V

V

V

Parameter Symbol Pins Conditions

Current

consumption

during

HALT mode

(Note 4)

IDDHALT(1) HALT mode

IDDHALT(2) HALT mode

DD1=

•FmCF=10MHz Cera mic

DD2=

DD3

resonator oscillation

•FsX’tal=32.768kHz

crystal oscillation

•System clock :

CF 10MHz oscillation

•Internal RC oscillation

stopped.

•Divider: 1/1

•CF1=20MHz for extern al

clock

•FsX’tal=32.768kHz

crystal oscillation

•System clock :

CF1 oscillation

•Internal RC oscillation

stopped.

•Divider :1/2

Ratings

VDD[V] min. typ. max.

4.5 to 6.0

4.5 to 6.0

unit

mA

IDDHALT(3) 4.5 to 6.0

IDDHALT(4)

IDDHALT(5) 4.5 to 6.0

IDDHALT(6)

IDDHALT(7) 4.5 to 6.0

IDDHALT(8)

HALT mode

HALT mode

HALT mode

•FmCF=4M Hz Ceramic

resonator oscillation

•FsX’tal=32.768kHz

crystal oscillation

•System clock :

CF 4MHz oscillation

•Internal RC oscillation

stopped.

•Divider: 1/1

•FmCF=0Hz

(Oscillation stop)

•FsX’tal=32.768kHz

crystal oscillation

•System clock :

RC oscillation

•Divider: 1/2

•FmCF=0Hz

(Oscillation stop)

•FsX’tal=32.768kHz

crystal oscillation

•System clock : 32.768kHz

•Internal RC oscillation

stopped.

•Divider: 1/2

2.5 to 4.5

2.5 to 4.5

2.5 to 4.5

A

µ

Continued/

No.6842-19/24

Page 20

LC8772C8B/B2B/96B/80B

Parameter Symbol Pins Conditions

during HOLD mode

during Date/time

clock HOLD mode

IDDHOLD(1) 4.5 to 6.0 Current consumption

IDDHOLD(2)

IDDHOLD(3) 4.5 to 6.0 Current consumption

IDDHOLD(4)

VDD1 HOLD mode

•CF1=VDD or open

(when using external

clock)

VDD1 Date/time clock HOLD

mode

•CF1=VDD or open

(when using external

clock)

•FmX’tal=32.768kHz

crystal oscillation

Ratings

VDD[V] min. typ. max.

2.5 to 4.5

2.5 to 4.5

(Note 4) The currents through the output transistors and the pull-up MOS transistors are ignored.

unit

A

µ

No.6842-20/24

Page 21

LC8772C8B/B2B/96B/80B

Main system clock osci llation circuit characteristics

The characteristics in the table bellow is based on the following conditions:

1. Use the standard evaluation board SANYO has provided.

2. Use the peripheral parts with indicated value externally.

3. The peripheral parts value is a recommended value of oscillator manufacturer

Table 1. Main system clock oscillation circuit cha racteris tics using ceramic resonator

Frequency Manufacturer Oscillator

10MHz

4MHz

Circuit parameters

C1 C2 Rd1

supply voltage

Operating

range

Oscillation

stabilizing time

typ max

Notes

The oscillation stabilizing time is a period until the oscillation becomes stable after VDD becomes higher than

minimum operating voltage. (Refer to Figure4)

Subsystem clock osci lla tion circuit characteristics

The characteristics in the table bellow is based on the following conditions:

1. Use the sta nda rd evaluation board SANYO has pro vided.

2. Use the peripheral parts with indicated value externally.

3. The peripheral parts value is a recommended value of oscillator manufacturer

Table 2. Subsystem clock oscillation circuit characteristics using crysta l oscil lator

Frequency Manufacturer Oscillator

32.768kHz

Circuit parameters

C3 C4 Rf Rd2

Operating

supply voltage

range

Oscillation

stabilizing time

typ max

Notes

The oscillation stabilizing time is a period until the oscillation becomes stable after executing the instruction which starts the

sub-clock oscillation or after releasing the HOLD mode. (Refer to Figure4)

(Notes) • Since the circuit pattern affects the oscillation frequency, place the oscillation-related parts as close to

the oscillation pins as possible with the shortest possible pattern length.

CF2 CF1

Rd1

Rf

XT2 XT1

Rd2

C1

CF

C2

C3

X’tal

C4

Figure 1 Ceramic oscillation circuit Figure 2 Crystal oscillation circuit

No.6842-21/24

Page 22

LC8772C8B/B2B/96B/80B

,

,

0.5VDD

Figure 3 AC timing measurement point

Power Supply

RES

Reset time

Internal RC

Resonator oscillation

CF1

CF2

XT1

XT2

tmsCF

tmsXtal

Operation mode

Unfixed

Rese t Instruction exe cution mod e

Reset time and oscillation stable time

HOLD release signal

Without HOLD

Release signal

HOLD release signal VALID

Internal RC

Resonator oscillation

tmsCF

CF1,CF2

tmsXtal

XT1,XT2

Operation mode

HOLD HALT

HOLD release signal and oscillation stable time

Figure 4 Oscillation stabilizing time

VDD

VDD limit

0V

No.6842-22/24

Page 23

SIOCLK

DATAIN

DATAOUT

SIOCLK

DATAIN

DATAOUT

SIOCLK

DATAIN

DATAOUT

LC8772C8B/B2B/96B/80B

VDD

RES

R

(Note)

RES

RES

C

Select CRES and RRES value to assure that at least 200µs

reset time is gene rated after the VDD b ecomes highe r than

the minimum operating voltage.

Figure 5 Reset circuit

DI0 DI1 DI2 DI3 DI4 DI5 DI6 DI7 DI8

DO0 DO1 DO2 DO3 DO4 DO5 DO6 DO7 DO8

Data RAM

transmission period

(only SIO0)

tSCK

tSCKL tSCKH

tsDI thDI

tdDO

Data RAM

transmission period

(only SIO0)

tSCKLA tSCKHA

tsDI thDI

tdDO

Figure 6 Serial input / output wave form

No.6842-23/24

Page 24

LC8772C8B/B2B/96B/80B

(

tPIL tPIH

Figure 7 Pulse input timing

VDD

SW : ON/OFF(programmable)

4R

SW : ON

VLCD=VDD)

2R

R

R

VLCD

2/3VLCD

1/2VLCD

1/3VLCD

2R

GND

Figure 8 LCD bias resistor

PS

No.6842-24/24

Loading...

Loading...