SANYO LB1875 Datasheet

Ordering number : EN6002

6.2

36

1

0.8

17.9

2.7

0.3

(4.9)

1.3

10.5

0.65

0.25

0.55

7.9

2.25

2.5max

0.1

LB1875

Monolithic Digital IC

LB1875

Polygon Mirror Motor Predriver IC

Overview

The LB1875 is a predriver IC for polygon mirror

motors. By using a driver array or discrete transistors (FETs) at the output, motor drive with high

rotation precision is possible. PAM drive or direct

PWM drive can be selected for the output to realize

high-efficiency control with minimum power loss.

Features

• Three-phase bipolar drive

• Direct PWM drive (bottom side) or PAM drive selectable

• PLL speed control circuit

• PWM oscillator

• Quartz oscillator

• Frequency divider

• FG with Schmitt comparator

• FG input single edge, dual edge selector circuit

• Integrating amplifier

• Phase lock detector output

• Current limiter

• Motor lock protection

• Thermal protection

• Forward/reverse circuit

• 5V regulator output

Package Dimensions

unit: mm

3235-HSOP36

[LB1875]

SANYO : HSOP36

Any and all SANYO products described or contained herein do not have specifications that can handle

applications that require extremely high levels of reliability, such as life-support systems, aircraft's

control systems, or other applications whose failure can be reasonably expected to result in serious

physical and/or material damage. Consult with your SANYO representative nearest you before using

any SANYO products described or contained herein in such applications.

SANYO assumes no responsibility for equipment failures that result from using products at values that

exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other

parameters) listed in products specifications of any and all SANYO products described or contained

herein.

SANYO Electric Co., Ltd. Semiconductor Business Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

D0898RM(KI)

No. 6002-1/17

LB1875

Specifications

Maximum Ratings at Ta = 25°C

Parameter Symbol Conditions Ratings Unit

Maximum supply voltage V

Output current I

Allowable power dissipation Pd max IC only 0.9 W

Operating temperature Topr °C

Storage temperature Tstg °C

Operation Conditions at Ta = 25°C

Parameter Symbol Conditions Ratings Unit

Maximum supply voltage V

Output current I

5V regulated output current I

Voltage applied at LD pin V

LD pin output current I

Voltage applied at PWM pin V

PWM pin output current I

max 14.5 V

CC

max 30 mA

O

with substrate (114.3 x 76.1 x 1.6 mm3,

glass exposy)

2.1 W

– 20 to +80

– 55 to +150

1 8 to 13.5 V

CC

V

2

When shorted between V

CC

O

REG

LD

LD

PWM

PWM

CC

and V

REG

4.5 to 5.5 V

20 mA

0 to –20 mA

0 to 13.5 V

0 to 10 mA

0 to 13.5 V

0 to 20 mA

2.4

With substrate

2.1

2.0

1.6

1.2

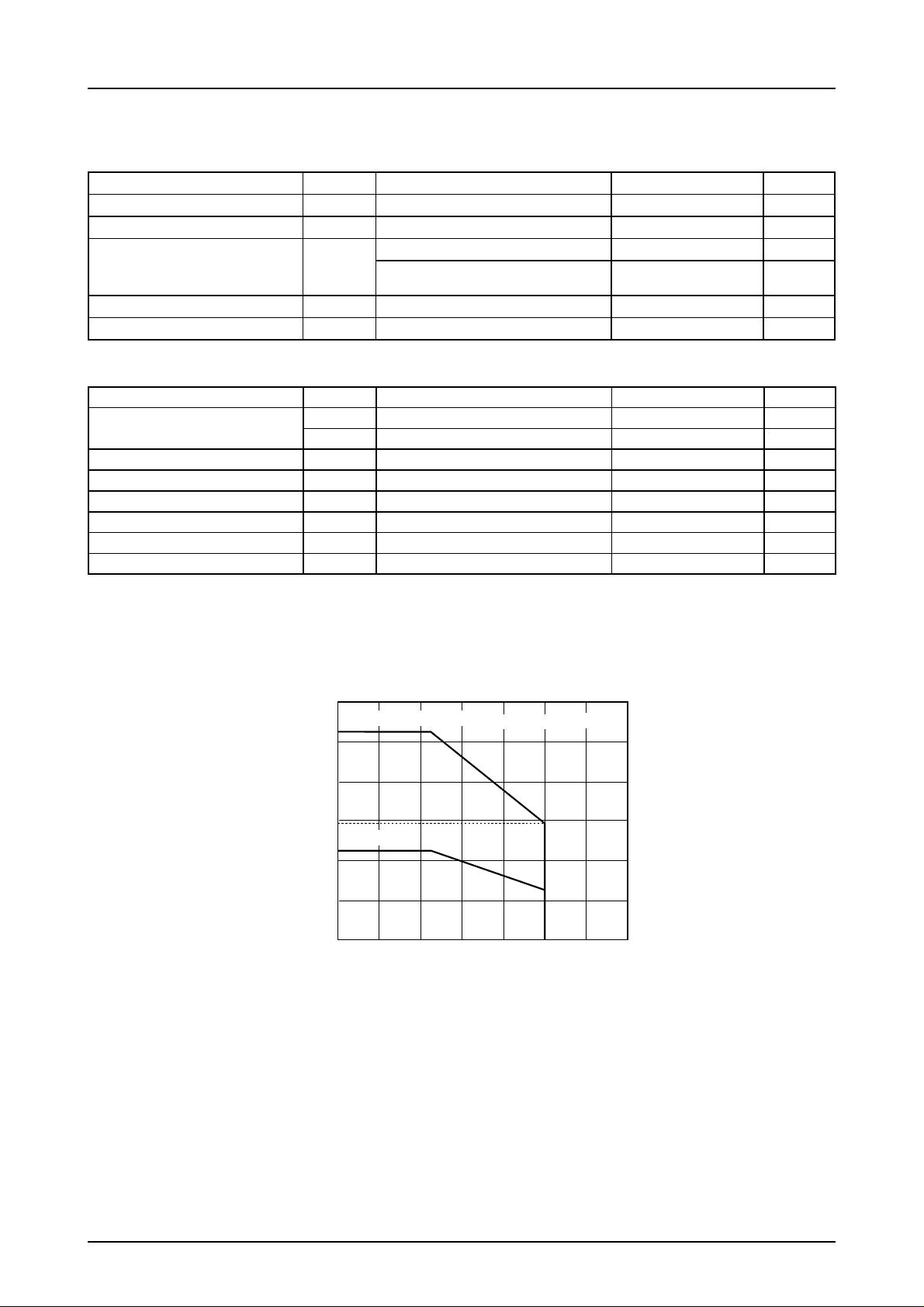

Pd max – Ta

(114.3 x 76.1 x 1.6 mm, glass exposy)

IC only

0.9

0.8

0.4

Power dissipation, Pd max – W

0

0–20 20 40 60 80 100 120

Ambient temperature, Ta – ˚C

1.18

0.5

No. 6002-2/17

LB1875

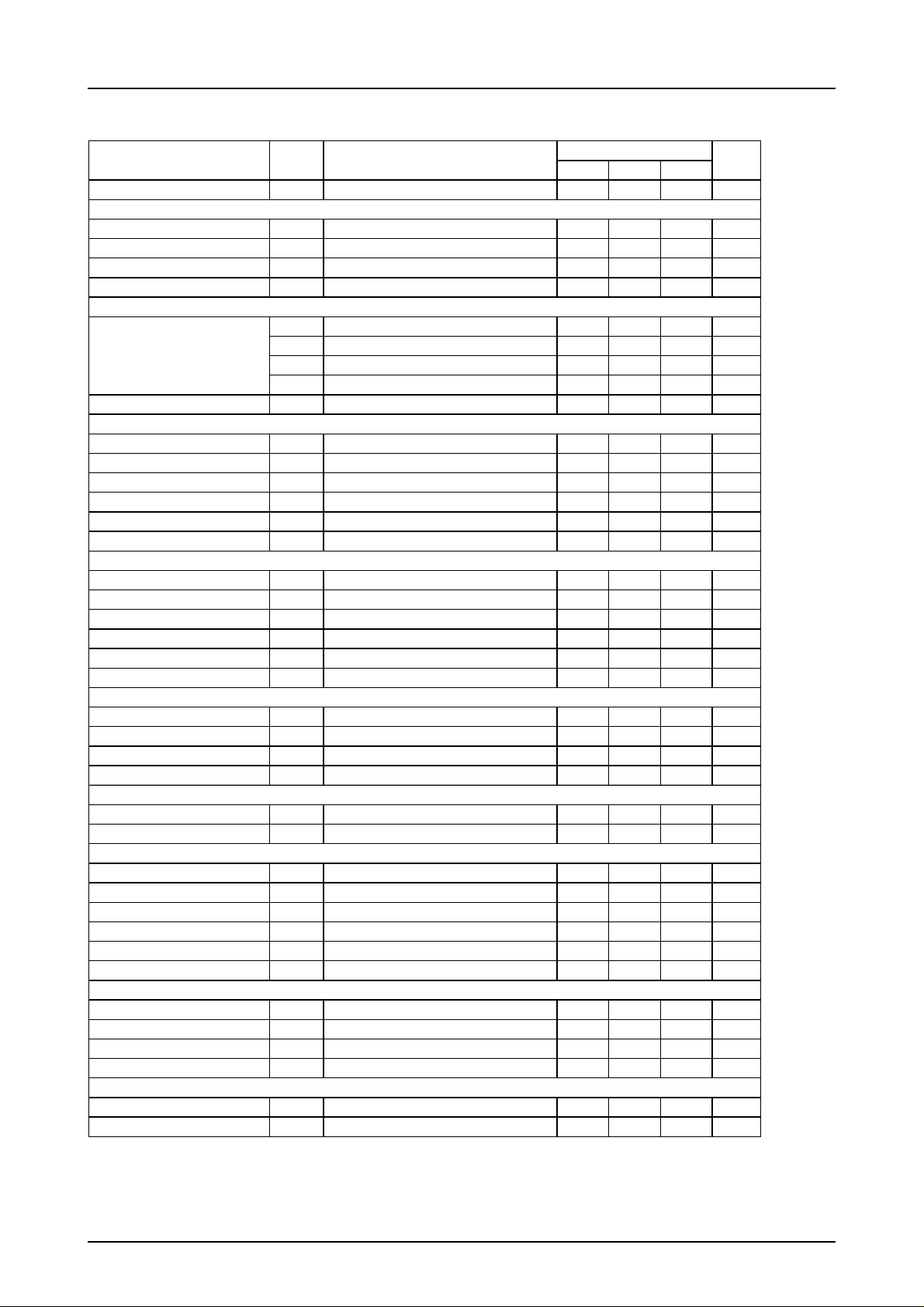

Electrical Characteristics at Ta = 25°C, VCC = 12V

Parameter

Power supply current I

Symbol Conditions

CC

[5V regulated output ]

Output fluctuation V

Voltage fluctuation ∆V

Load fluctuation ∆V

Temperature coefficcient ∆V

REG

1VCC=8 to 13.5V 40 100

REG

2IO=0 to –15 mA 20 100

REG

3 Design target value 0

REG

[Output Section]

Output saturation voltage V

(sat)1-1 UH, VH, WH "L" level, IO=50 µA 0.1 0.3 V

O

Vo(sat)1-2 UH, V H, WH " L" lev el, IO=10 mA 0.9 1.1 V

(sat)2 UH, VH, W H "L" leve l, IO=20 mA VCC–0.9 VCC–1.1 V

V

O

V

(sat)3 UL, VL, WL, IO=20 mA 0.2 0.4 V

O

Output leak current I

leak UL, VL, WL 10 µA

O

[Hall amplifier]

Input bias current I

Same-phase input voltage range V

(HA) –4 –1 µA

HB

ICM

Hall input sensitivity 30 mV

Hysteresis width ∆VIN(HA) 8 14 24 mV

Input voltage L->H V

Input voltage H->L V

SLH

SHL

[FG/Schmitt comparator section]

Input bias current I

Same-phase input voltage range V

Input sensitivity V

(FGS) –4 –1 µA

B

(FGS) 0 VCC–2.0 V

ICM

(FGS) 30 mV

IN

Hysteresis width ∆VIN(FGS) Design target value 8 14 24 mV

Input voltage L->H V

Input voltage H->L V

(FGS) Design target value 7 mV

SLH

(FGS) Design target value –7 mV

SHL

[PWM oscillator]

Output High level voltage V

(OSC) 2.7 3.0 3.3 V

OH

Output Low level voltage VOL(OSC) 1.5 1.8 2.1 V

Oscillator frequency f(OSC) C=2200 pF 30 kHz

Amplitude V(OSC) 1.0 1.2 1.4 V

[PWM output]

Output saturation voltage V

(PWM) I

OL

Output leak current IL(PWM) VO=V

=15 mA 0.9 2.0 V

PWM

CC

[CSD oscillator ]

Output High level voltage V

(CSD) 2.5 2.8 3.1 V

OH

Output Low level voltage VOL(CSD) 0.55 0.85 1.15 V

External C charge current I

External C discharge current I

Oscillator frequency f

Amplitude V

1 –13 –10 –7 µA

CHG

2 7 10 13 µA

CHG

C=0.068 µF 35 Hz

CSD

CSD

[Phase comparator output]

Output High level voltage V

Output Low level voltage V

Output source current I

Output sink current I

PD

PD

=–100 µAV

PDHIOH

=100 µA 0.1 0.2 V

PDLIOH

+

VPD=V

/2 –0.6 mA

–

REG

VPD=V

/2 1.5 mA

REG

[Phase lock detector output]

Output saturation voltage V

Output leak current IL(LD) VO=V

(LD) ILD=10 mA 0.1 0.4 V

OL

CC

Ratings

min typ max

30 40

4.65 5.0 5.35

0 VCC–2.0 V

7 mV

–7 mV

10 µA

1.75 1.95 2.15 V

–0.2 V

REG

–0.1 V

REG

10 µA

Continued on next page

Unit

mV/°C

mA

V

mV

mV

P-P

P-P

P-P

P-P

No. 6002-3/17

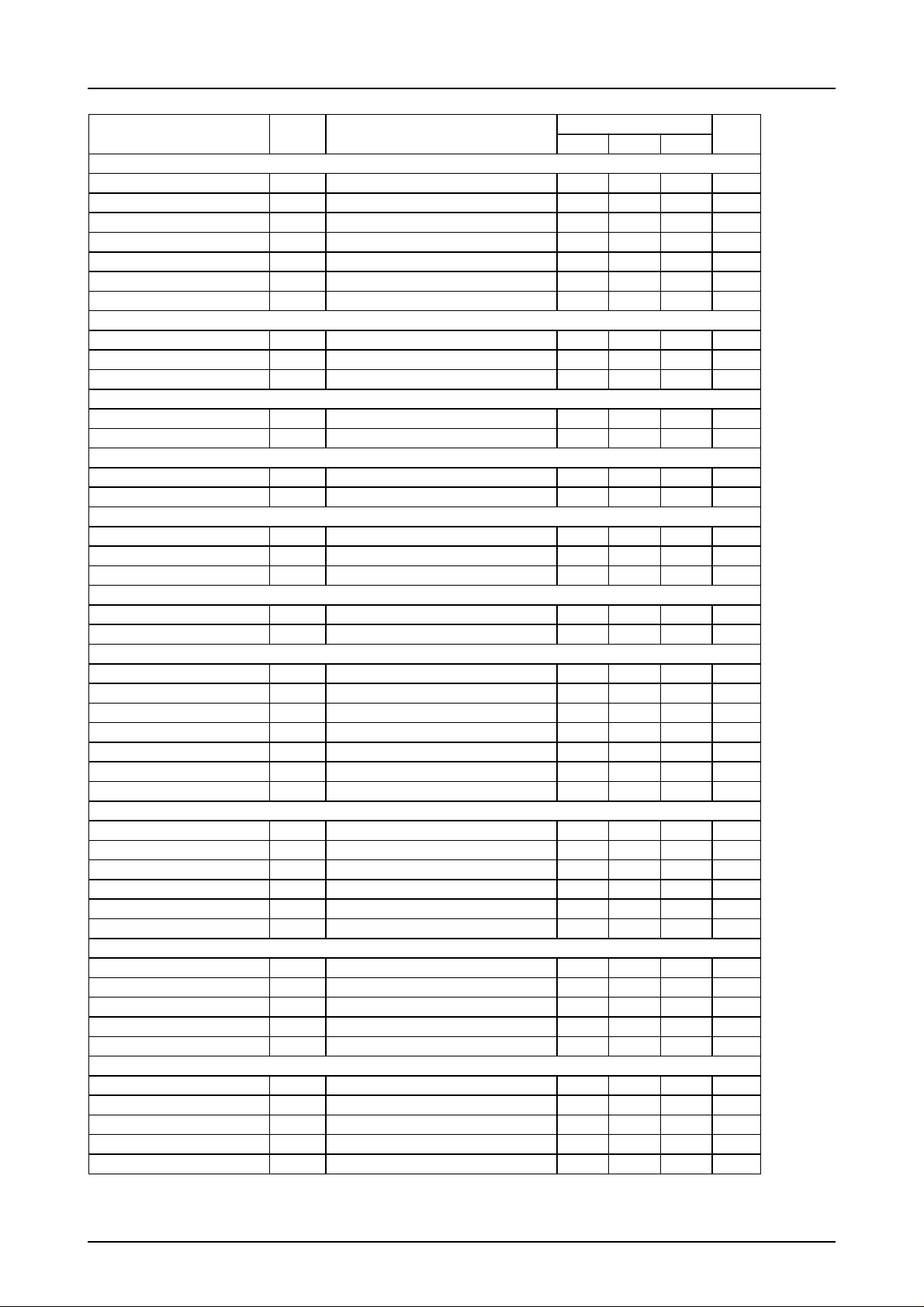

LB1875

Continued from preceding page

Parameter Symbol Conditions

[ERR amplifier]

Input offset voltage V

(ER) Design target value –10 +10 mV

IO

Input bias current IB(ER) –1 +1 µA

Ouput High level voltage V

Ouput Low level voltage V

DC bias level V

(ER) IOH = –500 µAV

OH

(ER) IOL=500 µA 0.9 1.2 V

OL

(ER) –5% V

B

[Current limiter]

Limiter voltage V

RF

[Low-voltage protection circuit]

Operation voltage V

Release voltage V

SDL

SDH

Hysteresis width ∆VSD 0.15 0.25 0.35 °C

[Thermal shutdown operation]

Termal shutdown temperature TSD Design target value (junction temperature) 150 180 °C

Hysteresis width ∆TSD Design target value (junction temperature) 30 °C

[SOFT pin]

Stop voltage V

External C discharge current I

In stop condition 3.0 3.3 3.6 V

SFT

DCHG

[Quartz oscillator]

Quartz oscillator frequency f

Low level pin voltage V

High level pin voltage V

pin]

[CLK

OUT

Output saturation voltage

Output leak current IL(CKOUT) VO=V

pin]

[CLK

IN

External input frequency f

High level input voltage V

Low level input voltage V

Input open voltage V

Hysteresis width V

High level input current I

Low level input current I

OSC

OSCLIOSC

OSCHVOSC=VOSCL

VOL(CKOUT)

I(CKIN)

IH(CKIN)

IL(CKIN

IO(CKIN)

IS(CKIN)

IH(CKIN)VCKIN=VREG

IL(CKIN)VCKIN

=–0.5 mA 1.45 V

+0.6V 0.5 mA

I

=2 mA 0.1 0.4 V

CKOUT

CC

) 0 1.5 V

V

=0V –200 –140 µA

[S/S pin]

High level input voltage V

(SS) 3.5 V

IH

Low level input voltage VIL(SS) 0 1.5 V

Input open voltage V

Hysteresis width V

High level input current I

Low level input current I

(SS) V

IO

(SS) 0.3 0.4 0.5 V

IS

(SS) VS/S=V

IH

(SS) VS/S=0V –200 –140 µA

IL

REG

[F/R pin]

High level input voltage V

(FR) 3.5 V

IH

Low level input voltage VIL(FR) 0 1.5 V

Input open voltage V

High level input current I

Low level input current I

pin]

[FG

SEL

High level input voltage

Low level input voltage

Input open voltage

High level input current

Low level input current

(FR) V

IO

(FR) VF/R=V

IH

(FR) VF/R=0V –200 –140 µA

IL

(FSEL) 3.5 V

V

IH

(FSEL) 0 1.5 V

V

IL

(FSEL) V

V

IO

(FSEL) V

I

IH

(FSEL) V

I

IL

REG

FSEL=VREG

=0V –200 –140 µA

FSEL

Ratings

min typ max

–1.2 V

REG

–0.9 V

REG

/2 V

REG

+ 5%

0.45 0.5 0.55 V

3.55 3.75 3.95 V

3.8 4.0 4.2 V

4 6 8 µA

2 10 MHz

10 µA

0.1 10 kHz

3.5 V

–0.5 V

REG

REG

REG

0.3 0.4 0.5 V

–10 0 +10 µA

REG

–0.5 V

REG

REG

–10 0 +10 µA

REG

–0.5 V

REG

REG

–10 0 +10 µA

REG

–0.5 V

REG

REG

–10 0 +10 µA

Continued on next page

Unit

V

V

V

V

V

V

V

V

No. 6002-4/17

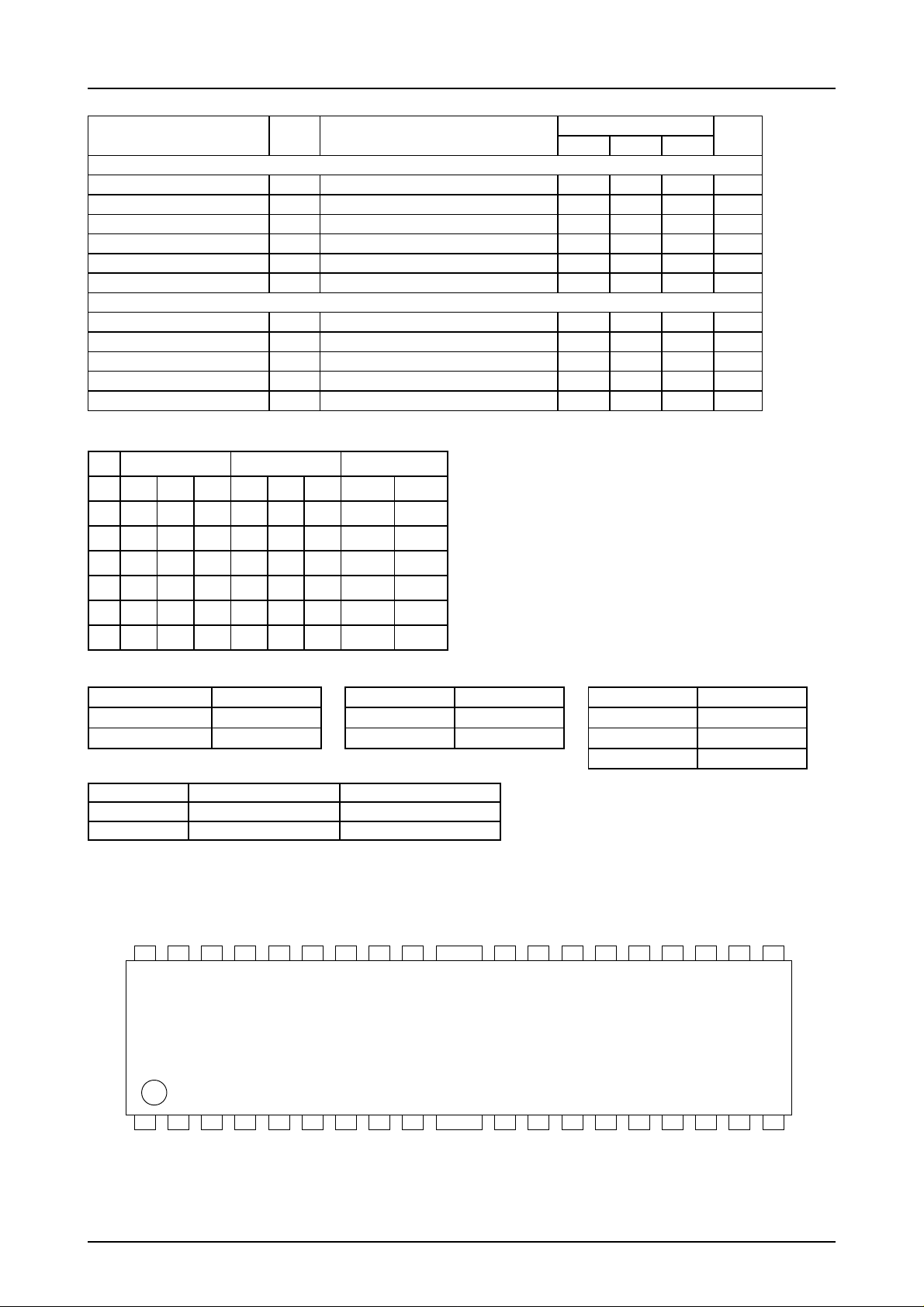

LB1875

Continued from previous page

Parameter Symbol Conditions

[CLK

pin]

SEL

High level input voltage V

Middle level input voltage VIM(CSEL) 2.0 3.0 V

Low level input voltage V

Input open voltage V

High level input current I

Low level input current I

[LIM pin]

High level input voltage V

Low level input voltage VIL(LIM) 0 1.5 V

Input open voltage V

High level input current I

Low level input current I

(CSEL) 4.0 V

IH

(CSEL) 0 1.0 V

IL

(CSEL) V

IO

(CSEL) V

IH

(CSEL) V

IL

IH

IL

CSEL=VREG

=0V –200 –140 µA

CSEL

(LIM) 3.5 V

IH

(LIM) V

IO

(LIM) V

LIM=VREG

(LIM) V

=0V –200 –140 µA

LIM

3-phase logic truth table (IN = “H” indicates the IN+ > IN– condition)

Ratings

min t yp max

REG

–0.5 V

REG

–10 0 +10 µA

–0.5 V

REG

–10 0 +10 µA

REG

REG

REG

Unit

V

V

V

V

F/R= "L" F/R= "H"

IN1 IN2 IN3 IN1 IN2 IN3 SOURCE SYNC

1HLHLHL VH UL

2HLLLHHWH UL

3HHLLLHWH VL

4LHLHLH UH VL

5LHHHLL UH WL

6LLHHHL VH WL

Output

FGSEL pin

CLKSEL pinS/S pin

Input state Condition Input state Edge detection Input state Divisor

High or open Stop High or open FG dual edge High or open 1024 x 4

L Start L FG single edge M 1024

L 1024 x 3

LIM pin

Input state Output pin (UH, VH, WH) PWMOUT pin

High or open No PWM (PAM operation) PWM output

L PWM (direct PWN operation) FG/Schmitt comparator output

Pin Assignment

–

36

CSD

35

+

IN

IN

FG

FG

34

33

+

IN1

–

IN1

32

31

+

IN2

–

IN2

30

29

+

IN3

28

–

IN3

GND

27

V

CC

26

UL

25

UH

24

VL

23

VH

22

WL

21

WH

20

RF

OUT

PWM

19

1

REG

V

LB1875

2

3

4

5

6

7

8

F/R

9

SEL

FG

I

O

X

X

S/S

SEL

CLK

IN

CLK

OUT

CLK

GND

10

LIM

11

LD112LD2

13PD14

15

16

17

SOFT

18

PWM

C

A11348

I

O

E

E

TOC

No. 6002-5/17

LB1875

Block Diagram and Sample Application Circuit

(Sample application: PAM drive, FET output)

V

REG

PDLD1LD2

V

REG

FG

IN

FG

IN

FGSEL

CLK

CLK

OUT

CLKSEL

CPWM

S/S

F/R

CSD

XO

–

+

IN

XI

CLK

OSC

PWM

OSC

S/S

F/R

SD

OSC

–

+

–

+

CLK

SELECT

ECL

1/8

LOGIC

FILTER

SELECT

PLL

1/128

1/384

1/512

FG

FG

HALL LOGIC

LD

LVSD TSD

V

REG

COMP

–

+

V

REG

PRI

DRIVER

PWM

EI

EO

TOC

PWM

OUT

V

CC

V

REG

UL

UH

VL

VH

WL

WH

12V

+

24V

+

+

HALL

HYS AMP

IN1+IN1–IN2+IN2–IN3+IN3–SOFT GNDLIM

V

CC

CURR

LIM

RF

A11596

Note: For applications where the motor has variable speed and control at low motor voltages is required, the base voltage of the

output interface transistor must be made low. In this case, a P-channel FET which can be used at low gate voltages must be

selected.

No. 6002-6/17

Loading...

Loading...