SANYO LB11990W Datasheet

Ordering number : ENN6216A

LB11990W

Three-Phase Brushless Motor Driver

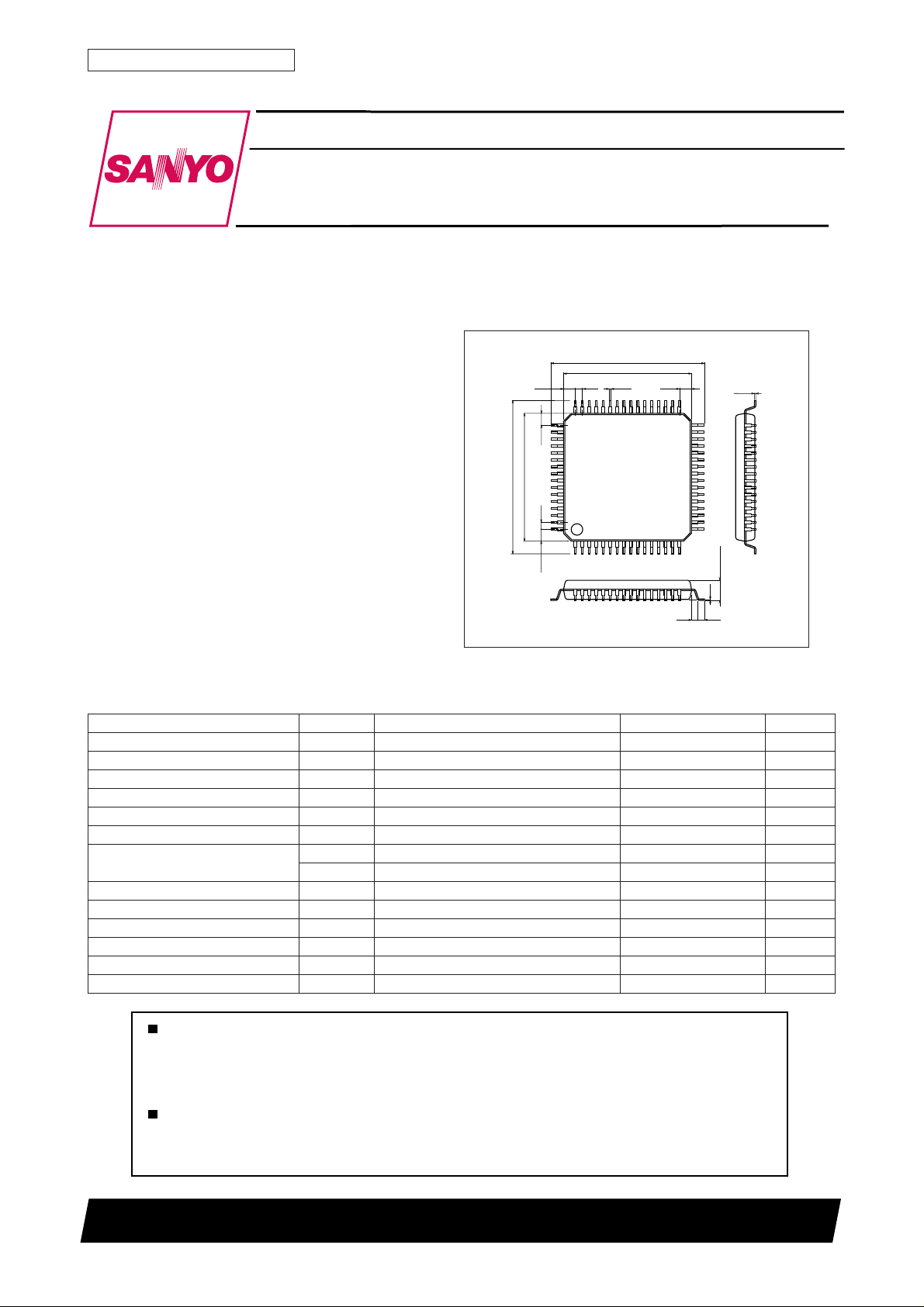

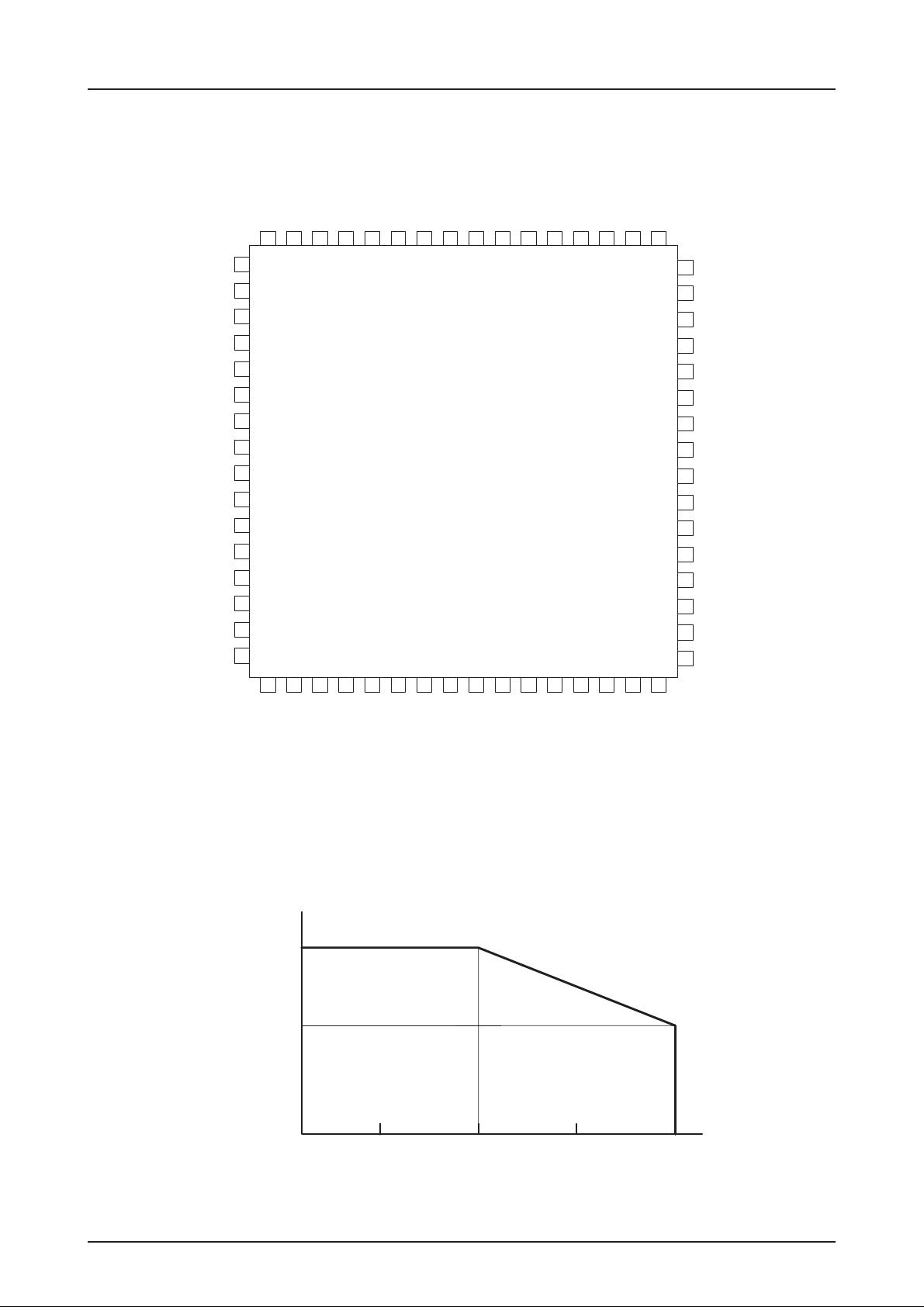

Package Dimensions

unit: mm

3190-SQFP64

1.25 0.5 1.250.18

48

49

1.25

10.0

12.0

[LB11990W]

12.0

10.0

Monolithic Digital IC

LB11990W

0.15

33

32

0.5

17

16

1.7max

0.1

0.5

0.5

SANYO : SQFP64

1.25

64

1

Specifications

Absolute Maximum Ratings at Ta = 25°C

Parameter Symbol Conditions Ratings Unit

Maximum supply voltage 1 VCC1 max 7 V

Maximum supply voltage 2 VCC2 max 8.5 V

Maximum supply voltage 3 VS_C max Capstan motor driver 7.0 V

Maximum supply voltage 4 VS_D max Drum motor driver 7.0 V

Maximum supply voltage 5 VS_L max Loading motor driver 7.0 V

Applied output voltage Vo max 8.0 V

Applied input voltage VI1 max Control circuits –0.3 to VCC1 + 0.3 V

VI2 max U, V, W, COM 8.0 V

Capstan motor output current IOC max 1.0 A

Drum motor output current IOD max 1.0 A

Loading motor output current IOL max 0.6 A

Allowable power dissipation Pd max IC only 0.6 W

Operating temperature Topr –20 to +75 °C

Storage temperature Tstg –55 to +150 °C

Any and all SANYO products described or contained herein do not have specifications that can handle

applications that require extremely high levels of reliability, such as life-support systems, aircraft's

control systems, or other applications whose failure can be reasonably expected to result in serious

physical and/or material damage. Consult with your SANYO representative nearest you before using

any SANYO products described or contained herein in such applications.

SANYO assumes no responsibility for equipment failures that result from using products at values that

exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other

parameters) listed in products specifications of any and all SANYO products described or contained

herein.

SANYO Electric Co.,Ltd. Semiconductor Company

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

N0199RM(KI)

No. 6216-1/14

LB11990W

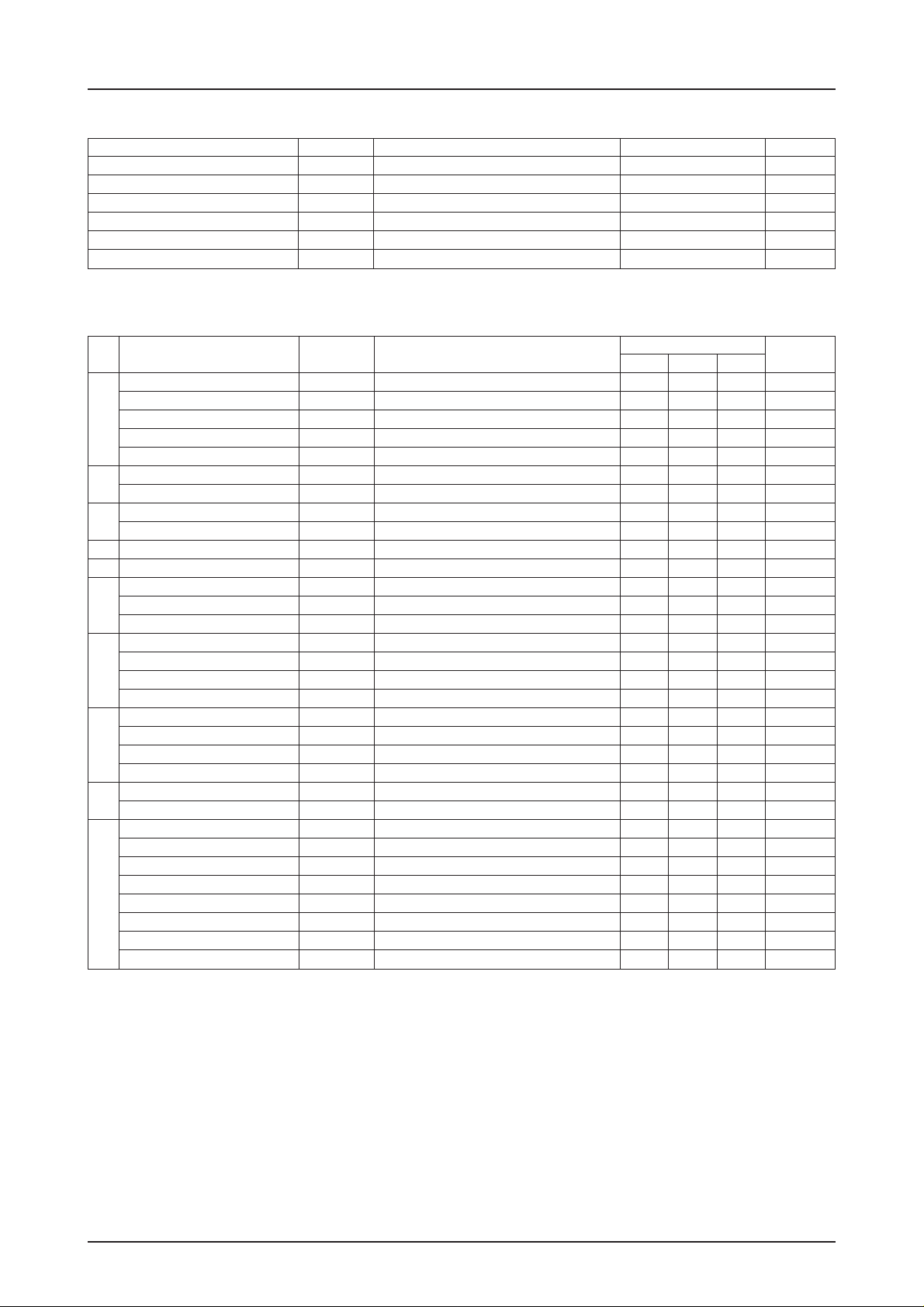

Allowable Operating Ranges at Ta = 25°C

Parameter Symbol Conditions Ratings Unit

Power supply voltage 1 VCC1VCC1 ≤ VCC2 2.7 to 6.0 V

Power supply voltage 2 VCC2 3.5 to 8.5 V

Power supply voltage 3 VS_C VS_C ≤ VCC2 to 7.0 V

Power supply voltage 4 VS_D VS_D ≤ VCC2 to 7.0 V

Power supply voltage 5 VS_L VS_L ≤ VCC2 2.2 to 7.0 V

Hall input amplitude VHALL Capstan motor ±20 to ±80 mVp–p

Electrical Characteristics/Capstan Motor Driver Block at Ta = 25˚C, VCC1 = 3V, VCC2 = 4.75V, VS = 1.5V

Parameter Symbol Conditions

Vcc1 power supply current Icc1 Iout = 100 mA VSTBY_C = 3V 4 8 mA

Vcc2 power supply current Icc2 Iout = 100 mA VSTBY_C = 3V 6 12 mA

Vcc1 idle current Icc1Q VSTBY_C = 0V 2.1 4 mA

Vcc2 idle current Icc2Q VSTBY_C = 0V 100 µA

Vs idle current IsQ VSTBY_C = 0V 75 100 µA

Power supply current

Upper side residual voltage VXH1 Iout = 0.2A 0.15 0.22 0.29 V

VX1VX2

Lower side residual voltage VXL1 Iout = 0.2A 0.15 0.20 0.25 V

Upper side residual voltage VXH2 Iout = 0.5A 0.25 0.40 V

Lower side residual voltage VXL2 Iout = 0.5A 0.25 0.40 V

Output saturation voltage Vosat Iout = 0.8A, Sink + Source 1.40 V

Overlap amount O.L RL = 39Ω × 3, Rangle = 20 kΩ Note 2 73 80 87 %

Input offset voltage VHOFF Note 1 Design target value –5 +5 mV

Common mode input range VHCM Rangle = 20 kΩ 0.95 2.1 V

Input/output voltage gain VGVH Rangle = 20 kΩ 24.5 27.5 30.5 dB

Hall amplifier

High level voltage VSTH 2.5 VCC1V

Low level voltage VSTL –0.2 +0.7 V

Input current ISTIN VSTBY_C = 3V 50 µA

Leakage current ISTLK VSTBY_C = 0V –30 µA

Standby pinFRC pinVH

High level voltage VFRCH 2.5 VCC1V

Low level voltage VFRCL –0.2 +0.4 V

Input current IFRCIN VFRC_C = 3V 20 30 µA

Leakage current IFRCLK VFRC_C = 0V –30 µA

Hall power supply voltage VHALL IH = 5 mA, VH(+) – VH(–) 0.75 0.85 0.95 V

(–) pin voltage VH(–) IH = 5 mA 0.81 0.88 0.95 V

Input offset voltage VFGOFF –3 +3 mV

Input bias current IbFG VFGIN+ = VFGIN– = 1.5V 500 nA

Input bias current offset ∆IbFG VFGIN+ = VFGIN– = 1.5V –100 +100 nA

Common mode input range VFGCM 1.2 2.5 V

High level output voltage VFGOH With internal pull-up 2.8 V

Low level output voltage VFGOL With internal pull-up 0.2 V

FG comparator

Voltage gain VGFG Note 1 Design target value 100 dB

Output current (Sink) IFGOs At output pin “L” 5 mA

Note 1: Design target value, not measured

Note 2: The overlap amount specification is taken as the measurement specification.

Ratings

min typ max

Unit

No. 6216-2/14

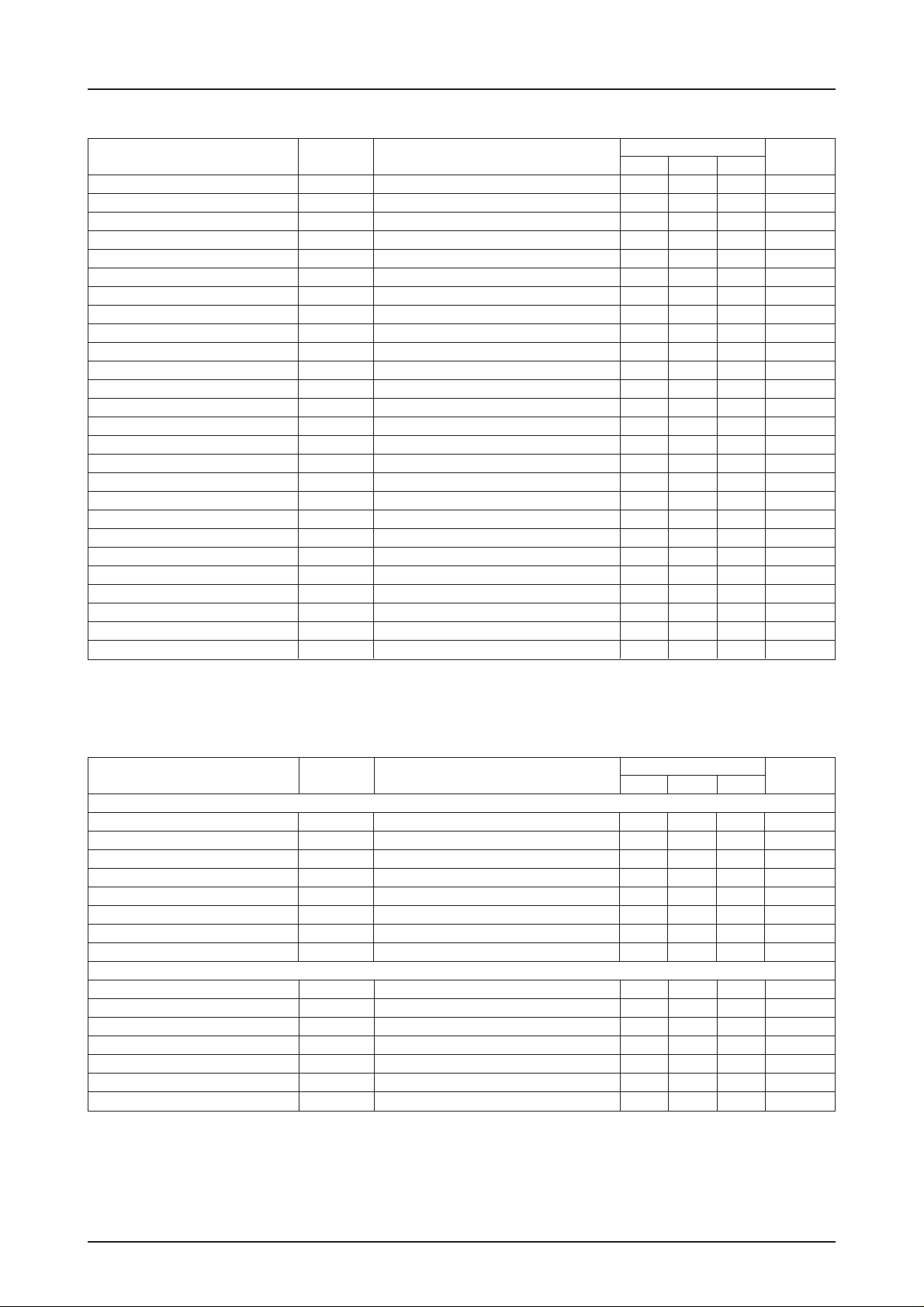

LB11990W

Cylinder Motor Driver Block at Ta = 25°C, VCC1 = 3V, VCC2 = 4.75V, VS = 3V

Parameter Symbol Conditions

Power supply current 4 ICC2 IO = 76 mA VSTBY_D = 3V VSTBY_C = 0V 0.75 2.5 mA

Output idle current 4 ICC2Q VSTBY D = VSTBY_C = 0V 100 µA

Output idle current 5 IS(D)Q VSTBY D = VSTBY_C = 0V 100 300 µA

Output saturation voltage, upper side 1

Output saturation voltage, lower side 1

Output saturation voltage, upper side 2

Output saturation voltage, lower side 2

COM pin common mode input voltage range

Standby pin High level voltage VSTBYH 2 VCC1V

Standby pin Low level voltage VSTBYL –0.2 +0.7 V

Standby pin input current ISTBYH VSTBY_D = 3V 50 µA

Standby pin leakage current ISTBYL VSTBY_D = 0V –10 µA

FRC pin High level voltage VFRCH 2 VCC1V

FRC pin Low level voltage VFRCL –0.2 +0.7 V

FRC pin input current IFRCI VFRC_D = 3V 50 µA

FRC pin leakage current IFRCL VFRC_D = 0V –10 µA

Slope pin source current ratio RSOURCE ICSLP1SOURCE/ICSLP2SOURCE –15 +15 %

Slope pin sink current ratio RSINK ICSLP1SINK/ICSLP2SINK –15 +15 %

CSLP1 source/sink current ratio RCSLP1 ICSLP1SOURCE/ICSLP1SINK –35 +15 %

CSLP2 source/sink current ratio RCSLP2 ICSLP2SOURCE/ICSLP2SINK –35 +15 %

Startup frequency Freq Cosc = 0.1 µF, OSC frequency (Target) 11.5 Hz

Phase delay-width Dwidth (Target) 30 deg

SELCSLP pin High level voltage VSELH 2 VCC1V

SELCSLP pin Low level voltage VSELL –0.2 +0.7 V

SELCSLP pin input current ISELH VSELCSLP = 3V 50 µA

SELCSLP pin leakage current ISELL VSELCSLP = 0V –10 µA

Note) Items shown to be “Target” are not measured.

VOU1 IO = 0.1A RF = 0.25Ω 0.3 0.5 V

VOD1 IO = 0.1A RF = 0.25Ω 0.3 0.5 V

VOU2 IO = 0.4A, VS = 3V RF = 0.25Ω 0.5 0.8 V

VOD2 IO = 0.4A, VS = 3V RF = 0.25Ω 0.5 0.8 V

VIC 0.3

Ratings

min typ max

VCC2–0.9

Unit

V

FG/PG Amplifier Block at Ta = 25°C, VCC1 = 3V, VCC2 = 4.75V, VS = 3V

Parameter Symbol Conditions

[FG amplifier]

Input offset voltage VIO (Target) ±1 ±5mA

Input bias current IBIN– (Target) 250 nA

Common mode input voltage range VICOM (Target) 1 2 V

Open loop gain GVFG f = 1 kHz (Target) 55 dB

Output ON voltage VOL At IO = 10 µA 0.4 V

Output OFF voltage VOH At IO = 10 µA

Schmitt amplifier hysteresis width VSHIS (Target) 50 mV

Reference voltage VREF 1.15 1.30 1.45 V

[PG amplifier]

Input offset voltage VIO (Target) ±1 ±5mV

Input bias current IBIN– (Target) 250 nA

Common mode input voltage range VICOM (Target) 1 2 V

Open loop gain GVPG f = 1 kHz (Target) 55 dB

Output ON voltage VOL At IO = 10 µA 0.4 V

Output OFF voltage VOH At IO = 10 µA

Schmitt amplifier hysteresis width VSHIS (Target) 50 mV

Note) Items shown to be “Target” are not measured.

Ratings

min typ max

VCC1–0.5

VCC1–0.5

Unit

V

V

No. 6216-3/14

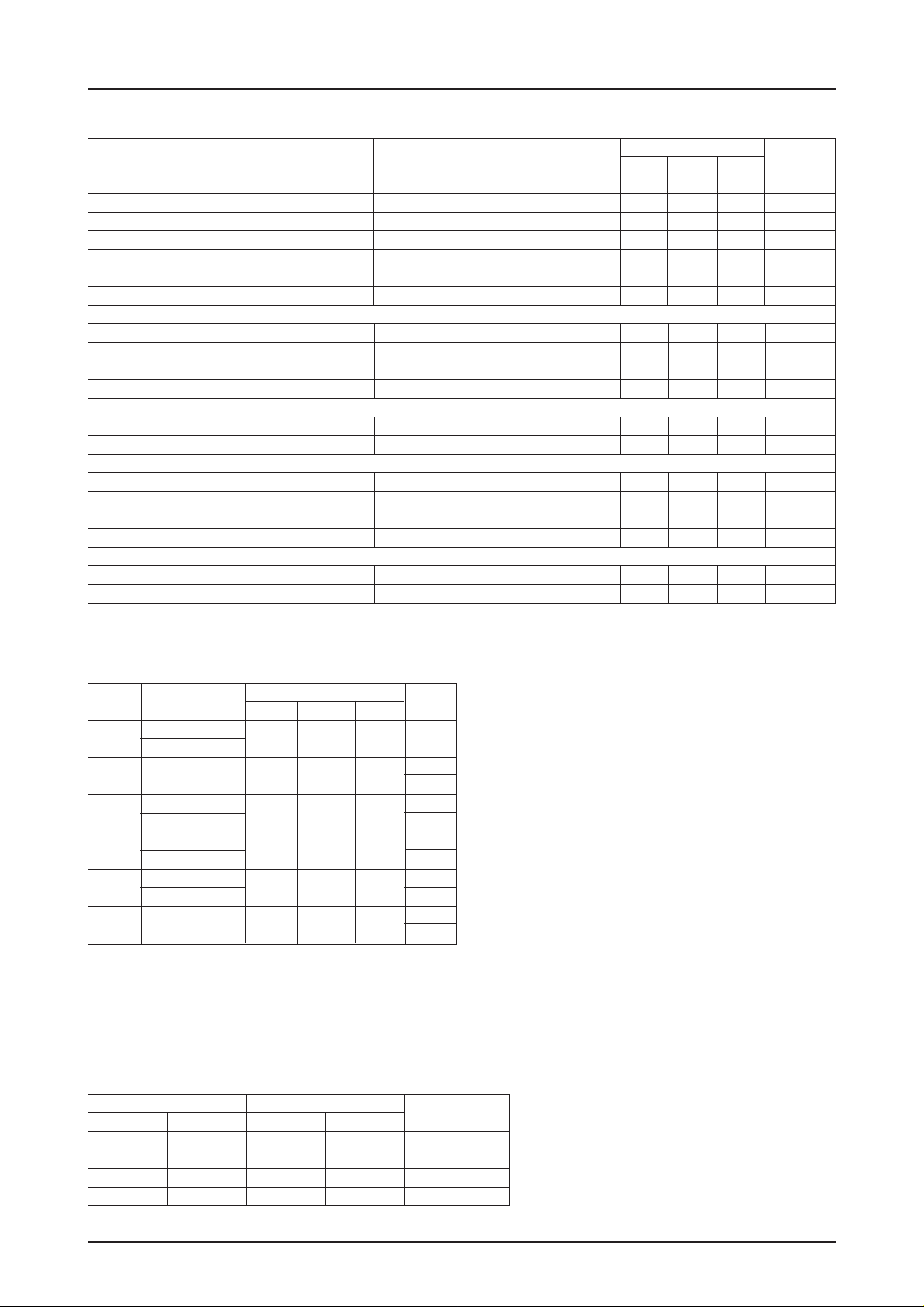

LB11990W

Loading Motor Driver Block at Ta = 25°C, VCC1 = 3V, VCC2 = 4.75V, VS = 3V

Parameter Symbol Conditions

VCC1 power supply current 1 ICC11 VSTBY_C = VSTBY_D = 0V (standby) 2.1 4 mA

VCC1 power supply current 2 ICC12

VCC1 power supply current 3 ICC13 VSTBY_C = VSTBY_D = 0V (at braking) 10 14 mA

VCC2 power supply current 1 ICC21

VCC2 power supply current 2 ICC22 VSTBY_C, D = 0V (standby (VCC1 = 3.0V)) 100 µA

VCC2 power supply current 3 ICC23 VSTBY_C, D = 0V (forward/reverse) 15.0 25 mA

VS L power supply current I VS L VSTBY_C, D = 0V (standby) 20 µA

[Logic input (DEC1 pin, DEC2 pin)]

High level input voltage VINH VCC1 = 2.7 to 4.0V 2.0 VCC1V

High level flowing current IINH VIN = 3.0V 41 65 µA

Low level input voltage VINL VCC1 = 2.7 to 4.0V –0.2 0.6 V

Low level flowing current IINL VIN = 0.6V 5 10 µA

[Loading motor driver]

Output saturation voltage 1 VOH IO = 200 mA (upper/lower composition) 0.2 0.3 V

Output saturation voltage 2 VSHIS IO = 400 mA (upper/lower composition) 0.4 0.6 V

[Reel FG amplifier]

Input offset voltage VIO ±1 ±5mV

Input bias current IB 1 µA

Common mode input voltage range VICM 1 2 V

Open loop gain GV1 55 dB

[Thermal shutdown circuit]

TSD operating temperature T-TSD (Target) 180 °C

TSD temperature hysteresis width ∆TSD (Target) 15 °C

Note) Items shown to be “Target” are not measured.

VSTBY_C = VSTBY_D = 0V (forward/reverse)

VSTBY_C, D = 0V (standby (VCC1 = OPEN))

Ratings

min typ max

14 19 mA

Unit

100 µA

Truth Table

Capstan Motor Truth Table

Hall input

Source –> Sink U V W FRC

1

2

3

4

5

6

Note: “H” for FR means a voltage of 2.50V or above. “L” for FR means a voltage of 0.4V or below.

Note: At the Hall input, “H” means that the potential of the (+) terminal for each phase input is at least 0.02V higher than the (–) terminal.

V –> W

W –> V L

U –> W

W –> U L

U –> V

V –> U L

W –> V

V –> W L

W –> U

U –> W L

V –> U

U –> V L

(Vcc1 = 3V)

“L” means that the potential of the (+) terminal for each phase input is at least 0.02V lower than the (–) terminal.

HHL

HLL

HLH

LLH

LHH

LHL

Loading Motor Truth Table

Input Output Mode

DEC1 DEC2 OUT1 OUT2

L L Off Off Standby

H L H L Forward

L H L H Reverse

H H L L Brake

H

H

H

H

H

H

No. 6216-4/14

Pin Assignment

UIN2

UIN1

WOUT_C

RF_C

VOUT_C

NC

UOUT_C

WOUT_D

RF_D

VOUT_D

UOUT_D

VS_D

OUT2

RF_L

OUT1

RS_L

585960616264 63 4950515253545557 56

VIN1

48

1

VIN2

47

2

WIN1

46

3

WIN2

45

4

LB11990W

VS_C

VH+

VH–

42

43

44

LB11990W

7

6

5

VCC2

41

8

FRC_C

39

40

9

ANGLE

FGIN+

38

11

10

FGIN–

37

12

FGOUT_C

FGOUT_D

35

36

14

13

FGIN1_D

FGIN2_D

33

34

16

15

FGIN_D

VREF

PGIN

PGC

PGOUT_D

GND

WIN

VIN

UIN

COM

232221201917 18 3231302928272624 25

VCC1

FC2

FILTER

FC1

OSC

FRC_D

NC

0.6

0.36

Power dissipation, Pd max [W]

0

DEC2

RLM1

VS_L

Ambient temperature, Ta [°C]

DEC1

STBY_C

RLP1

RLO1

RLO2

Pd max – Ta

RLP2

RLM2

CSLP1

SELCSLP

BFGO

CSLP2

STBY_D

Top view

75–20 25 500

No. 6216-5/14

Loading...

Loading...