Page 1

FILE NO.

Service Manual

Micro Component System

CONTENTS

Laser beam safety precaution..........................................1

Block diagram ..................................................................1, 7

Tuner Adjustment.............................................................2

Exploded View (Cabinet & Chassis) ................................3

Parts List ..........................................................................4

Schematic Diagram (Main) .............................................. 12

Wiring Diagram (CD Main, CD Door Sw, LED1, LED2,

and Audio).........................................14

Wiring Diagram (Display and Phone & Remote)............16

Wiring Connection...........................................................Rear

DC-MCR50 (XE)

PRODUCT CODE No.

129 664 02

REFERENCE No. SM5810404

Page 2

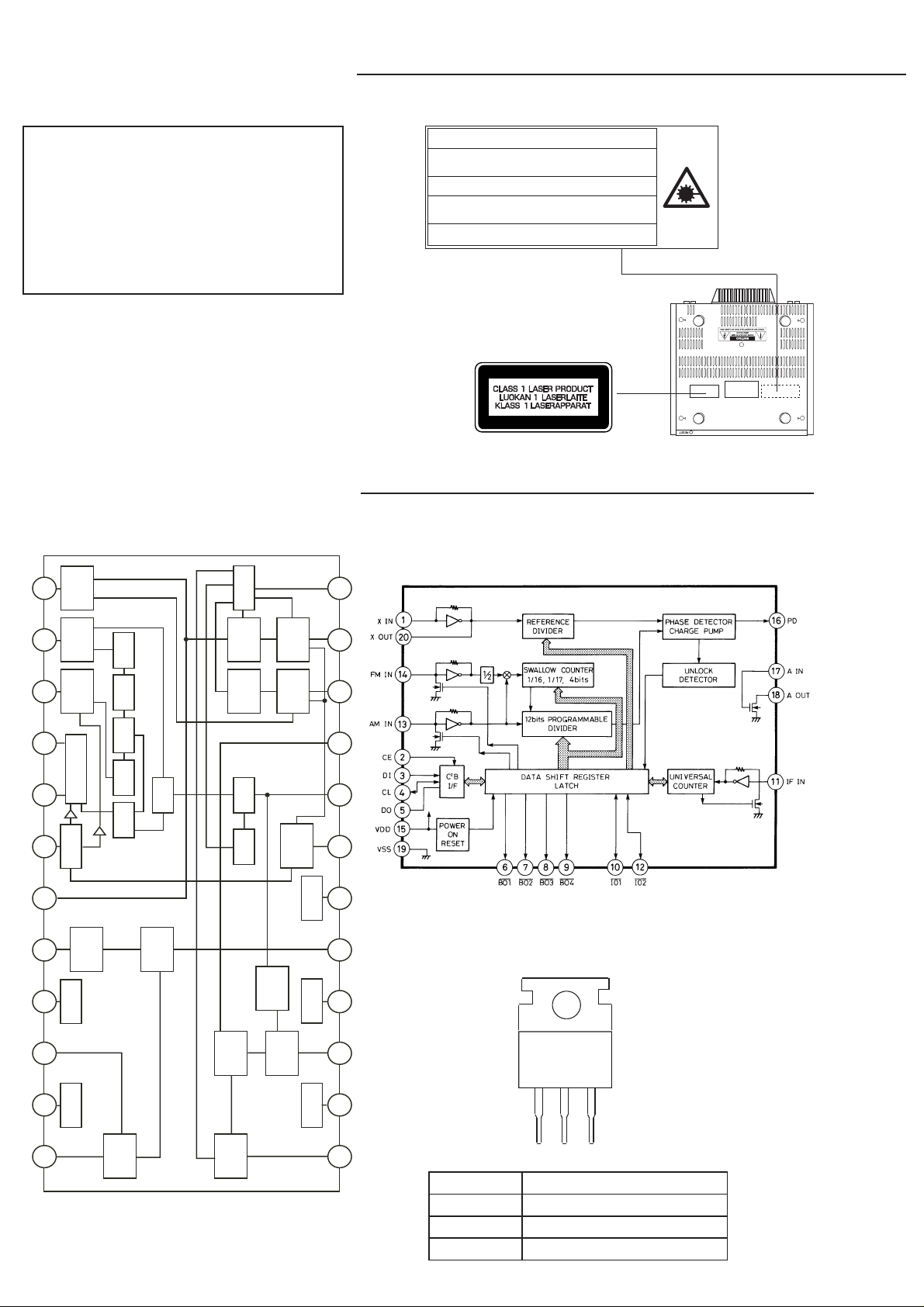

LASER BEAM SAFETY PRECAUTION

1 2 3

Pin No. Function

1INPUT

2COMMON

3

OUTPUT

• Pick-up that emits a laser beam is used in this CD player section.

CAUTION :

USE OF CONTROLS OR ADJUSTMENTS

OR PERFORMANCE OF PROCEDURES

OTHER THAN THOSE SPECIFIED HEREIN

MAY RESULT IN HAZARDOUS RADIATION

EXPOSURE

LASER OUTPUT..........0.6 mW Max. (CW)

WAVELENGTH ............. 790 nm

IC BLOCK DIAGRAM & DESCRIPTION

CAUTION – INVISIBLE LASER RADIATION WHEN OPEN AND

INTERLOCKS DEFEATED. AVOID EXPOSURE TO BEAM.

ADVARSEL – USYNLIG LASER STRÅLING VED ÅBNING, NÅR

SIKKERHEDSAFBRYDERE ER UDE AF FUNKTION, UNDGÅ UDS ÆTTELSE

FOR STRÅLING.

VARNING – OSYNLIG LASER STRÅLNING NÄR DENNA DEL ÄR ÖPPNAD

OCH SPÄRR ÄR URKOPPLAD. STRÅLEN ÄR FARLIG.

VORSICHT – UNSICHTBARE LASERSTRAHLUNG TRITT AUS, WENN

DECKEL GEÖFFNET UND WENN SICHERHEITSVERRIEGELUNG

ÜBERBRÜCKT IST. NICHT, DEM STRAHL AUSSETZEN.

VARO – AVATTAESSA JA SUOJALUKITUS OHITETTAESSA OLET ALTTIINA

NÄKYMÄTTÖMÄLLE LASERSÄTEILYLLE. ÄLÄ KA

TSO SÄTEESEEN.

IC101 LA1823 (FM/AM MIX.)

FM

DET

DET

PILOT

COMP

PHASE

FF FFFF

FM

OSC

VCO

ST SW

FM

TRIG

MIX

DECODER

MUTEV

AGCST

AM

DET

FM

S-METER

SD

AM

FM

IF

IC102 LC72131 (PLL)

IF

IF

BUFFER

IC401 KIA7808 (Regulator)

2GND2

CC

24 23 22 21 20 19 18 17 16 15 14 13

FM

RF

AM

AM

MIX

RF

OSC

BUFFER

AM

1 GND1

CC

OSC

REG V

1 2 3 4 5 6 7 8 9 10 11 12

- 1 -

Page 3

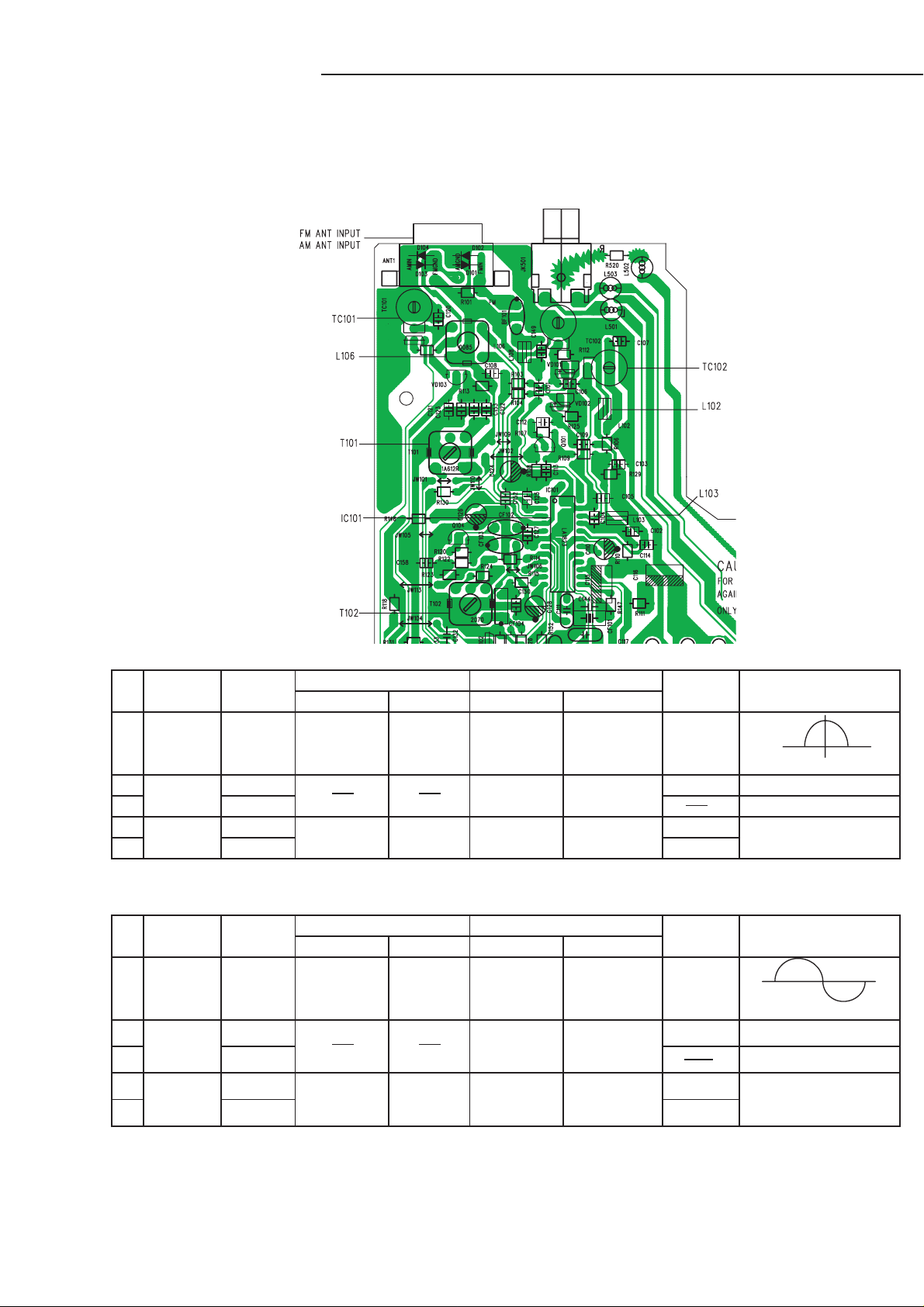

TUNER ADJUSTMENTS

Use a plastic screw driver for adjustments.

Adjust the intermediate frequency of AM and FM to the frequency of ceramic filter.

Supply voltage : DC 12.0V

Phones impedance : 32 ohms

Function switch : RADIO

a. Parts Location

b. AM Adjustment BAND SELECT SWITCH: AM.

Adjusting Tuning Input Connection Output Connection Adjustment VTVM Oscilloscope

Ste

circuit Frequency Measurement Input

1 IF 999 kHz AM Sweep Loop ANT VTVM

(450 KHz) Genertor

2 Tuning 522 KHz

3 Coverage 1611 kHz Voltmeter C131(E)

4 603 kHz AM Signal VTVM C146TU(L)

5 Tracking 1404 kHz Generator

b. FM Adjustment BAND SELECT

p Adjusting Tuning Input Connection Output Connection Adjustment

Ste

circuit Frequency Measurement Input

1 IF 98.0 MHz FM Sweep IC101(5)H

(10.70 MHz)

2 Tuning 87.5 MHz

Coverage

3

4 90.0 MHz FM Signal C110 (H) VTVM C146TU(L)

5 Tracking 106.0 MHz

108 MHz Voltmeter C105(E)

Genertor IC101(6) E

Digital C105(H) L103 2.0V+/- 0.2V

Generator

Digital C131(H), T101 1.50V+/- 0.05 V

Loop ANT

SWITCH: FM.

IC101(6)E

Measurement

Oscilloscope

Oscilloscope

Measurement

VTVM IC101PIN19(H)

Oscilloscope IC101PIN6(E)

Oscilloscope

Output Parts OR VT. VOLT.

IC101PIN19(H)

IC101PIN6(E)

IC101 pin6(E) TC101

FM Dummy Antenna : 75 ohm unbalance

Output Parts

IC101 pin6(E)

T102

Confirm 7.8V+/-0.8 V

L106

VTVM Oscilloscope

(Non-adjustment)

Confirm6,5V+/- 0.8V

L102

TC102

Maximum

Maximum

- 2 -

Page 4

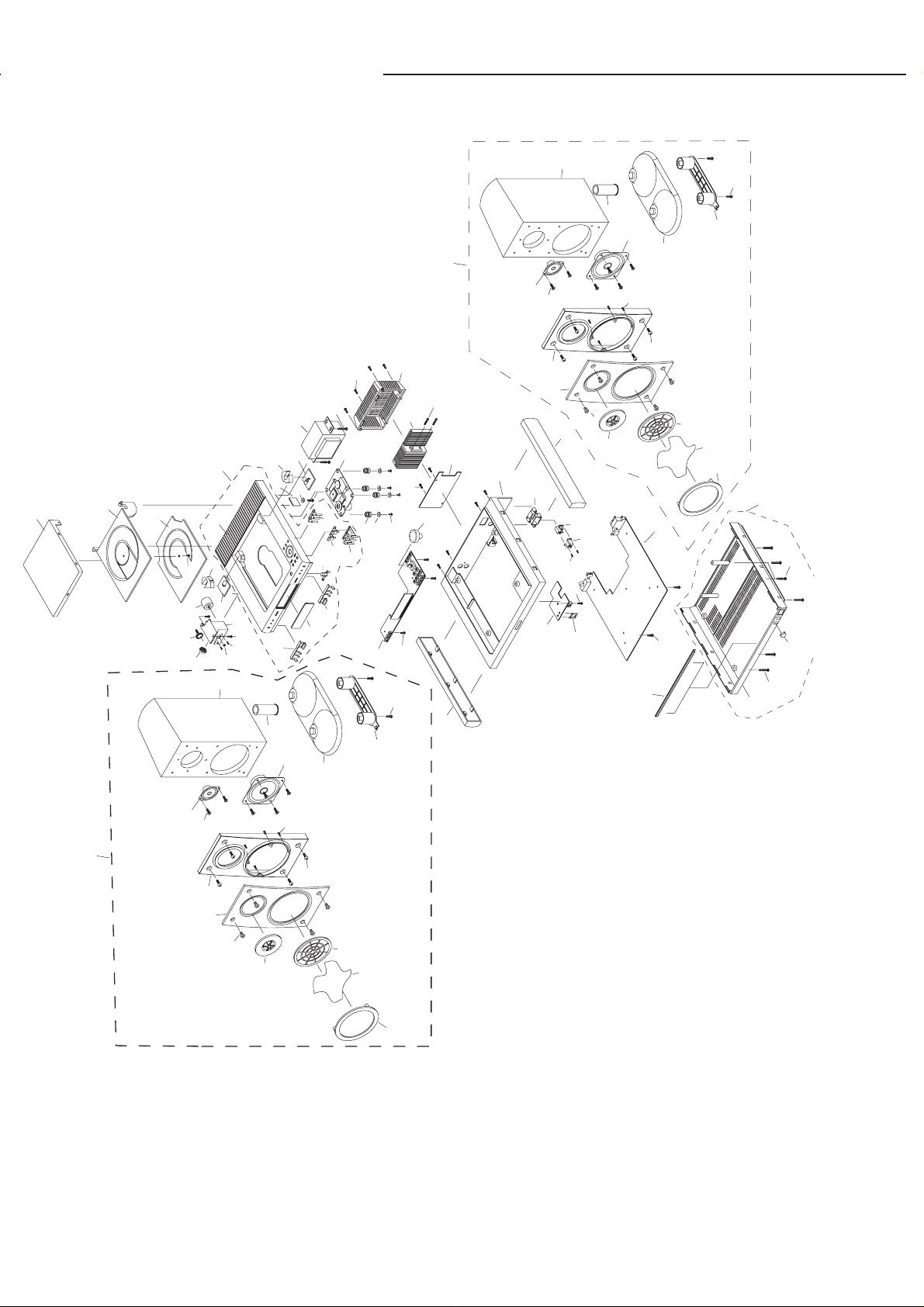

EXPLODED VIEW(CABINET & CHASSIS)

48

1

2

3

12

14

5

6

7

8

10

11

15

27

17

16

18

19

21

25

34

26

30

31

32

35

36

39

40

42

43

33

44

45

46

47

49

52

51

53

55

56

57

58

59

28

9

60

50

61

S1

S2

S3

S5

S6

S7

S8

S9

S10

S11

S11

S13

S14

S16

S17

S18

S14

S14

S21

S22

S23

S24

13

29

S4

54

57

S22

S23

60

59

S24

58

61

56

51

53

54

S21

55

50

52

49

29

63

62

4

20

62

49

- 3 -

Page 5

PARTS LIST

PRODUCT SAFETY NOTICE

EACH PRECAUTION IN THIS MANUAL SHOULD BE FOLLOWED DURING SERVICING. COMPONENTS IDENTIFIED WITH

!!

!

THE IEC SYMBOL

CAN OF SPECIAL SIGNIFICANCE. WHEN REPLACING A COMPONENT IDENTIFIED , USE ONLY THE REPLACEMENT

PARTS DESIGNATED, OR PARTS WITH THE SAME RATINGS OF RESISTANCE, WATTAGE OR VOLTAGE THAT ARE

DESIGNATED IN THE PARTS LIST IN THIS MANUAL. LEAKAGE-CURRENT OR RESISTANCE MEASUREMENTS MUST

BE MADE TO DETERMINE THAT EXPOSED PARTS ARE ACCEPTABLY INSULATED FROM THE SUPPLY CIRCUIT BEFORE

RETURNING THE PRODUCT TO THE CUSTOMER.

CAUTION : Regular type resistors and capacitors are not listed. To know those values, refer to the schematic diagram.

IN THE PARTS LIST AND THE SCHEMATIC DIAGRAM DESIGNATE COMPONENTS IN WHICH SAFETY

Regular type resistors are less than 1/4W carbon type and 0 ohm chip resistors.

Regular type capacitors are less than 50V and less than 1000µF of Ceramic type and Electrolytic type.

PACKING & ACCESSORIES

REF.NO. PART NO. DESCRIPTION

645 062 1918 INSTRUCTION MANUAL

645 027 2073 POLY BAG,PWR CORD

645 044 1943 POLY BAG,I/B

645 062 2014 POLY BAG,UNIT

645 062 2007 POLY BAG,SPK

645 062 2021 POLY FOAM,KIT

645 062 2083 CARTON CASE

!!

!

645 023 3463 POWER CORD

645 061 6280 REMOTE CTL,RC29-100000-010

62 645 062 0652 SPK BOX L,LEFT

63 645 062 0669 SPK BOX R,RIGHT

645 061 6297 ANTENNA LOOP

CABINET & CHASSIS

REF.NO. PART NO. DESCRIPTION

1 645 062 1659 CD DOOR

2 645 062 1437 CD DOOR BKT

3 645 062 1567 CD DOOR LENS

4 645 062 0591 ASSY CABINET TOP

6 645 062 1383 PULLEY WORM GEAR

7 645 062 1284 CD DOOR GEAR

8 645 062 1376 MOTOR PULLEY

9 645 062 1420 MOTOR BKT

11 645 062 1611 TRANSPARNT LENS L

12 645 062 1628 TRANSPARNT LENS R

15 645 062 1338 KNOB BASS

16 645 062 1321 KNOB TUNING

17 645 062 1369 KNOB PRESS

18 645 062 1505 KNOB CD DOOR,OPEN

19 645 062 1512 KNOB FUNCTION

20 645 062 1352 KNOB SW,MONO/STEREO

21 645 062 1574 CD DISPLAY LENS

26 645 062 1345 KNOB VOLUME

27 645 062 1208 CD DECK MECHANISM

28 645 033 3446 RUBBER SILICON,HARDNESS

29 645 027 1373 WASHER METAL

30 645 062 1635 CAB REAR COVER,

31 645 062 1222 HEAT SINK

33 645 062 1307 CABINET MIDDLE

34 645 062 1482 PANEL SIDE L,LEFT

35 645 062 1499 PANEL SIDE R,RIGHT

36 645 062 1406 AC SOCKET BKT

40 645 033 0391 AC SKT COVER

43 645 055 7514 REMOTE RECEIVER BKT

45 645 062 1598 DECOR FRANT LENS

46 645 062 1314 CABINET BOTTOM

47 645 062 1536 REMOTE LENS

48 645 062 1642 CABINET TOP

49 645 062 0584 ASSY CABINET BOTTOM

HEAT SINK COVER

FIXING PARTS

REF.NO. PART NO. DESCRIPTION

S10 645 023 6594 SCREW ST 3X8,DISPLAY BD

S11 645 023 6594 SCREW ST 3X8,ANT JACK,

S13 645 023 6594 SCREW ST 3X8,AUX JACK,

S14 645 062 1116 SCR 3X15,CAB BTM TO CAB TOP

S16 645 023 6617 SCREW ST 3X10,AC SOCKET

S17 645 023 6594 SCREW ST 3X8,H/JACK BD

S18 645 023 6594 SCREW ST 3X8,MAIN BD

S1 645 062 1086 SCR 2X5,CD DOOR LENS

S2 645 062 1109 SCR 2.6X4,MOTOR

S3 645 023 6594 SCREW ST 3X8,MOTOR BKT

S4 645 027 1168 SCR 3X8,CD DOOR SW

S5 645 062 1116 SCR 3X15,

S6 645 023 6594 SCREW ST 3X8,

S7 645 023 6587 SCREW ST 3X8,IC TO H/S

S8 645 023 6594 SCREW ST 3X8,AUDIO BD

S9 645 033 0247 SCR 2.6X8,CD DECK

OPTICAL JACK

RCA JACK

PWR TRANS TO CAB BTM

H/S COVER TO CD TRAY

ELECTRICAL-PARTS

REF.NO. PART NO. DESCRIPTION

5 645 062 1215 CD DOOR MOTOR

14

39 645 032 9760 AC SOCKET S-1-1225

!!

!

645 062 0683 PWR TRANS,9023FS

645 062 0928 2P CONNECTOR,SPEAKER

645 042 9569 HSG 6P,MAIN CN902 TO CD DECK

645 062 1000 HSG 2P,MAIN CN706 TO LED BD

645 062 1017 HSG 4P,MAIN CN704 TO CN804

645 062 1024 HSG 4P,MAIN CN303 TO CN305

645 062 1031 HSG 5P,MAIN CN301 TO CN801

645 062 1048 HSG 7P,MAIN CN302 TO CN304

645 062 1055 HSG 14P,MAIN CN703 TO CN708

645 062 1062 HSG 5P,

645 062 1079 FFC CABLE 16P,

645 062 1185 HSG 12P,MAIN CN701 TO CN709

645 062 1192 HSG 13P,MAIN CN702 TO CN707

MAIN CN903 TO CD DOOR SW

MAIN CN901 TO CD DECK

- 4 -

Page 6

PARTS LIST

LED 1 P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

10 614 327 0034 ASSY,PWB,LED 1(Only initial)

LED01 645 062 0881 LED

CD DOOR SW P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

13 614 327 0058 ASSY,PWB,CD DOOR SW

(Only initial)

SW001 645 062 0836 MICRO SW

SW002 645 062 0836 MICRO SW

DISPLAY P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

25 614 327 0010 ASSY,PWB,DISPLAY(Only initial)

LD701 645 062 0843 LCD DISPLAY,LCD701

LE701 645 062 0881 LED,LED701

LE702 645 062 0881 LED,LED702

SW701 645 062 0829 SW TACT,POWER

SW702 645 062 0829 SW TACT,MO/ST

SW703 645 062 0829 SW TACT,INTRO

SW704 645 062 0829 SW TACT,AUX

SW705 645 062 0829 SW TACT,TU/BAND

SW706 645 062 0829 SW TACT,MODE

SW707 645 062 0829 SW TACT,STOP

SW708 645 062 0829 SW TACT,CD P/P

SW709 645 055 7064 SW TACT,OPEN/CLOSE

SW710 645 055 7064 SW TACT,MEMORY

SW711 645 055 7064 SW TACT,RENDOM

SW712 645 055 7064 SW TACT,REPEAT

SW713 645 055 7064 SW TACT,B-SKIP

SW714 645 055 7064 SW TACT,F-SKIP

SW715 645 055 7064 SW TACT,MUTE

SW716 645 055 7064 SW TACT,X-BASS

SW717 645 055 7064 SW TACT,EQ

VR701 645 055 7309 ROTARY ENCODER,VOL701

645 062 1413 DISPLAY BKT PLATE

645 062 1444 DISPLAY BKT

AUDIO P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

32 614 327 0003 ASSY,PWB,AUDIO(Only initial)

CN304 645 062 0959 7P HEADER

CN305 645 027 3803 WAFER 4P

IC301 645 062 0799 IC LA4725

Q0301 645 033 3538 TR 2SD1936S AC

Q0302 645 033 3538 TR 2SD1936S AC

PHONE & REMOTE P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

42 614 327 0027 ASSY,PWB,H/JACK(Only initial)

CN801 645 062 0942 5P HEADER

JK303 645 062 1147 ST PHONEJACK

L0801 645 044 1721 FERRITE BEAD

L0802 645 044 1721 FERRITE BEAD

L0803 645 044 1721 FERRITE BEAD

RM701 645 033 3477 DIODE RPM-6938-V4,REM701

SW718 645 055 7064 SW TACT,RESET

CD MAIN P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

44 614 326 9991 ASSY,PWB,CD MAIN(Only initial)

ANT01 645 062 1161 ANTENNA JACK,FM ANT

BF101 645 051 6467 BAND PASS FILTER

C0111 403 056 7908 POLYESTER 1000P K 50V

C0118 403 057 0403 POLYESTER 0.01U K 50V

C0119 403 057 0403 POLYESTER 0.01U K 50V

C0122 645 055 6791 POLY CAP 390PF

C0147 403 058 8200 POLYESTER 1800P K 50V

C0148 403 058 8200 POLYESTER 1800P K 50V

C0303 403 059 5901 POLYESTER 0.022U K 50V

C0304 403 059 5901 POLYESTER 0.022U K 50V

C0328 403 058 5209 POLYESTER 0.15U K 50V

C0404 403 125 5507 ELECT 1000U M 16V

REF.NO. PART NO. DESCRIPTION

C0509 403 058 5209 POLYESTER 0.15U K 50V

C0510 403 058 5209 POLYESTER 0.15U K 50V

C0511 403 058 5209 POLYESTER 0.15U K 50V

C0512 403 058 5209 POLYESTER 0.15U K 50V

C0513 403 059 3600 POLYESTER 2200P K 50V

C0514 403 059 3600 POLYESTER 2200P K 50V

C0524 403 056 7908 POLYESTER 1000P K 50V

C0525 403 056 7908 POLYESTER 1000P K 50V

C0719 645 055 6784 GOLD CAP DX-5R5H104,GOLD CAP

C0901 403 057 2803 POLYESTER 0.1U K 50V

C0902 403 060 8205 POLYESTER 0.033U K 50V

C0907 403 060 6102 POLYESTER 3300P K 50V

C0908 403 062 0306 POLYESTER 0.047U K 50V

C0909 403 057 2803 POLYESTER 0.1U K 50V

C0914 403 057 2803 POLYESTER 0.1U K 50V

C0915 403 058 3205 POLYESTER 0.015U K 50V

C0916 403 058 9900 POLYESTER 0.018U K 50V

C0917 403 060 6102 POLYESTER 3300P K 50V

C0922 403 060 6102 POLYESTER 3300P K 50V

C0924 403 059 3600 POLYESTER 2200P K 50V

C0926 403 060 8205 POLYESTER 0.033U K 50V

C0933 403 062 0306 POLYESTER 0.047U K 50V

C1105 403 121 2807 ELECT 6800U M 16V

C1107 403 135 0004 ELECT 2200U M 25V

CF101 645 062 0751 CERAMIC FILTER

CF102 645 062 0768 CERAMIC FILTER

CF103 645 062 0768 CERAMIC FILTER

CF104 645 055 6920 CERAMIC FILTER

CN701 645 062 0966 12P HEADER

CN702 645 062 0973 13P HEADER

CN703 645 062 0980 14P HEADER

CN704 645 042 9552 HEADER 4PINS

CN706 645 034 6798 HEADER 2PINS

CN901 645 055 7163 16P FFC HEADER

CN903 645 051 6535 5P HEADER

D0101 645 055 6821 DIODE 1N4148

D0102 645 055 6821 DIODE 1N4148

D0103 645 055 6821 DIODE 1N4148

D0104 645 055 6821 DIODE 1N4148

D0105 645 055 6821 DIODE 1N4148

D0301 645 055 6821 DIODE 1N4148

D0302 645 055 6821 DIODE 1N4148

D0303 645 055 6821 DIODE 1N4148

D0304 645 055 6821 DIODE 1N4148

D0701 645 055 6821 DIODE 1N4148

D0703 645 055 6821 DIODE 1N4148

D0709 645 055 6821 DIODE 1N4148

D0710 645 055 6821 DIODE 1N4148

D0711 645 055 6821 DIODE 1N4148

D0713 645 055 6821 DIODE 1N4148

D0714 645 055 6821 DIODE 1N4148

D0715 645 055 6821 DIODE 1N4148

D0716 645 055 6821 DIODE 1N4148

D0717 645 055 6821 DIODE 1N4148

D0718 645 055 6821 DIODE 1N4148

D0719 645 055 6821 DIODE 1N4148

D0722 645 055 6821 DIODE 1N4148

D0723 645 055 6821 DIODE 1N4148

D1101 645 027 0932 RECTIFIER 1N-5401

D1102 645 027 0932 RECTIFIER 1N-5401

D1103 645 027 0932 RECTIFIER 1N-5401

D1104 645 027 0932 RECTIFIER 1N-5401

F1101 645 062 0935 GLASS FUSE,FS1101

IC101 645 055 6975 IC LA1823ESIA

IC102 645 055 7019 IC LC72131

IC401 645 055 6982 IC KIA7808P

IC501 645 055 7026 IC LC75342

IC701 645 062 0805 IC LC587008 1P46

IC702 645 055 6951 IC PST600C

IC703 645 055 6968 IC PST600L

IC901 645 055 8436 IC LA9242M

IC902 645 033 4740 IC LC78622E

IC903 645 033 4702 IC LA6541D

IC904 645 062 0782 IC LB1641

- 5 -

Page 7

PARTS LIST

REF.NO. PART NO. DESCRIPTION

JK301 645 062 1178 SPEAKER TERMINAL

JK302 645 057 2449 OPTICAL TRANSMITTING,

SUBWOOFER

JK501 645 062 1154 RCA JACK

L0102 645 062 0812 FM COIL

L0103 645 027 0345 VHF COIL

L0104 645 062 0874 CHOKE COIL 39MH

L0105 645 062 0874 CHOKE COIL 39MH

L0106 645 062 0775 IFT,OSC OA10-871104

L0107 645 027 0352 CHOKE COIL 100UH

L0108 645 044 7013 FM COIL 3.5T

L0301 645 062 0867 CHOKE COIL 10UH 2A

L0302 645 062 0867 CHOKE COIL 10UH 2A

L0303 645 062 0867 CHOKE COIL 10UH 2A

L0304 645 062 0867 CHOKE COIL 10UH 2A

L0305 645 033 3637 CHOKE COIL 10UH

L0306 645 033 3637 CHOKE COIL 10UH

L0501 645 033 3637 CHOKE COIL 10UH,FCC

L0502 645 033 3637 CHOKE COIL 10UH,FCC

L0503 645 033 3637 CHOKE COIL 10UH,FCC

L0701 645 027 0352 CHOKE COIL 100UH

L0901 645 042 0108 CHOKE COIL 26UH

L0903 645 027 0352 CHOKE COIL 100UH

Q0101 645 027 3797 TR 9018H

Q0102 645 034 7078 TR 2SC3330U

Q0103 645 027 0420 TR 8050C

Q0104 645 055 6876 TR 9018F

Q0303 645 032 9890 TR KTC-9015C

Q0304 645 033 3538 TR 2SD1936S AC

Q0305 645 033 3538 TR 2SD1936S AC

Q0306 645 034 7078 TR 2SC3330U

Q0307 645 023 6129 TR 9014C

Q0308 645 023 6129 TR 9014C

Q0309 645 032 9890 TR KTC-9015C

Q0310 645 023 6129 TR 9014C

Q0401 645 055 6883 TR KSA928A

Q0402 645 027 0420 TR 8050C

Q0403 645 023 6129 TR 9014C

Q0404 645 027 0420 TR 8050C

Q0407 645 023 6129 TR 9014C

Q0408 645 023 6129 TR 9014C

Q0409 645 055 6869 TR 8550B C

Q0410 645 055 6883 TR KSA928A

Q0705 645 055 6890 TR 2SC3400AC

Q0706 645 055 6890 TR 2SC3400AC

Q0707 645 055 6890 TR 2SC3400AC

Q0712 645 023 6129 TR 9014C

Q0713 645 023 6129 TR 9014C

Q0714 645 023 6129 TR 9014C

Q0715 645 023 6129 TR 9014C

Q0901 645 061 8246 TR 2SA608NFNPAAT

Q0903 645 033 3514 TR 2SB764D

R0409 402 071 1304 FUSIBLE RES 2.2 JA 1/4W

T0101 645 055 6944 IFT,OSC 1A612R

T0102 645 033 3866 AM COIL,IF 2070

T0801 645 027 0307 BIAS COIL,IFT 3630

TC101 645 023 6310 TRIMMER 10PF

TC102 645 023 6310 TRIMMER 10PF

VD101 645 062 0713 DIODE ISV101

VD102 645 062 0713 DIODE ISV101

VD103 645 055 6814 DIODE SVC348

X0101 645 062 0904 CRYSTAL

X0701 645 062 0898 CRYSTAL

X0702 645 062 0911 CRYSTAL 32.768KHZ

X0901 645 061 9915 RESONATOR 16.9344MHZ

ZD101 645 055 6838 ZENER 5.6V

ZD102 645 062 0744 ZENER 9.1V

ZD302 645 062 0720 ZENER 3.6V

ZD401 645 062 0737 ZENER 6.2V

ZD402 645 055 6838 ZENER 5.6V

ZD901 645 023 6105 ZENER DIODE

645 035 0511 FUSE HOLDER MW1010K,FS1101

645 062 0997 HSG 1P,FM ANT

645 042 0344 CONTACT PIN,FM RT-01T-1.0B

LED 2 P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

62 614 327 0041 ASSY,PWB,LED 2(Only initial)

LED02 645 062 0881 LED

SPEAKER SYSTEM

REF.NO. PART NO. DESCRIPTION

49 645 062 1550 HIGH SPK RING,ORNAMETAL

50 645 062 1277 SPK CLOTH

51 645 062 1468 SPK NET HOLDER

52 645 062 1543 LOW SPK RING,ORNAMETAL

53 645 062 1529 SCREW PLASTIC,DECORATION

54 645 062 1604 SPK PANEL LENS

55 645 062 1475 SPK PANEL

56 645 062 0690 SPK 2

57 645 062 0706 SPK 3.5

58 645 062 1291 SPK BOX PLASTIC PIPE

59 645 062 1888 SPK BOX STAND

60 645 062 1451 SPK AVOID QUAKE RING

61 645 062 1994 SPK BOX

62 645 062 0652 SPK BOX L,LEFT

63 645 062 0669 SPK BOX R,RIGHT

S21 645 062 1116 SCR 3X15,SPK PANEL

S22 645 062 1093 SCR 2X10,SPK RING

S23 645 027 1168 SCR 3X8,SPK

S24 645 062 1130 SCR 3.5X15,SPK STAND

- 6 -

Page 8

IC BLOCK DIAGRAM & DESCRIPTION

IC501 LC75342 (2 band equalizer)

LSELO LIN LTRE LBASS1 LBASS2 LOUT

10 9 7 6 58

L4

11

L3

12

L2

13

L1

14

NC

15

NC

16

R1

17

R2

18

R3

19

R4

20

21 22 24 25 2623

RSELO RIN RTRE RBASS1 RBASS2 ROUT

Pin functions

CONTROL

CIRCUIT

LOGIC

CIRCUIT

CONTROL

CIRCUIT

LVref

CCB

INTERFACE

RVref

4

TEST

3

SS

V

2

CE

1

DI

30

CL

29

DD

V

28

Vref

27

NC

PinNumber

14

13

12

11

17

18

19

20

10

21

7

6

24

25

9

22

5

26

8

23

28

3

29

PinDescription

L1

L2

L3

L4

R1

R2

R3

R4

LSEL0

RSEL0

LBASS1

LBA

RBA

RBA

LIN

RIN

LOU

ROUT

LTRE

RTRE

Input signal connections

Input selector outputs

SS2

Connections for the resistorsand capacitors that form thebass band filters.

SS1

SS2

Vo lume control and equalizer input

T

Vo lume and e qualizer outputs

Connections for the capacitors that form the treble band filters

Connection to the 0.5xVDD voltage generator circuit used asthe analog signalground.

Vref

Vss

VDD

Applications must connect a c apacitor ofabout 10 uFbetween this pina nd Vss

to exclude powersupply ripple

.

Ground

Po wer supply

.

Chip enable

2CE

Data is writtento the internal latch when thispin goes fromhigh to low.

The internal analog switches operate at this point.Data transfer is

enabled when thispin is high.

1

30

4

15

16

27

Vss

NC

DI

CL

Serial data and clock inputs used for IC control .

Electronic volume and tone control testing

Thispin must be tied toVss during normal operation.

Unused.

These pins must be left open or connected toVss during normal operation.

- 7 -

Page 9

IC BLOCK DIAGRAM & DESCRIPTION

IC701 LC587008 (4bit MICON)

Address

V

DD

V

SS

V

1

DD

2

V

DD

CUP1

CUP2

Input

CFIN

Output

CFOUT

XTIN Input 20

Output

XTOUT

S1

S2

Input

S3

S4

K1

K2

I/O

K3

K4

M1

M2

I/O

M3

M4

A1

A2

I/O

A3

A4

P1

P2

I/O

P3

P4

Pin No.

24

Power supply

23

LCD drive power supply

22

VDD

21

VDD1

VDD2

VSS

Switching pin used to supply the LCD drive voltage to the VDD1and

V2PINS

DD

3

Connect a nonpolarized capacitor between CUP1 and CUP2 when

4

1/2 or 1/3bias is used

Leave open when a bias other than 1/2 or1/3 is used.

System clock oscillator connections

25

Ceramic resonator connection (CF specifications)

RC component connection (RC specifications)

External signal input pin (CFOUT isleft open)

26

This oscillator is stopped by the execution of aSTOP or SLOW

instruction.

Referenc e calculation(cl ock specification s,LCD alternain g freq uency),

system clock oscillator

32 kHz crystal resonator connection

65 kHz crystal resonator connection

19

This oscillator is stopped by the execution of aSTOP instruction.

Input-only ports

Input pins used to read data into RAM

27

Built-in 7.8 msand 1.95 mschatter rejection circuits

28

Built-in pull-up/pull-down resistors

29

Note: The 7.8 ms and 1.95 ms times are the times whenf 0 is

30

32.768kHz.

I/O ports

Input pins used to output readdata into RAM

31

Output pins used to output data from RAM

32

Built-in 7.8 msand 1.95 msinput-mode chatter rejection circuits.

33

The selection of7.8 or 1.95 ms is linked to that for the S ports.

34

Note: The 7.8 ms and 1.95 ms times are the times whenf 0 is

32.768 kHz.

I/O ports

35

Input pins used to read data into RAM

Output pins used to output data from RAM

36

M4 is used as the external clock input pinin Tm2 mode 3.

37

*The minimum period for the external clock is twicethe cycle time.

38

Built-in pull-up/pull-down resistors

11

I/O ports

12

Input pins used to read data into RAM

Output pins used to output datafrom RAM

13

Built-in pull-up/pull-down resistors

14

15

I/O ports

16

Function: The same as pins A1to A4

17

18

Function

NON 1/1 bias

1/2 bias

1/3 bias

CF specifications

RC specifications

External

Specifications

Not used

32k specifications

65k specifications

38k specifications

Not used

Transistor to hold

alow orhigh level

Selection of either

pull-up or pulldown resistor

Transistors to hold

a low orhigh level

Selection of either

pull-up or pulldown resistor

The same as K1 toK4The same as K1 to

The same as K1 to

K4

The same as K1 to

K4

Option

At reset

The pull-up or pulldown resistor are

on.

Note:

These pins go

to the floatin g

state when

reset is cle are d.

The pull-up or pulldown resistors are

on.

Note:

These pins go

to the floatin g

state when

reset is cle are d.

Input mode

Output latch data is

set high.

K4

The same as K1 to

K4

The same as K1 to

K4

Continued from preceding

So1

So2

So3

So4

N1

N2

N3

N4

INT

RES

TST

Seg1,

Seg2 to

Seg35

COM1

COM2

COM3

COM4

- 8 -

page.

QIP-80

I/O

Pin

I/O

Output

Input

Input

Input

Output

Output

Pin No.

I/O ports

Function: The same as for pins A1 to A4

Pins So1 to So3 area also used for the serial interface.

7

Use of these pins inserial mode can be selected under program

8

cotrol.

9

Pin functions: SO1:Serial input pin

10

The serial clock pin can beswitched between internal and external,

and between rising edge output andfalling edge output.

Output-only ports

Output pins usedto output data from RAM

39

An alarm signal can be output from pin N4.(Note that this isonly

40

when the N4 output latch islow.)

41

An alarm signal modulated at 1,2 or 4 kHzcan be output.(These

42

frequencies are output when f 0 is 32.768 kHz.)

Acarrier signal can be output from N3.(Note thatthis is only

when the N3 output latch islow.)

Input ports

External interrupt request inputs

Input pins used to read datainto RAM

6

Input detection can be performed oneither rising orfalling edges.

Built-in pull-up/pull-down resistors

LSI internal reset input

The reset input level can beselected to beeither high or low.

5

Built-in pull-up/pull-down resistors

Note: The reset pulse must beat least 500us.

Test input

QIP80 products: Connect to Vss.

43

Chip products :Leave open orconnect to Vss.

LCD panel drive/general-purpose

LCD panel drive

STATIC

1/2 bias-1/2 duty

1/2 bias-1/3 duty

1/2 bias-1/4 duty

1/3 bias-1/3 duty

1/3 bias-1/4 duty

Types Ito V can be specified as mask

44,

General-purpose output mode

45 to

CMOS

78

P-channel open drain

N-channel open drain

Types Ito III can be specified asmask options.

LCD/general -purpo se output contro l is handle d by the segme nt PLA,

and thus program control is not required.

These pins support output latch control on reset andin standby

states when theoscillators are stopped.

Arbitrary com binat ions of LCD drive and gene ral-purpose output s can

be used.

LCD panel drive common polarity outputs

The table below shows how these pins are used depen ding on the duty

used.( values for alterna ting freque ncy reflect a typical specif ication of

32.768 MHz for f 0.)

2

1

COM1

COM2

80

79

COM3

COM4

Alternation

frequency

Note: A cross( X ) indicates that the pin is not used with that duty type.

SO2:Serial output pin

SO3:Serial clock pin

Static duty

32 Hz32 Hz

Function

1/2 duty

32 Hz

output

options.

1/3 duty

42.7 Hz

The same as for K1

to K4

type:

The outp ut levels on

pins N1 to N4 can be

specified as an opti on

LCD drive

*:Determined by

mask options

General purpose

outputs

Note:

These pins go to

the static drive

mode during the

reset

The static drive

waveform is output

during the reset

period.

*There are cases

where the

alternati ng

frequenc y stops for

the CF,RC and

external clock

specifica tions.

(These cases differ

dependi ng on option

specifica t

At reset

All se gm ents on

All se gm ents off

High level

Low level

Determined by

mask options

When a

combinatio n of

LCD drive and

general-

purpose

outputs,the

output state is

either:

All lit/hig h level

All off/low level.

period.

ions.)

Option

Tran sis tors to hold

alowor high level

Selecti on of either

pull-up or pulldown resistors

Interna l serial clock

divisor selecti on

I1/1

II 1/2

III 1/4

Pins N1 to N4

output circuit

Pins N1 toN4

output

level

Tran sistors to hold

a low or high level

Select ion of either

pull-up or pulldown resistors

Signal convers ion

(rising/f alling)

selectio n

*Only when the

input resisto r open

specificat ion is

selected

LCD driver/

general-purpose

output switching

LCD drive type

switching

STATIC

1/2 bias-1/2

duty

1/2 bias-1/3

duty

1/2 bias-1/4

duty

1/3 bias-1/3

duty

1/3 bias-1/4

duty

General-purpose

output circuit

switching

CMOS

P-channel

open drain

N-channel

open drain

Output latch control

in sta ndb y modes

1/4

duty

32

Hz

Page 10

IC BLOCK DIAGRAM & DESCRIPTION

IC702 PST600 (Regulator)

1

2

3

IC901 LA9242 (Servo)

FIN2

1

FIN1

2

E

3

F

4

5

TB

TE-

6

TE

7

TESI

8

9

SCI

10

TH

11

TA

12

TD-

13

TD

14

JP

15

TO

64

VCC1

I/V

-

+

1

2

3

LDS

63

APC

+

-

T.SERVO

VCC

GND

Vout

LDD

62

TE

& T

+

-

PH1

BH1

60

61

RF DET

VCA

VCABAL

.LOGIC

F.SERVO & F.LOGIC

+

-

VR

LF2

59

58

VCC2

REF1

FSS

56

57

DRF

55

54

CE

53

CL

DAT

525150

CLK

DEF

49

REF

48

NC

47

TBC

46

U-COM

INTER FACE

SLC

-

+

-

+

RF Amp

SPINDLE SERVO

-

+

-

+

SLED SERVO

+

-

45

44

43

42

41

40

39

38

37

36

35

34

33

FSC

DGND

SLI

SLC

RFS-

RFSM

CV+

CV-

SLOF

HFL

TES

TOFF

TGL

JP+

16

FD

PIN FUNCTION

1 FIN2

2 FIN1

3 E

4 F

5 TB

6 TE7 TE

8 TESI

9 SCI

10

TH

11 TA

12 TD13 TD

14 JP

15 TO

16 FD

17 FD18 FA

19 FA20

FE

17

18

FA

FD-

21 FE22 AGND

23 NC

24 SP

25 SPG

26 SP27 SPD

28 SLEQ

29 SLD

30 SL-

19

20

FE

FA-

31 SL+

32 JP33 JP+

34 TGL

35 TOFF

36 TES

37 HFL

38 SLOF

39 CV40 CV+

- 9 -

2221

FE-

AGND

25

23

24

SP

NC

SPG

41 RFSM

42 RFS43 SLC

44 SLI

45 DGND

46 FSC

47 TBC

48 NC

49 DEF

50 CLK

27

28

26

SP-

SPD

29

SLD

SLEQ

51 CL

52 DAT

53 CE

54 DRF

3130

SL-

SL+

32

JP-

61 BH1

62 LDD

63 LDS

64

Vcc1

55 FSS

56 Vcc2

57 REF1

58 VR

59 Lf2

60 Ph1

Page 11

IC BLOCK DIAGRAM & DESCRIPTION

IC902 LC78622 (Digital Signal Processor)

EFMO VVDDVV

9

SS

PDO ISET FR PCK TAI

4

6

357 2

21

TEST2 TEST4

TST11

TEST1 TEST3 TEST5

59 64 11 32 33 62

VDDV

23

SS

8

1

DEFI

EFMIN

FSEQ

CLV+

CLV-

V/P

PW

SBCK

SBSY

SFSY

WRQ

SQOUT

CQCK

COIN

RWC

10

22

12

13

14

49

51

47

50

63

CS

53

55

57

56

54

Slice level

Control

Syncrnous Detect

EFM Demodulation

CLV

Digital Servo

Subcode Dxract

QCRC

µCOM

Inter Fase

Servo Commander

15 16 17 20 19 58 18 24 25 26 27 28 29 48 60 61 46 52 45 44 43 39 41 42 40 37 35 38 36

RESJP+JP-TOFFTESHFL

VCO Clock Oscillator

& Clock Control

General Ports

CONT1

TGL

CONT2

CONT3

CONT4

No. Pin Name I/O Function

1 DEFI I Input terminal for detect signal of defect

2 TAI I Input terminal for test.

3 PDO O The phase comparison output terminal for

external VCO control.

4 VVSS - Ground terminal for built-in VCO

5 ISET I Resistance connection terminal for

electric current adjustment of PDO output.

6 VVDD - Built-in VCO power supply terminal.

7FRIVCO frequency range adjustment.

8 VSS - Ground for Digital

9 EFMO O EFM signal output terminal for slice level control.

10 EFMIN I EFM signal input terminal for slice level control.

11 TEST2 I TEST pin. Normal time is non connection.

12 CLV+ O Output terminal for Disc motor control.

13 CLV- O Output terminal for Disc motor control.

14 V/P O Change of rough servo / phase control

Rough servo : "H", Phase control : "L"

15 HFL I Input terminal of track search signal.

16 TES I Input terminal of tracking error signal.

17 TOFF O Output terminal of tracking off.

18 TGLOOutput terminal for change of tracking gain.

19 JP+ O Output terminal for tracking jump control.

20 JP- O Output terminal for tracking jump control.

21 PCK O Clock monitor output terminal for EFM data

playback. (4.3218 MHz)

22 FSEQ O Output terminal for detect of SYNC signal.

23 DVDD - +5V

24 CONT1 I/O

25 CONT2 I/O This output can control at serial control from

26 CONT3 I/O micro processor.

27 CONT4 I/O

28 CONT5 I/O

29 EMPH O Output terminal of de-emphasis monitor .

"H" : de-emphasis

30 C2F O Output terminal of C2 flag

31 DOUT O Output terminal of digital out

2KÅ~8bit

RAM

C1 C2 Error Detect &

Correct Control Flag

X'tal Root

Timing Generator

4.2M16MEFLGEMPHCONT5

XV

SS

No. Pin Name I/O Function

32 TEST3 I Test pin.

33 TEST4 I Test pin.

34 NC - Non connection.

35 MUTEL O Mute output terminal for L-ch

36 LVDD - Power supply for L-ch

37 LCHOOOutput terminal for L-ch

38 LVSS - GND for L-ch

39 RVSS - GND for R-ch

40 RCHO O Output terminal for R-ch

41 RVDD - Power supply for R-ch

42 MUTER O Mute output terminal for R-ch

43 XVDD -Power supply of crystal oscillation

44 XOUT O Connection terminal of crystal oscillation (16.9344MHz)

45 XIN I Connection terminal of crystal oscillation (16.9344MHz)

46 XVSS - GND of crystal oscillation

47 SBSY O Output terminal for synchronizing signal of

48 EFLGOOutput terminal for correction monitor of C1, C2,

49 PW O Output terminal for sub-cord of P, Q, R, S, T, U and W

50 SFSYOOutput terminal for synchronizing signal of

51 SBCK I Input terminal for readout clock of sub-cord

52 FSX O Output terminal of Synchronizing signal (7.35kHz)

53 WRQOOutput terminal for standby of sub-cord Q output

54 RWC I Input terminal of read / write control

55 SQOUT O Output terminal of sub-cord Q

56 COIN I Input terminal of command from micro processor

57 CQCK I Clock input for reading sub-cord from SQOUT

58 RES I Reset (turn on : L)

59 TST11 O Test pin

60 16M O 16.9344MHz

61 4.2M O 4.2336MHz

62 TEST5 I Test pin

63 CS I Chip select terminal

64 TEST1 I Test pin

- 10 -

XINFSX

XOUT

XV

DD

RAM Address

Generatorl

Interpolalation Mute

Billingual

Digital Attenuator

Quadruple Over Sampling

Digital Filter

1bit DAC

RV

DD

MUTER

RCHO

RV

SS

sub-cord block

Single and Double

sub-cord frame

L.P.F

C2F

30

Digital Out

MUTELLCHO

DD

LV

LV

SS

31

DOUT

(NC)

34

Page 12

IC BLOCK DIAGRAM & DESCRIPTION

1

2

4

3

11

+

ñ

IN

Predriver Power

13

12

Predriver Power

Load short

protector

Overvoltage/

surge protector

Output pin-to-GND

short protector

Output pin-to-V

CC

short protector

Thermal

shutdown

Standby

SW

BIAS

circuit

Ripple

filter

Pop noise

prevention

circuit

V

CC

6

5

8

+

ñ

IN

Predriver Power

9

10

Predriver Power

Load short

protector

Power

GND2

Output pin-to-GND

short protector

Output pin-to-V

CC

short protector

7

14

IC903 LC6541D (4 ch. Bridge CD Driver)

Vcc Vref VIN4 VG4 Vo8 Vo7 GND Vo6 Vo5 VG3 VIN3 CD RES

11k Ω 11k Ω

Vcc

131415161718192021222324

Level

Sift

Level

Sift

123456 789

Vcc Mute VIN1 VG1 Vo1 Vo2 GND Vo3 Vo4 VG2 VIN2 Reg OUT Reg IN

IC904 LC1641 (Motor Driver)

OUT1P1

VCC2

3

2

BTL

Driver

BTL

Driver

OUT2 P2VZVCC

8

10

9

PRE-

DRIVE

BTL

Driver

BTL

Driver

Level

Sift

Level

Sift

11k Ω11k Ω

10 11 12

IC301 LA4725 ( Power)

7

4

RESET

Regulator

IN1

GND

5

1

INPUT LOGIC CIRCUIT

Input Output Action

IN1

IN2

OUT1

0

0

1

0

0

1

1

1

OUT2

0

1

0

0

0

0

1

0

Brake

Normal(Reverse)Rotary

Reverse(Normal)Rotary

Brake

6

IN2

- 11 -

Page 13

SCHEMATIC DIAGRAM (MAIN)

This is a basic schematic diagram.

- 13 -- 12 -

Page 14

WIRING DIAGRAM (CD MAIN, CD DOOR SW, LED1, LED2 and AUDIO)

CD DOOR SW

CD MAIN

LED2 LED1

AUDIO

- 15 -- 14 -

Page 15

WIRING DIAGRAM (DISPLAY and PHONE & REMOTE )

PHONE & REMOTE

- 16 -

DISPLAY

Page 16

WIRING CONNECTION

This is a basic wiring connection .

Apr./ '03 BB Printed in Japan

SANYO Electric Co., Ltd.

OSAKA, JAPAN

Loading...

Loading...