Page 1

SANYO FISHER SERVICE CORPORATION

TRAINING MANUAL

REFERENCE No. TI780010

INTRODUCTION TO THE VB7C

CHASSIS (AVM-2780G)

AS

FGH

A

S

Page 2

– i –

FOREWORD

This technical publication familiarizes service technicians with the C-003 CPU

circuits, the new BUS Controlled Signal Processor, the new MTS Processor,

the new PIP Signal Processor, the new Comb Filter and the new Switching

Power Supply circuits employed in type VB7C color television chassis. The

C-003 CPU is used on all models using the VB7C chassis, which includes the

AVM-2550S, AVM-2580G, AVM-2759S (Chassis No. G5G-2759S2), AVM2760S, AVM-2780G, AVM-3259G (Chassis No. G5R-3259G2/3/4), AVM3260G, AVM-3259S (Chassis No. G5R-3259S1), AVM-3280G, AVM-3650G,

AVM-3680G, PC-25S00, PC-27S90 (Chassis No. G5G-27S901/2), PC-32S90

(Chassis No. G5R-32S901/2) and PC-36S00. The descriptions given in this

manual for the circuit operations use model AVM-2780G for the schematic

nomenclature. Circuit operations for all VB7C chassis will be the same,

however, schematic nomenclature may vary with the model.

Note: This publication should be used only as a training aid. Refer to the

specific service data for information about parts, CPU programming,

safety and alignment procedures.

Safety Information:

All product safety requirements and testing must be completed prior to

returning the television to the consumer. Do not defeat safety features or

fail to perform safety checks. Failure to comply with these safety

procedures may result in damage or personal injury.

Integrated circuits and many other semiconductors are electrostatically

sensitive. Special handling techniques are required when handling these

components.

Many electrical and mechanical parts have special safety related

characteristics, some of which are often not evident from visual inspection,

nor can the protection they give necessarily be obtained by replacing the parts

with components rated for higher voltage, wattage, etc. Such parts are often

identified in the service literature. A common means of identification is

shading or a ★ on the schematic and/or parts list. Always be on the alert for

any special product safety notices, special parts identification etc. Use of a

substitute part that does not have the same safety characteristics can create

shock, fire, and/or other hazards. Use the part recommended in the service

literature.

Page 3

– 1 –

TABLE OF CONTENTS

INTRODUCTION TO THE C-003 CPU • • • • • • • • • • • • • • 2

CPU PROGRAMMING • • • • • • • • • • • • • • • • • • • • • • • • 4

KEY SCAN CIRCUIT • • • • • • • • • • • • • • • • • • • • • • • • • 6

REMOTE CONTROL INPUT • • • • • • • • • • • • • • • • • • • • 8

PLL DATA OUT CIRCUIT • • • • • • • • • • • • • • • • • • • • • • 10

AFT CIRCUIT • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • 12

SIGNAL PROCESSOR BUS CONTROL CIRCUIT • • • • • • 14

MTS PROCESSOR BUS CONTROL CIRCUITS • • • • • • • 16

SOUND CONTROL CIRCUIT • • • • • • • • • • • • • • • • • • • • 18

DIGITAL CONTROL CIRCUITS • • • • • • • • • • • • • • • • • • • 20

POWER ON/OFF and PROTECTION CIRCUITS • • • • • • • 22

TV/AV SWITCHING CIRCUITS • • • • • • • • • • • • • • • • • • • 24

REFERENCE OSCILLATOR • • • • • • • • • • • • • • • • • • • • 26

CRT DISPLAY CIRCUIT • • • • • • • • • • • • • • • • • • • • • • • 27

MEMORY CONTROL CIRCUIT • • • • • • • • • • • • • • • • • • • 28

MOMENTARY MUTE CIRCUIT • • • • • • • • • • • • • • • • • • • 30

AFT DEFEAT CIRCUIT • • • • • • • • • • • • • • • • • • • • • • • • 32

CPU RESET OPERATION • • • • • • • • • • • • • • • • • • • • • • 34

AUTOMATIC BRIGHT LEVEL ADJUSTMENT SYSTEM • • 36

AUTOMATIC RF AGC ADJUSTMENT SYSTEM • • • • • • • 40

CLOSED-CAPTIONING DESCRIPTION • • • • • • • • • • • • • 44

THE CLOSED-CAPTION DECODER SECTION • • • • • • • 46

CAPTION DATA SLICER • • • • • • • • • • • • • • • • • • • • • • • 48

F/S TUNING SYSTEM DESCRIPTION • • • • • • • • • • • • • • 52

PLL OPERATION • • • • • • • • • • • • • • • • • • • • • • • • • • • • 54

PIP CONTROL CIRCUITS • • • • • • • • • • • • • • • • • • • • • • 56

PIP CIRCUITS • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • 58

MTS CIRCUIT • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • 60

COLOR ENHANCER CONTROL CIRCUIT • • • • • • • • • • • 62

COMB FILTER • • • • • • • • • • • • • • • • • • • • • • • • • • • • • • 63

SWITCHING POWER SUPPLY • • • • • • • • • • • • • • • • • • 64

CPU TROUBLESHOOTING HINTS • • • • • • • • • • • • • • • • 70

Page 4

– 2 –

INTRODUCTION TO THE C-003 CPU

The C-003 CPU tuning system is capable of electronically tuning 181 different

channels and is similar to conventional synthesized tuning systems described

in earlier training manuals. The major difference between the C-003 and

previous C-983 CPU systems is the additional circuits for the new BUS

Controlled PIP Signal Processor and the new BUS Controlled MTS

Processor.

The C-003 is a multi-purpose CPU and uses the On-screen Service

Adjustment Menu to program the options available for each model.

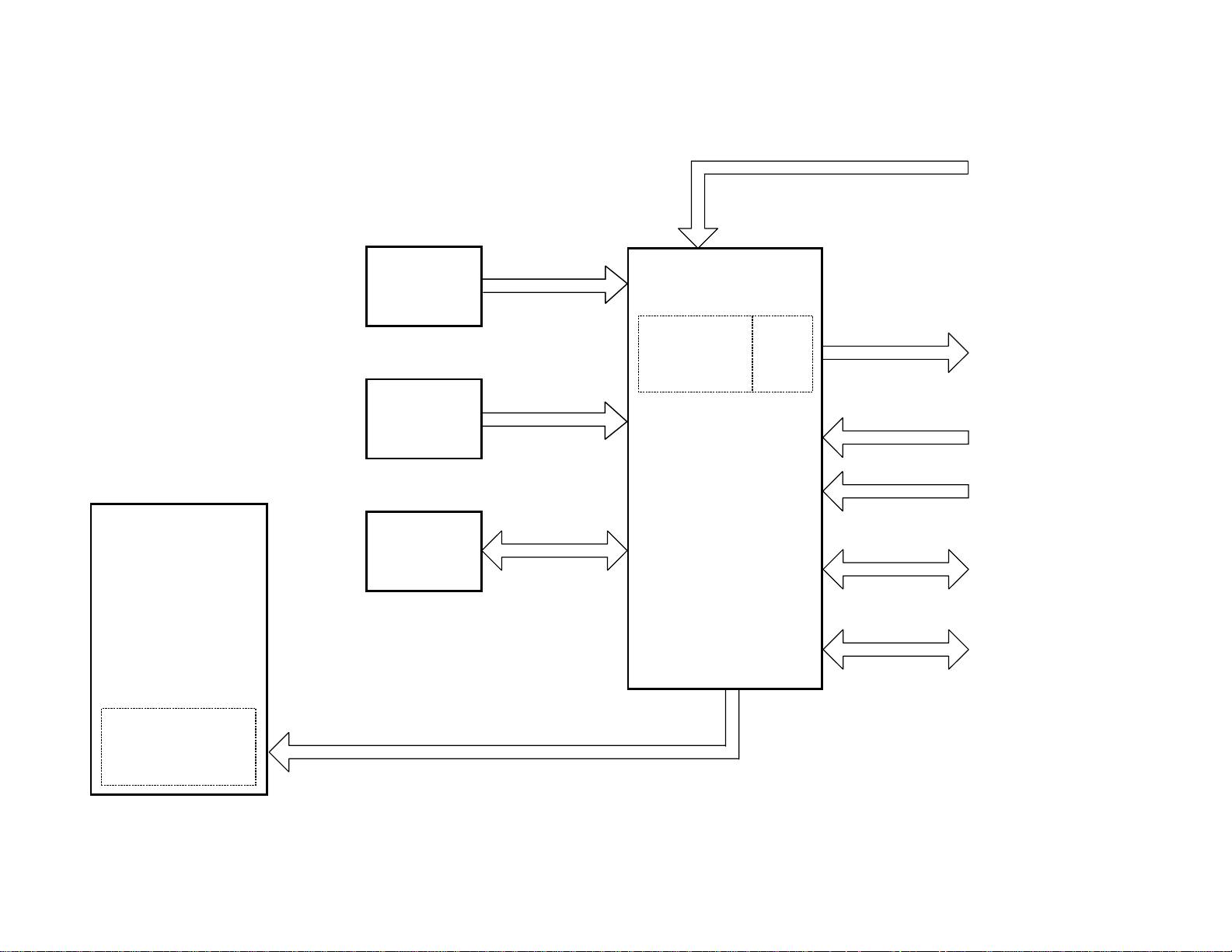

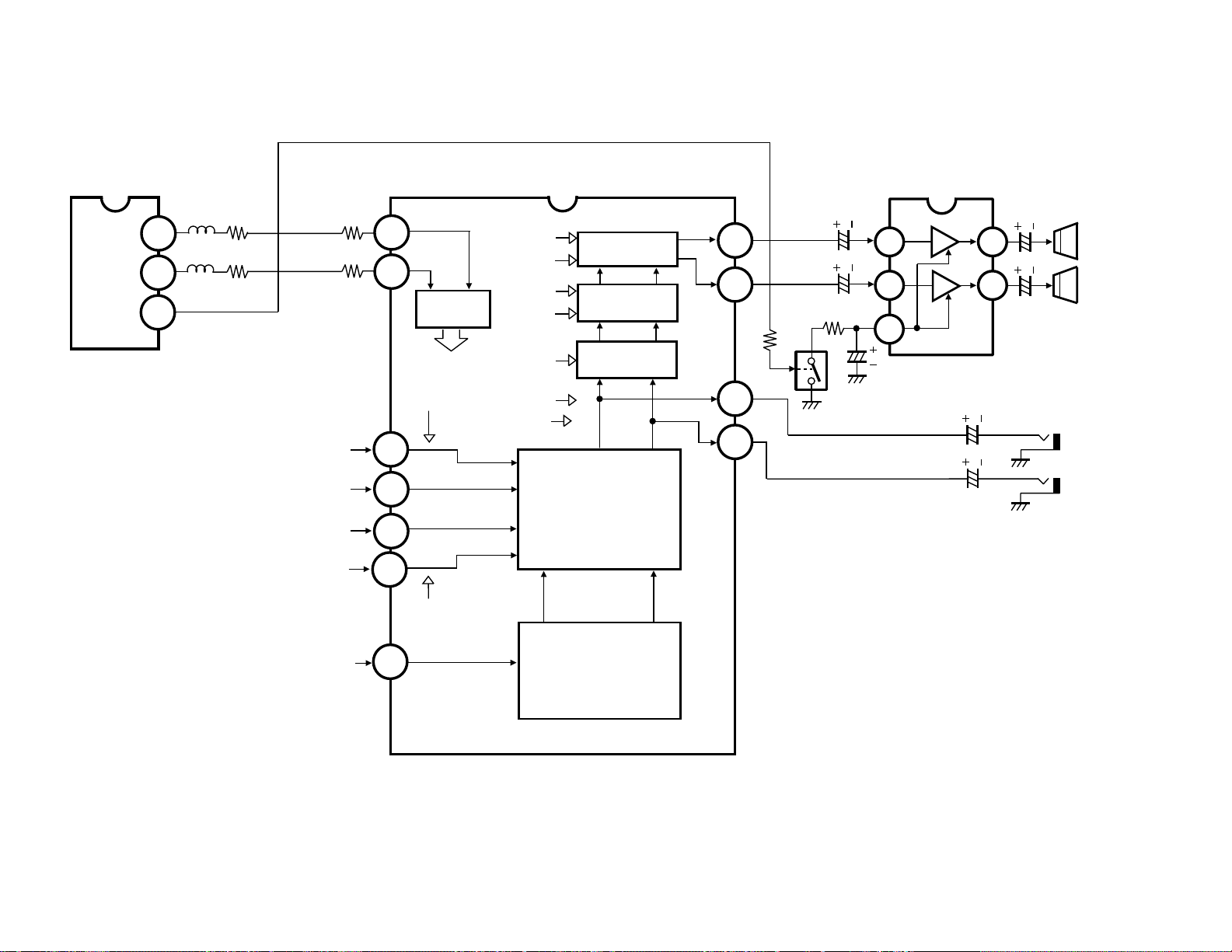

The block diagram of the C-003 frequency synthesizer (F/S) tuning system

and the BUS control circuits is shown in the diagram below. An outline of the

operation of each block is given below.

A. CPU

The CPU is the nucleus of the system, controlling each block according to the

signals input from the keyboard or remote control transmitter. The basic

function which the CPU controls are as follows:

1. Blanking and multi-color CRT signals for the on-screen displays

2. Time of Day clock and Sleep Timer function

3. Auto Program, Channel Memory function

4. Auto Shut-Off function (Turns TV OFF if no video signals are received

for 15 minutes)

5. TV/AV input switching function

6. Phase Locked Loop function (PLL) (programmable divider and phase

detector)

7. Power supply protection function

8. Digital control functions for picture and audio

9. Trilingual (English/Spanish/French) On-Screen menu system

10. AFT search function

11. Caption Data Slicer

12. V-Guide control function

13. Color Enhancer control function

14. On-screen Service Adjustment Menu system

15. Automatic RF AGC adjustment system

16. Automatic Bright Level adjustment system

17. Signal Processor BUS control function

18. MTS Processor control function

19. Front Surround control function

20. PIP control function

21. EEPROM control

B. Key Matrix

1. Produces DC voltages for the keyboard input.

C. BUS Control Output Circuit

1. Outputs the BUS data from the CPU to each control register within the

UHF/VHF tuner, the new Signal Processor, the new PIP Signal

Processor, and the new MTS Processor.

D. EEPROM (Nonvolatile Memory)

1. Stores channel memory, antenna mode, customer settings of digital

control, caption mode, and language mode.

2. Stores the BUS data used for factory/service adjustment.

E. RF AGC A/D Input Circuit

1. Detects and resistive divides the RF AGC voltage supplied from the

new Signal Processor to match with the A/D input of the CPU.

F. Beam Current Detector

1. Detects and converts the CRT beam current from the flyback

transformer to DC voltages for the A/D input of the CPU.

G. Remote Control Input

1. Amplifies and couples the remote control data to the CPU.

Page 5

– 3 –

C-003 Tuning System Block Diagram

RC

PRE-AMP

COMPOSITE

VIDEO

TUNER

PLL

PRE-SCALER

BAND SW

KEY

BOARD

EEPROM

CAPTION

DATA SLICER

CPU

(C-003)

OSD

DISPLAY

RF AGC

A/D INPUT

BEAM CURRENT

DETECTOR

DIGICON

SOUND

AV

MTS

PIP

AFT

BUS CONTROLLED

SIGNAL PROCESSOR

Page 6

– 4 –

CPU PROGRAMMING

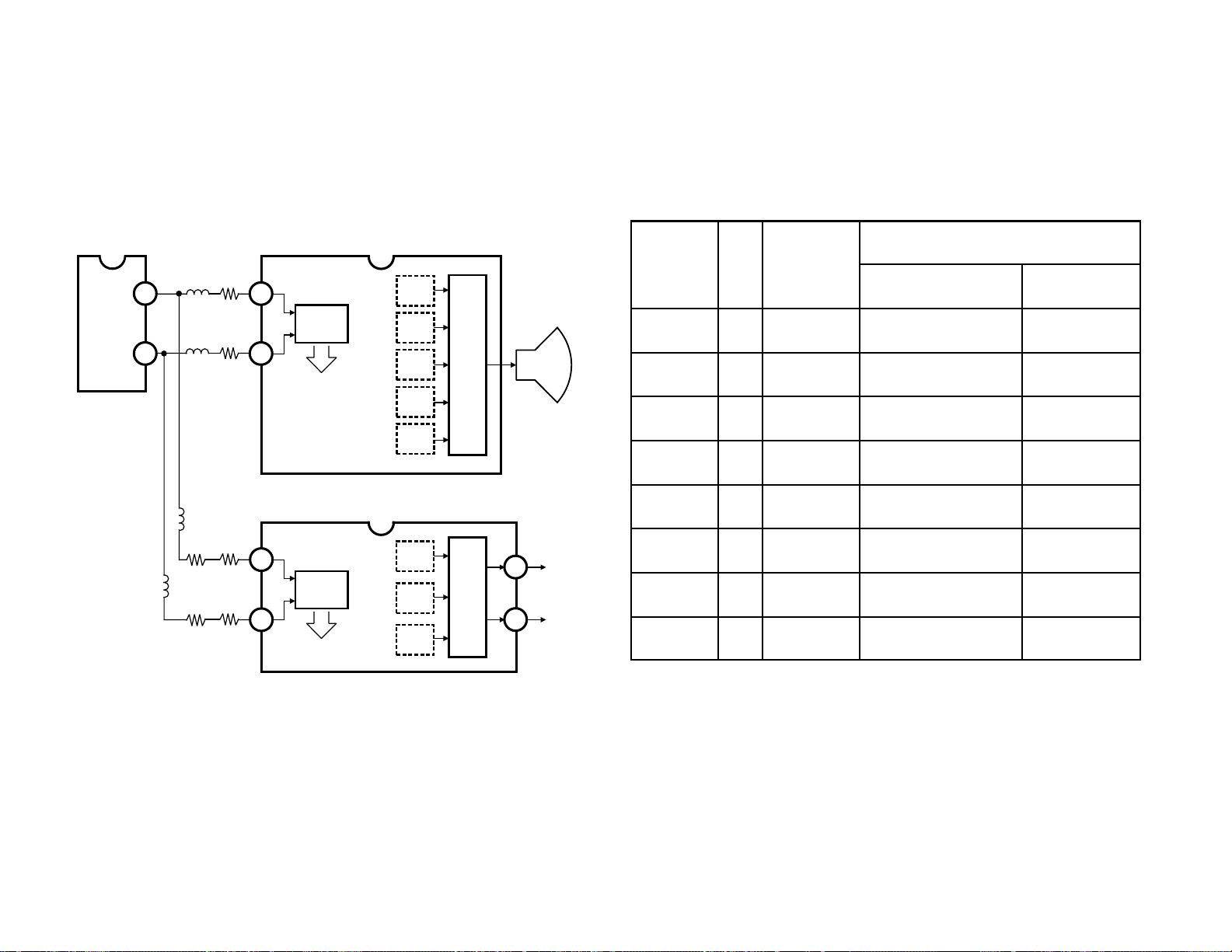

The On-screen Service Adjustment Menu system employed in the VB7C

chassis replaces the resistors used to change the voltage on the option pins

of the previous CPU. In order to program the CPU for the different options

available for the VB7C chassis, the On-screen Service Adjustment Menu is

used to change the option data in IC802, the EEPROM.

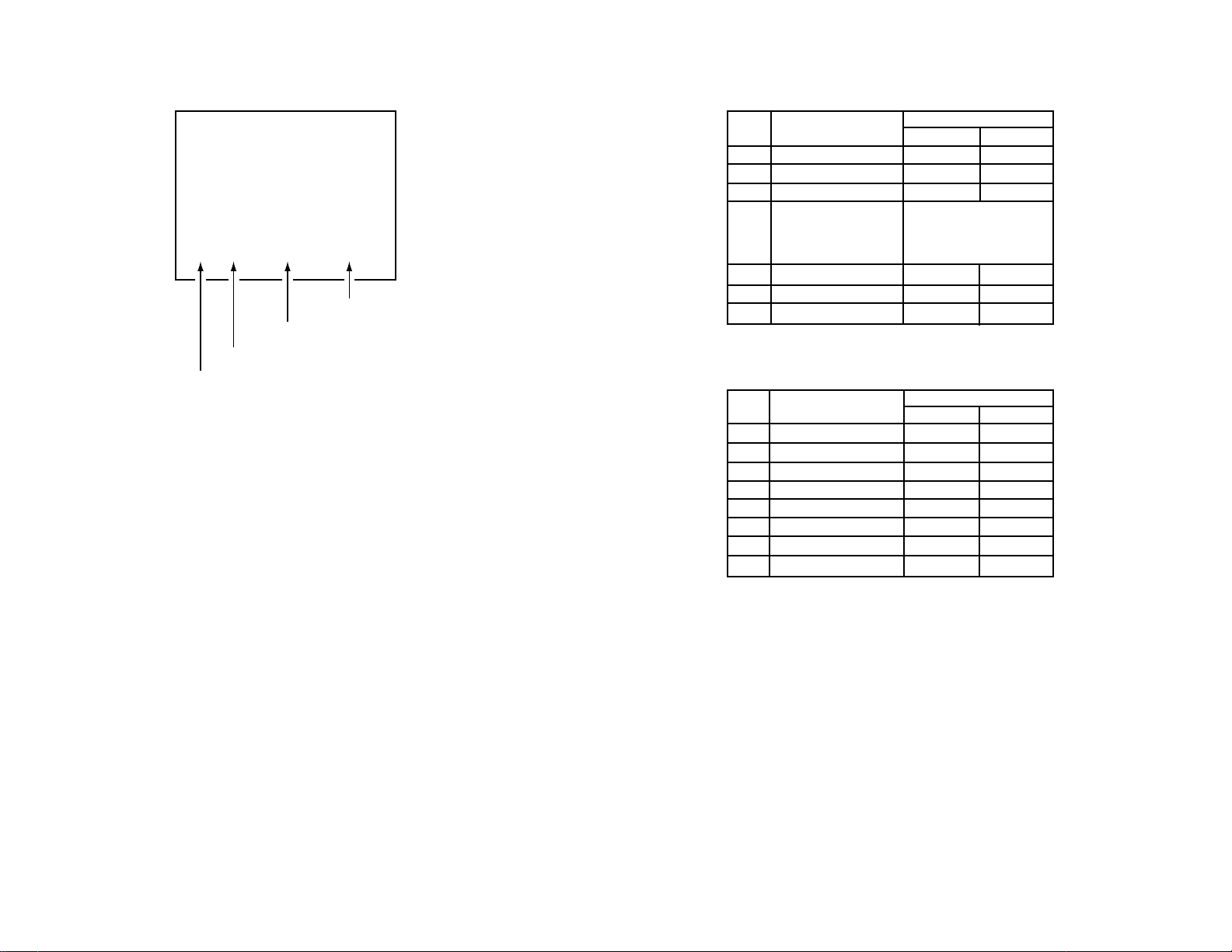

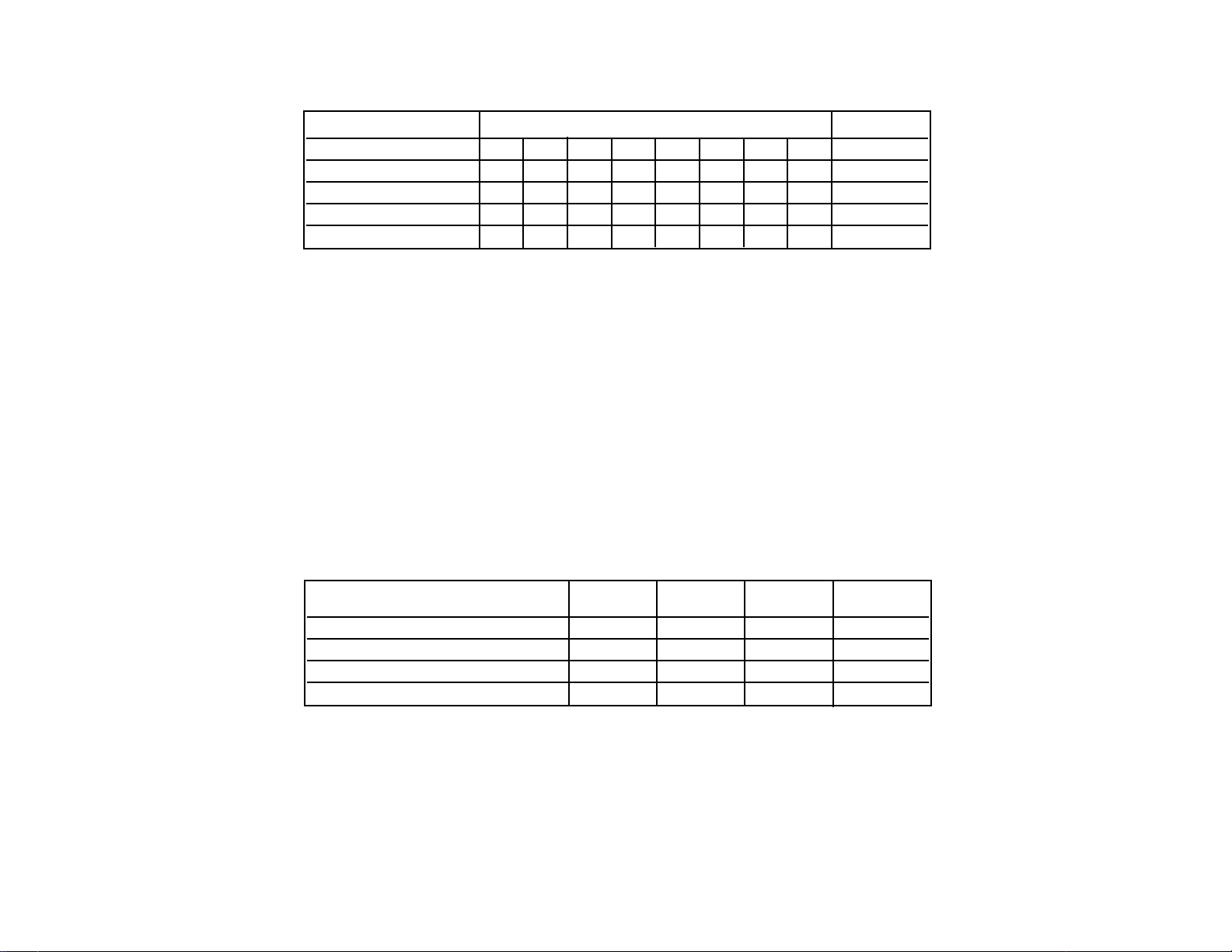

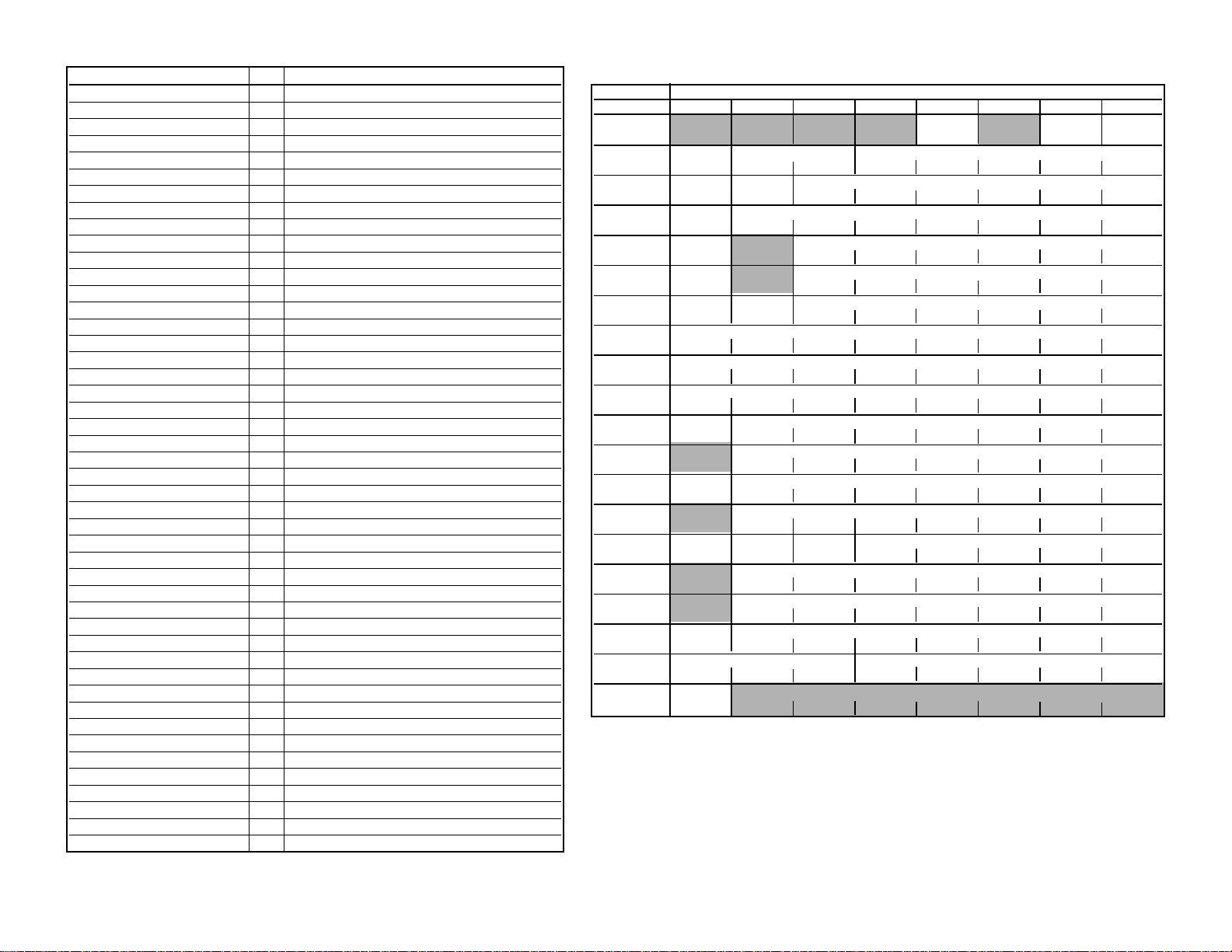

The Service Adjustment Menu display shown below and the following table

show the different options available and the necessary data. The option data

shown are for Mode AVM-2780G and include these options: with Clock, with

Surround, with Software for PIP Rating Information Processing, with Color

Enhancer, with Initial Channel, with PIP, with 2 AV Inputs, and with Bass &

Treble controls.

Memory Control Circuits

IC801

CPU

R808

ALWAYS

5V

L801

IC802

EEPROM

C801

IIC

SCL

IIC

SDA

33

31

R807

6

5

SCL

SDA

Page 7

– 5 –

PROGRAM CODES

The microprocessor used in the VB7C chassis is a multi-purpose type and is

used in several different models. To ensure proper operation and the correct

features for your particular model, the Program Codes must be correct.

Note: To enter the service adjustment menu, connect the AC power cord

while pressing the MENU key. The service adjustment can be made

with the remote control. To exit the service adjustment mode, press the

MENU key again. Refer to the specific Service Manual for your model

for complete adjustment procedure.

* . . . .When the Initial Channel option is used, the Initial Channel (the TV can

be set automatically to tune to a specific channel each time it is turned

on.) and XDS (Extended Data Service) features are available.

BIT FUNCTION

DATA

01

0 NOT USED

–– ––

1 NOT USED

–– ––

2 NOT USED

–– ––

00: NONE

3, 4 CLOCK 01: YES (AC 60 Hz)

10: YES (INT OSC)

11: INHIBITED (=NONE)

5 NOT USED

–– ––

6 SURROUND NONE YES

7 NOT USED –– ––

BIT FUNCTION

DATA

01

0 PIP RATING INFO.

–– ––

1 COLOR ENHANCER NONE YES

2 INITIAL CHANNEL NONE YES *

3 NOT USED –– ––

4 PIP NONE YES

5 AV1 / AV1, AV2 AV1 AV1, AV2

6 TONE / BASS, TREBLE BASS, TRE. TONE

7 NOT USED

–– ––

NO. DATA

XXX OPT XXX XXXXXXXX

DECIMAL DATA (ZERO SUPPRESSED)

NO. 29, 30

TITLE OPT, OP2

BINARY DATA (8 bit)

Option Data 1

Option Data 2

Page 8

– 6 –

Key Scan

The Key Scan circuit uses an analog circuit to generate and send voltage to

the CPU when a key is pressed. The CPU uses this voltage to determine

which key was pressed. This resistive circuit eliminates the need for

encoder/decoder devices, simplifying design and adding to the reliability of

the receiver.

The CPU performs a key scan approximately every 20ms to check for a

pressed key. When the key data change is the same for two consecutive

reads, it is determined that a key has been pressed and the corresponding

command executed.

The table below shows the voltages input to CPU pin 9 when a given key is

pressed.

Key Input

The function of the keys on keyboard and those of the remote control

transmitter are the same.

The following keys, when activated, perform a series step action. The time of

each series step action is also shown below.

A . CH Up/Down 500 ms/step.

B . Vol Up/Down 140ms/step. It takes about 9 seconds to change from

minimum to maximum volume.

Preceding and succeeding mutes are performed when turning power Off/On,

changing channels, switching Antenna mode, searching channels, changing

MTS or TV/AV mode, exchanging programs between the main screen and

PIP window, or switching Surround sound mode.

Channel and Mode Change Mutes

Key Scan Voltages

KEY INPUT VOLTAGE FUNCTION

SW1901 4.26 ~ 5.00 POWER

SW1902 3.63 ~ 4.26 VOL +

SW1903 3.01 ~ 3.63 VOL SW1904 2.38 ~ 3.01

CH ▲

SW1905 1.60 ~ 2.38

CH ▼

SW1906 1.13 ~ 1.60 MENU

OFF 0.00 ~ 1.13

–––

KEY SCAN CIRCUIT

PRESSING KEY

MODE OUTPUT

MODE CHANGE

PRECEDING

MUTE

MUTE SIGNAL MUTE OFFMUTE ON

SUCCEEDING

MUTE

Page 9

– 7 –

IC801

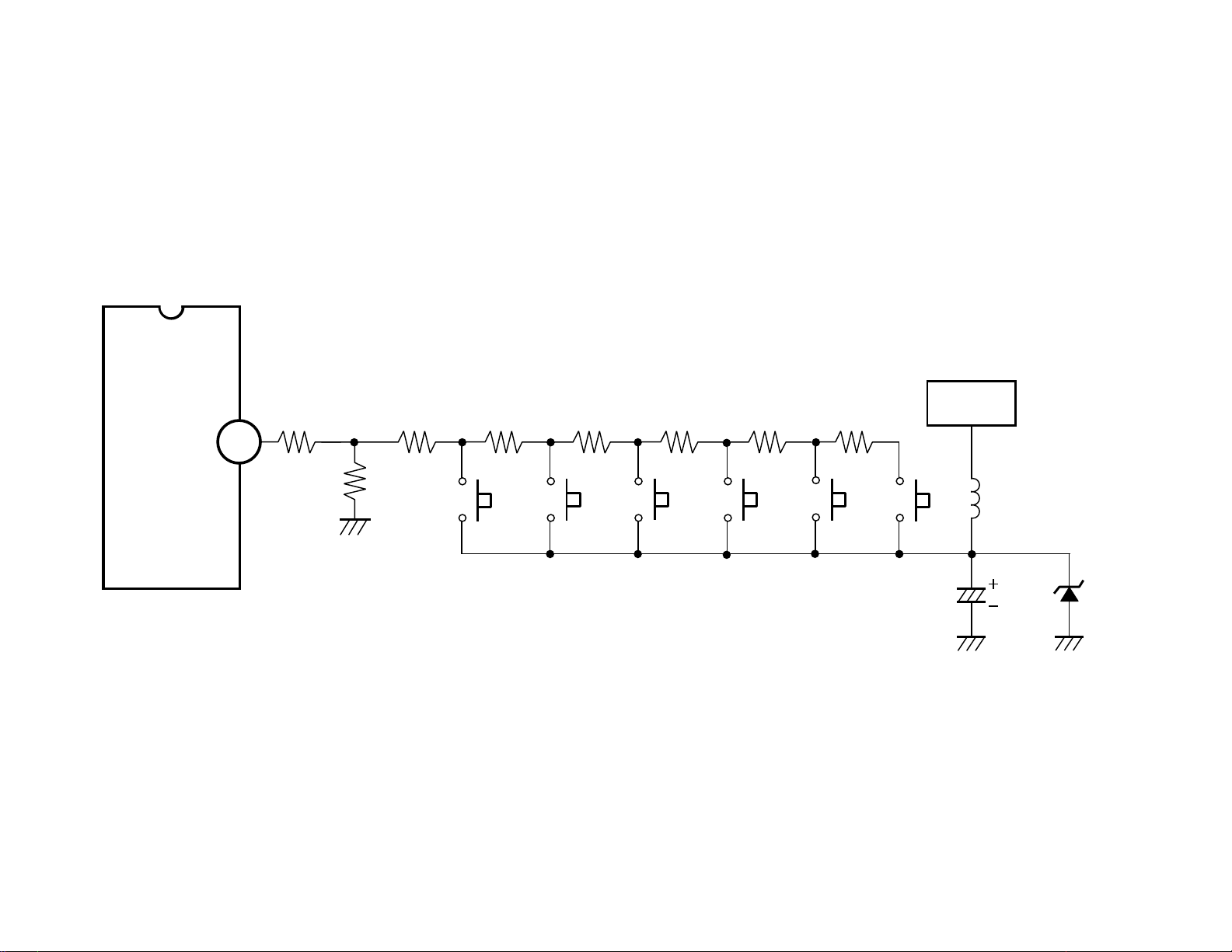

Key Scan Circuit

CPU

ALWAYS

R1910

R1907R1906R1905R1904R1903R1902

5V

9

R1901

L1901

SW1901

(POWER)

SW1902

(VOL + )

SW1903

(VOL – )

SW1904

(CH ▲ )

SW1905

(CH ▼ )

SW1906

(MENU)

C1902

D1901

(7.5V)

Page 10

– 8 –

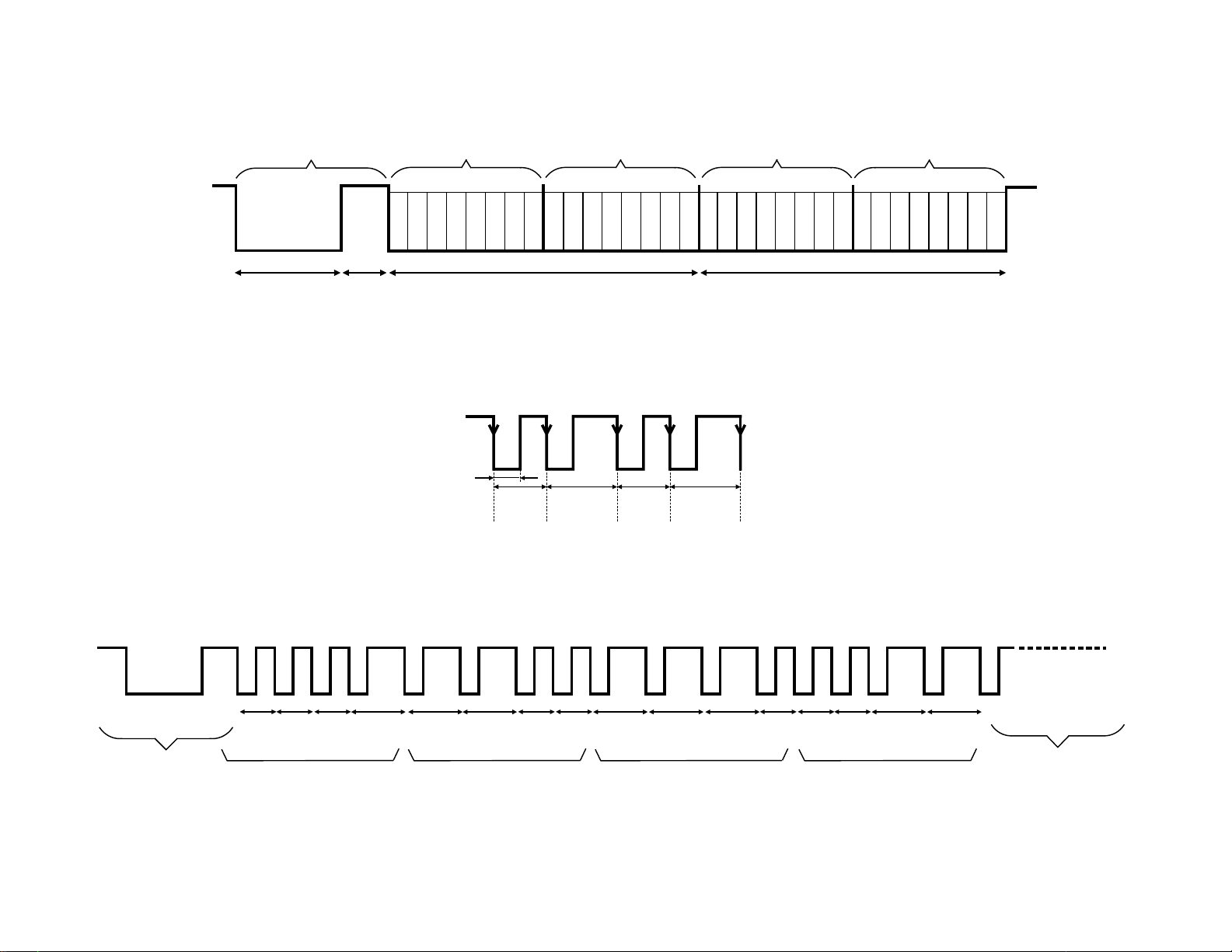

REMOTE CONTROL INPUT

The data received from the remote control is first amplified to 5 V digital

pulses by the pre-amplifier module A1901 and then input to the CPU on pin

10. See Remote Transfer Code figure below. The remote data is a transfer

code consisting of a leader code, an 8-bit custom code, and an 8-bit data

code. A signal transfer code is 32 bits which allows the custom and data

codes to be sent twice, once in the normal mode and then inverted. This

provides a type of redundancy check to prevent misoperation.

Custom and Data codes differentiate between the “1” and “9” values by the

pulse duration. See “1” and “0” Pulse Duration diagram below.

The custom code is a unique code assigned to each manufacturer.

Its purpose is to help prevent operation of the TV by remote controls for other

components such as VCRs, CD players etc. The code assigned to our

company is 38H. See Custom Code figure below. The data code is the

command, or channel number.

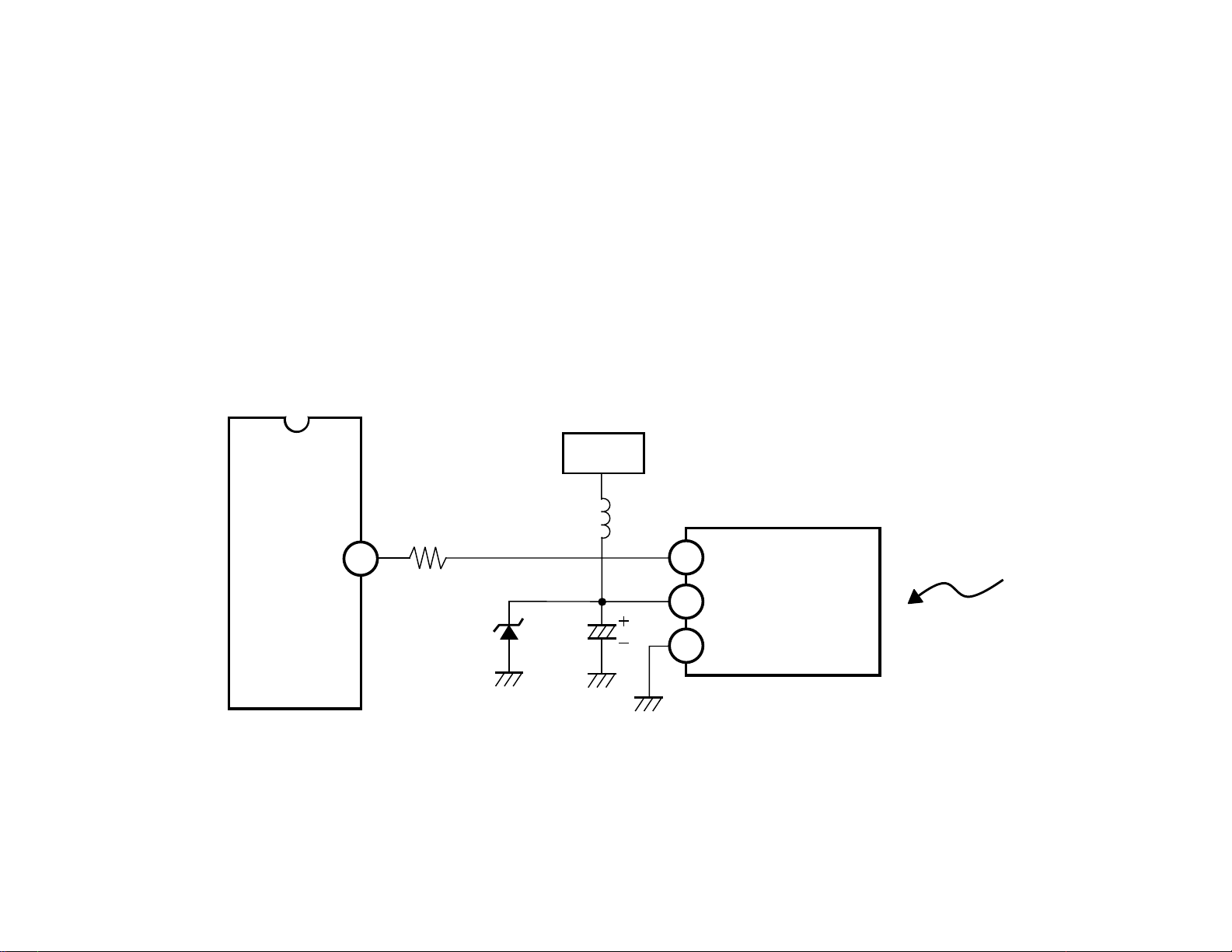

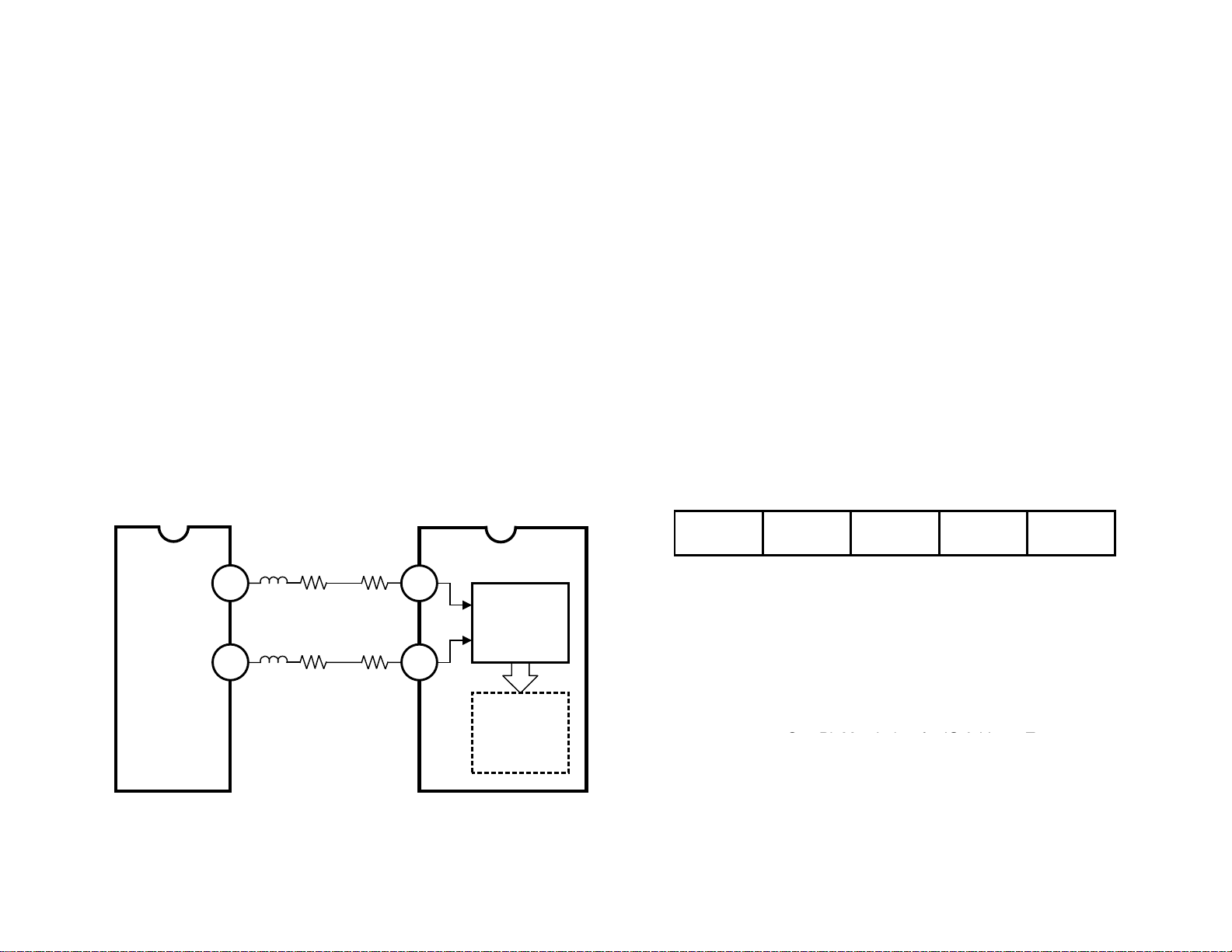

Remote Input Circuit

IC801

CPU

L1901

R1909

10

ALWAYS

5V

1

A1901

RC PRE-AMP

D1901

(7.5V)

2

C1902

3

Page 11

– 9 –

LEADER CODE CUSTOM CODE CUSTOM CODE DATA CODE DATA CODE

C0C1C2C3C4C5C6C7

Remote Transfer Code

0.56msms

1.125ms 2.25ms 1.125ms 2.25ms

" 0 " " 1 " " 0 " " 1 "

"1" and "0" Pulse Duration

D0D1D2D3D4D5D6D7

27ms9ms 4.5ms 27ms

0

000

LEADER CODE DATA CODE

111

00

111

00

1

1

Custom Code

Page 12

– 10 –

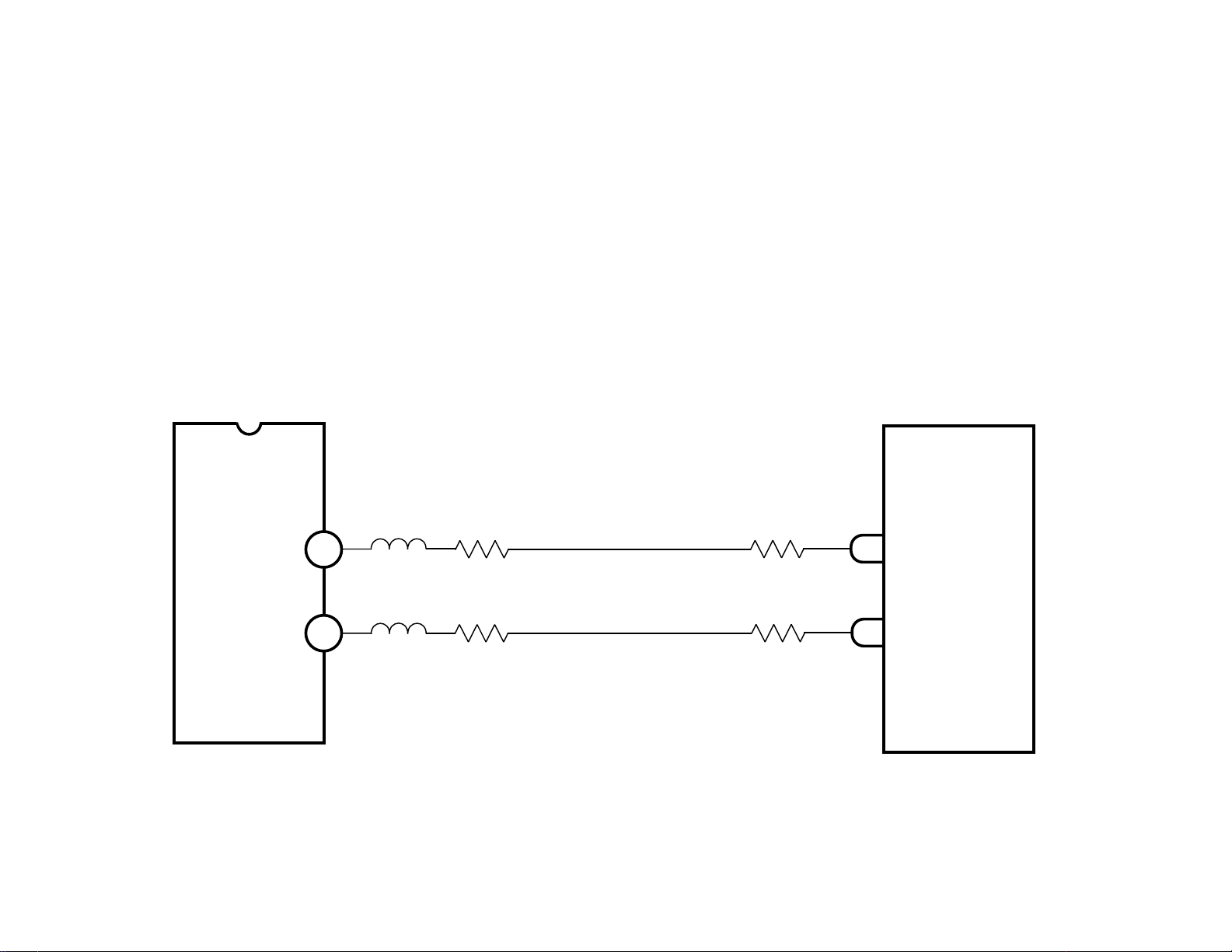

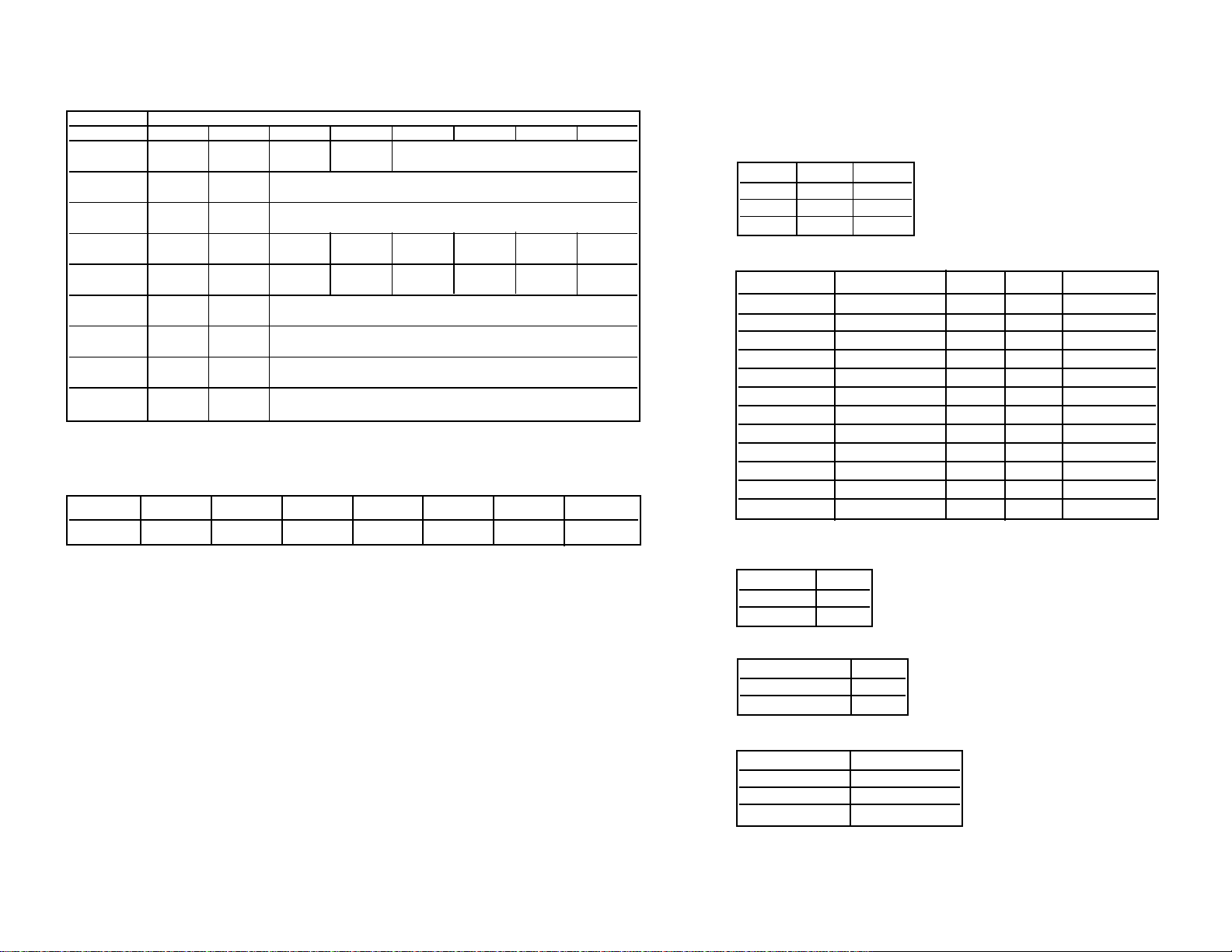

PLL DATA OUT CIRCUIT

The VB7C chassis uses a new BUS-Controlled UHF/VHF Tuner with a builtin Phase Locked Loop, Prescaler and Band Switch. Including these circuits

in the tuner reduced RF radiation and simplified shielding requirements and

printed wiring board layout. The primary difference between this chassis and

the previous chassis (C-983) is the exclusive PLL control lines (PLL Enable,

PLL Data, PLL Clock) are unified to the common BUS control lines (BUS SDA,

BUS SCL), and the BUS control program is incorporated in the CPU (C-003).

Channel selection requires only two inputs from the CPU. These are the Data

signal input from pin 32, and the Clock signal input from pin 34. The Data

signal controls the band switching, the channel selection and the AFT. The

channel selection and the AFT function are controlled by changing the divide

ratio for the PLL.

The tuning data format is composed of 5 byte data. See Tuning Data Format

figure below.

PLL Data Circuit

IC801

CPU

BUS

SDA

L881

32

R881

A101

TUNER

R856

DATA

BUS

SCL

34

L882

R882

R857

CLOCK

Page 13

– 11 –

BYTE (MSB) DATA BYTE (LSB) COMMAND

Address byte (ADB) 1 1 0 0 0 MA1 MA0 0 A

Divider byte 1 (DB1) 0 M9 M8 M7 M6 M5 M4 M3 A

Divider byte 2 (DB2) M2 M1 M0 S4 S3 S2 S1 S0 A

Control byte (CB) 1 CP T1 CD X 1 1 0 A

Band switch byte (BB) X X X X BU FMT BVH BVL A

PLL Data Format

A • • • • • • • • • • • • • • acknowledge

MA1 and MA2 • • • • • address selection bits

M8~M0, S4~S0 • • • • programmable divider bits

CP • • • • • • • • • • • • • charge pump current (tuning speed) switch control

T1 • • • • • • • • • • • • • test mode selection

CD • • • • • • • • • • • • • charge pump defeat switch control

X • • • • • • • • • • • • • • don’t care bit

BU • • • • • • • • • • • • • UHF band switch control

FMT • • • • • • • • • • • • FM trap (92.5MHz) switch control at channel 6

BVH • • • • • • • • • • • • VH band switch control

BVL • • • • • • • • • • • • VL band switch control

BAND BU FMT BVH BVL

VL (WITHOUT CH 06 ONLY) L L L H

VL (CH 06 ONLY) L H L H

VH L LHL

UHF H L L L

Band Switch Control Data

Page 14

– 12 –

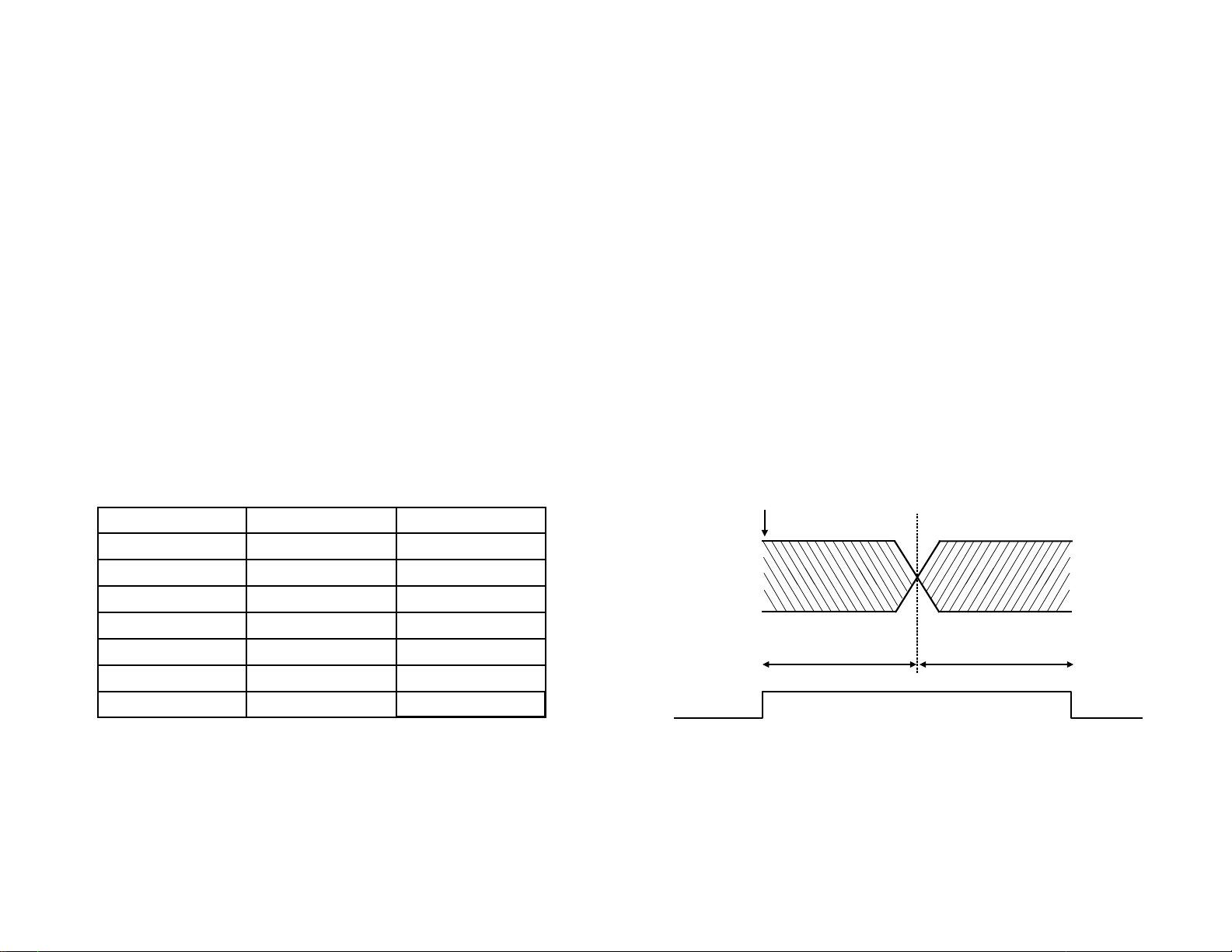

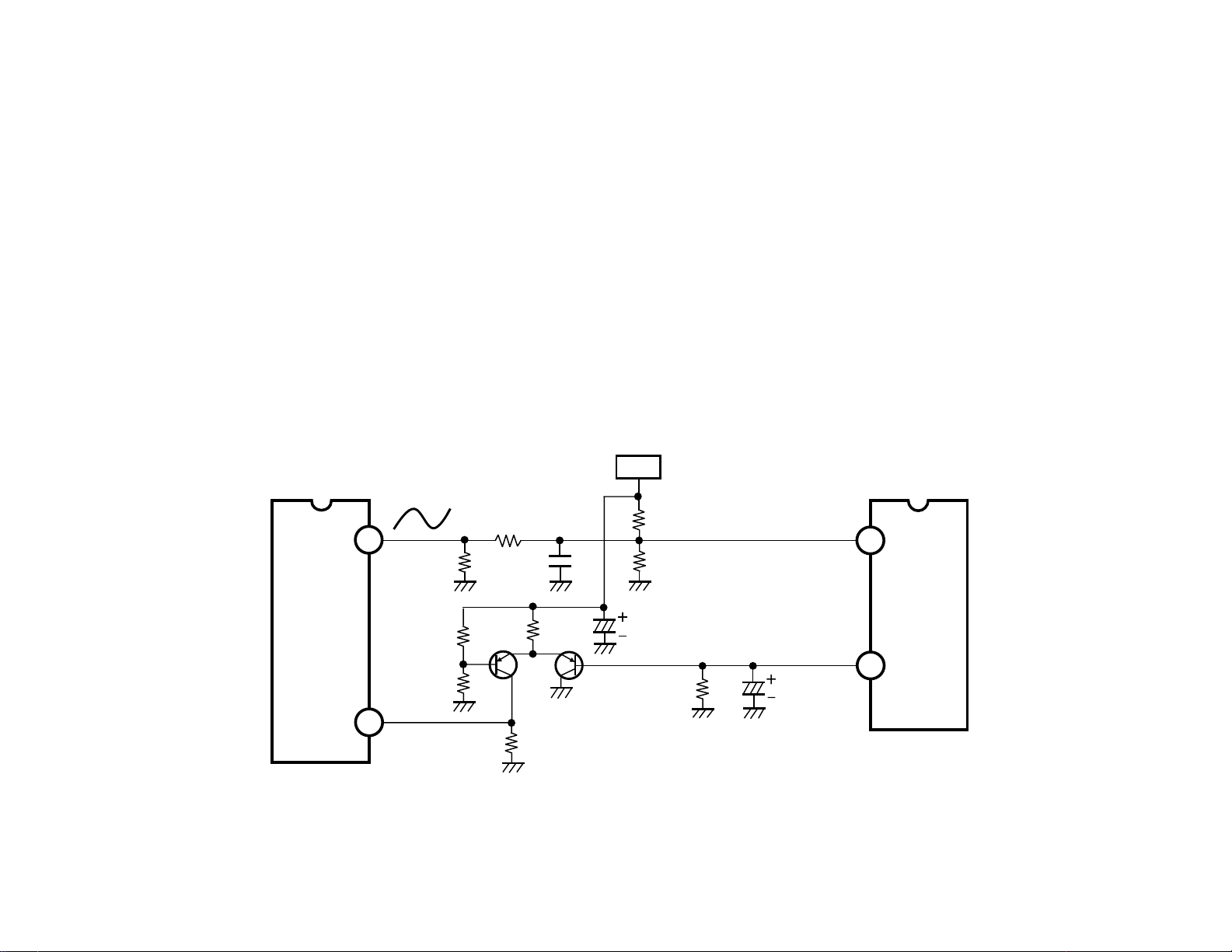

AFT CIRCUIT

The Automatic Fine Tuning (AFT) program incorporated in the CPU functions

to fine tune the tuner local oscillator to the center of the actual broadcast

frequency. This is necessary because the transmitted TV signal may not be

exactly on its assigned channel frequency. In addition, certain CATV

channels are purposely slightly offset to reduce interference from broadcast

frequencies. The operating range of the AFT is ± 2.25 MHz from FCC center.

Specifically, the AFT searches the frequency band ± 2.25 MHz from FCC

center in 62.5 KHz steps by changing the PLL division ratios while evaluating

the binary signals from IC101, the Signal Processor.

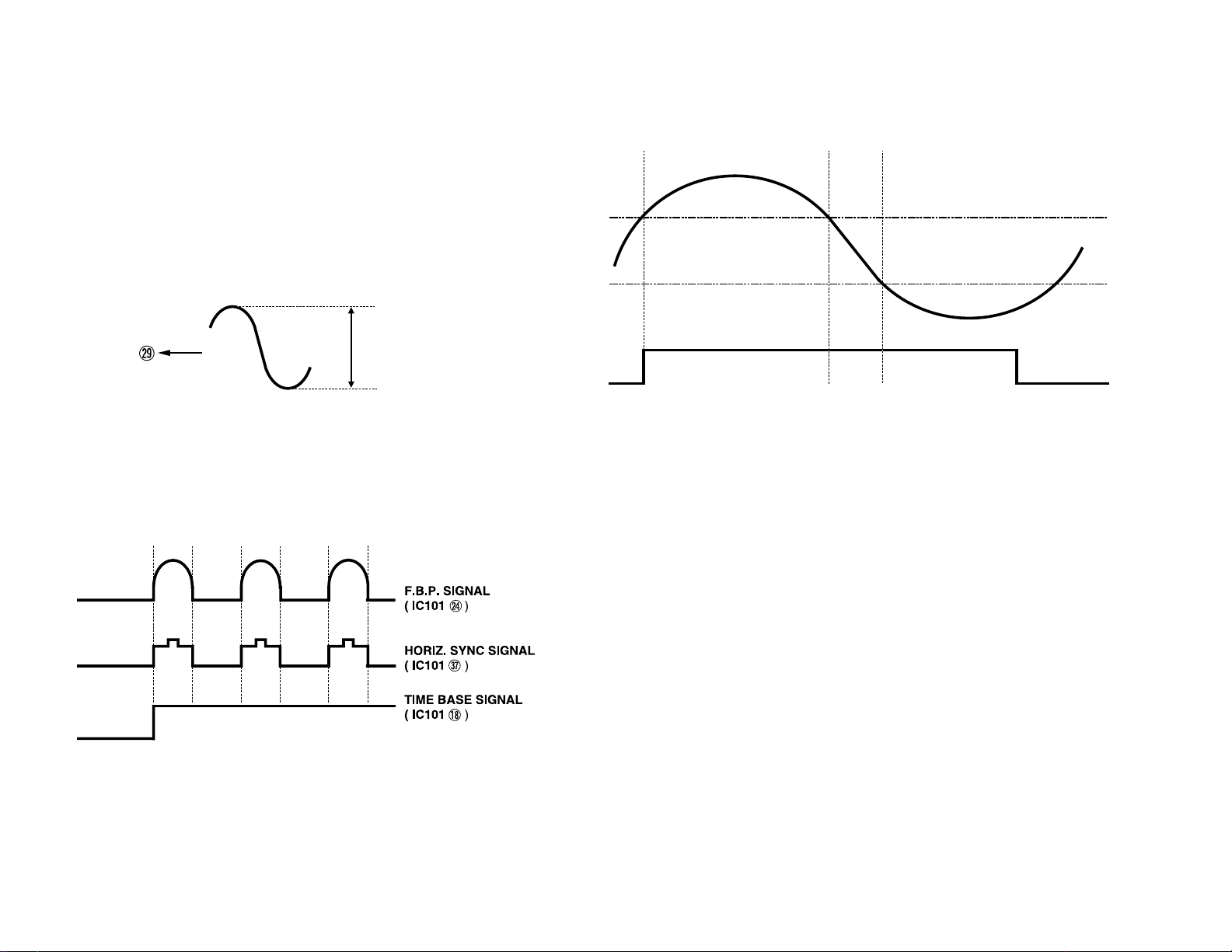

The station center is determined to have been found when the Time Base

signal at pin 26 is High and the AFT S-Curve signal at pin 29 is between 3.3

VDC and 1.67 VDC. However, the slope (right down) is also checked to

distinguish the station center from a pseudo-tuning point.

The Time Base signal is the AND signal of the horizontal sync signal from the

flyback transformer and the horizontal sync signal from the video (Y) signal.

The AFT S-Curve signal is an indication of the video IF carrier frequency

45.75 MHz.

The Time Base and AFT S-Curve signals are checked after each stepping

action. If station center cannot be confirmed after a complete search of the

upper and lower limits of the AFT range, the frequency is returned to FCC

center and the AFT action ceased.

The AFT only operates when first entering the channel. When entering the

channel C05 or C06, the operating range of the AFT is ± 2.25MHz from FCC

center +125 KHz (2 steps).

AFT Circuit

IC801

CPU

R167

AFT

S-CURVE

29

R168

C161

7.6 V

IC101

SIGNAL

PROCESSOR

R161

13

R162

TIME

BASE

26

R371

R377

Q372

R376

R372

Q371

C258

R373

18

C371

Page 15

– 13 –

CPU

RANGE OF 0 ~ 5 V

AFT

S-CURVE

TIME BASE

SIGNAL

3.3 V

1.67 V

TUNING

POINT

AFT S-Curve Signal

Time Base Signal

Station Center

Page 16

– 14 –

SIGNAL PROCESSOR BUS CONTROL CIRCUIT

The VB7C chassis is equipped with a new single-chip BUS-Controlled NTSC

Signal Processor IC to replace much of the mechanically adjusted

factory/service controls and all of the low pass filters in the PWM control lines

for the customer setting digital controls used in the conventional chassis.

The primary difference between this chassis and the conventional chassis is

the addition of the BUS Interface circuit and the movement of the control

registers into the Signal Processor IC, and the BUS control program

incorporated in the CPU (C-003).

The advantages of this chassis include reduced control lines and associated

circuitry, and improved productivity and increased accuracy of the factory

adjustments during production. This is due to the computerized and digitized

control circuit which allows remote operation.

Control of the Signal Processor IC is through CPU pins 32 and 34.

Pin 34 is the BUS SCL (Serial Data) signal. The BUS SDA is a bi-directional

signal and is used to transfer data into and out of the control registers within

IC101. Data is processed through an 8 bit read or write for each sub address

in an IC address “1011010” with in IC101.

See Bit Map below for IC Address,

Sub Address or Data for details.

IC801

CPU

BUS

SCL

BUS

SDA

34

32

L814

L813

SIGNAL PROCESSOR

R804

43

CLK

R803

44

DATA

IC101

BUS

Interface

STA

ICW SUB DA STO

STA = START Condition

ICW = IC Address* + Write

SUB = Sub. Address*

DA = Data*

STO = STOP Condition

Control

Registers

Signal Processor BUS Control Circuit

c

*

See Bit Map below for IC Address,

Sub Address or Data for details.

BUS Data Format In Write Mode

Page 17

– 15 –

Register Name Bits General Description

T Enable 1 Disable the Test SW & enable Video Mute SW

Video Mute 1 Disable video outputs

Sync Kill 1 Force free-run mode

ABL Defeat SW 1 Disable ABL function

AFC Gain 2 Select horizontal first loop gain

Horizontal Phase 5 Align sync to flyback phase

IF AGC SW 1 Disable IF and RF AGC

AFT Defeat 1 Disable AFT output

RF AGC Delay 6 Align RF AGC threshold

Video SW 1 Select Video Signal (INT/EXT)

PLL Tuning 7 Align IF VCO frequency

BNI Enable 1 Enable black noise inverter

Audio Mute 1 Disable audio outputs

APC Det Adjust 6 Align AFT crossover

V Count Down Mode 1 Selected vertical countdown mode

Vertical Test Enable 3 Selected vertical DAC test modes

Vertical DC 6 Align Vertical DC bias

Vertical Kill 1 Disable vertical output

Color Kill 1 Enable Color Killer

Vertical Size 6 Align vertical amplitude

Red Bias 8 Align Red OUT DC level

Green Bias 8 Align Green OUT DC level

Blue Bias 8 Align Blue OUT DC level

Blanking Defeat 1 Disable RGB output blanking

Red Drive 7 Align Red OUT AC level

Drive Test 1 Enable drive DAC test mode

Blue Drive 7 Align Blue OUT AC level

Color Difference Mode Enable 1 Enable Color difference mode

Brightness Control 7 Customer brightness control

Contrast Test 1 Enable Contrast DAC test mode

Contrast Control 7 Customer contrast control

Trap & Delay SW 1 Select luma filter mode

AutoFlesh Enable 1 Enable autoflesh function

Black Stretch Defeat 1 Disable black stretch

Sharpness Control 5 Customer sharpness control

Tint Test 1 Enable tint DAC test mode

Tint Control 7 Customer tint control

Color Test Enable 1 Enable color DAC test mode

Color Control 7 Customer color control

White Peak Limiter Enable 1 Disable White Peak Limiter

G Drive Reduction 4 Select Green OUT AC level

V Size Compensation 3 Selected Gain of V Size Compensation

Video Level 3 Align IF video level

FM Level 5 Align WBA output level

Audio SW 1 Select Audio Signal (INT/EXT)

Volume Control 7 Customer volume control

Control Register Descriptions

IC Address: BAh (10111010)

Sub Address (MSB) DATA (LSB)

D7

• • • • • •

D0 DA7 DA6 DA5 DA4 DA3 DA2 DA1 DA0

$00 ✻✻✻✻T_Enable ✻ Vid_Mute

SSnncc KKiilll

l

(tr0) 1 0 0

$01 ABL DEF AFC Gain H_Phase

(tr1) 1 1 1 0 1 1 1 1

$02 IF AGC SW

AAFFTTDDEEF

F RF_AGC_Delay (Note-1)

(tr2) 0 0 1 1 0 0 1 0

$03 VIDEO SW PLL TUNING

(tr3) 0 1 0 0 0 0 0 0

$04 N/I SW Audio_Mute APC DET ADJUST

(tr4) 1 0 0 1 1 1 1 1

$05 VCD MODE V_Test Ver_DC

(tr5) 0 0 1 0 0 0 0 0

$06

VVeerr KKiillllCCooll KKiilll

l Ver_size

(tr6) 0 0 1 0 0 0 0 0

$07 R_Bias (Note-2)

(tr7) 0 0 0 0 0 0 0 0

$08 G_Bias (Note-2)

(tr8) 0 0 0 0 0 0 0 0

$09 B_Bias (Note-2)

(tr9) 0 0 0 0 0 0 0 0

$0A BLK_DEF R-Drive

(tr10) 0 0 1 1 0 1 1 1

$0B Drv_Test B_Drive

(tr11) 0 0 1 1 0 1 1 1

$0C C_Diff

BBrriigghht

t

(tr12) 0 1 0 0 0 0 0 0

$0D Cot_Test

CCoonnttrraasst

t

(tr13) 0 1 1 1 1 1 1 1

$0E Trap&D_SW A Flesh Black ST

SShhaarrppnneesss

s

(tr14) 0 1 0 1 0 0 0 0

$0F Tin_Test

TTiinnt

t

(tr15) 0 1 0 0 0 0 0 0

$10 Col_Test

CCoolloor

r

(tr16) 0 1 0 0 0 0 0 0

$11 W Peak G Drive Reduction V-Comp.

(tr17) 1 1 0 0 0 0 0 0

$12 VIDEO LEVEL FM LEVEL

(tr18) 1 0 0 0 1 1 1 1

$13 AUDIO SW Volume

(tr19) 1 1 1 1 1 1 1 1

• The shaded data shows fixed data.

• The outlined data can be changed except during the Service Menu mode.

• The data except above can be set with the Service Menu.

• Note-1: shows the data that can be set with the Service Menu or the Automatic Adjustment Menu.

• Note-2: shows the data that can be set with the R/G/B Bias Adjustments in the Service Menu.

Bit Map

Page 18

– 16 –

MTS PROCESSOR BUS CONTROL CIRCUIT

The VB7C chassis is equipped with a new single-chip BUS-Controlled MTS

Processor IC to replace much of the mechanically adjusted factory/service

controls and all of the low pass filters in the PWM control lines for the

customer setting digital controls used in the conventional chassis. In addition,

the Bass, Treble and Volume control circuits have been also integrated into a

single-chip IC.

The primary difference between this chassis and the conventional chassis is

the addition of the BUS Interface circuit and movement of the control registers

into the MTS Processor IC, and the BUS control program incorporated in the

CPU (C-003).

The advantages of this chassis include reduced control lines and associated

circuitry, and improved productivity and increased accuracy of the factory

adjustments during production. This is due to the computerized and digitized

control circuit which allows remote operation.

Control of the MTS Processor IC is through CPU pins 32 and 34.

Pin 34 is the BUS SCL (Serial Clock) signal. The BUS SCL input is used to

clock all data into and out of IC101.

Pin 32 is the BUS SDA (Serial Data) signal. The BUS SDA is a bi-directional

signal and is used to transfer data into and out of the control registers within

IC3401. Data is processed through an 8-bit read or write for each sub

address in an IC address “10000100” (Read Address) or “10000101” (Write

Address) within IC3401.

See Bit Map below for IC Address,

Sub Address or Data for details.

IC801

CPU

IC3401

MTS PROCESSOR

STA

ICA SUB DA STO

BUS

SDA

L881

32

R3401

SDA

5

BUS

R881

Interface

BUS

SCL

34

L882

R882

R3402

6

SCL

Control

Registers

MTS Processor BUS Control Circuit

STA = START Condition

ICA = IC Address* + Read or Write

SUB = Sub. Address* (needed only in Write mode)

DA = Data*

STO = STOP Condition

c

*

See Bit Map below for IC Address,

Sub Address or Data for details.

BUS Data Format in Write Mode

Page 19

– 17 –

IC Write Address: 84h (10000100)

Sub Address (MSB) DATA (LSB)

D7

• • • • • •

D0 DA7 DA6 DA5 DA4 DA3 DA2 DA1 DA0

00h ✻✻TEST-DA TEST 1 ATT (Note-1)

00

01h ✻✻ SPECTRAL (Note-2)

02h ✻✻ WIDEBAND (Note-2)

03h ✻ M2 EXT1 EXT2 NRSW FOMO SAPC M1

(Note-5) (Note-3) (Note-3) (Note-4) (Note-4) 0 (Note-5)

04h ✻ PSW ✻ SURR ATT SW ✻ FEXT1 FEXT2

0 (Note-6) 0 0 0

05h ✻✻ BASS (Note-7)

06h ✻✻ TREBLE (Note-7)

07h ✻✻ VOL-L (Note-8)

08h ✻✻ VOL-R (Note-8)

• Note-1: ATT for the Input Level Adjustment.

• Note-2: SPECTRAL for the High Separation and WIDEBAND for Low Separation

Adjustments.

• Note-3: EXT1 and EXT2 for the AV Selection.

• Note-4: NRSW for Stereo/SAP Selection and FOMO for Forced Mono Selection.

Mode EXT1 EXT2

TV 0 0

AV1 1 0

AV2 1 1

Mode selected Receiving Signal NRSW FOMO Output Signal

MONO Mono 0 ✻ MONO

Stereo 0 1 MONO

SAP + Mono 0 1 MONO

SAP + Stereo 0 1 MONO

STEREO Mono 0 1 MONO

Stereo 0 0 STEREO

SAP + Mono 0 1 MONO

SAP + Stereo 0 0 STEREO

SAP Mono 0 1 MONO

Stereo 0 0 STEREO

SAP + Mono 1 0 SAP

SAP + Stereo 1 0 SAP

• Note-5: M1 for TVOUT Mute and M2 for LSOUT Mute functions. LSOUT Mute is

accomplished by M2 and Volume Mute.

Mode Data

MUTE ON 0

MUTE OFF 1

• Note-6: SURR for Surround On/Off Selection.

Mode Data

SURROUND OFF 0

SURROUND ON 1

• Note-7: BASS for Bass Control and TREBLE for Treble Control.

Control Level Data

MAXIMUM 3Fh (111111b )

CENTER 1Fh (011111b)

MINIMUM 00h (000000b)

• Note-8: VOL-L for L-Channel Volume Control and VOL-R for R-Channel Volume

Control.

IC Read Address: 85h (10000101)

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

POWER STEREO SAP NOISE –– –– –– ––

✻: Don’t care bit.

POWER=1 : Reset

STEREO=1 : Stereo is present.

STEREO=0 : Stereo is absent.

SAP=1, NOISE=0 : SAP is present.

SAP=1, NOISE=1 : SAP is absent.

SAP=0 : SAP is absent.

Page 20

– 18 –

SOUND CONTROL CIRCUIT

The sound level is controlled by the BUS control signal form the CPU, the

BUS SDA (Serial Data) signal from pin 32, and the BUS SCL (Serial Clock)

signal from pin 34. The BUS control signals from the CPU are coupled to the

BUS Interface circuit within IC3401, the MTS Processor. The BUS Interface

circuit transfers a 6-bit volume data into both of the Volume Control Registers

VOL-L and VOL-R. A 6-bit volume control data from each of the Volume

Control Registers is converted to a 0-63 steps analog signal (DC voltages) in

the Volume D/A converter for input to the Volume Control Circuit. Now the

audio signal is output from pins 3 and 4 of IC3401.

The volume control data “000000” and the audio mute control data “0” are

input to the Volume Control Registers VOL-L and VOL-R, and the Audio Mute

Control Register M2 (Sub Address 03h, Bit 6), respectively to set the output

sound level to step 0/63 during Mute ON. (See page 30 for the Audio Mute

Control Register M2.)

In addition, the CPU outputs the Mute (High) signal from pin 38 to prevent

buzz or static in the speakers when turning On/Off or during Standby mode.

The Mute (High) is coupled to the base of Q001, switching Q001 On,

grounding pin 5 of the Audio Amplifier IC001.

BUS Data Format in Write Mode - Volume Level at 16/63 step

STA ICW SUB DA STO

D6

D5

D4

D7 D0D1D2D3

D0D1D2D3

D7

D6

D5

00000011

STA: START Condition

ICW: IC Address + Write

SUB: Sub. Address

DA : Data

STO: STOP Condition

D4

DA7

1000001

✻✻010000

1

DA6

DA5

DA4

DA1

DA2DA3

(LSB)(LSB) (LSB) (MSB)(MSB)(MSB)

DA0

IC WRITE ADDRESS

D6

D5

D4

D7

D6

D7 D0D1D2D3

SUB. ADDRESS

D5

D4

00000011 00100000

IC WRITE ADDRESS

SUB. ADDRESS

Don't care bits

DA7D0D1D2D3

DA6

DA5

DA4

VOL-L

(LSB)(LSB) (LSB) (MSB)(MSB)(MSB)

DA0DA1DA2DA3

✻✻010000

Don't care bits

VOL-R

Page 21

– 19 –

Sound Control Circuit

IC801

CPU

BUS

SDA

BUS

SCL

MUTE

32

34

38

L881

L882

R881

R882

R3401

R3402

AV1-R

AV1-L

AV2-R

33

34

36

5

6

BUS

Interface

to BUS Line

FEXT1

IC3401

MTS PROCESSOR

VOL-R

VOL-L

TREBLE

BASS

SURR

M2

EXT1/EXT2/M1

VOLUME

CONTROL

BASS/TREBLE

CONTROL

SURROUND

BLOCK

AUDIO SW

3

4

38

39

IC001

AUDIO AMP.

C002

R

L

8

10

C001

C007

R011

R012

R

L

Q001

MOMENTARY

MUTE

5

C3437

C3435

C010

SP901

3

1

C011

R

SPEAKER (R)

SP902

L

SPEAKER (L)

K1011

FIXED

AUDIO OUT (R)

K1021

FIXED

AUDIO OUT (L)

AV2-L

SIF In

37

13

FEXT2

MTS DECODER

BLOCK

Page 22

– 20 –

DIGITAL CONTROL CIRCUITS

Digital electronic controls replace the mechanical customer controls. This

provides a more precise setting of the controls as well as allowing the

convenience of remote operation. The BUS data output from the CPU for

each Control Register are essentially the same as those previously described

for the Sound Control Circuit.

The BUS Interface circuit (see diagram below) is necessary to transfer each

control data in the BUS data from the CPU into a corresponding Control

Register in the Signal Processor IC101, and the MTS Processor IC3401.

After accessing the on-screen main menu system with the MENU key and

selecting the Picture/Sound Manual adjustment menu with the CH ▲ / ▼ and

VOL – / + keys, digital control is carried out by pressing the MENU key for

seven separate controls. the CH ▲ / ▼ key is used to select the control to

be changed. Each time a CH ▲ / ▼ key is pressed, the mode will advance

to the next control. The sequence is: Color, Tint, Contrast, Brightness,

Sharpness, Bass and Treble. the active control will be displayed on the

screen and then can be adjusted with the VOL – / + keys.

It takes 140 ms per step to change the control level with the VOL – / + keys.

There are 64 step control level changes in each control mode with the output

characteristics of each control mode independent of the others. When a VOL

– / + key is pressed it takes approximately 5 seconds to change from center

to minimum or center to maximum. The BUS data changes for the controls

are the same as those shown for the volume control.

When the FACTORY PRESET mode is selected with the RESET key, the

Picture/Sound controls will return to the factory settings. During FACTORY

PRESET mode the settings are as follows: COLOR 32/64*

1

, TINT 32/64*1,

CONTRAST 64/64*

2

, BRIGHTNESS 32/64*3, SHARPNESS 32/64*4, BASS

32/64, TREBLE 32/64. Furthermore, the FACTORY PRESET mode clears all

the other customized settings.

When the FACTORY PRESET mode is selected, the customized settings of

the digital controls will be reset. If desired, customized settings can be made

again using the on-screen menu.

*

1

A 7-bit control data up to 127 steps are output for each control register.

One and one half of the customer control steps (1.5x64 =96 steps) are

assigned for customer setting and the remainder (31 steps) are

provided for service adjustment.

*

2

A 7-bit control data up to 127 steps are output for this control register.

One and one half of the customer control steps (1.5x64 =96 steps) are

assigned for customer setting and the remainder (31 steps) are always

output.

*

3

A 7-bit control data up to 127 steps are output for this control register.

64 steps are assigned for customer setting and the remainder (63

steps) are provided for service adjustment.

*

4

A 5-bit control data up to 31 steps are output for this control register.

One fourth of the customer control steps (1/4x64=16 steps) are

assigned for customer setting and the remainder (15 steps) are

provided for service adjustment.

Page 23

– 21 –

Output Range of BUS Data

IC801

FUNCTION BTS

OUTPUT

RANGE OF

BUS DATA

RANGE OF STEPS

CUSTOMER

CONTROL

SERVICE

ADJUSTMENT

Color 7 0 ~ 127

(0~64)/127x1.5

=0/127~96/127

(0~31)/127

=0/127~31/127

Tint 7 0 ~ 127

(0~64)/127x1.5

=0/127~96/127

(0~31)/127

=0/127~31/127

Contrast 7 31 ~ 127

(0~64)/127x1.5+31/127

=31/127~127/127

(0)/127

=0/127

Brightness 7 0 ~ 127

(0~64)/127

=0/127~64/127

(0~63)/127

=0/127~63/127

Sharpness 5 0 ~ 31

(0~64)/31x1/4

=0/31~16/31

(0~15)/31

=0/31~15/31

Volume 6 0 ~ 63 0/63~63/63 ––

Bass 6 10 ~ 54 10/63~54/63 ––

Treble 6 10 ~ 54 10/63~54/63

––

CPU

BUS

SDA

BUS

SCL

32

34

L813

L814

R803

R804

44

43

SIGNAL PROCESSOR

IC101

Color

BUS

Interface

to BUS Line

Tint

Contrast

Brightness

Sharpness

Write

7 bit

Write

7 bit

Write

7 bit

Write

7 bit

Write

5 bit

CRT

Video/Chroma

Processing Circuit

R881

L882

R882

L881

R3401

5

R3402

6

Digital Controls

IC3401

MTS PROCESSOR

Volume

-L/R

BUS

Interface

to BUS Line

Treble

Bass

Write

6/6 bit

Write

6 bit

Write

6 bit

3

MTS Signal

4

Processing Circuit

R-OUT

L-OUT

Page 24

– 22 –

POWER ON/OFF and PROTECTION CIRCUITS

Power On/Off

The CPU performs the On/Off function through pin 27. In the Power On mode

pin 27 changes from Low to High, forward biasing Q681. When Q681

switches On, the base of Q627 will become Low, forward biasing Q627.

When Q627 (+12V Sw.) switches On, forward bias will be applied to Q486

(+9V Reg.). When Q627 switches On, current will flow through relay RL601,

closing the contacts and applying AC power to the degaussing circuit.

In the Power Off mode, pin 27 of the CPU will become Low. Q681 will now

be switched Off, switching Off Q627. Then Q486 (+9V Reg.) will switch Off.

With Q627 Off, current will cease to flow through RL601, opening the

contacts.

Power Supply Protection

The C-003 CPU provides a power source protection function to automatically

switch Off the power if an abnormal condition occurs in the chassis power

supplies to help prevent secondary damage.

Detection of an abnormal condition is accomplished by monitoring the +4.8V

(IC301 VDD), +7.6V and the +9V DC supplies at pin 3 of the CPU.

Pin 3 is normally High, approximately 5V (Vcc). If, while the power is On, pin

3 becomes Low (0.4 VCC or less) for a continuous period of approximately 1.5

seconds, pin 27 (power) of the CPU will be switched Low, shutting Off the

power.

If, while the power is Off, the power is switched On and pin 3 remains Low for

a period of approximately 3.0 seconds, pin 27 will be switched Low, shutting

Off the power.

In circuit operation, if all +4.8V, +7.6V and +9V supplies are their normal

potential, the diodes D312, D801, and D489 will be reversed biased. With all

diodes Off, a High of 5V will be input to pin 3 of the CPU. Should either +4.8V,

+7.6V, or +9V supply become 2V or less, one of the diodes will switch On,

forcing a Low at pin 3 of the CPU. The input to pin 3 is evaluated every 20

ms.

Note: The C-003 CPU provides a Power Surge Protection feature. If power

failures occur three times within 15 minutes, the CPU will automatically

stop functioning to help prevent secondary damage. (TV will not turn

On by pressing the POWER key.) To reset the operating programs

within the CPU, disconnect the AC power cord for at least 10 seconds.

Auto Shut Off Function

The Auto Shut Off feature operates to switch the TV Off if no video signal is

received for a certain period of time. The Time Base signal is used within the

CPU to determine the presence of an active channel. If pin 26 of the CPU

goes Low for a continuous period of approximately 15 minutes, the CPU

program will determine that no active channel is present and activate the Auto

Shut Off feature. The Auto Shut Off has priority over the Sleep Timer function,

however, it is inactive when the TV is in the AV (Video) mode.

Anode Current Leak Protection

The VB7C chassis provides an anode current leak protection circuit to

automatically switch Off the power to help prevent the risk of fire if an

abnormal condition such as high voltage arcing occurs on the picture tube

anode or in the high voltage circuits due to accumulated dust or liquid spilled

into the TV cabinet.

Detection of an abnormal condition is accomplished by monitoring the Heater

voltage supply at pin 3 of the CPU. Since the high voltage arcing on the

picture tube anode or in the high voltage circuits causes excessive current

flows and lower voltage supplies from the secondary windings of the Flyback

Transformer (T402), the excessive current flows are effectively monitored.

In circuit operation, the normal potential Heater voltage, approximately

22VDC higher than the zener voltage (15V) of D428, is applied to the cathode

of D428, diode D429 will be reversed biased.

With D429 Off, a High of 5V will be input to pin 3 of the CPU. Should the

cathode voltage of D428 become 15.2V or less, D429 will, switch On, forcing

a Low at pin 3 of the CPU.

Page 25

– 23 –

Power and Protection Circuits

TIME BASE

26

IC801

CPU

POWER

ON/OFF

TIME

BASE

POWER

FAIL

27

3

+12V

B4

ALWAYS

+5V

R852

C629

R835

C683R683

TJ2

R628

Q681

IC681

+5V REG

D801

D312

Q627

R627

D680

R629

R691

D629

(20V)

+7.6V

+4.8V

D311

(5V)

C626

R311

L623

D683

TJ7

D493

(7.5V)

D624

POSISTOR

R498C497C258

R310

R489

RL601

PS601

T601 (POWER)

AC IN

L901

DEGAUSSING

COIL

TJ5

D489

(7V)

R428

+9V

D428

(15V)

C484D429

D482

D486

(10V)

R482

Q486

R486

R487

T402 (F.B.T)

CRT HEATER

R497

Page 26

– 24 –

TV/AV SWITCHING CIRCUITS

The VB7C chassis (AVM-2780G) provides for the input of Auxiliary Video and

Audio signals.

When the AV1 or AV2 mode is selected from the remote control, pin 8 of the

CPU will go High. The High from pin 8 is coupled to the base of Q216. The

High coupled to the base of Q216 will switch Q216 On and ground the base

of Q343, the Band Pass Switch. The Low at the base of Q343 will switch

Q343 Off, cutting off L341 and C343 from the Band Pass Filter. This will

flatten the response curve of the Band Pass Filter to compensate for the

differences in the frequency characteristics of the AV video signal and the TV

video signal. This compensation will help to maintain a constant chroma

signal (3.58 MHz) gain.

The selection of the TV Audio, AV1 Audio or AV2 Audio signal is controlled by

the MTS Processor IC3401 through the CPU IC801. All of the TV, AV1 and

AV2 audio inputs are applied to an audio switch within IC3401 which is

controlled by the BUS interface.

CPU TV/AV Switching Signal

The selection of the AV1 S-Video, AV1 Composite Video, or AV2 Video signal

is controlled by the CPU and the mechanical switch of AV1 S-Video input jack

K1051.

When the AV1 is selected, pin 5 of the CPU will be Low. When the AV2 is

selected, pin 5 of the CPU will go High.

When the AV1 S-Video is connected during AV1 mode, pin 10 of IC1001 and

pin 12 of the CPU will be forced Low. With the Low at pin 12, the CPU will

regard the S-Video as connected and output the High signal from pin 4.

The selection of the TV Video or AV Video signal in the Signal Processor

IC101 is controlled by the CPU IC801. Both of the TV and AV video signals

are applied to an input switch within IC101 which is controlled by the BUS

interface. Either of the video signals is applied to the Comb Filter IC301 and

coupled to the Main S1/V1/V2 Switch IC1081.

Note: • Using the AV1 S-Video Input jack overrides the AV1 Composite

Video Input jack during the AV1 mode.

TV/AV Mode Switching Signal

AV1

MODE TV S-VIDEO COMPOSITE AV2

VIDEO

CPU (4) L H L L

CPU (5) –– L L H

CPU (8) L H H H

CPU (12) H L H H

CPU (6) –– L L H

CPU (7) L H H H

AV1

MODE TV S-VIDEO COMPOSITE AV2

VIDEO

IC1001 (9) –– L L H

IC1001 (10) H L H H

IC1001 (11) H H H H

IC1002 (9) –– L L H

IC1002 (10) –– L L H

IC1002 (11) L H H H

IC1081 (9) L H L L

IC1081 (10) L H L L

IC1081 (11) –– L L H

Page 27

– 25 –

TV

TV/AV Switching Circuit

ANT

K1051

S1 IN

K1002

V2 IN

K1001

V1 IN

C

A101

TUNER

Q162

1ST

VIDEO

SIGNAL PROCESSOR

10

11

45

47

1

EXT V IN

INT V FOR PIP

Y

IC101

BUS

Interface

VIDEO

DET.

44

43

38

40

42

Q202

BUFFER

Y

C

Q8065

BUFFER

Q306

BUFFER

INPUT

FILTER

Q307

BUFFER

+9V

IC1001

S1/V1/V2

SWITCH

V1

IC801

CPU

BUS SDA

32

BUS SCL

34

MUTE

38

TV/AV

8

16 15 14 13 12 11 10 9

HLH L

1 2 3 4 5 6 7 8

S1-SW

MAIN AV1/AV2

PIP TV/AV

PIP AV1/AV2

MAIN S SELECT

Y1

12

5

7

6

4

R1027

V2

HL

C1C1

R1007

Q8073

BUFF.

INPUT

FILTER

Q8097

BUFFER

Q8093

BUFFER

Q8090

BUFFER

Q8076

BUFFER

Q1071

BUFFER

PIP SIGNAL PROCESSOR

SCL

25

SDA

ACK

PIP

CVBS IN

MAIN Y

MAIN C

Y OUT

C OUT

Interface

24

23

13

49

51

47

SWITCH

45

BUS

YC SEP

PIP

IC8001

PROCESSOR

PIP

FIXED AUDIO OUT (R)

FIXED AUDIO OUT (L)

K1011

K1021

SP901

SPEAKER (R)

SP902

SPEAKER (L)

(R)

(L)

IC001

AUDIO AMP.

3

1

IC3401

MTS PROCESSOR

R

38

L

39

R

3

L

4

8

10

5

6

13

34

37

33

36

SDA

SCL

TV COMP.

AUDIO (L)

AV1 AUDIO(L)

AV2 AUDIO(L)

AV1 AUDIO(R)

AV2 AUDIO(R)

5

Q001

MOMENTARY

MUTE ON/OFF

+9V

IC1002

PIP

COMPO.

VIDEO

SWITCH

+9V

IC1081

MAIN

S1/V1/V2

SWITCH

EXT.V

R1041

16 15 14 13 12 11 10 9

HLH L

1 2 3 4 5 6 7 8

C

16 15 14 13 12 11 10 9

HLH L

1 2 3 4 5 6 7 8

C1

HL

R1082

HL

Y

R1042

R1081

Q1093,

C

Q1094,

Q1096

Y

Y(COMB)

C(COMB)

YC MIX

Q332

BUFFER

Q342

BUFFER

Q343

BAND

PASS

SW

BAND PASS

FILTER

IC301

15

COMB

FILTER

13

Q341

BUFFER

LPF

Q216

INVERT.

4

Page 28

– 26 –

REFERENCE OSCILLATOR

REFERENCE OSCILLATOR

The CPU requires a stable oscillator to serve as the clock signal. This clock

signal will be used to control the timing of all CPU functions and control

pulses. X801 connected between pins 19 and 20 of the CPU, provides a

stable, crystal controlled oscillator frequency of 8 MHz that is used for the

clock signal.

TIME DISPLAY FEATURE

The C-003 CPU provides a time display feature. The time of day clock is

timed by counting the reference oscillator frequency of 8 MHz served to the

CPU. The oscillator frequency is maintained accurate within ± 0.003 percent,

which provides a convenient and accurate timing signal for the clock. The

Clock and the Sleep Timer cannot be set if this timing signal is missing,

because of no signal to control the timing of all CPU functions and control

pulses.

8 MHz Reference Oscillator

C809

X801

C808

IC801

CPU

19

20

Page 29

– 27 –

CRT DISPLAY CIRCUIT

The CPU generates and controls all characters and data for the on-screen

displays. Excluding Captions, the VB7C chassis is designed for a green, red,

white, yellow and cyan screen display. In order to provide correct positioning,

vertical and horizontal sync signals are input to IC801 (CPU) on pins 1 (Hsync) and 2 (V-sync). The horizontal and vertical sync pulses are limited and

wave shaped by Q882 and Q881 respectively.

Operation

Beginning with the input of the vertical sync signal, horizontal sync pulses are

counted. After counting a certain number of horizontal sync pulses, the CPU

will begin counting 8 MHz clock pulses developed at pins 19 and 20. At the

desired number of clock pulses, the letter signals are output on pins 40-42,

and the blanking signals are output on pin 39. The letter and the blanking

signals are output as active Highs. The exact count of horizontal sync pulses

and 8 MHz clock pulses is controlled by the CPU program and will change

with the display pattern.

All display signals from the CPU are input to IC101, the Signal Processor, on

pins 33-36 where they are added to the video signal. Since the C-003 CPU

includes the Caption Data Slicer and Caption OSD, the screen displays and

caption displays cannot be shown simultaneously.

Screen Display Control Circuit

IC801

CPU

R-OUT

G-OUT

B-OUT

BLK-OUT

42

41

40

39

IC101

SIGNAL PROCESSOR

R849

R848

R847

R846

C843

33

R844

C842

34

R843

C841

35

R842

36

(8 MHz)

C809

C808

X801

ALWAYS

5V

R821

Q882

Q881

19

20

H-SYNC

X-IN

X-OUT

V-SYNC

1

R826

2

R827

R822

C832 R828

C831

R823

T402

5

IC501

7

Page 30

– 28 –

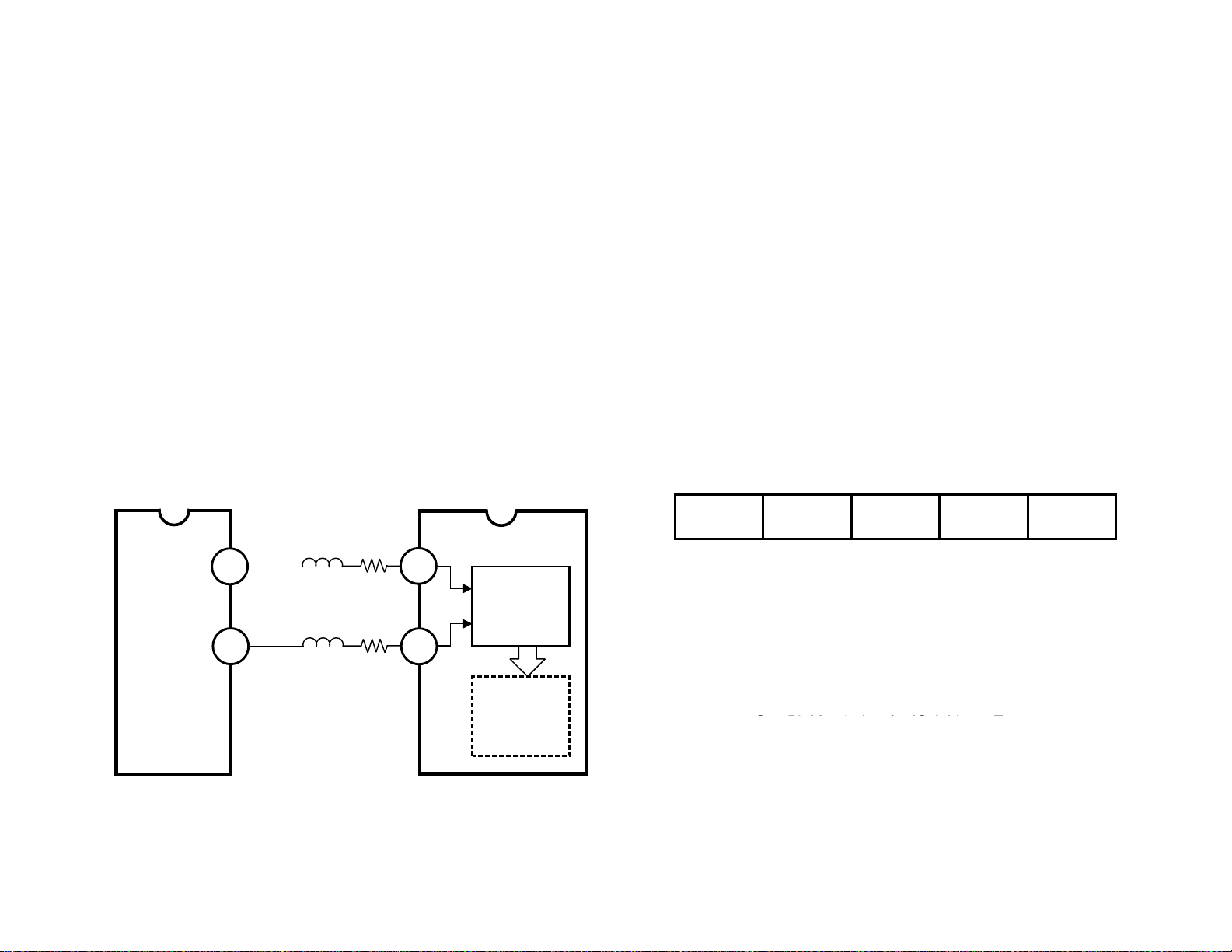

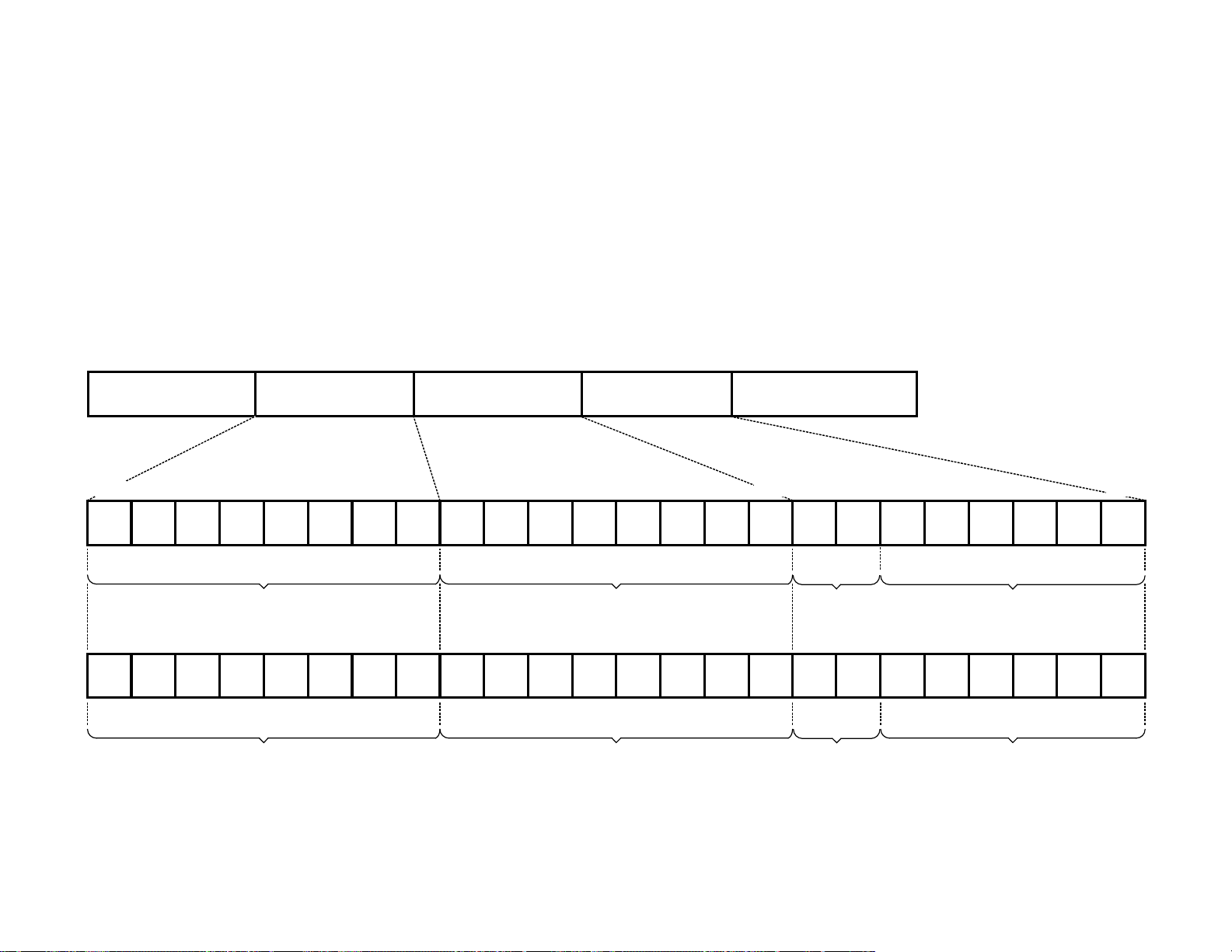

MEMORY CONTROL CIRCUIT

The VB7C chassis is equipped with a nonvolatile memory IC to store certain

information that should remain intact through a power failure. IC802 is the 2K

bit serial EEPROM used to store this information. An EEPROM or E2PROM

is an Electrical Erasable Programmable Read Only Memory integrated circuit.

IC802 will store Channel Memory, including active and inactive channels for

total of 125 channels, the Air/Cable mode, the customer settings of Digital

Control, Caption mode, Language mode, TV/AV mode, Surround On/Off

mode, Color Enhancer mode, the Line-SW On/Off mode, and the BUS data

used for factory/service adjustments. (The Line-SW On/Off mode is a special

mode used only for production.)

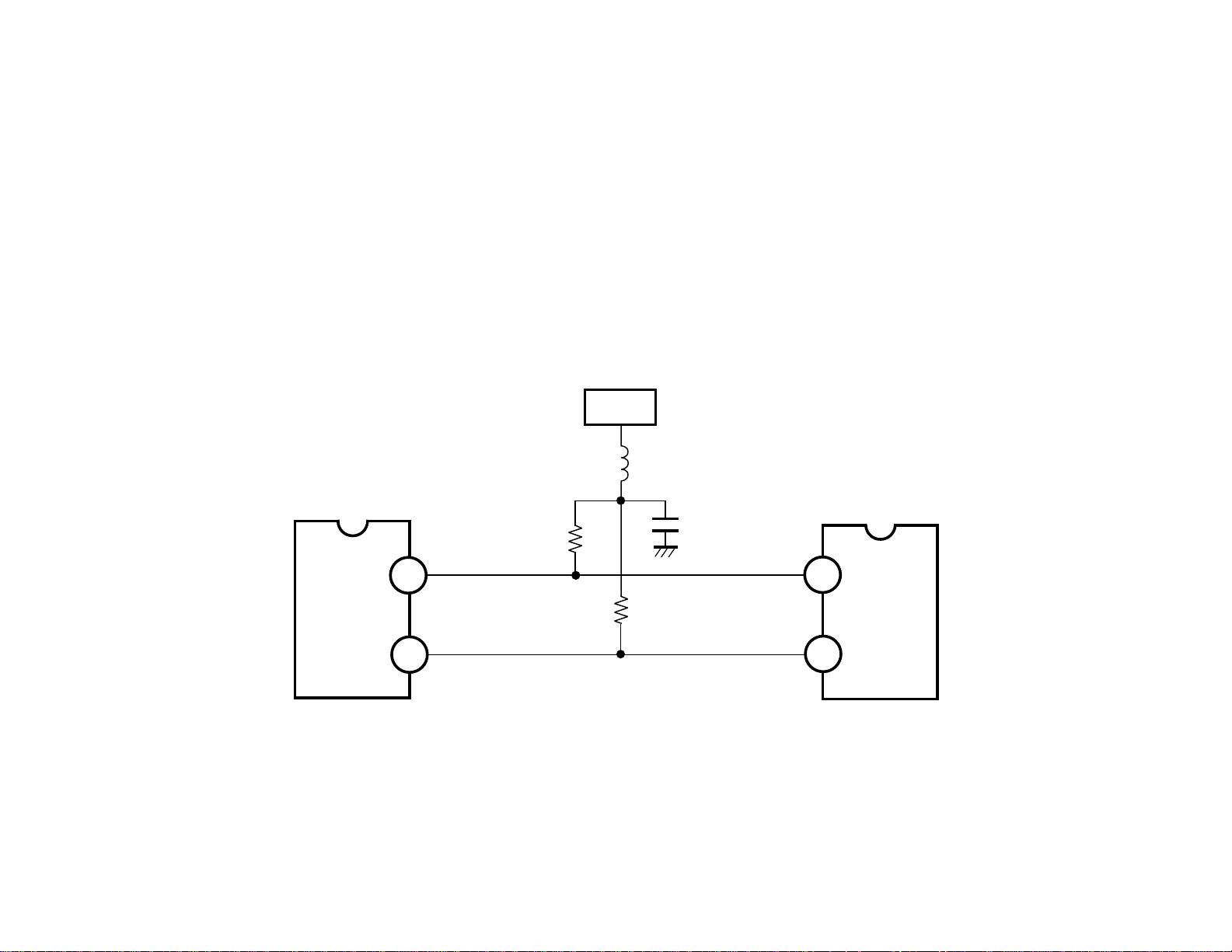

Control of the memory IC is through CPU pins 31 and 33.

Pin 33 is the IIC SCL (Serial Clock) signal. The IIC SCL input is used to clock

all data into and out of IC802.

Pin 31 is the IIC SDA (Serial Data) signal. The IIC SDA is a bidirectional

signal and is used to transfer data into and out of memory. Data is processed

through an 8 bit read or write for each address and there are 256 addresses.

Therefore, IC802 has a capacity of 256 x 8 or 2K bits of data.

Memory Control Circuit

IC801

CPU

R808

ALWAYS

5V

L801

IC802

EEPROM

C801

IIC

SCL

IIC

SDA

33

31

R807

6

5

SCL

SDA

Page 31

– 29 –

CPU

CPU

CPU

CPU

S1 100 00000

S

T

DEVICE CODE

A

R

T

CONTROL BYTE

READ/WRITE

NOTE : ACK=ACKNOWLEDGE BIT

S1 100 00000

S

T

DEVICE CODE

A

R

T

CONTROL BYTE

A

C

K

READ/WRITE

A

C

K

WORD

ADDRESS(n)

WORD

ADDRESS(n)

A

C

K

DATA n DATA n+1 DATA n+7

Write-In Mode

S1 100 10000

S

A

T

C

K

DEVICE CODE

A

R

T

CONTROL BYTE

A

C

K

A

C

K

READ/WRITE

A

C

K

A

DATA n DATA n+X

C

K

A

C

K

P

S

T

O

P

P

S

T

O

P

NOTE : ACK=ACKNOWLEDGE BIT

Read-Out Mode

Page 32

– 30 –

MOMENTARY MUTE CIRCUIT

The Momentary Mute circuit is provided to prevent buzz or static in the

speakers when changing channels. The momentary mute circuit operates

when the power key is pressed, when changing channels, when switching

Antenna mode, when searching channels, when changing MTS or TV/AV

modes, when switching Surround On/Off mode, and when exchanging

programs between the main screen and PIP window. The momentary mute

should not be confused with the normal mute function performed by pressing

the MUTE key on the remote control. The momentary mute operates for a

period of 0.2 to 1.6 seconds depending on the operation being performed.

The momentary mute is controlled by the BUS control signal and the Mute

signal from the CPU: the BUS SDA (Serial Data) signal from pin 32, the BUS

SCL (Serial Clock) signal from pin 34, and the Mute signal from pin 38.

When changing channels, the CPU will output the BUS control signals and the

Mute signal to perform the momentary mute. The BUS control signals from

the CPU are input to the BUS Interface circuit within IC3401, the MTS

Processor. The BUS interface circuit will write a 6-bit data “000000” into each

of the Volume Control Registers and a 1 bit data “0” into each of the Audio

Mute Control Registers to minimize the output level at pins 3, 4, 38 and 39 of

IC3401. In addition the Mute (High) is coupled to the base of Q001, switching

Q001 On, grounding pin 5 of IC001. The minimum output level at pins 3, 4,

38 and 39 of IC3401 and the Low at pin 5 of IC001 will mute the audio output

of the Audio Amplifier IC001 and the external audio equipment, preventing

buzz or static in the speakers. Once the operation is complete, the CPU will

output the BUS control signal and the Mute (Low) signal to restore the output

sound level, allowing the audio to return to normal.

BUS Data Format in Write Mode - Momentary Mute Operation

STA ICW SUB DA STO

(MSB)

D7

D6

D5

D4

D3

D2

D1

(LSB)

D0

(MSB)

D7

D6

D5

00000011

IC WRITE ADDRESS

(MSB)

D7

D6

D5

D4

D3

D2

D1

(LSB)

D0

(MSB)

D7

D6

D5

STA: START Condition

ICW: IC Address + Write

SUB: Sub. Address

DA : Data

STO: STOP Condition

(LSB)

(MSB) (LSB)

D4

D3

SUB. ADDRESS

D4

D3

DA7

D0D1D2

1000000

1

(LSB)

D0D1D2

DA6

✻

0

Don't

care bit

(MSB) (LSB)

DA7

M2

DA6

DA5

DA4

000000

EXT1

EXT2

DA5

DA4

DA2

DA3

NRSW FOMO SAPC

DA2

DA3

DA0DA1

M1

DA0DA1

D7

D6

IC WRITE ADDRESS

D5

D4

IC WRITE ADDRESS

00000011

SUB. ADDRESS

(LSB)

(MSB)(MSB)

D2D3

D1

D0

D7

D6

D5

D4

D3

1000001

(LSB) (MSB)

D0

D1D2

00000011

SUB. ADDRESS

✻✻000000

1

Don't care bits

DA7

✻✻000000

00100000

Don't care bits

DA6

DA5

DA4

VOL-L

DA3

VOL-R

DA2

DA1

(LSB)

DA0

Page 33

– 31 –

Sound Control Circuit

IC801

CPU

BUS

SDA

BUS

SCL

MUTE

32

34

38

L881

L882

R881

R882

R3401

R3402

AV1-R

AV1-L

AV2-R

33

34

36

5

6

BUS

Interface

to BUS Line

FEXT1

IC3401

MTS PROCESSOR

VOL-R

VOL-L

TREBLE

BASS

SURR

M2

EXT1/EXT2/M1

VOLUME

CONTROL

BASS/TREBLE

CONTROL

SURROUND

BLOCK

AUDIO SW

3

4

38

39

IC001

AUDIO AMP.

C002

R

L

8

10

C001

C007

R011

R012

R

L

Q001

MOMENTARY

MUTE

5

C3437

C3435

C010

SP901

3

1

C011

R

SPEAKER (R)

SP902

L

SPEAKER (L)

K1011

FIXED

AUDIO OUT (R)

K1021

FIXED

AUDIO OUT (L)

AV2-L

SIF In

37

13

FEXT2

MTS DECODER

BLOCK

Page 34

– 32 –

AFT DEFEAT CIRCUIT

The AFT Defeat circuit is provided to reduce interference or “tweet” in the

video produced by the AFT circuitry. Since the AFT function is needed only

when changing channels, the AFT can be disabled at all other times.

The AFT enabling/disabling is controlled by the BUS control signal from the

CPU: the BUS SDA (Serial Data) signal from pin 32, and the BUS SCL (Serial

Clock) signal from pin 34. Normally the CPU outputs the BUS control signal

to disable the AFT circuitry. The BUS control signal from the CPU are input

to the BUS interface circuit within IC101, the Signal Processor. The BUS

interface circuit will write a 1 bit data “1” into the AFT Defeat Control Register

to turn off the AFT Amplifier, then the AFT output voltage at pin 13 of IC101

will be fixed to 1/2Vcc (approx. 3.8VDC). When changing channels, the AFT

enabling BUS data is input to the BUS Interface circuit to write a 1 bit data “0”

into the AFT Defeat Control Register, allowing the AFT circuit to operate.

An additional adjustment mode is provided for the service adjustment to

disable the AFT Circuitry continuously for adjusting the APC DET and PLL

Tuning. When you enter the APC DET or PLL Tuning adjustment mode in the

service menu, the CPU will automatically output the BUS data to disable the

AFT circuitry continuously.

BUS Data Format in Write Mode - AFT Defeat Operation

STA ICW SUB DA STO

STA: START Condition

ICW: IC Address + Write

SUB: Sub. Address

DA : Data

STO: STOP Condition

(MSB)

D6

D5

D4

D7 D0D1D2D3

(MSB)(LSB) (MSB)(LSB) (LSB)

D6

D5

D4

D7

01111010

IC WRITE ADDRESS

SUB. ADDRESS

DA6

AFT

DA5

DA4

RF AGC DELAY

DA7D0D1D2D3

01011001

01000000

IF AGC

DEFEAT

DA0DA1DA2DA3

Page 35

– 33 –

IF System

IF In

TP132

X141

SAW

C143

R143

IF

GND

VIF VCC

C147

10

11

9

7.6V

R207

VIF AMP

VIF

-1

Selected

Video Out

VIF-2VIF

7.6V

Internal

Video Out

External

Video In

C139

Video

SW

R138

CLAMP

-3

APC Det.

R164

L164

TP16

47

Video Det.

- π / 4

+ π / 4

FM Trap

(88.1 ~ 91.9MHz)

R159R163

R169

45

Video

Level

Write

3 bit

AMP

X153

4.5MHz

BPFX161

W/N

INV

LIM

AMP

B/N INV

VCO

C133

R133

5249

T131

FM Coil

Multiplier

Write

5 bit

FM Level

IC101

SIGNAL PROCESSOR

+

-

3.8V

FM

AMP

+

-

7

50

2

3

FM Out

TP21

FM Filter

T151

VCO Tank

TP20

C131

L166

R165

C166

R160

Q162

1424

RF AGC

Out

IC801

CPU

BUS

SDA

BUS

SCL

AFT

S-Curve

TP11

C106

APC Det.

7.6V

R142

6

Data

Clock

44

43

32

34

29

RF

AGC

Write

6 bit

RF AGC

Delay

to BUS Line

Interface

IF AGC

Drive

BUS

46

BUS

GND

Adjust

Write

1 bit

IF AGC

SW

TP12

Write

6 bit

C142

IF AGC

Filter

12

PIF AGC

Filter

R151

C151

A

48

PIF APC

Filter

B

AGC

Buzz

Canceler

B: When PLL Unlocked.

A: When PLL Locked.

PLL Pull-in SW

Write

1 bit

N/I SW

Lock

Det

B/N

INV

IF

AFT Out

PLL Tuning

+

-

Defeat

TP113

R167

Write

7 bit

AFT

Write

1 bit

AFT

Audio

SW

Volume

Write

1 bit

Audio

Mute

13

7.6V

R161

C161R162R168

Volume

D/A

Write

6 bit

Volume

N/C

5

(EXT Audio In)

N/C

51

(Audio Out)

N/C

8

(Vol. Filter)

Page 36

– 34 –

CPU RESET OPERATION

The CPU must be reset each time AC power is applied. The reset function

ensures that the 5 volt power supply is supplying sufficient power to the CPU,

and the crystal-controlled reference oscillator has stabilized before the CPU

may detect inputs from the keyboard or remote control. The reset operation

will also cancel any programs operating before the power was removed. The

circuitry to reset the CPU consists of Q831 and associated components.

After the reset function is complete, the following CPU conditions will exist:

A. Pin 27 (power) will be maintained in a Low state (TV power supply

Off).

B. The digital control functions (brightness, contrast, etc.) will be set to

the last setting modes (FACTORY PRESET or MANUAL).

C. The BUS data (sub color, sub tint, etc.) will be set to the last settings.

D. The time of day clock will be reset to zero and all Timer functions

cleared.

E. The volume control output is set to the last setting level.

F. The channel selection will be set to last channel selected.

G. The TV/AV mode will be set to the last TV/AV mode selected.

H. The MTS mode will be reset to Stereo.

I. The Surround mode will be set to the last Surround mode (ON or OFF)

selected.

J. The PIP mode will be set to OFF.

K. The Caption mode will be set to the last Caption mode selected.

L. The Language mode will be set to the last Language selected.

M. The Color Enhancer mode will be set to the last Color Enhancer mode

(NORMAL or WARM) selected.

The reset operation provides two functions for the CPU system First, when

power is first applied to the system the reset circuit will initiate a micro

computer program within the CPU. This sets the CPU into the conditions

described above. Second, at the time of a power failure and before the CPU

can go into disarray, the reset circuit clears any operating programs within the

CPU.

When a power failure occurs, the rest program keeps the TV in the Off

condition after the power is restored, until the power key is pressed.

Reset operation – AC power applied.

When AC is applied, the 5 VDC supply line to CPU pins 14 and 22 and the

emitter of Q831 will gradually rise. At 2 µs after the power supply line reaches

4.5 V, the collector of Q831 will change from a Low to High level. At this point

the CPU will execute a Reset On/Off, resetting the program counter to 0

(zero), and restart the program from the beginning.

Reset operation – AC power Off.

When the AC power is lost, the 5 VDC supply line to CPU pins 14 and 22 and

the emitter of Q831 will gradually begin to drop. At 15 µs after the power

supply line reaches 4.5 V, the collector of Q831 will change from a High to

Low level. At this point the CPU will execute a Reset Off/On, interrupt the

program in progress, reset the program counter to 0, and enter a standby

state. When the supply line reaches 4 V, the CPU will cease to function.

Page 37

– 35 –

IC801

CPU

VCC

22

C822

ALWAYS

5V

L821

+

C806

+

R816

22

CPU

14

CPU AVCC

4.5 V

VCC

RESET

AVCC

25

14

CPU

25

RESET

R814

Q831

R813

C811

+

CPU Reset Circuit

CPU

25

D831

(3.6V)

L851

RESET

22

CPU

CPU AVCC

VCC

14

4 V

2µS

15µS

CPU Reset Voltage

Page 38

– 36 –

AUTOMATIC BRIGHT LEVEL ADJUSTMENT SYSTEM

The Automatic Bright Level Adjustment System employed in the VB7C

chassis replaces the mechanically adjusted Sub-Bright Level control used in

conventional systems. The primary difference between this system and

conventional systems is the addition of the beam current detection circuit and

the adjustment program incorporated within the CPU (C-003).

The advantages of this system include improved productivity and increased

accuracy of the bright level adjustment during production. This is due to the

computerized and digitized alignment procedure which allows remote

operation.

A block diagram comparison of the previous and present system is shown

below.

Note: The automatic bright level adjustment system requires special

equipment and test signals. For this reason, this system should be

used only for production.

An additional adjustment mode is provided in the CPU (C-003) for

service. To enter the service menu, press and hold the MENU key

while connecting the AC power. Then select “NO. 25 SB” (Sub

Brightness) and adjust the data with the remote control. To turn off the

service menu display, press the MENU key again. Refer to the specific

Service Manual for your model for the complete Bright Level

Adjustment procedure.

The automatic bright level adjustment system is composed of the beam

current detection circuit and the automatic adjustment program in the CPU.

The fundamental operations are described below.

Fundamental Operation

The BUS data for the brightness control with the 7-bit control data up to 127

steps is output from IC801, the CPU. The 64 steps are used for customer

control and the remainder (63 steps) are provided for bright level adjustment.

The BUS data for the brightness control is input to IC101, the Signal

Processor, and coupled to the BUS Interface circuit within IC101. The BUS

Interface circuit transfers the 7-bit control data to the Brightness Control

Register in IC101. The 7-bit control data changes for the brightness control

are the same as those shown for the bright level on the screen.

Since the beam current required for displaying pictures on the screen is

supplied from the +B (130V) DC line within the beam current detection circuit,

the average beam current is detected and transformed into a DC level for

input to the CPU, pin 30 (A/D input). Maximum A/D input voltage is produced

at 0 beam current.

The average beam current is in inverse proportion to the A/D input voltage as

shown below. The beam current detection circuit has been designed to output

a certain DC voltage between 21/128 Vcc (0.82V) and Vcc (5.0V), at 0 beam

current. The CPU (C-003) has been programmed to automatically adjust the

bright level at a suggested beam current for a specified video signal input

during FACTORY PRESET mode.

Page 39

– 37 –

Tuner

Memory

R/C

Transmitter

IC802

Memory

R/C

Transmitter

DC

Voltage

Sub-Bright Level

Control

Signal

Processor

CPU

R/C

Receiver

PWM

D/A

Converter

(L.P.F)

Conventional Bright Level Adjustment System

IC801

CPU

(C-003)

A1901

R/C

Receiver

Special Signal

Input

IC101 Signal Processor

BUS

Data

ALWAYS

5V

D843

C829

BUS

Interface

D834

(18V)

R831

+B(130V)

R494

R833

D836

Brightness

Control

Register

R493

R491

R492

D487

Beam Current Detection Circuit

A101

Tuner

Contrast

Bright

ABL

C493

FBT

T402

FBT

CRT

CRT

HV

HV

Vcc

57/128 Vcc

53/128 Vcc

49/128 Vcc

45/128 Vcc

41/128 Vcc

37/128 Vcc

33/128 Vcc

A/D INPUT VOLTAGE (Vcc = 5V)

29/128 Vcc

0 100 200

A/D Input Voltage at 0 beam current

Standard Voltage: A

5 steps (20/128 Vcc)

Reference Voltage for specified

beam current during FACTORY

PRESET mode

Suggested Beam Current for

12 IRE flat video signal input

during FACTORY PRESET mode

AVERAGE BEAM CURRENT ( µ A)

AVM-2780G Automatic Bright Level Adjustment System

A/D Input Voltage

Page 40

– 38 –

AUTOMATIC BRIGHT LEVEL ADJUSTMENT SYSTEM (Continued)

When the command data for the Automatic Bright Level Adjustment is input

from the remote control, the CPU starts the automatic adjustment program.

Automatic Bright Level Adjustment Program

First, the Time Base signal at pin 26 of the CPU is checked. When the video

signal is input to the TV, the Time Base signal at pin 26 is High. If the Time

Base signal can not be confirmed, the CPU executes an error process to

cease the automatic adjustment operation.

After confirmation of the Time Base signal, the CPU presets the BUS data

outputs of the picture controls to eliminate beam current. The controls are set

as follows: BRIGHTNESS 0/27 (= 0/63 for Bright Level Adjustment + 0/64 for

Customer Control), CONTRAST 0/64, COLOR 0/64*, TINT 32/64 and

SHARPNESS 32/64.

* ....The Color Killer enabling BUS data is automatically input to the BUS

Interface circuit within IC101 to write a 1 bit data “1” into the Color Killer

Control Register, minimizing the output of the color control during the

Automatic Bright Level Adjustment.

With a low amplitude, flat video signal (12 IRE) input to the TV and the +B

(130V) DC power applied to the flyback transformer and the beam current

detection circuit, no beam current is supplied to the CRT. Maximum current

is now input to the beam current detection circuit and maximum DC voltage is

input to pin 30 (A/D input) of the CPU.

When the maximum A/D input voltage at pin 30 is between 21/128 Vcc

(0.82V) and Vcc (5.0V), the specified video signal is determined to have been

input and the A/D input voltage is read by the 5 bit (31 steps) comparator.

The CPU will begin decreasing the reference voltage from 125/128 Vcc (31/31

steps) sown to 21/128 Vcc (5/31 steps) by 2steps (8/128 Vcc) until the

reference voltage becomes just lower than the A/D input voltage. The

reference voltage is now memorized as a standard voltage (A) and stored in

IC802, the Memory IC. If the A/D input voltage is lower than the 21/128 Vcc

(0.82V), the CPU executes an error process to cease the automatic

adjustment operation. See example of A/D Input Voltage on previous page.

After determination of the standard voltage (A), the CPU changes the BUS

data outputs of brightness and contrast controls for FACTORY PRESET mode

as follow: BRIGHTNESS 50/127 (= 0/63 for Bright Level Adjustment + 50/64

for Customer Control), CONTRAST 64/64.

The CPU will now decrease the reference voltage of the comparator 5 steps

(20/128 Vcc) lower than the standard voltage (A) and compares it with the A/D

input voltage. When the A/D input voltage is higher than the reference

voltage, the CPU increases the BUS data output of the Bright Level

Adjustment from 0/63 up to 63/63 step by step until the A/D input voltage

becomes just lower than the reference voltage. The BUS data output step of

the Bright Level Adjustment is memorized into the Memory IC and the CPU

exits the automatic adjustment mode.

Page 41

– 39 –

Automatic Bright Level Adjustment Program

Enter Automatic Adjustment mode

Wait for 100 msec

(Error)

(Error)

NO

Time Base signal

at CPU pin 26 is High ?

YES

Preset BUS Data Outputs to eliminate beam

current: BRIGHTNESS 0/127*

1

, CONTRAST 0/64

Wait for 1 sec

Read A/D Input Voltage at CPU pin 30

NO

A/D Input Voltage

is in the range*

2

?

YES

Memorize A/D Input Voltage(Standard Voltage (A))

Change BUS Data Outputs for AUTO mode:

BRIGHTNESS 50/127*

3

, CONTRAST 64/64

Wait for 200 msec

Read A/D Input Voltage at CPU pin 30

YES

A/D Input Voltage*4< (A)-(20/128Vcc)

*1 ... 0/127 = 0/63 for Bright Level Adjustment + 0/64 for Customer Control

2

*

... range is between 21/128 Vcc (0.82V) and Vcc (5.0 V)

3

*

... 50/127 = 0/63 for Bright Level Adjustment + 50/64 for Customer Control

4

*

... A/D Input Voltage { [Standard Voltage (A)] - [20/128 Vcc (0.39 V)] }

Memorize Bright Level

Exit Automatic Adjustment mode

NO

Wait for 70 msec

Increase 1 step (1/63) of BUS Data Output for

Bright Level Adjustment

Page 42

– 40 –

AUTOMATIC RF AGC ADJUSTMENT SYSTEM

The Automatic RF AGC Adjustment System employed in the VB7C chassis

replaces the mechanically adjusted RF AGC control used in conventional

systems. The primary difference between this system and conventional

system is the addition of the RF AGC A/D input circuit and the adjustment

program incorporated in the CPU (C-003).

The advantages of this system include improved productivity and increased

accuracy of the RF AGC adjustment during production. This is due to the

computerized and digitized adjustment procedure which allows remote

operation.

Note: The automatic RF AGC adjustment system requires special equipment

and test signals. For this reason, this system should be used only for

production.

An additional adjustment mode is provided in the CPU (C-003) for

service. To enter the service menu, press and hold the MENU key

while connecting the AC power. Then select “NO. 03 RAD” (RF AGC

Delay) and adjust the data with the remote control. To turn off the

service menu display, press the MENU key again. Refer to the specific

Service Manual for your model for the complete RF AGC Adjustment

procedure.