Sanyo 17MB18 Diagram

15” TFT TV

SERVICE MANUAL

(17MB18)

TABLE OF CONTENTS

1.

INTRODUCTION ......................................................................................................................................3

1.1. Scope.................................................................................................................................................3

1.2. General Features...............................................................................................................................3

2. SYSTEM BUILDING BLOCKS ................................................................................................................4

2.1. Analog Front End...............................................................................................................................4

2.1.1. Tuner .........................................................................................................................................4

2.1.2. SAW Filters................................................................................................................................5

2.2. Back End............................................................................................................................................5

2.3. Side Board(s).....................................................................................................................................7

2.3.1. Side Audio Video.......................................................................................................................7

2.3.2. Keypads.....................................................................................................................................8

2.3.3. IR&Led Board............................................................................................................................8

2.4. Power.................................................................................................................................................8

3. IC AND COMPONENT DESCRIPTIONS...............................................................................................11

3.1. Basic IC List.....................................................................................................................................11

3.2. UOCIII ..............................................................................................................................................11

3.2.1. Pinout ......................................................................................................................................12

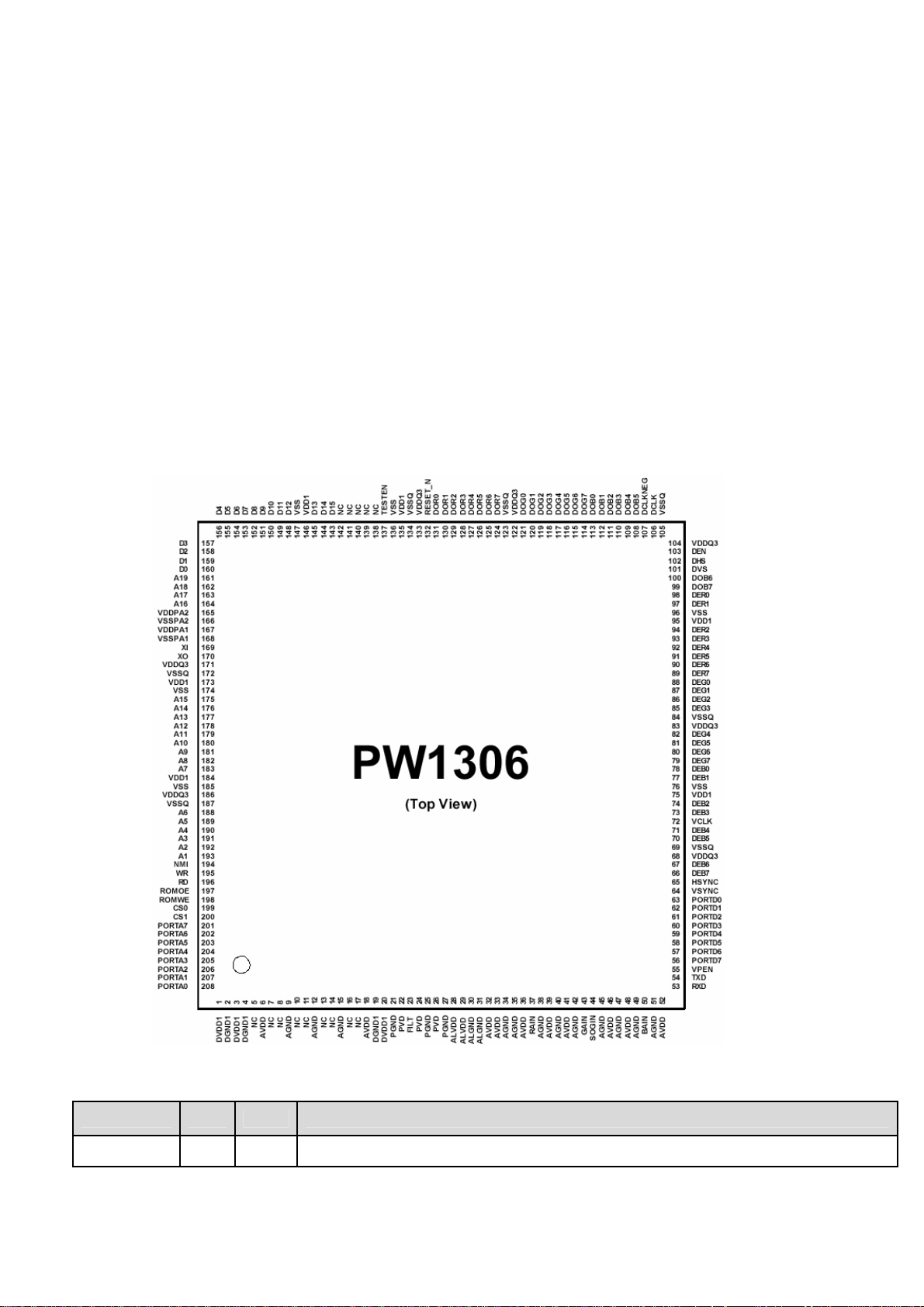

3.3. PW1306 ...........................................................................................................................................16

3.3.1. Pinout ......................................................................................................................................17

3.4. M29W800AT....................................................................................................................................25

3.5. DS90C385........................................................................................................................................25

3.6. P15V330 ..........................................................................................................................................25

3.7. 74HC4052........................................................................................................................................26

3.8. TDA7056A........................................................................................................................................26

3.9. TDA1308..........................................................................................................................................26

3.10. LM1117.....................................................................................................................................27

3.11. 24LC32 .....................................................................................................................................27

3.12. 24LC21 .....................................................................................................................................27

3.13. 74LVC541.................................................................................................................................28

3.14. MC34167 ..................................................................................................................................28

3.15. TFMS5360................................................................................................................................29

3.16. Board Connectors, Headers & Jumpers...................................................................................29

3.16.1. Analog PC Connector (PL400)................................................................................................29

3.16.2. Scart Connector (PL401).........................................................................................................29

3.16.3. S-Video Connector (JK403) ....................................................................................................30

3.16.4. LVDS Panel Connector(1x20 PL179)......................................................................................30

3.16.5. TTL Panel Connector -Even (2x17 PL177).............................................................................30

3.16.6. TTL Panel Connector -Odd (2x17 PL178) ..............................................................................30

3.16.7. Panel Inverter Connector (1x11 PL176)..................................................................................31

3.16.8. Keypad Card Connector (1x5 PL175).....................................................................................31

3.16.9. Optional Keypad Connector to UOC (1x2 PL 202) .................................................................31

3.16.10. LED & IR Receiver Connector (1x6 PL202)............................................................................31

3.16.11. Optional Rocker Sw. Connector (1x4 PL500).........................................................................31

3.16.12. PROMJet Connector (2x25 PL101).........................................................................................32

3.16.13. Side HP Connector for Side-card Option (PL405) ..................................................................32

3.16.14. Side AV Connector for Side-card Option (PL406)...................................................................32

3.16.15. Side SVHS Connector for Side-card Option (PL407)..............................................................32

4. SERVICE MENU SETTINGS .................................................................................................................33

4.1. UOCIII Service Menu.......................................................................................................................33

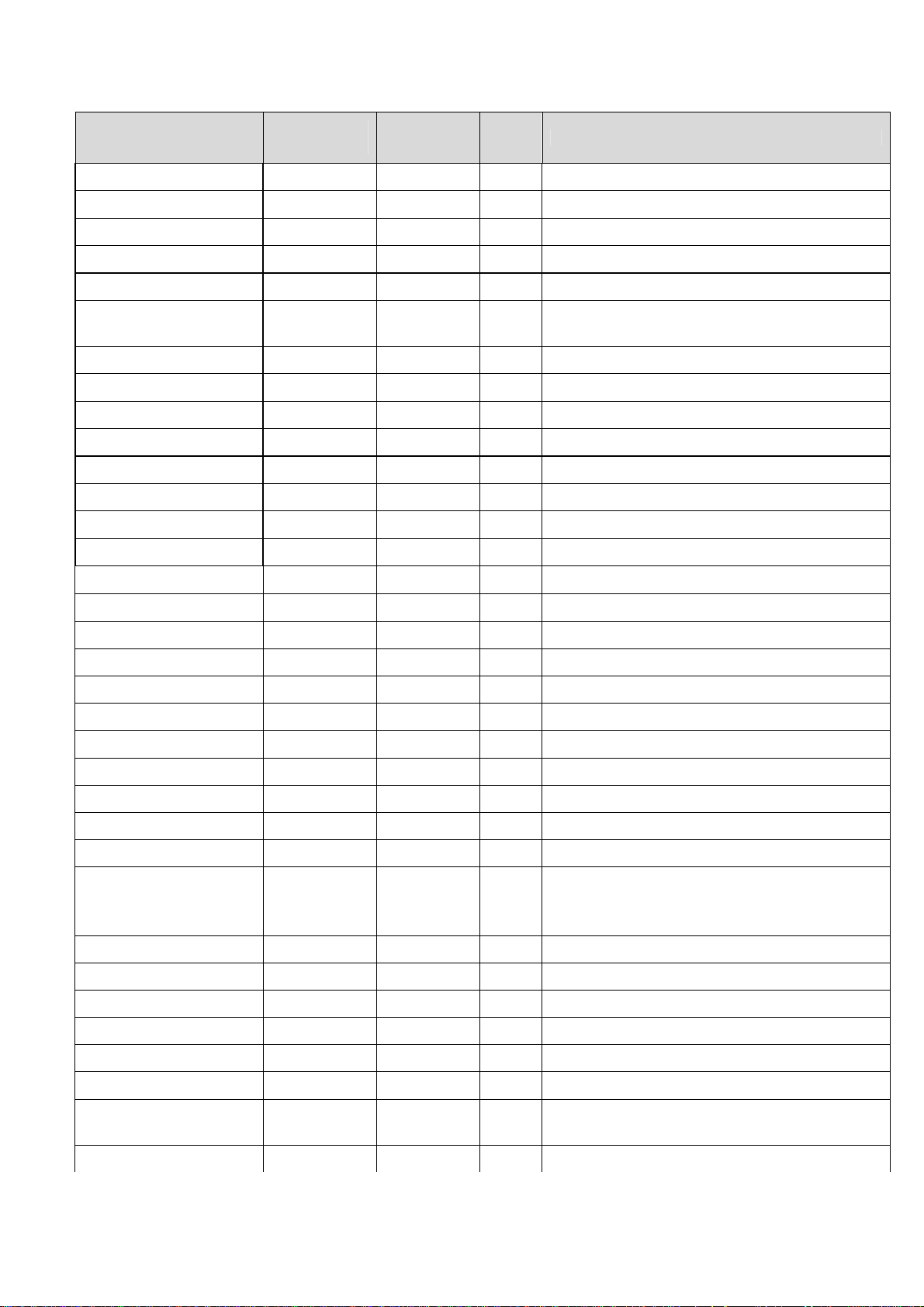

4.1.1. UOCIII Service Menu Settings ................................................................................................33

4.1.2. Tuner AGC Alignment.............................................................................................................37

4.1.3. DCXO Alignment.....................................................................................................................37

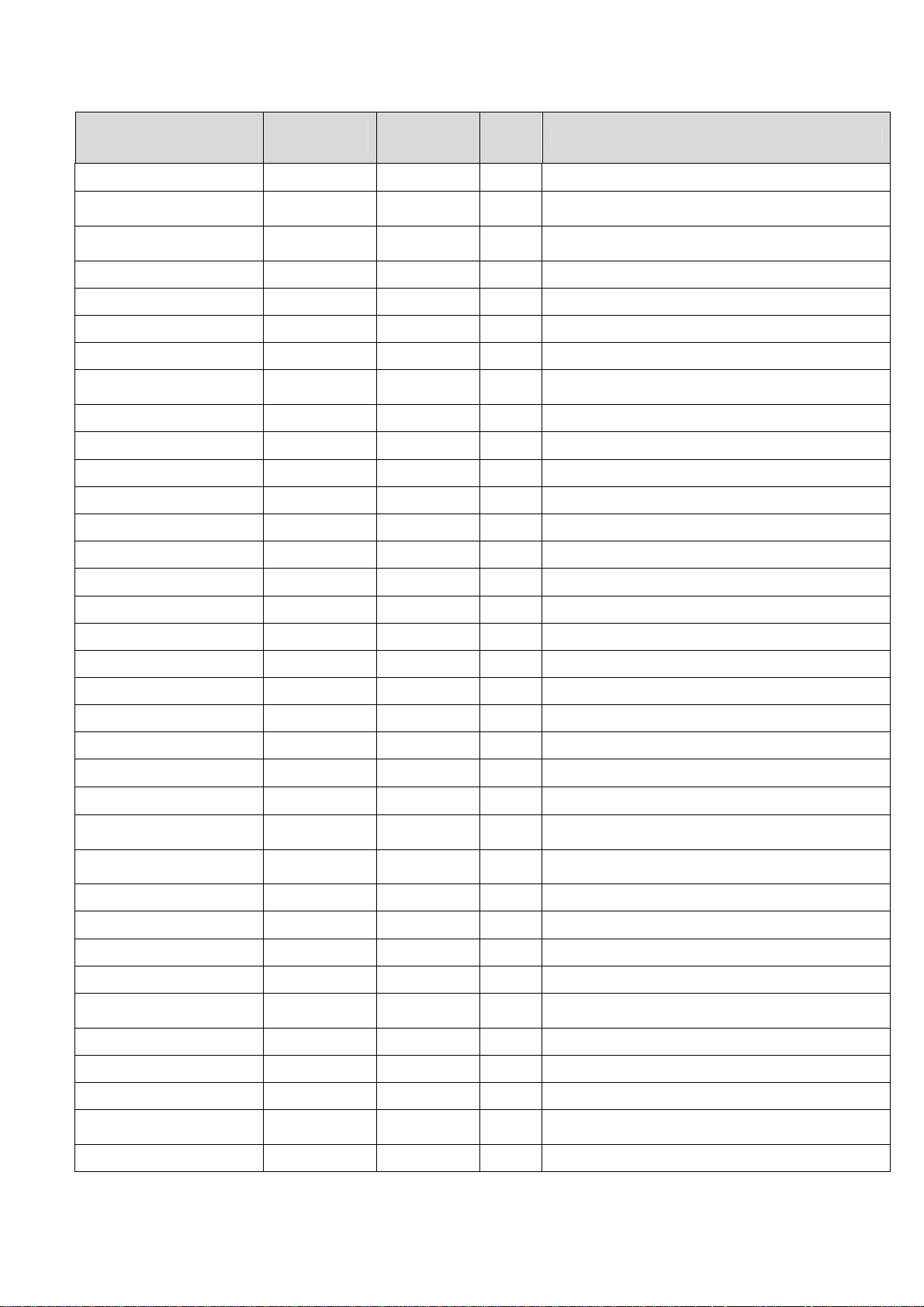

4.2. PW1306 Service Menu ....................................................................................................................37

4.2.1. UOC Horizontal Position .........................................................................................................38

4.2.2. UOC Calibration ......................................................................................................................38

4.2.3. PW1306 PC Input ADC Calibration.........................................................................................38

4.2.4. Panel Type Setting..................................................................................................................39

i

i

15” TFT TV Service Manual 21/06/2005

4.2.5.

Init NVM...................................................................................................................................39

4.2.6. AVL..........................................................................................................................................39

4.2.7. Initial APS................................................................................................................................39

4.2.8. Language.................................................................................................................................39

4.2.9. Country....................................................................................................................................39

4.2.10. Group.......................................................................................................................................39

4.2.11. Mode........................................................................................................................................40

4.2.12. Contrast, Brightness, Sharpness and Color............................................................................40

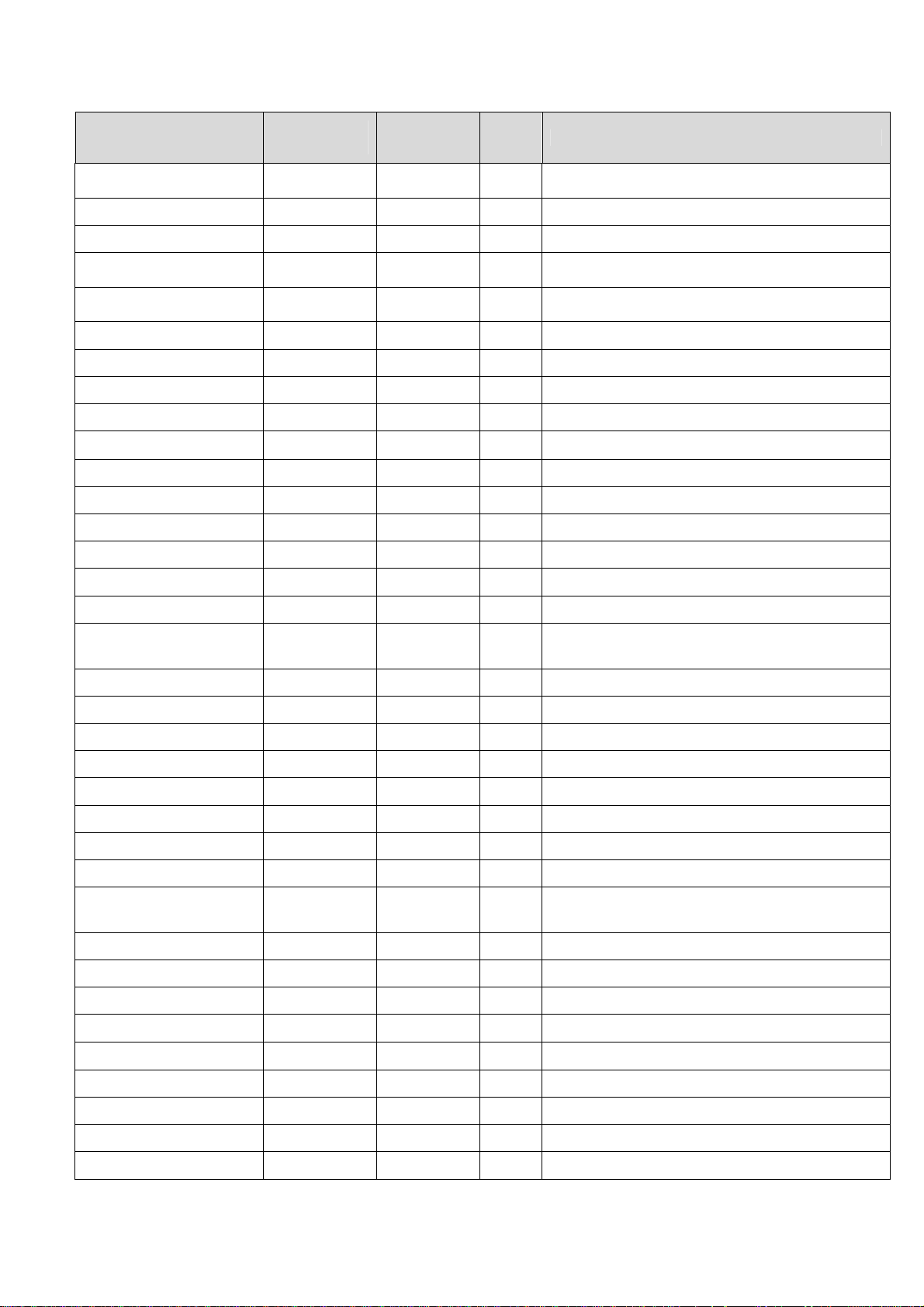

5. FACTORY DEFAULTS ..........................................................................................................................42

5.1. TV Menu...........................................................................................................................................42

5.1.1. Picture Menu ...........................................................................................................................42

5.1.2. Sound Menu............................................................................................................................42

5.1.3. Feature Menu..........................................................................................................................42

5.1.4. Installation Menu .....................................................................................................................42

5.1.5. Source Menu...........................................................................................................................43

5.2. PC Mode Menu................................................................................................................................43

5.2.1. PC Picture Menu .....................................................................................................................43

5.2.2. PC Sound Menu.....................................................................................................................43

5.2.3. Source Menu...........................................................................................................................43

6. TROUBLE SHOOTING ..........................................................................................................................44

7. ELECTRONIC PARTS ...........................................................................................................................46

8. BLOCK DIAGRAM.................................................................................................................................60

9. CIRCUIT DIAGRAMS.............................................................................................................................61

9.1. 17MB18-4 Schematics.....................................................................................................................61

9.2. Side AV Board Schematic................................................................................................................66

9.3. Keypad Schematics .........................................................................................................................67

9.4. IR&LED Board Schematics..............................................................................................................68

10. PCB PATTERN SCHEMATICS .............................................................................................................69

10.1. Complete PCB Pattern Schematic............................................................................................69

10.2. Top Level PCB Pattern.............................................................................................................70

10.3. In-1 Ground Level PCB Pattern................................................................................................71

10.4. In2_Power Level PCB Pattern..................................................................................................72

10.5. Bottom Level PCB Pattern........................................................................................................73

10.6. Top Layer Silk Print...................................................................................................................74

10.7. Bottom Layer Silk Print .............................................................................................................75

10.8. Topmask.lgx..............................................................................................................................76

10.9. Bottommsk.lgx ..........................................................................................................................77

11. VOLTAGE WAVEFORMS......................................................................................................................78

11.1. Power Signals...........................................................................................................................78

11.2. Syncronization Signals .............................................................................................................78

11.3. Communication Signals............................................................................................................81

11.4. Video Signals............................................................................................................................84

11.5. Audio Signals............................................................................................................................87

ii

ii

15” TFT TV Service Manual 21/06/2005

1. INTRODUCTION

1.1. Scope

The document covers 15” JVC (17MB18) chassis building blocks, basic features, service menu settings, and the other

information needed by service personnel.

1.2. General Features

The system is a 15” TFT LCD TV solution with UOCIII Versatile Signal Processor and PW1306 Video Image Processor

chip-set on 4-layer PCB. The TV will support PAL/SECAM B/G/D/K/I/L/L’.

The other general default features of the TV are as listed below:

• 1 Full Scart input (with SVHS support)

• 1 SVHS input through standard S-Video interface.

• 1 CVBS input through standard RCA jack

• 75 ohms antenna input

• D-Sub 15 PC Input

• NTSC Playback

• GERMAN + NICAM STEREO

• <3W S/B Power Consumption from mains supply

• 2x3W Speaker Output Power @16 Ohm spks; HP Output

• Stereo Audio line in

• PC Audio in

• Equalizer

• IR Control

• OSD; 19 Menu Languages ENG, FRA, GER, ITA, SPA, POR, TUR, SWE, DEN, FIN, NOR, POL, HUN, CZE,

BUL, ROM, RUS, DUTCH and GRE.

• Teletext

• 2H/4H Comb Filter

• White balance settings (Bright/Standard/Soft) for TV&PC

• Full AIR&CABLE band coverage

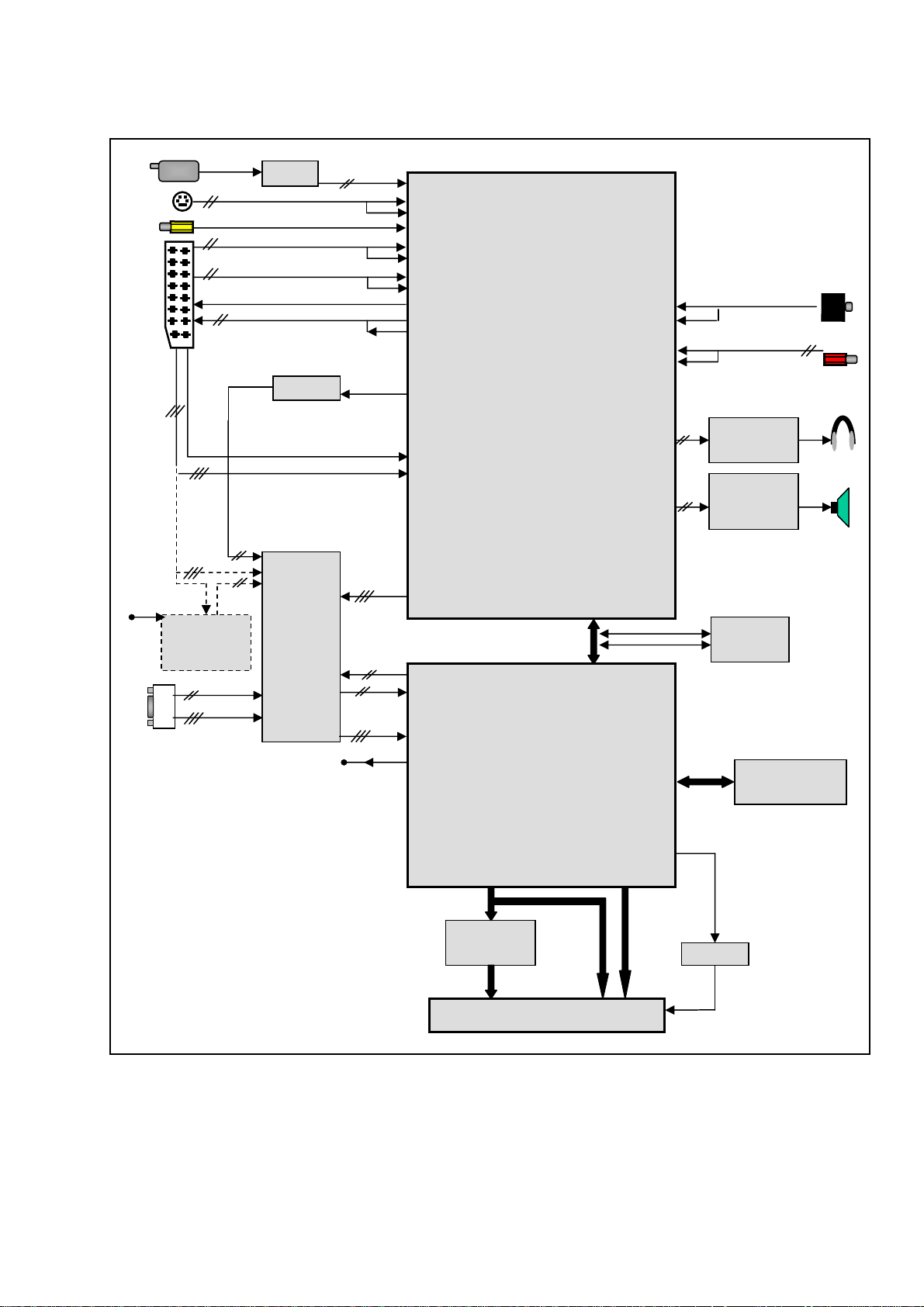

2. SYSTEM BUILDING BLOCKS

17MB18 chassis main blocks are as follows:

• Analog Front End : UOCIII (Microcontroller + Video Proccessor + Sound Proccessor + IF), Tuner, SAW

filters, Audio Amp., DAC

• Back End : PW1306(Microcontroller, Scaler, OSD, Keyboard/IR Interface)

• Side Board(s) : Side AV card, Keyboard, IR/LED Board,

2.1. Analog Front End

17MB18 Main Board consists of two major blocks. The first block is analog front-end and this block is handled by

UOCIII chip that is highly multifunctional. This IC does demodulation of Video & Audio from Tuner IF, CVBS, Audio,

RGB, SVHS input selection and processing. It has an audio processor that supports equalizer or tone control, volume

control, AVL, surround effect etc and supplies amplifier, headphone and CVBS & audio line outputs. It handles video

processing such as colour standard detection and demodulation, picture alignment (brightness, contrast, colour etc.). The

IC also does teletext decoding. After video processing, the processed video is applied to PW1306 chip in RGB format.

The TV Tuner is an asymmetrical IF output type and is PLL controlled. For multistandard reception, a switch able SAW

filter is used as the sound filter and it is controlled by SAW_SW output from UOC. After the SAW filter block, IF signal

is applied to UOC IF inputs (VIFIN[1,2] and SIF[1,2]).

As UOCIII can handle all the audio processing, there is no need for additional audio processor solution on the board.

UOC supports three Audio outputs. These outputs are assigned to Headphone, Speaker and Scart Audio line outputs. The

board employs TDA7056A and TDA1308 to drive speaker and headphone outputs respectively.

2.1.1.

Tuner

As the thickness of the TV set has a limit, a horizontal mounted tuner with longer connector is used in the

product. The tuning is available through the digitally controlled I

2

C bus (PLL). Below you will find info on the

Asymmetrical Tuner in use.

General description:

The tuner meets a wide range of applications. It is a combined VHF, UHF tuner suitable for CCIR systems

B/G, H, L, L’, I and I’. The low IF output impedance drives a wide variety of SAW filters with sufficient

suppression of triple transient.

Features:

• Small sized UHF/VHF tuners

• Systems CCIR: B/G, H, L, L’, I and I’; OIRT: D/K

• Digitally controlled (PLL) tuning via I

2

C-bus

• Off-air channels, S-cable channels and Hyper band

• ZS(AE) Aerial source impedance (unbalanced) 75 Ohm

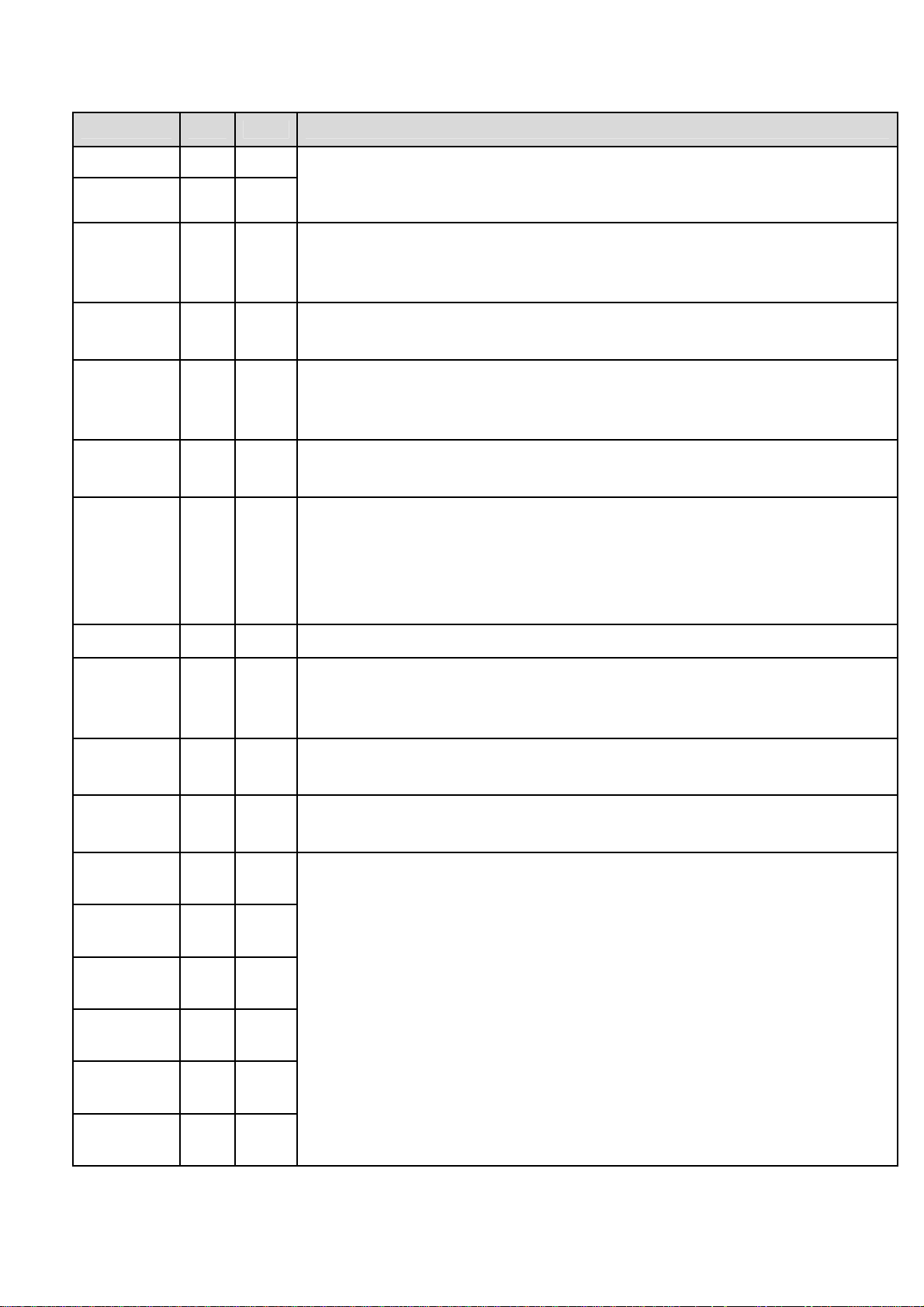

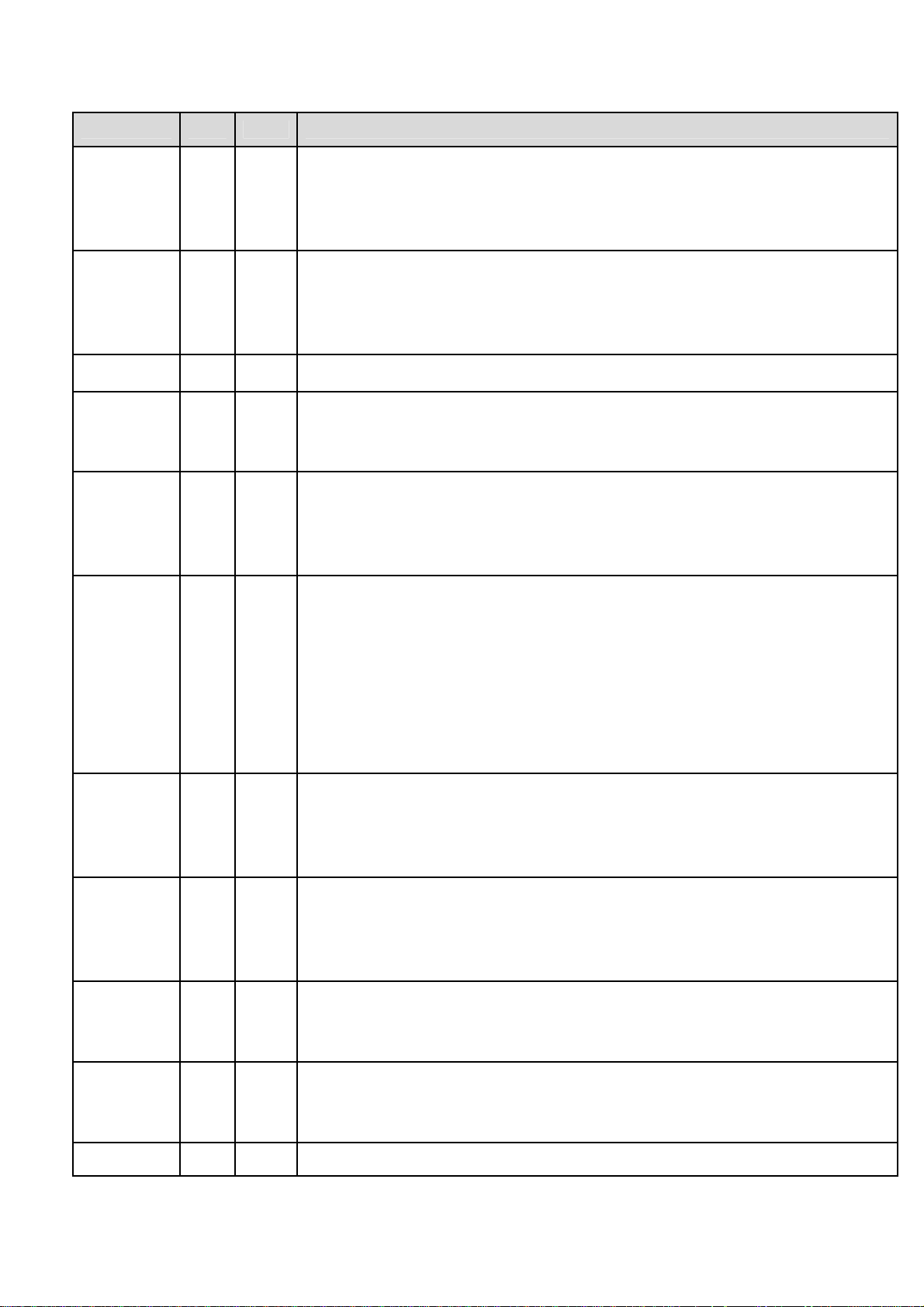

PIN SYMBOL DESCRIPTION

1

2

3

4

5

6

7

8

9

10

11

M1,M2,M3,

M4

AGC

Automatic Gain Control Voltage 4

±0.1

TU Tuning voltage monitor (output)

AS

SCL

SDA

I 2C-Bus Address Select

I 2C-Bus Serial Clock

I 2C-Bus Serial Data

n.c. Not Connected

s

V

ADC

ST

V

Supply Voltage +5V ±0.125

ADC Input

Fixed tuning Supply Voltage +33V ±0.5

I.F out 2 Symmetrical I.F output 2 / Do not connect for asymmetrical

I.F out 1 Asymmetrical I.F Output / Symmetrical I.F output 1

GND Mounting Tags (Ground)

2.1.2.

r

[R,G,B]

SAW Filters

K3953M is an IF Filter for Video Applications. The package is SIP5K. Supported standards are B/G, D/K, I,

L/L’.

K9656M is an IF Filter for Audio Applications. The package is SIP5K. Supported standards are B/G, D/K, I,

L/L’.

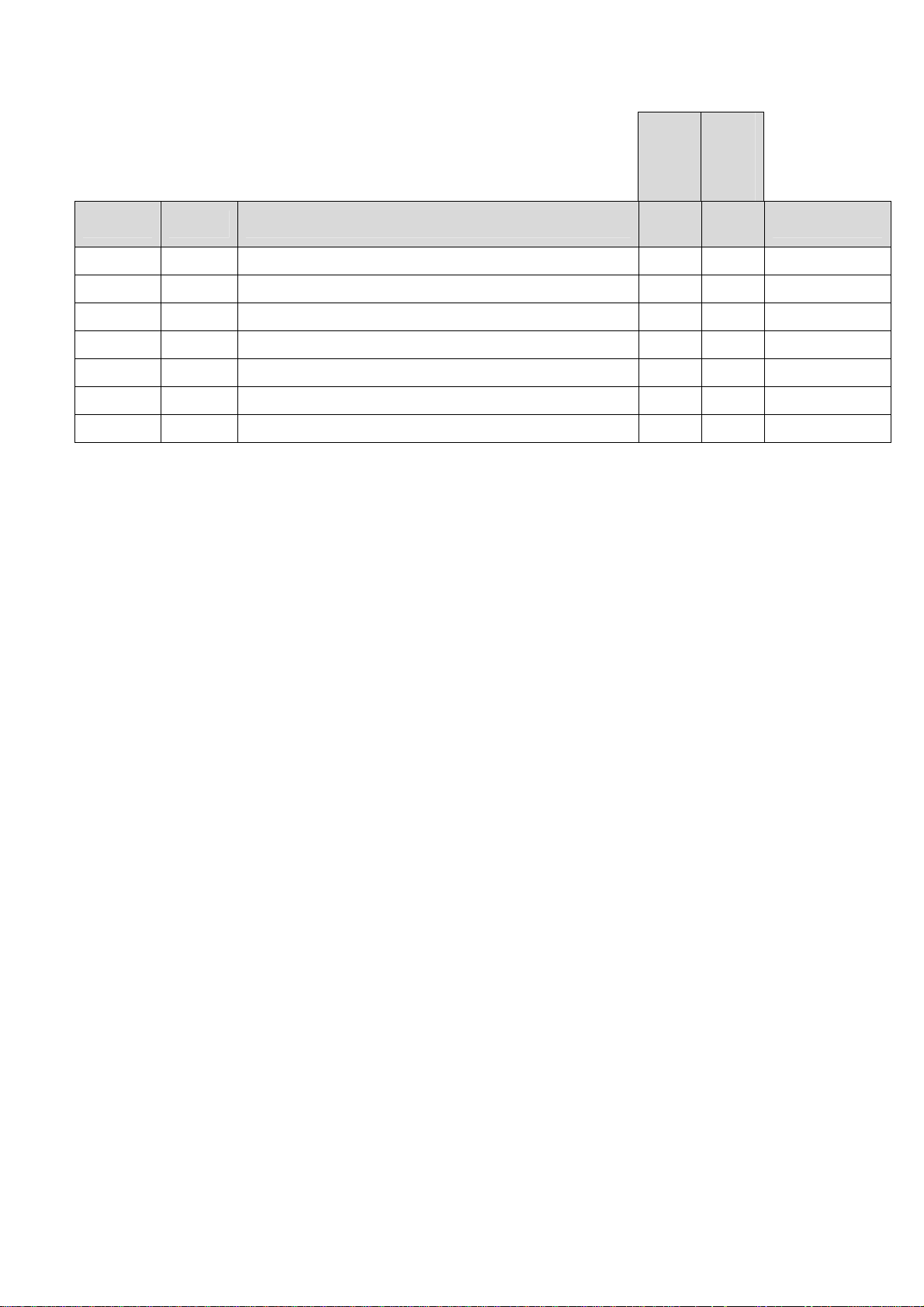

2.2. Back End

The Back End section is handled by PW1306 chip. This IC has built in ADC’s for RGB and SOY support. The RGB input

can handle standard interlaced RGB output from UOC, PC VGA RGB input. As only 1 set of ADC is present in PW1306

these sources should be multiplexed.

All the multiplexing operations are controlled by PW1306 via YUV_TV_SW (58) and VGA_TV_SW (57) signals.

A: VGA _TV_SW

B: YUV _TV_SW

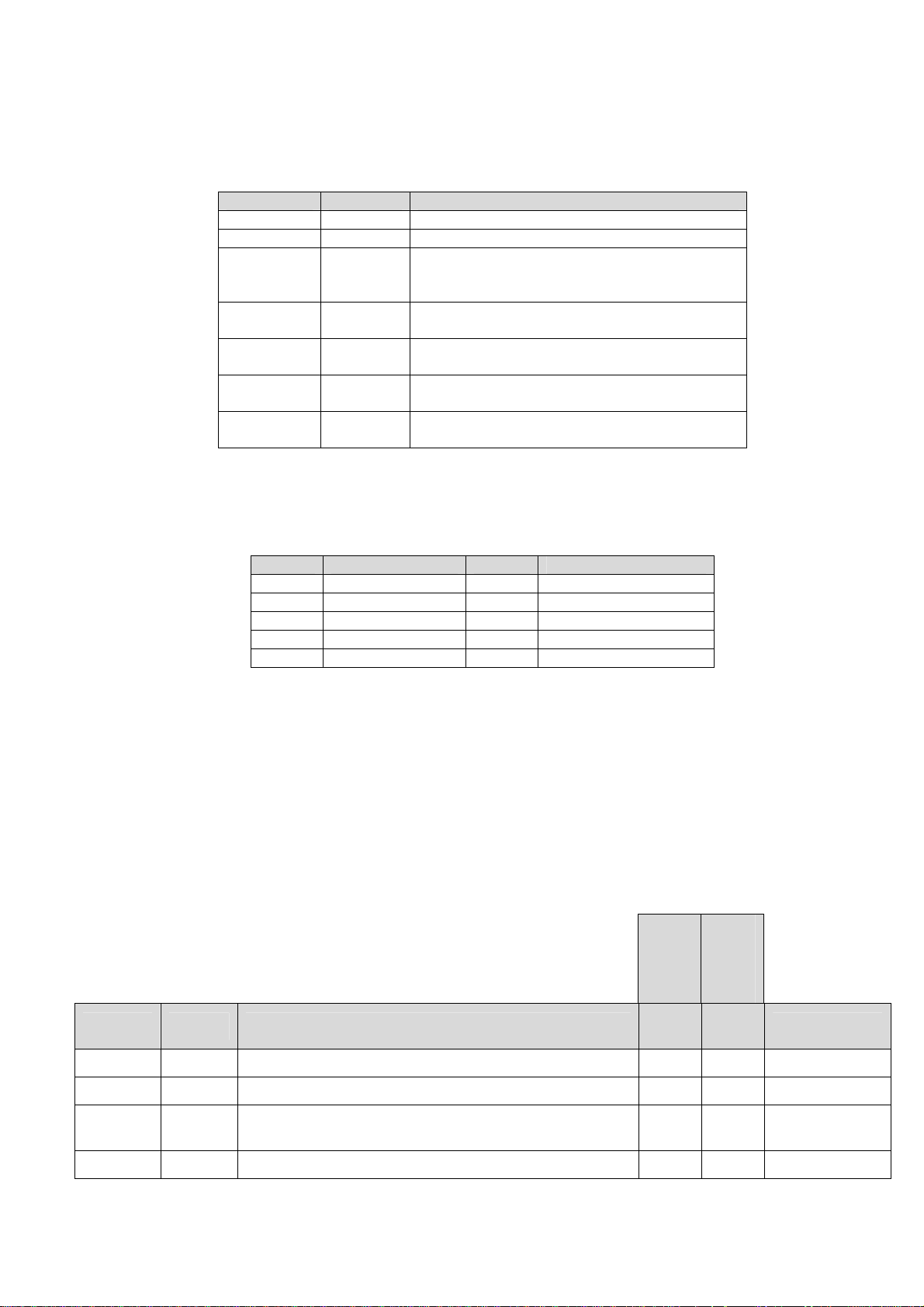

A B SYNC SOURCE

0 0 UOC

0 1 VGA

1 0 NOT USED for this model

1 1 NOT USED

Table 2: H/V Sync Multiplexing Table

The video output from PW1306 is a 48-bit digital RGB bus format and made available on two separate connectors with

TTL control signals (i.e. HS, VS, CLK, etc.). This digital output is intended to interface to TTL compatible display

devices. As PW1306 does not have integrated LVDS transmitter, 24 bit (even part of RGB) video output and TTL control

signals from PW1306 are also inputted to DS90C385 LVDS IC to produce single pixel LVDS output for LVDS

compatible LCDs.

Backlight control is also possible via PW1306 Porta7 pin (PWMOUT, PL176-10), that is a variable duty-cycle pulse

generator output.

MUX BLOCK

TV_[HS,VS]

PC_[HS,VS]

HD_[HS,VS]

YCbC

OUT

V[R,G,B]IN

MUX

74HC4052D

VIDEO

SWITCH

P15V330

TV_[R,G,B]AIN

VIDEO

SWITCH

P15V330

AHSYNC

AVSYNC

Control Signals:

VGA_TV_SW

YUV_TV_SW

RGB

Figure 1: MUX Block.

5

5

15” TFT TV Service Manual 21/06/2005

[R,G,B]

RF in

S-Video in

CVBS in

Scart

[R,G,B]IN

MACROVISION

PC in

FBLIN

YCbCr

Y HD_[HS,VS]

SYNC

SEPARATOR

EL1883

PC_[HS,VS]

V[R,G,B]IN

SAW

74HC14

MUX

BLOCK

MACROVISION

OUT

[YUV,VGA]_SW

A[H,V]SYNC

RGB

VFIN (24,25)

Y4(51)

C4(52)

CVBS3/Y3(58)

AUDIOIN5L(34)

AUDIOIN5R(35)

C2(59)

CVBS2/Y2(55)

IFVO(43)

AUDIOUTSL(36) PCAUDIOINL(49)

AUDIOUTSR(37) PCAUDIOINR(50)

VDRA,HOUT(23,67)

AUDOUTHP[L,R](62,63)

FBLIN

R,G,B(78,79,80)

AUDOUTLS[L,R](60,61)

[R,G,B]OUT(85,86,87)

Comunication

Signals:

I2C and Handhake

PORTD[5,6](58,57)

[H,V]SYNC(65,64)

[R,G,B]AIN(37,43,50)

PORTD7(56)

D[R,G,B]E[0-7], PORTA7(201)

DHS,DVS,DEN,DCLK D[R,G,B]O[0-7]

UOCIII

AUDIOIN3L(56)

AUDIOIN3R(57)

SDA_U, SCL_U

PW1306

HP DRIVER

TDA1308

AUDIO

AMPLIFIER

2xTDA7056

EEPROM

Flash ROM

PC Audio in

Audio in

LVDS

DS90C385

Buffer

PANEL

Figure 2: TV system block diagram.

6

6

15” TFT TV Service Manual 21/06/2005

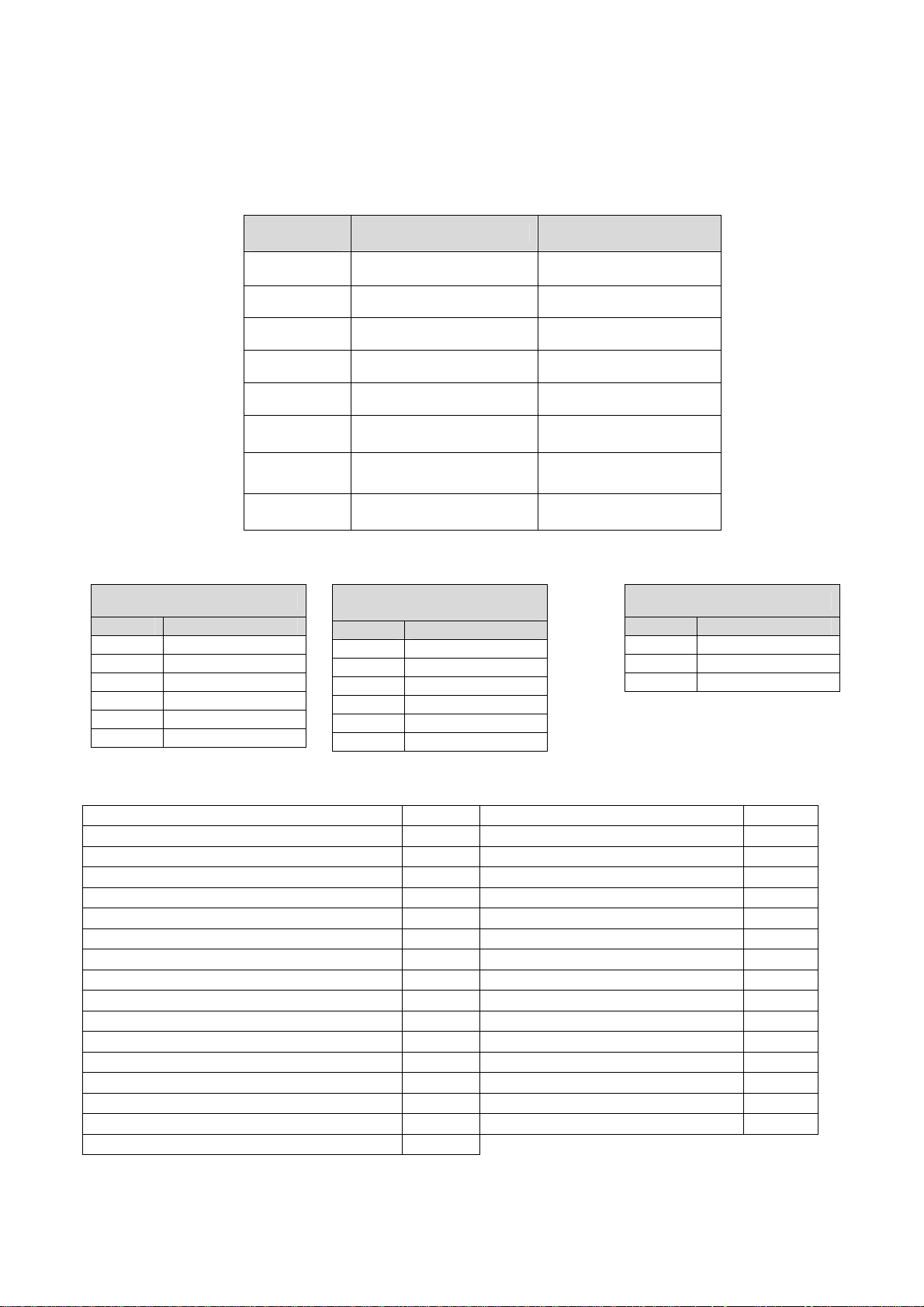

2.3. Side Board(s)

2.3.1.

Front Audio Video board (17FAV18) for 17MB18 main board is detailed in the Table below.

Connector pins are listed in the table below:

Headphone Connector

Pin No: Name

1 Ground

2 R Channel

3 Ground

4 L Channel

5 Ground

6 Mute Signal

The component tree for 17FAV18 is listed in the tabe below:

Definition Position Definition Position

CONN HEADER 3P 2.5MM TOP YELLOW PL100 CAP SMD 4.7NF 50V K (0603) C100

RCA JACK 1P WHITE 28 FAV JK102 CAP SMD 4.7NF 50V K (0603) C101

RCA JACK 1P RED 28 FAV JK103 RES SMD 1/16W 10K J (0603) R102

RCA JACK 1P YELLOW 28 FAV JK101 RES SMD 1/16W 10K J (0603) R103

JACK 4P DIN TYPE FOR SVHS JK104 RES SMD 1/16W 22K J (0603) R104

JACK HEADPHONE HP01/2/3/4/5/6 JK100 RES SMD 1/16W 22K J (0603) R106

CONN MALE 6P MOLEX VERTICAL(TFT PL101 RES SMD 1/16W 470R J (0603) R105

CONN MALE 6P MOLEX VERTICAL(TFT PL102 RES SMD 1/16W 470R J (0603) R107

FIXED COIL 1UH Q45 M-A L102 JUMPER SMD 0603 R100

FERRITE BEAD 3.5X4.7X0.8 L103 JUMPER SMD 0603 R101

FIXED COIL 22UH Q40 K L100 JUMPER SMD 0603 S100

FIXED COIL 22UH Q40 K L101 JUMPER SMD 0603 S102

CAP SMD 100PF 50V J (0603) C102 JUMPER SMD 0603 S103

CAP SMD 100PF 50V J (0603) C103 RES SMD 1/16W 33R J (0603) R108

CAP SMD 100PF 50V J (0603) C104 RES SMD 1/16W 33R J (0603) R109

CAP SMD 100PF 50V J (0603) C105

15” TFT TV Service Manual 21/06/2005

Side Audio Video

Connector

Name

JK104 SVHS Jack 4P DIN Type Side SVHS Input

JK101 RCA Jack Yellow Side CVBS Input

JK103 RCA Jack Red Sid e Audio Input Right

JK102 RCA Jack White Side Audio Input Left

JK100 Headphone Jack Side Headphone

PL100 Connector Header 3P Connector 3P for SVHS

PL102 Connector Male 6P Connector 6P for HP

PL101 Connector Male 6P

Type Function

Connector 6P for CVBS,

Audio R and L

CVBS, Audio L and Audio R

Connector

Pin No: Name

1 Ground

2 Audio L In

3 Ground

4 Audio R In

5 Ground

6 CVBS In

7

SVHS Connector

Pin No: Name

1 Y In

2 Ground

3 C In

2.3.2.

The keypad (17TK33) for 15’’ JVC 17MB18 main board is detailed in the Table below.

Connector PL1 on keypads (connected to the connector PL175 on the main board):

Keypads

Key Name Type Function

Std. By Tact sw. TV stand by on-off button.

TV/AV Tact sw. Input source select button.

Menu Tact sw. Display main menu on the screen. If any menu is

active, display the upper menu. If main menu is

active, turn menu off.

Program- Tact sw. Go to the lower program at any time in TV mode.

In menu mode, go to down menu item.

Program+ Tact sw. Go to the upper program at any time in TV mode.

In menu mode, go to up menu item.

Volume- Tact sw. Decrease the volume level in the volume. In menu

mode, go to left menu item.

Volume+ Tact sw. Increase the volume level in the volume. In menu

mode, go to right menu item.

Pin No: Name Pin No: Name:

1 Volume+ 6 Program+

2 Volume- 7 Program3 Ground 8 Menu

4 Not Connected* 9 TV/AV

5 Ground 10 Stand-by

*Reserved: It can be +5V in the future designs if needed.

2.3.3.

IR&LED board contains LED indicator(s) to show TV’s status (Red for stand-by, green for normal operation) and one IR

receiver to get remote control instructions. All the IR&LED boards have the same circuit and connector pinning but the

different mechanical structure to fit different cabinets (see the related section for schematics and connector pinning).

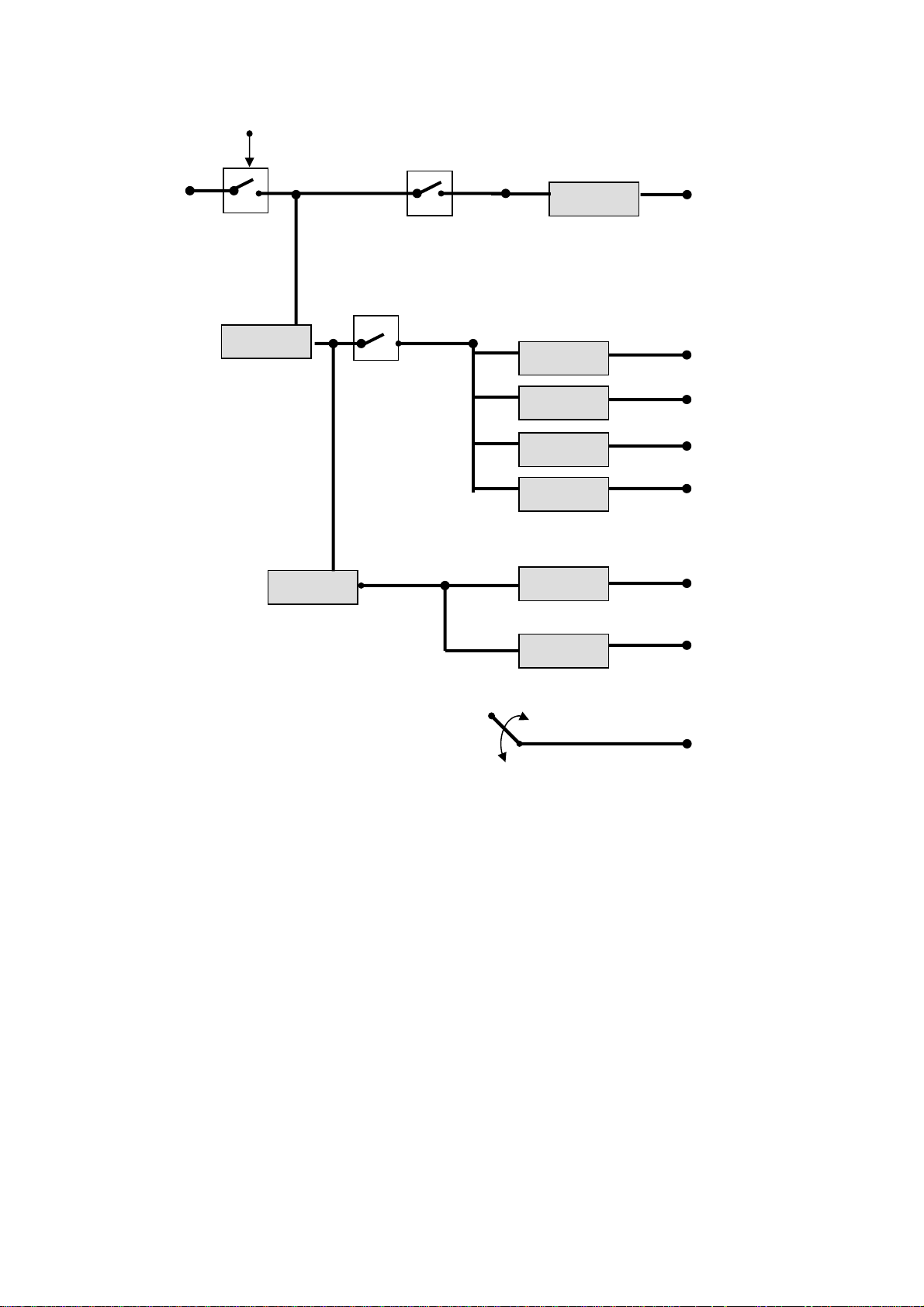

2.4. Power

Several linear regulators and switches are used to generate several separate analog and digital voltage supplies such as +5, +3.3,

+1.8, etc. (Please check the Figure 3, and Table 3 for power management details.)

SIGNAL VALUE SUPPLIED IC s

12V_INV 12 V Panel Inverter - - PSU

12VA 12 V IC410, IC411 Audio Amplifiers X PSU

VCC5A 5 V

V3_3A 3.3 V

IR&Led Board

OFF AT

STDBY

ALWAYS

ON

IC203 UOC, TU200 Tuner, Sync Circuit, IC401

Headphones, IC402 MUX Block, IC400 DDC-EEPROM

IC203 UOC, IC175 Keypad I/O, IC101 I2C-EEPROM X IC502, LM1117

X

SUPPLY

IC505, MC3416

8

15” TFT TV Service Manual 21/06/2005

OFF AT

STDBY

ALWAYS

ON

SIGNAL VALUE SUPPLIED IC s

V3_3D 3.3 V

V1_8D 1.8 V

V1_8A 1.8 V

VADC3 3.3 V

V1_8V1 1.8 V

V1_8V2 1.8 V

IC100 PW1306, IC102 Flash, IC176 LVDS, , X IC500, LM1117

IC100 PW1306 X IC501, LM1117

IC100 PW1306 X IC504, LM1117

IC100 PW1306 X IC503, LM1117

IC203 UOC X

IC203 UOC X

SUPPLY

VPP 3.3 V Panel Display Electronics X

Table 3: Power management table.

9

15” TFT TV Service Manual 21/06/2005

12V

12V_INV

12VA

9V

LM1117

IRF7314

MC34167

LM1117

VCC5

VCC5A

V3_3A

VCC5A

or

V3_3D

or

12VA

V3_3D

LM1117

V1_8D

LM1117

V1_8A

LM1117

VADC3

LM1117

V1_8V1

V1_8V2

VPP

10

15” TFT TV Service Manual 21/06/2005

3. IC AND COMPONENT DESCRIPTIONS

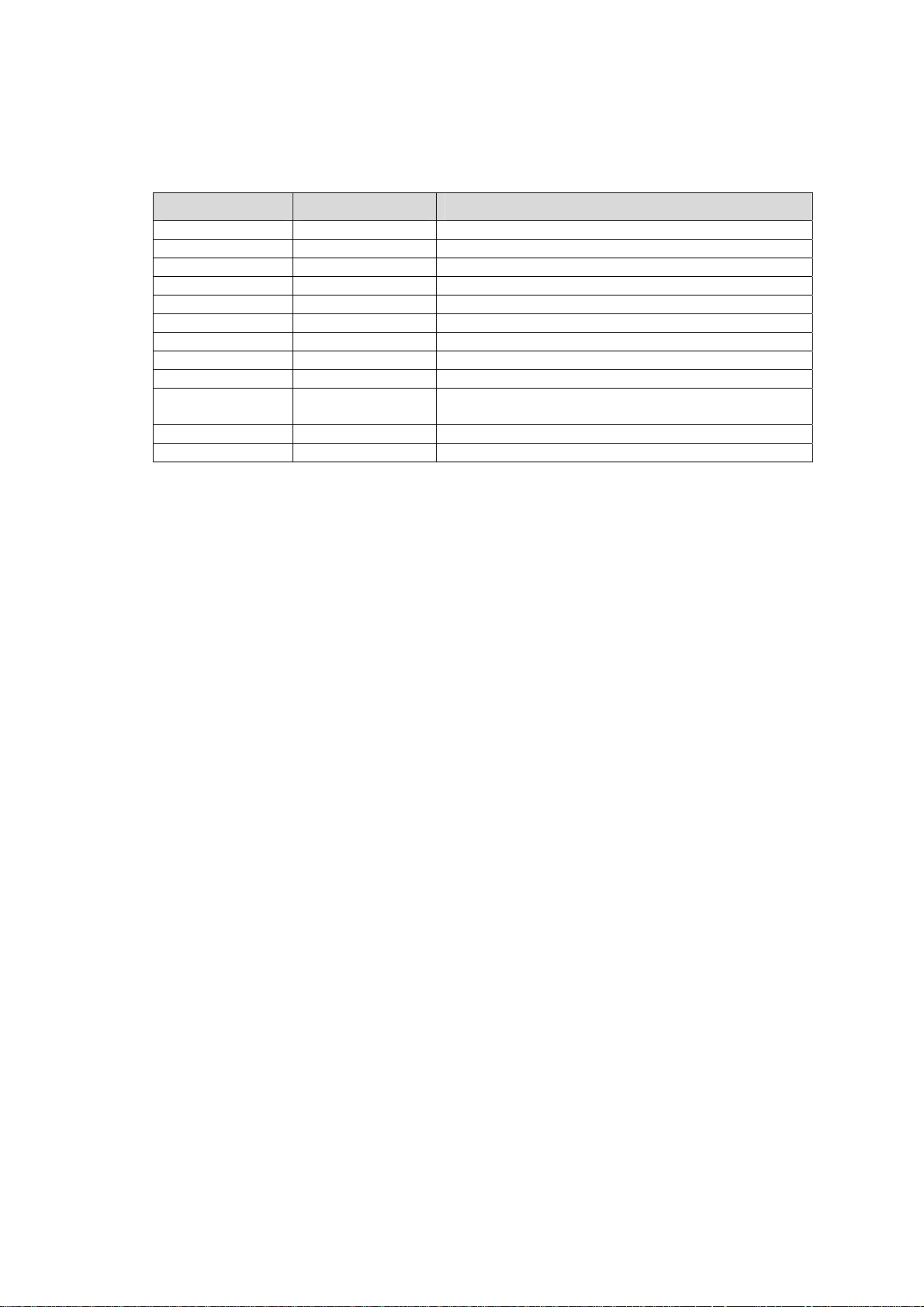

3.1. Basic IC List

No Title Description

IC203 UOCIII Versatile Signal Processor

IC100 PW1306 Video Image Processor with Analog Interface

IC102 MT28F800B3W Flash Memory

IC176 DS90C385 Programmable LVDS Transmitter

IC103 EL1883 Sync Separator

IC405, IC402 P15V330 Wide Bandwidth 2-channel Multiplexer/Demultiplexer

IC404 7 4HC4052 D ual 4-channel Analog Multiplexer

IC410, IC411 TDA7056A Class AB Mono 3W Power Amplifier

IC401 TDA1308 Class AB Stereo Headphone Driver

IC500/1/2/3/4,

IC201

IC400 24LC21

IC101 24LC32

3.2. UOCIII

The UOCIII

series combines the functions of a Video Signal Processor (VSP) together with a FLASH embedded

TEXT/Control/Graphics m-Controller (TCG m-Controller) and US Closed Caption decoder. In addition the following functions

can be added:

• Adaptive digital (4H/2H) PAL/NTSC comb filter

• Teletext decoder with 10 page text memory

• Multi-standard stereo decoder

• BTSC stereo decoder

• Digital sound processing circuit

• Digital video processing circuit

The UOC III series consists of the following 3 basic concepts:

• Stereo versions. These versions contain the TV processor with a stereo audio selector, the TCG m-Controller, the multi-

standard stereo or BTSC decoder, the digital sound processing circuit and the digital video processing circuit. Options are

the adaptive digital PAL/NTSC comb filter and a teletext decoder with 10 page text memory.

• AV stereo versions. These versions contain the TV processor with stereo audio selector and the TCG m-Controller. Options

are the digital sound processing circuit, the digital video processing circuit, the adaptive digital PAL/NTSC comb filter and

a teletext decoder with a 10 page text memory.

• Mono sound versions. These versions contain the TV processor with a selector for mono audio signals and the TCG m-

Controller. Options are the adaptive digital PAL/NTSC combfilter and a teletext decoder with 10 page text memory.

LM1117 Linear Regulator

Serial Electrically Erasable PROM

Serial Electrically Erasable PROM

11

15” TFT TV Service Manual 21/06/2005

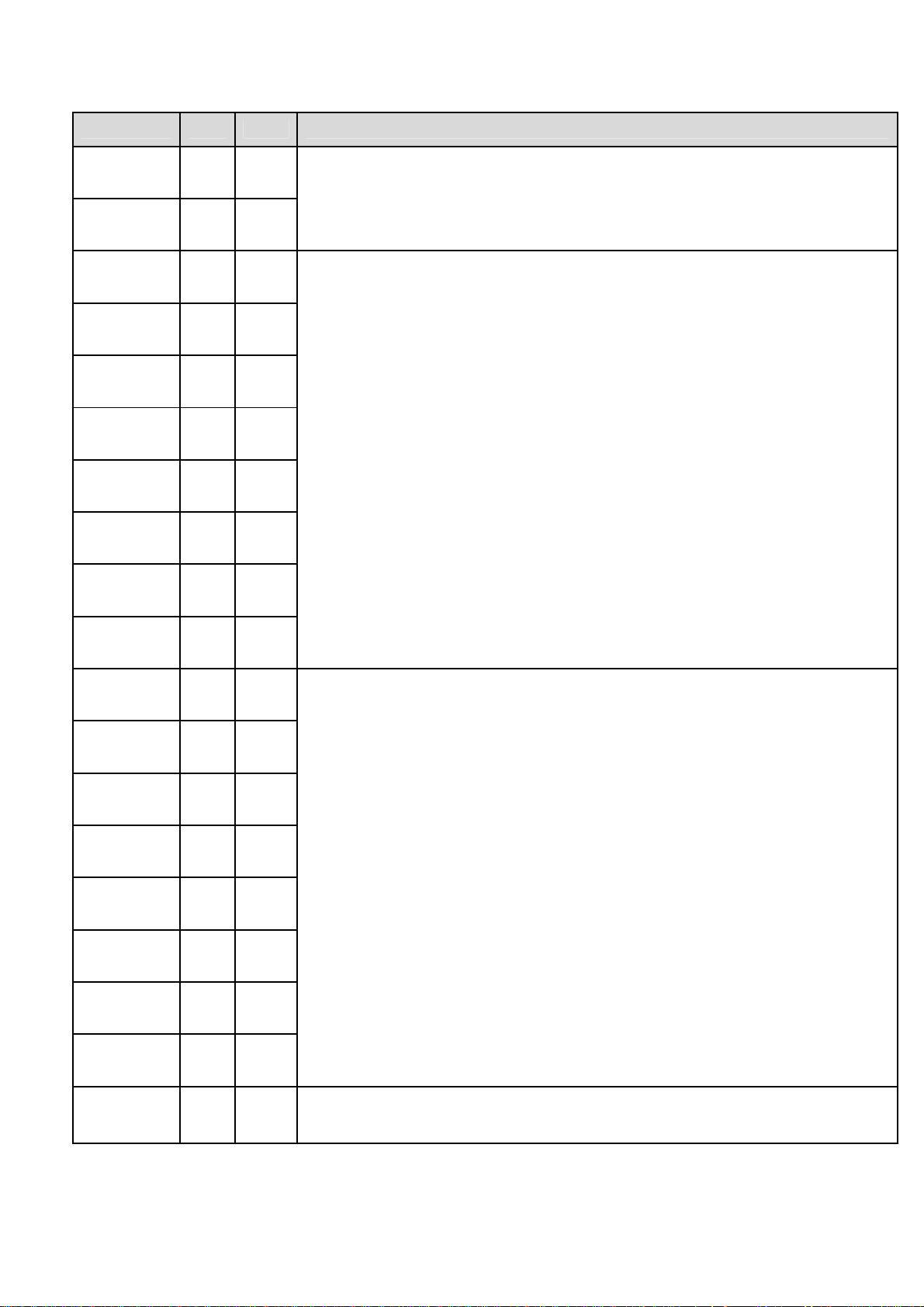

3.2.1.

Pinout

Figure 6: UOCIII Pin configuration “stereo” and “AV-stereo” versions with Audio DSP

SYMBOL

VSSP2 1 1 1 ground

VSSC4 2 2 2 ground

VDDC4 3 3 3 digital supply to SDACs (1.8V)

VDDA3(3.3V) 4 4 4 supply (3.3 V)

VREF_POS_LSL 5

VREF_NEG_LSL+HPL 6

VREF_POS_LSR+HPR 7

STEREO +AV

STEREO

AV STEREO

NO AUDIO

DSP

- -

- -

- -

MONO DESCRIPTION

positive reference voltage SDAC (3.3 V)

negative reference voltage SDAC (0 V)

positive reference voltage SDAC (3.3 V)

12

15” TFT TV Service Manual 21/06/2005

SYMBOL

STEREO +AV

STEREO

VREF_NEG_HPL+HPR 8

VREF_POS_HPR 9

AV STEREO

NO AUDIO

DSP

- -

- -

MONO DESCRIPTION

negative reference voltage SDAC (0 V)

positive reference voltage SDAC (3.3 V)

XTALIN 10 10 10 crystal oscillator input

XTALOUT 11 11 11 crystal oscillator output

VSSA1 12 12 12 ground

VGUARD/SWIO 13 13 13

V-guard input / I/O switch (e.g. 4 mA current

sinking capability for direct drive of LEDs)

DECDIG 14 14 14 decoupling digital supply

stsupply voltage TV-processor (+5 V)

VP1 15 15 15

1

PH2LF 16 16 16 phase-2 filter

PH1LF 17 17 17 phase-1 filter

GND1 18 18 18 ground 1 for TV-processor

SECPLL 19 19 19 SECAM PLL decoupling

DECBG 20 20 20 bandgap decoupling

EWD/AVL (1)

21 21 21 East-West drive output or AVL capacitor

VDRB 22 22 22 vertical drive B output

VDRA 23 23 23 vertical drive A output

VIFIN1 24 24 24 IF input 1

VIFIN2 25 25 25 IF input 2

VSC 26 26 26 vertical sawtooth capacitor

IREF 27 27 27 reference current input

GNDIF 28 28 28 ground connection for IF amplifier

SIFIN1/DVBIN1 (2)

SIFIN2/DVBIN2 (2)

29 29 29 SIF input 1 / DVB input 1

30 30 30 SIF input 2 / DVB input 2

AGCOUT 31 31 31 tuner AGC output

EHTO 32 32 32 EHT/overvoltage protection input

AVL/SWO/SSIF/

REFO/REFIN

(2)(3)

33 33 33 Automatic Volume Levelling / switch output /

sound IF input / subcarrier reference output /

external reference signal input for I signal mixer for

DVB operation

AUDIOIN5

AUDIOIN5L 34 34

- -

34 audio 5 input

-

audio-5 input (left signal)

AUDIOIN5R 35 35 - audio-5 input (right signal)

AUDOUTSL 36 36

-

audio output for SCART/CINCH (left signal)

AUDOUTSR 37 37 - audio output for SCART/CINCH (right signal)

DECSDEM 38 38 38 decoupling sound demodulator

QSSO/AMOUT/AUDEEM

(2)

39 39 39

QSS intercarrier output / AM output / deemphasis

(front-end audio out)

GND2 40 40 40 ground 2 for TV processor

13

15” TFT TV Service Manual 21/06/2005

AV STEREO

NO AUDIO

DSP

MONO DESCRIPTION

SYMBOL

STEREO +AV

STEREO

PLLIF 41 41 41 IF-PLL loop filter

SIFAGC/DVBAGC (2)

DVBO/IFVO/FMRO (2)

42 42 42

43 43 43

AGC sound IF / internal-external AGC for DVB

applications

Digital Video Broadcast output / IF video output /

FM radio output

DVBO/FMRO (2) 44 44 - Digital Video Broadcast output / FM radio output

VCC8V 45 45 45 8 Volt supply for audio switches

AGC2SIF 46

VP2 47 47 47

IFVO/SVO/CVBSI (2)

AUDIOIN4

48 48 48

- -

AUDIOIN4L 49 49

- -

49 audio 4 input

-

AGC capacitor second sound IF

ndsupply voltage TV processor (+5 V)

2

IF video output / selected CVBS output / CVBS

input

audio-4 input (left signal)

AUDIOIN4R 50 50 - audio-4 input (right signal)

CVBS4/Y4 51 51 51 CVBS4/Y4 input

C4 52 52 52 chroma-4 input

AUDIOIN2

AUDIOIN2L/SSIF (3)

- -

53 53

53 audio 2 input

-

audio 2 input (left signal) / sound IF input

AUDIOIN2R 54 54 - audio 2 input (right signal)

CVBS2/Y2 55 55 55 CVBS2/Y2 input

AUDIOIN3 - - 56 audio 3 input

AUDIOIN3L 56 56

-

audio 3 input (left signal)

AUDIOIN3R 57 57 - audio 3 input (right signal)

CVBS3/Y3 58 58 58 CVBS3/Y3 input

C2/C3 59 59 59 chroma-2/3 input

AUDOUTLSL 60 62

AUDOUTLSR 61 63

AUDOUT/AMOUT/FMOU

- -

T

-

audio output for audio power amplifier (left signal)

- audio output for audio power amplifier (right

signal)

62

audio output / AM output / FM output, volume

controlled

AUDOUTHPL 62 - - audio output for headphone channel (left signal)

AUDOUTHPR 63

- -

audio output for headphone channel (right signal)

CVBSO/PIP 64 64 64 CVBS / PIP output

SVM 65 65 65 scan velocity modulation output

FBISO/CSY 66 66 66

flyback input/sandcastle output or composite H/V

timing output

HOUT 67 67 67 horizontal output

VSScomb 68 68 68 ground connection for comb filter

VDDcomb 69 69 69 supply voltage for comb filter (5 V)

VIN (R/PRIN2/CX) 70 70 70

UIN (B/PBIN2) 71 71 71

V-input for YUV interface (2

Xinput)

C

U-input for YUV interface (2

ndR input / PRinput or

ndB input / PB input)

14

15” TFT TV Service Manual 21/06/2005

SYMBOL

STEREO +AV

STEREO

YIN (G/YIN2/CVBS-YX) 72 72 72

AV STEREO

NO AUDIO

DSP

MONO DESCRIPTION

Y-input for YUV interface (2nd G input / Y input or

CVBS/Y

Xinput))

YSYNC 73 73 73 Y-input for sync separator

YOUT 74 74 74 Y-output (for YUV interface)

UOUT (INSSW2) 75 75 75

U-output for YUV interface (2

insertion input)

ndRGB / YPBPR

VOUT (SWO1) 76 76 76 V-output for YUV interface (general purpose

switch output)

rdRGB / YPBPR insertion input

INSSW3 77 77 77

R/PRIN3 78 78 78

G/YIN3 79 79 79

B/PBIN3 80 80 80

3

3

rdR input / PRinput

rdG input / Y input

3

rdB input / PBinput

3

GND3 81 81 81 ground 3 for TV-processor

rdsupply for TV processor

VP3 82 82 82

3

BCLIN 83 83 83 beam current limiter input

BLKIN 84 84 84 black current input

RO 85 85 85 Red output

GO 86 86 86 Green output

BO 87 87 87 Blue output

VDDA1 88 88 88 analog supply for TCG m-Controller and digital

supply for TV-processor (+3.3 V)

VREFAD_NEG 89 89 89 negative reference voltage (0 V)

VREFAD_POS 90 90 90 positive reference voltage (3.3 V)

VREFAD 91

- -

reference voltage for audio ADCs (3.3/2 V)

GNDA 92 92 92 ground

VDDA(1.8V) 93 93 93 analogue supply for audio ADCs (1.8 V)

VDDA2(3.3) 94 94 94 supply voltage SDAC (3.3 V)

VSSadc 95 95 95 ground for video ADC and PLL

VDDadc(1.8) 96 96 96 supply voltage video ADC and PLL

INT0/P0.5 97 97 97

external interrupt 0 or port 0.5 (4 mA current

sinking capability for direct drive of LEDs)

P1.0/INT1 98 98 98 port 1.0 or external interrupt 1

P1.1/T0 99 99 99 port 1.1 or Counter/Timer 0 input

VDDC2 100 100 100 digital supply to core (1.8 V)

VSSC2 101 101 101 ground

P0.4/I2SWS 102

P0.4

-

P0.3/I2SCLK 103

- - port 0.4 or I

102 102 port 0.4

- - port 0.3 or I

2S word select

2S clock

P0.3 - 103 103 port 0.3

P0.2/I2SDO2 104

- - port 0.2 or I

2S digital output 2

15

15” TFT TV Service Manual 21/06/2005

SYMBOL

P0.2 - 104 104 port 0.2

STEREO +AV

STEREO

AV STEREO

NO AUDIO

DSP

MONO DESCRIPTION

P0.1/I2SDO1 105

P0.1

P0.0/I2SDI1/O 106

P0.0

P1.3/T1 107 107 107 port 1.3 or Counter/Timer 1 input

P1.6/SCL 108 108 108

P1.7/SDA 109 109 109

VDDP(3.3V) 110 110 110

P2.0/TPWM 111 111 111 port 2.0 or Tuning PWM output

P2.1/PWM0 112 112 112 port 2.1 or PWM0 output

P2.2/PWM1 113 113 113 port 2.2 or PWM1 output

P2.3/PWM2 114 114 114 port 2.3 or PWM2 output

P3.0/ADC0 115 115 115 port 3.0 or ADC0 input

P3.1/ADC1 116 116 116 port 3.1 or ADC1 input

VDDC1 117 117 117 digital supply to core (+1.8 V)

DECV1V8 118 118 118 decoupling 1.8 V supply

P3.2/ADC2 119 119 119 port 3.2 or ADC2 input

-

-

- - port 0.1 or I

105 105 port 0.1

- - port 0.0 or I

106 106 port 0.0

port 1.6 or I

port 1.7 or I

supply to periphery and on-chip voltage regulator

(3.3 V)

2S digital output 1

2S digital input 1 or I2S digital output

2C-bus clock line

2C-bus data line

P3.3/ADC3 120 120 120 port 3.3 or ADC3 input

VSSC/P 121 121 121 digital ground for m-Controller core and periphery

P2.4/PWM3 122 122 122 port 2.4 or PWM3 output

P2.5/PWM4 123 123 123 port 2.5 or PWM4 output

VDDC3 124 124 124 digital supply to core (1.8V)

VSSC3 125 125 125 ground

P1.2/INT2 126 126 126 port 1.2 or external interrupt 2

P1.4/RX 127 127 127 port 1.4 or UART bus

P1.5/TX 128 128 128 port 1.5 or UART bus

3.3. PW1306

The PW1306 Video Image Processor is a “system-on-a-chip ” that oversamples and processes RGB or YPbPr video from

analog video decoders. The PW1306 integrates video processing, including deinterlacer and video enhancement filters with a

triple ADC. Analog RGB or YPbPr in PC graphics, standard, or high-definition video can be displayed in either 4:3 or 16:9

formats.

• Supports analog video decoders with triple 8-bit Analog-to-Digital Converters (ADCs) up to 140 MSPS conversion rate

• Supports Sync-on-Green (SOG), Sync-on-Luma (SOY),and Composite sync inputs

• 1080i/720p/480p HDTV; 480i and 576i NTSC/PAL SDTV; PC graphics (up to SXGA)

• YPbPr/YCbCr/YUV-to-RGB Color Space Converter with programmable coefficients

• On-chip, bitmap-based, OSD controller with on-chip memory

• 24/30/48-bit RGB output with 135 MPixels/second maximum output rate

16

15” TFT TV Service Manual 21/06/2005

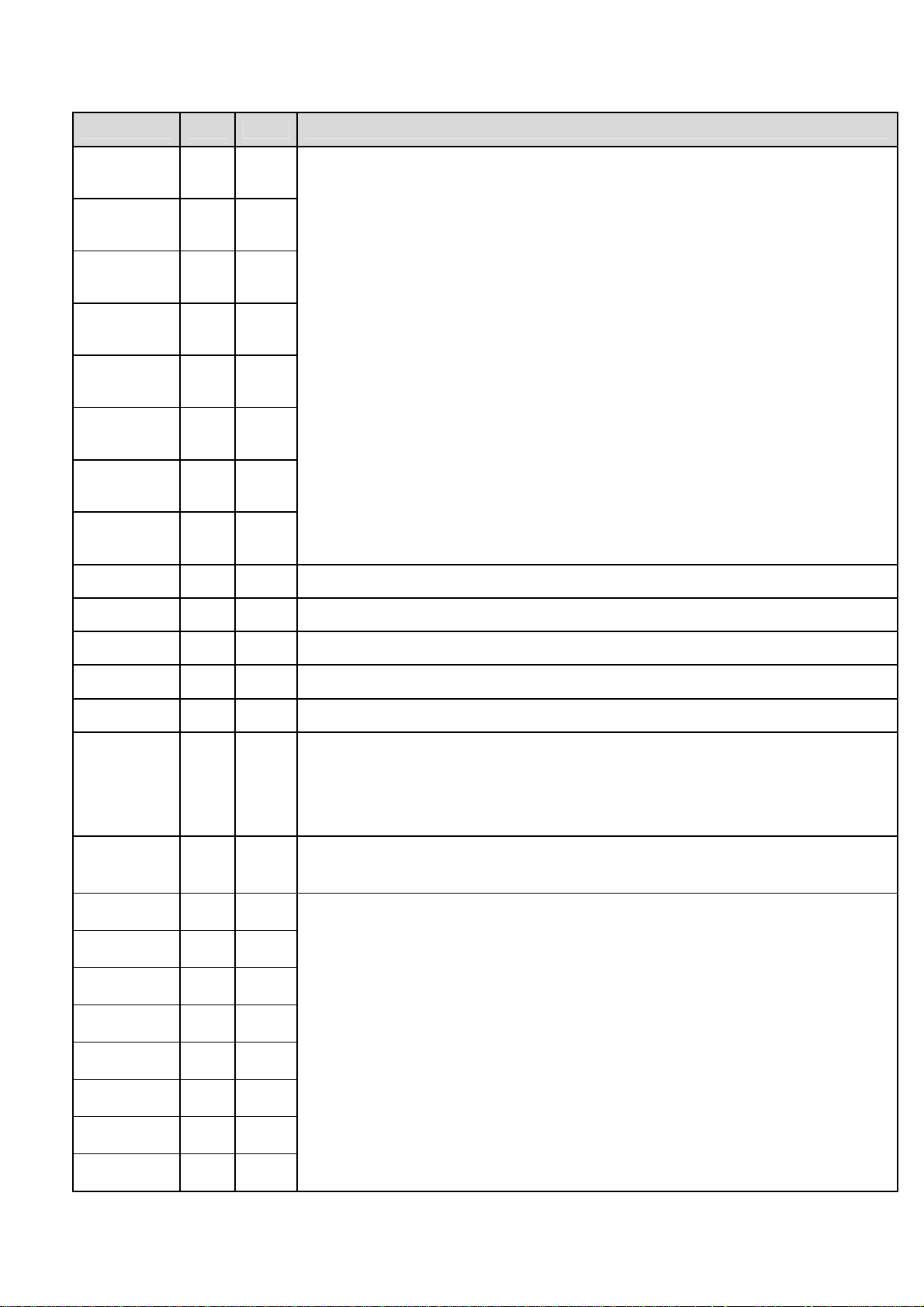

3.3.1.

This section lists the pin functions for the PW1306 208-pin PQFP package. Pin types include:

• I/O SR5 (I/O slew rate-controlled,5V input tolerant)

• I/O D5 (bidirectional, 5-volt tolerant with pull-down)

• I/O U5 (bid irectio nal, 5-volt tolerant with pull-up)

• ID 5 (input, 5-volt tolerant with pull-down)

• OS (output with fixed slew-rate control)

• AI (analog input, 5-volt tolerant)

• DI (digital input, 5-volt tolerant)

• DIS (digital input, 5-volt tolerant, Schmitt trigger)

• I (XTALIN)

• (XTALOUT)

• P (power)

• NC (no connect)

• BOD (bidirectional open drain)

• OSR (output with slew rate)

Pinout

Figure 8: PW1306 Pin configuration.

Signal Pin Type Function

RAIN 37 AI

15” TFT TV Service Manual 21/06/2005

Red/Green/Blue Analog Inputs. These pins receive the Red, Green and Blue, or

17

Signal Pin Type Function

GAIN 43 AI

BAIN 50 AI

SOGIN 44 AI

FILT 23 AI

HSYNC 65 DIS

VSYNC 64 DIS

DCLK 106 OSR

YPbPr/YCbCr/YUV analog signals from the analog video source. For proper

operation of the clamp feature, these inputs must be AC-coupled.

Analog Sync-On-Green or Sync-On-Luma input. Allows recovery of the HSYNC

signal when this pin is AC-coupling to the Green (Red or Blue) analog signal source.

If not used, this pin should be left unconnected.

External PLL Loop Filter. When using the on-chip PLL, this pin must be connected to

an external filter network.

Horizontal Synchronization Input. This digital input signal controls the horizontal scan

frequency by synchronizing the start of the horizontal scan. The logic polarity of this

signal is controlled by the HSPOL bit.

Vertical Synchronization Input. This digital signal controls the vertical scan

frequency.

DPort Pixel Clock. Output clock for the display port pixel data. DCLK is enabled by

the DCLKEN bit and can be inverted by the DCPOL bit. DCLK can be set to run at ½

pixel rate, for dual pixel output mode, by setting the DCK2EN bit. The internal DCLK

clock domain can be disabled by the DCLKOFF bit to reduce power consumption.

DCLKNEG 107 OSR DPort Pixel Clock.

DVS 101 OS

DHS 102 OS

DEN 103 OS

DER0 98 OSR

DPort Vertical Sync. DVS can be either active-high or active-low depending on the

VSPOL bit. Width and timing is controlled by the VPLSE and VDLY registers.

DPort Vertical Sync. DHS can be either active-high or active-low depending on the

HSPOL bit. Sync width can be controlled by the HPLSE register.

DPort Pixel Enable. This signal is active whenever valid data is present. The polarity

is specified by the DENPOL bit.

DEPort Red Pixel Data. In dual pixel output mode these pins are the EVEN red

outputs.

DER1 97 OSR

DER2 94 OSR

DER3 93 OSR

DER4 92 OSR

DER5 91 OSR

18

15” TFT TV Service Manual 21/06/2005

Signal Pin Type Function

DER6 90 OSR

DER7 89 OSR

DEG0 88 OSR

DEG1 87 OSR

DEG2 86 OSR

DEG3 85 OSR

DEPort Green Pixel Data. In dual pixel output mode these pins are the EVEN green

outputs.

DEG4 82 OSR

DEG5 81 OSR

DEG6 80 OSR

DEG7 79 OSR

DEB0 78 OSR

DEB1 77 OSR

DEB2 74 OSR

DEB3 73 OSR

DEB4 71 OSR

DEB5 70 OSR

DEB6 67 OSR

DEPort Blue Pixel Data. In dual pixel output mode these pins are the EVEN blue

outputs.

DEB7 66 OSR

VCLK 72 I/O D5

DVPort Pixel Clock. The VCLK pin is used for DV port image capture. The polarity

can be selected by the VCLKPOL bit.

19

15” TFT TV Service Manual 21/06/2005

Signal Pin Type Function

DVPort Pixel Enable. Used when external flow control capture mode is enabled by

the EXTFCE bit. When VPEN is active, the input data is valid. The polarity can be

VPEN 55 I/O D5

selected by the PENPOL bit. Use of this pin allows non-contiguous input data.

PORTD(7:0) can be used as GPO (Output Only).

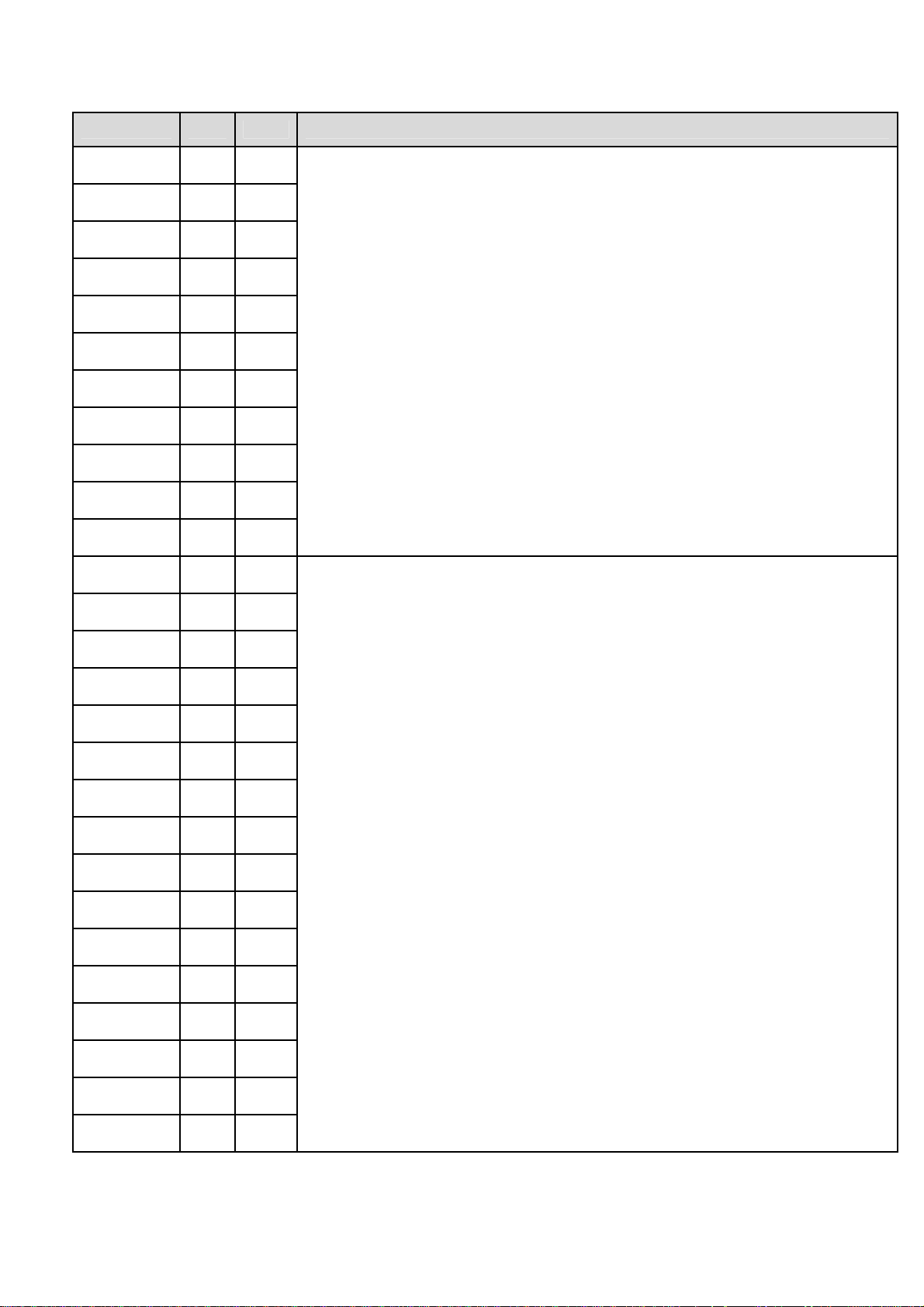

PORTD[0-7]

DOR0 131

DOR1 130

DOR2 129

DOR3 128

DOR4 127

DOR5 126

DOR6 125

DOR7 124

[56-

63]

I/O

I/O

SR5

I/O

SR5

I/O

SR5

I/O

SR5

I/O

SR5

I/O

SR5

I/O

SR5

I/O

SR5

DOPort Red Pixel Data. In dual pixel output mode these pins are the ODD red

outputs. In single pixel output mode these pins are not used.

DOG0 121

DOG1 120

DOG2 119

DOG3 118

DOG4 117

DOG5 116

DOG6 115

DOG7 114

I/O

SR5

I/O

SR5

I/O

SR5

I/O

SR5

I/O

SR5

I/O

SR5

I/O

SR5

I/O

SR5

DOPort Green Pixel Data. In dual pixel output mode these pins are the ODD green

outputs. In single pixel output mode these pins are not used.

20

15” TFT TV Service Manual 21/06/2005

Signal Pin Type Function

DOB0 113

DOB1 112

DOB2 111

DOB3 110

DOB4 109

DOB5 108

DOB6 100

DOB7 99

I/O

SR5

I/O

SR5

I/O

SR5

I/O

SR5

I/O

SR5

I/O

SR5

I/O

SR5

I/O

SR5

DOPort Blue Pixel Data. In dual pixel output mode these pins are the ODD blue

outputs. In single pixel output mode these pins are not used.

WR 195 I/O D5 Write Enable. Low indicates a write to external RAM or other devices.

RD 196 I/O D5 Read Enable. Low indicates a read to external RAM or other devices.

ROMOE 197 OS ROM Output Enable. Low output indicates a read from external ROM.

ROMWE 198 OS ROM Write Enable. Low indicates a write to external ROM.

CS0 199 I/O D5 Miscellaneous Chip Select 0. Low selects external devices.

Miscellaneous Chip Select 1. When EXTRAMEN=0, low selects external devices.

Chip select for external RAM. When EXTRAMEN=1, low selects external RAM.

CS1 200 I/O D5

NMI 194 ID 5

A1 193

A2 192

A3 191

A4 190

A5 189

A6 188

A7 183

A8 182

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

(RAMCS)

Non-Maskable Interrupt. A high input triggers a non-maskable interrupt to the on-chip

microprocessor.

Microprocessor address bus output bits (19:1).

21

15” TFT TV Service Manual 21/06/2005

Signal Pin Type Function

A9 181

A10 180

A11 179

A12 178

A13 177

A14 176

A15 175

A16 164

A17 163

A18 162

A19 161

D0 160

D1 159

D2 158

D3 157

D4 156

D5 155

D6 154

D7 153

D8 152

D9 151

D10 150

D11 149

D12 148

D13 145

D14 144

D15 143

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

I/O

D5

Microprocessor 16-bit bidirectional data bus.

22

15” TFT TV Service Manual 21/06/2005

Signal Pin Type Function

General-purpose I/O port bit controlled by PADAT0 and PAEN0. This pin has one

other possible function when EXTRAMEN=1. When EXTRAMEN=1 and PAEN0=0,

PORTA0 208

I/O

U5

PORTA1 is microprocessor address bit 0 (A0).

General-purpose I/O port bit controlled by PADAT1 and PAEN1. This pin has one

other possible function when EXTRAMEN=1. When EXTRAMEN=1 and PAEN1=0,

PORTA1 207

I/O

U5

PORTA1 is microprocessor byte-high enable (BHEN)

PORTA2 206

PORTA3 205

PORTA4 204

PORTA5 203

PORTA6 202

I/O

U5

I/O

U5

I/O

U5

I/O

U5

I/O

U5

General-purpose I/O port bit controlled by PADAT2 and PAEN2.

General-purpose I/O port bit controlled by PADAT3 and PAEN3. This pin can also

function as an external clock source for DCLK (DCLKEXT) when both the internal

PLLs are disabled or when DPLLBYP=1.

General-purpose I/O port bit controlled by PADAT4 and PAEN4. This pin has one

other possible function when IREN=1. When IREN=1 and PAEN4=1, this pin can

function as an input to the on-chip IR receiver 0. (IRRCVR0)

General-purpose I/O port bit controlled by PADAT5 and PAEN5. This pin has other

possible functions depending on the IREN, EIEN registers. When EIEN=1 and

PAEN5=1, this pin can function as an external interrupt to the on-chip CPU. When

IREN=1 and PAEN5=1, this pin can function as an input to the on-chip IR receiver 1

(IRRCVR1). When DPLLBYP=1 and PAEN=0, this pin becomes the output of the

DCLK PLL. This output can be routed through an external spread spectrum chip and

then back into port A3 (DCLK input) to implement spread spectrum.

General-purpose I/O port bit controlled by PADAT6 and PAEN6. This pin has one

other possible function when PREF1EN=1. When PREF1EN=1 and PAEN6=0,

PORTA6 is a variable duty-cycle pulse reference generator (PWM) output controlled

by PREF1HI and PREF1LO.

General-purpose I/O port bit controlled by PADAT7 and PAEN7. This pin has one

other possible function when PREF0EN=1. When PREF0EN=1 and PAEN7=0,

PORTA7 201

I/O

RXD 53 I/O U5

TXD 54 I/O U5

D5

PORTA7 is a variable duty-cycle pulse reference generator (PWM) output controlled

by PREF0HI and PREF0LO.

Serial Receive Data. RXD is the serial receive data for the on-chip serial port. This

pin can also function as the 2-wire master data pin when 2WMEN=16.

Serial Transmit Data. TXD is the serial transmit data for the on-chip serial port. This

pin can also function as the 2-wire master clock output pin when 2WMEN=16.

TESTEN 137 ID 5 Test Mode Enable. Connect to ground for normal operation.

23

15” TFT TV Service Manual 21/06/2005

Signal Pin Type Function

RESET_N 132 BOD

XI 169 I

Reset Output. RESET_N is a bidirectional pin that can be used to either drive

external logic in the system or receive an external reset signal.

Crystal Input. Connect to external crystal. XI can also function as the MCLK input

LVTTL-level signal from an external oscillator.

XO 170 O Crystal Output. Connect to external crystal.

75,

95,

VDD1

135,

146,

P 1.8V digital core power.

173,

184

76,

96,

VSS

136,

147,

P Digital core ground.

174,

185

68,

83,

104,

VDDQ3

122,

P 3.3V digital I/O power.

133,

171,

186

69,

84,

105,

VSSQ

123,

P Digital I/O ground.

134,

172,

187

VDDPA1 167 P 1.8V analog clock generator power.

VDDPA2 165 P 1.8V analog clock generator power.

VSSPA1 168 P Clock generator analog ground.

VSSPA2 166 P Clock generator analog ground.

22,

PVD

24,

P 1.8V PLL power.

26

21,

PGND

25,

P PLL ground.

27

DVDD1

DGND1

ALVDD

ALGND

1, 3,

20

2, 4,

19

28,

29

30,

31

P 1.8V ADC digital power.

P ADC digital ground.

P 1.8V ADC PLL power.

P ADC PLL ground.

24

15” TFT TV Service Manual 21/06/2005

Signal Pin Type Function

6,

18,

32,

33,

AVDD

36,

39,

P 3.3V ADC analog power.

41,

46,

48,

52

9,

12,

34,

35,

38,

AGND

40,

P ADC analog ground.

42,

45,

47,

49,

51

3.4. M29W800AT

Low Voltage Single Supply Flash Memory to store PW1306 code.

ELECTRONIC SIGNATURE

– Manufacturer Code: 20h

– Top Device Code, M29W800AT: D7h

3.5. DS90C385

The DS90C385 transmitter converts 28 bits of LVCMOS/ LVTTL data into four LVDS (Low Voltage Differential Signaling)

data streams. A phase-locked transmit clock is transmitted in parallel with the data streams over a fifth LVDS link. Every cycle

of the transmit clock 28 bits of input data are sampled and transmitted. At a transmit clock frequency of 85 MHz, 24 bits of

RGB data and 3 bits of LCD timing and control data (FPLINE, FPFRAME, DRDY) are transmitted at a rate of 595 Mbps per

LVDS data channel. Using a 85 MHz clock, the data throughput is 297.5 Mbytes/sec.

• 20 to 85 MHz shift clock support

• Tx power consumption <130 mW (typ) @85MHz Grayscale

• Supports VGA, SVGA, XGA and Dual Pixel SXGA.

• Up to 2.38 Gbps throughput

• Up to 297.5 Megabytes/sec bandwidth

• PLL requires no external components

• Compatible with TIA/EIA-644 LVDS standard

3.6. P15V330

The PI5V330 is a true bidirectional Quad 2-channel multiplexer/demultiplexer that is for both RGB and composite video

switching applications.

• 200 MHz bandwidth

• 3 Ohm on-resistance

• Switching at 10 ns

• 100 mA output current

25

15” TFT TV Service Manual 21/06/2005

3.7. 74HC4052

The 74HC/HCT4052 are dual 4-channel analog multiplexers/demultiplexers with common select logic. Each multiplexer has

four independent inputs/outputs (nY0 to nY3) and a common input/output (nZ). The common channel select logics include two

digital select inputs (S0 and S1) and an active LOW enable input (E).

• Wide analog input voltage range: ± 5 V.

• Low “ON” resistance:

80 Ohm (typ.) at VCC - VEE = 4.5 V

70 Ohm (typ.) at VCC - VEE = 6.0 V

60 Ohm (typ.) at VCC - VEE = 9.0 V

3.8. TDA7056A

The TDA7056A is a mono BTL output amplifier with DCvolume control. It is designed for use in TV and monitors.

• Mute mode, No switch-on and off clicks,

• Thermal protection,

• Short-circuit proof,

• ESD protected on all pins.

3.9. TDA1308

The TDA1308 is an integrated class AB stereo headphone driver contained in an SO8, DIP8 or a TSSOP8 plastic package.

• Wide temperature range

• No switch on/off clicks

• Low power consumption

• Short-circuit resistant

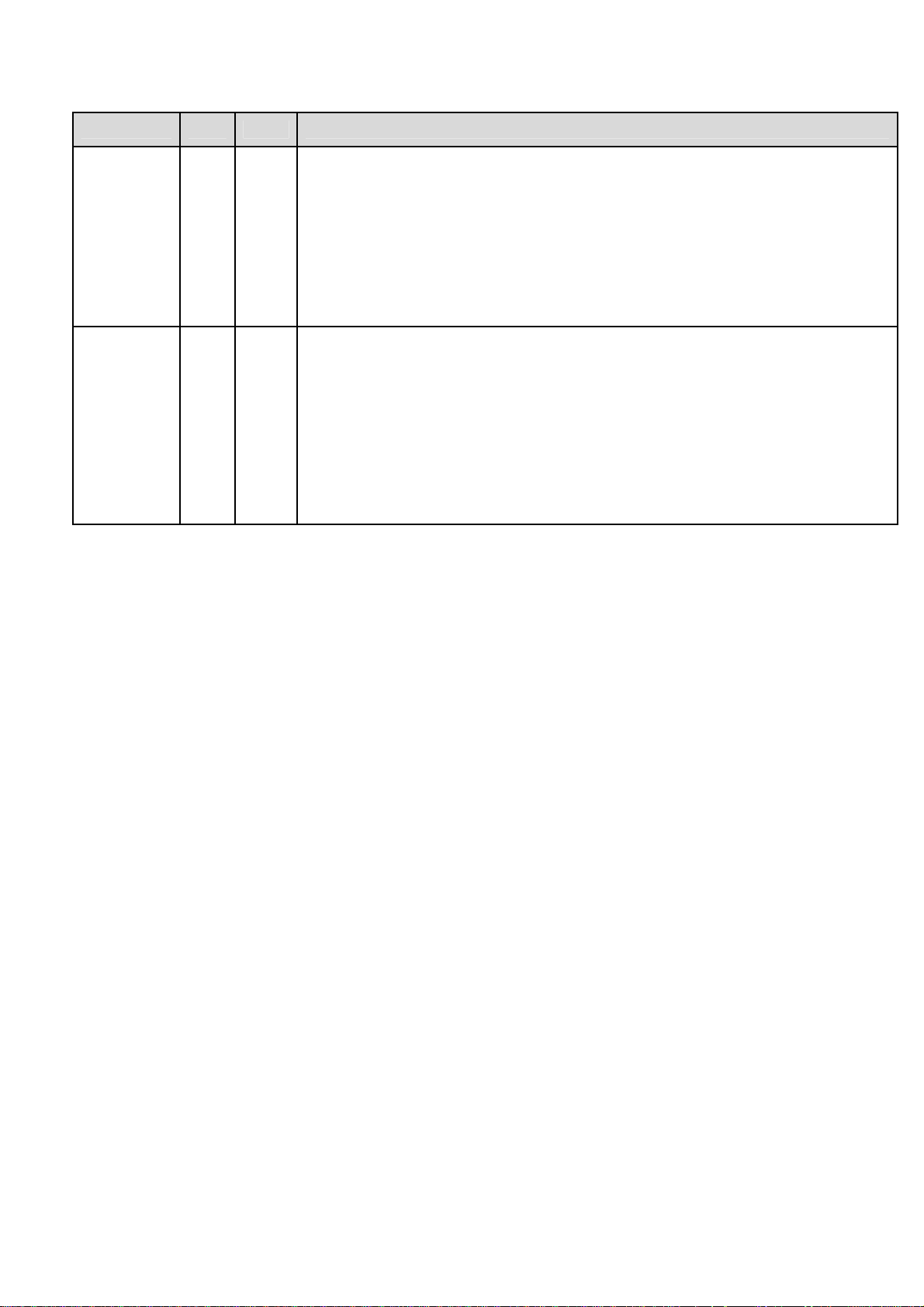

PIN SYMBOL DESCRIPTION PIN VALUE

1 OUTA Output A (Voltage swing) Min : 0.75V, Max : 4.25V

2 INA(neg) Inverting input A Vo(clip) : Min : 1400mVrms

3 INA(pos) Non-inverting input A 2.5V

4 VSS Negative supply 0V

5 INB(pos) Non-inverting input B 2.5V

6 INB(neg) Inverting input B Vo(clip) : Min : 1400mVrms

7 OUTB Output B (Voltage swing) Min : 0.75V, Max : 4.25V

8 VDD Positive supply 5V, Min : 3.0V, Max : 7.0V

26

15” TFT TV Service Manual 21/06/2005

Loading...

Loading...