Page 1

SmartMedia™ 128MByte

Product Manual

®

CORPORATE HEADQUARTERS

140 Caspian Court

Sunnyvale, CA 94089

408-542-0500

FAX: 408-542-0503

URL: http://www.sandisk.com

Page 2

SanDisk® Corporation general policy does not recommend the use of its products in life support applications where in a failure or

malfunction of the product may directly threaten life or injury. Per SanDisk Terms and Conditions of Sale, the user of SanDisk

products in life support applications assumes all risk of such use and indemnifies SanDisk against all damages.

The information in this manual is subject to change without notice.

SanDisk Corporation shall not be liable for technical or editorial errors or omissions contained herein; nor for incidental or

consequential damages resulting from the furnishing, performance, or use of this material.

All parts of the SanDisk documentation are protected by copyright law and all rights are reserved. This documentation may not, in

whole or in part, be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine readable form

without prior consent, in writing, from SanDisk Corporation.

SanDisk and the SanDisk logo are registered trademarks of SanDisk Corporation. SmartMedia is a trademark of Toshiba

Corporation.

Product names mentioned herein are for identification purposes only and may be trademarks and/or registered trademarks of their

respective companies.

© 2001 SanDisk Corporation. All rights reserved.

SanDisk products are covered or licensed under one or more of the following U.S. Patent Nos. 5,070,032; 5,095,344; 5,168,465;

5,172,338; 5,198,380; 5,200,959; 5,268,318; 5,268,870; 5,272,669; 5,418,752; 5,602,987. Other U.S. and foreign patents awarded

and pending.

Lit. No. 80-36-00174 Rev. 1.2 8/01 Printed in U.S.A.

Revision History

• Revision 1—initial release.

• Revision 1.1—several minor edits throughout document.

• Revision 1.2—several minor edits throughout document.

2

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 3

SmartMedia 128MByte Product Manual

Table of Contents

1.0 Description......................................................................................................................5

1.1 Features........................................................................................................................................... 5

2.0 Timing Diagrams ...........................................................................................................11

3.0 Pin Functions .................................................................................................................. 26

3.1 Pin Descriptions............................................................................................................................. 26

3.2 Schematic Cell Layout and Address Assignment..................................................................... 27

3.3 Operation Mode: Logic and Command Tables ......................................................................... 28

4.0 Device Operation ...........................................................................................................30

4.1 Read Mode (1) ................................................................................................................................ 30

4.2 Read Mode (2) ................................................................................................................................ 31

4.3 Read Mode (3) ................................................................................................................................ 32

4.4 Sequential Read (1) (2) (3)............................................................................................................. 32

4.5 Status Read ..................................................................................................................................... 33

4.6 Auto Page Program ....................................................................................................................... 34

4.7 Auto Block Erase............................................................................................................................ 35

4.8 Multi Block Program..................................................................................................................... 36

4.8.1 Internal Addressing in Relation with the Districts......................................................... 37

4.8.2 Address Input Restriction for the Multi Block Program Operation............................. 38

4.8.3 Operating Restriction During the Multi Block Program Operation............................. 38

4.9 Status Read Operation .................................................................................................................. 38

4.10 Multi District Block Erase............................................................................................................. 39

4.10.1 Internal Addressing in Relation with the Districts......................................................... 39

4.10.2 Address Input Restriction for the Multi District Block Erase Operation .................... 40

4.11 Reset................................................................................................................................................. 40

4.12 ID Read............................................................................................................................................ 42

5.0 Application Notes and Comments.............................................................................. 43

5.1 Prohibition of Unspecified Commands ...................................................................................... 43

5.2 Restriction of Commands While in Busy State.......................................................................... 43

5.3 Pointer Control for 00H, 01H and 50H ....................................................................................... 43

5.4 Acceptable Commands After Serial Input Command 80H ..................................................... 44

5.5 Status Read During a Read Operation........................................................................................ 45

5.6 Auto-Programming Failure.......................................................................................................... 45

5.7 Addressing for Program Operation ............................................................................................ 45

5.8

R/B: Termination for the Ready/Busy Pin ( R/B)................................................................. 46

5.9 Status After Power-on................................................................................................................... 46

5.10 Power-on/off Sequence ................................................................................................................ 46

5.11 Note Regarding the

5.12 When Five Address Cycles are Input.......................................................................................... 48

5.13 Several Programming Cycles on the Same Page (Partial Page Program).............................. 49

5.14 Note Regarding the

5.15 Invalid Blocks (Bad Blocks).......................................................................................................... 50

5.16 Failure Phenomena for Program and Erase Operations........................................................... 52

5.17 Chattering of Connector ............................................................................................................... 52

WP Signal ................................................................................................. 47

RE Signal ................................................................................................... 49

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

3

Page 4

SmartMedia 128MByte Product Manual

Table of Contents (continued)

6.0 Handling Precautions....................................................................................................53

7.0 Package Dimensions......................................................................................................54

7.1 SmartMedia Card Dimensions..................................................................................................... 54

Ordering Information and Technical Support.......................................................................55

Ordering Information................................................................................................................57

SmartMedia Card ..................................................................................................................................... 57

Technical Support Services.......................................................................................................58

Direct SanDisk Technical Support .........................................................................................................58

SanDisk Worldwide Web Site................................................................................................................. 58

SanDisk Sales Offices................................................................................................................59

Limited Warranty.......................................................................................................................63

4

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 5

1.0 Description

SmartMedia 128MByte Product Manual

The SanDisk SmartMedia Card is a 3.3-V 1-Gbit (1,107,296,256) NAND Electrically Erasable and

Programmable Read-Only Memory (NAND E

2

PROM) device, organized as 528 bytes X 32 pages X 8192

blocks. This device has a 528-byte static register which allows program and read data to be transferred

between the register and the memory cell array in 528-byte increments. The Erase operation is

implemented in a single block unit (16 Kbytes + 512 bytes: 528 bytes X 32 pages).

The SanDisk SmartMedia Card is a serial-type memory device which uses the I/O pins for both address

and data input and output as well as for command inputs. The Erase and Program operations are

automatically executed making the device ideal for applications such as solid-state file storage, voice

recording, image storage for digital cameras and other systems which require high-density non-volatile

memory data storage.

1.1 Features

• Organization

- Memory cell array 528 × 128K × 8 x 2

- Data Register 528 × 8

- Page size 528 bytes

- Block size (16K + 512) bytes

• Modes

- Read, Reset, Auto Page Program

- Auto Block Erase, Status Read

- Multi Block Program, Multi Block Erase

• Mode Control

- Serial Input/Output

- Command control

TM

• Complies with the SmartMedia

SSFDC Forum (SmartMedia Card).

• Power Supply—V

= 2.7 V to 3.6 V

CC

• Program/Erase Cycles — 1E5 cycles (with ECC)

• Access time

- Cell array to register 25 µs max

- Serial Read Cycle 50 ns min

• Operating current

- Read (50 ns cycle) 10 mA typ.

- Program (avg.) 10 mA typ.

- Erase (avg.) 10 mA typ.

- Standby 100 µA max

• Package

- SDSM-128-101-01: SmartMedia Card (Weight: 1.8g typical)

Electrical Specification and Data Format Specification issued by

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

5

Page 6

SmartMedia 128MByte Product Manual

123456

CLE ALE WE WP I/O2I/O1 I/O3 I/O4V

ss

22 21 20 19 18 17 16 15 14 13 12

CE RE

V

CC

R/B

GND LVD I/O8 I/O7 I/O6 I/O5 V

7891011

VssV

ss

I/O1 to 8

CC

CE

WE

RE

CLE

ALE

WP

R/B

GND

LVD

V

CC

V

SS

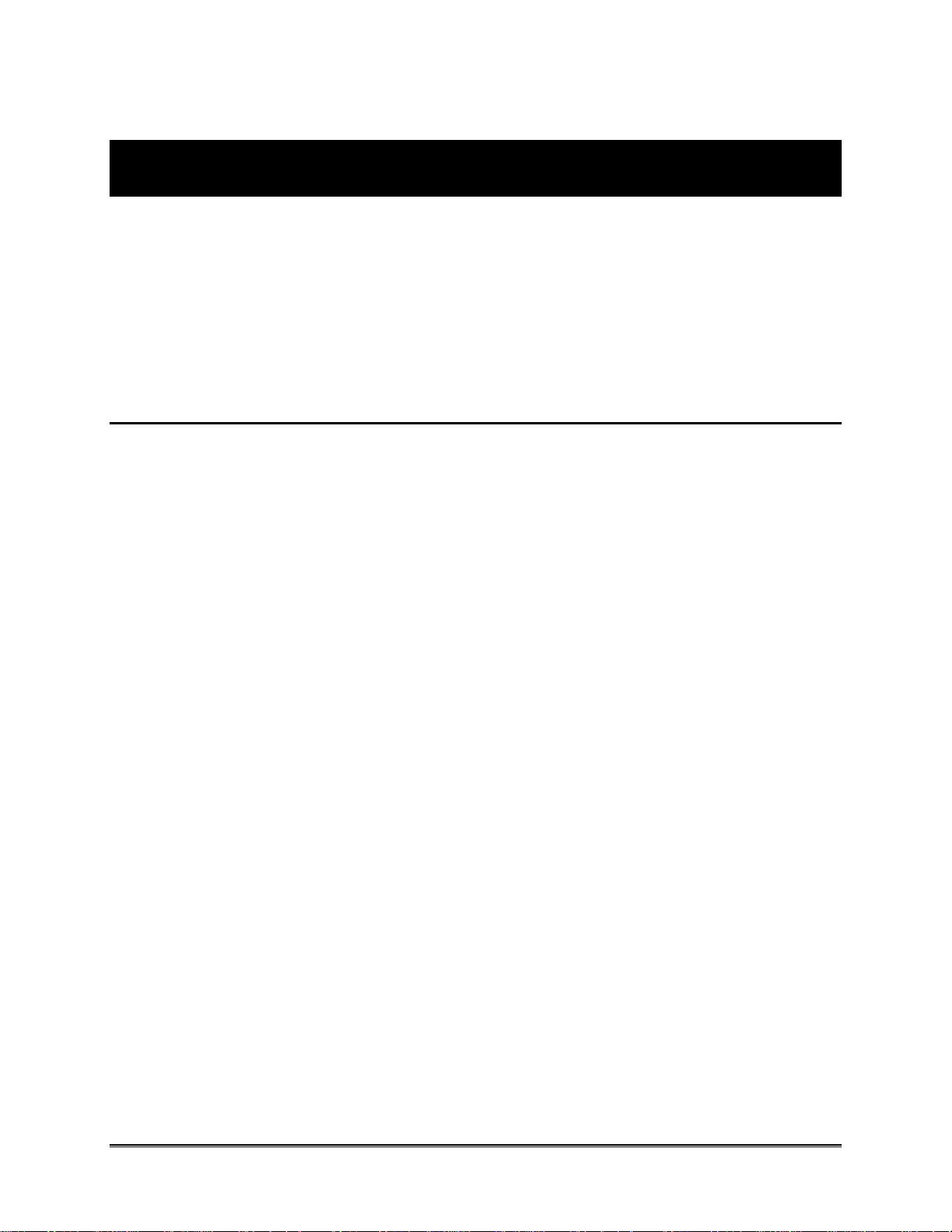

Figure 1-1 1024 Mbit SmartMedia Card Pin Assignments

PIN NAMES

I/O Port

Chip Enable

Write Enable

Read Enable

Command Latch Enable

Address Latch Enable

Write Protect

Ready/Busy

Ground Input

Low Voltage Detect

Power Supply

Ground

(Top View)

Figure 1-2 Block Diagram

6

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 7

SmartMedia 128MByte Product Manual

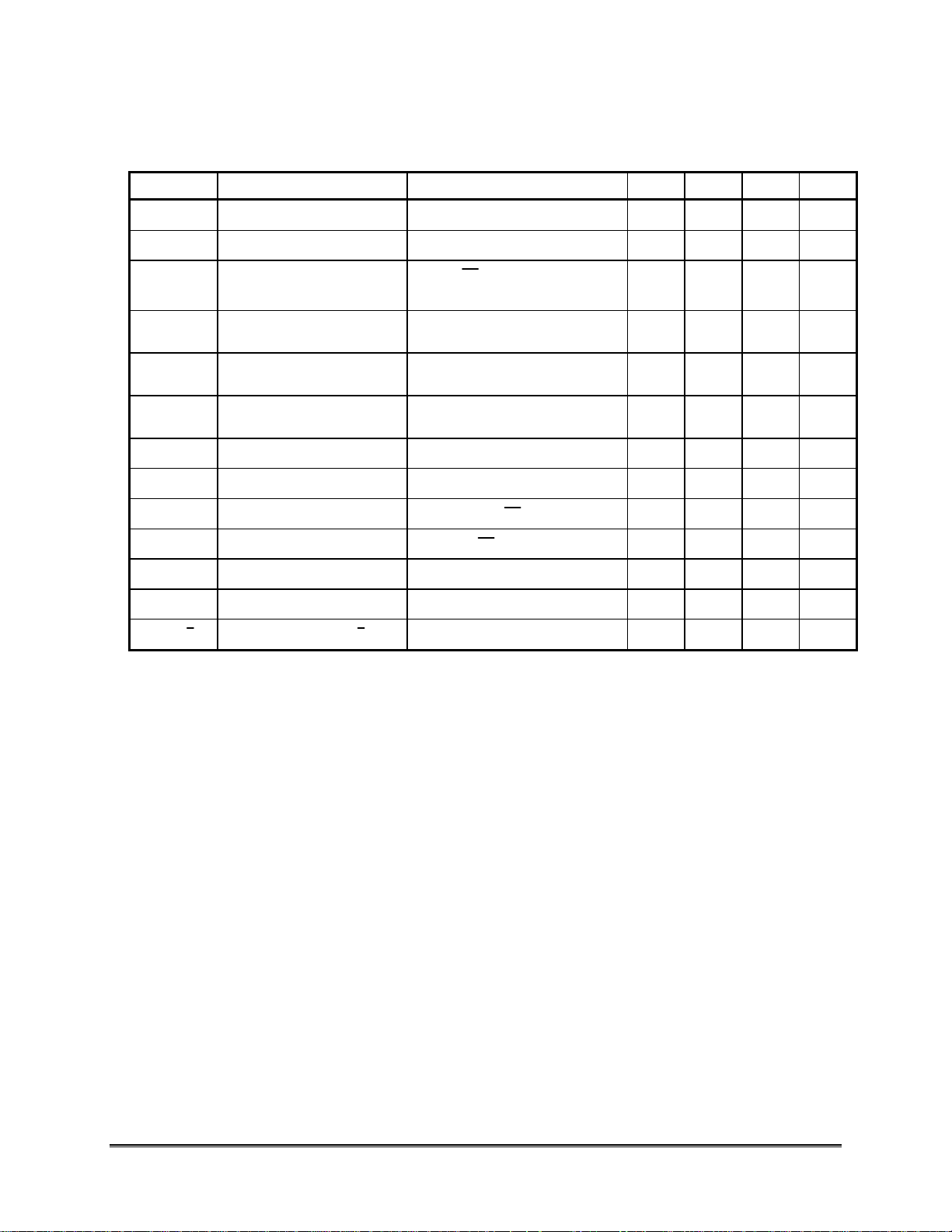

Table 1-1 Absolute Maximum Ratings

Symbol Item Value Unit

V

V

T

T

CC

V

IN

I/O

P

STG

OPR

Power Supply Voltage

Input Voltage

Input /Output Voltage

D

Power Dissipation

Storage Temperature

Operating Temperature

−0.6 to 4.6

−0.6 to 4.6

-0.6 V to V

(≤4.6 V)

−20 to 65

0 to 55

0.3

+ 0.3 V

CC

V

V

V

W

°C

°C

Table 1-2 Capacitance *(Ta = 25°C, f = 1 MHz)

Symbol Parameter Condition Min. Max. Unit

CIN

C

OUT

Input

Output

VIN = 0 V

V

OUT

* This parameter is periodically sampled and is not tested for every device.

= 0 V

20 pF

20 pF

Table 1-3 Valid Blocks

Symbol Parameter Min. Typ. Max. Unit

NVB

Notes: (1) The SmartMedia Card occasionally contains unusable blocks. Refer to section 5.15 toward the end of this

document.

(2) SSFDC Forum Spec. : 1002 MIN per Zone (each 16 k Bytes).

(1)

Number of Valid Blocks 8032

(2)

- 8192 Blocks

Table 1-4 Recommended DC Operating Conditions

Symbol Parameter Min. Typ. Max. Unit

VCC

VIH

VIL

* −2 V (pulse width ≤ 20 ns)

Power Supply Voltage 2.7 3.3 3.6 V

High Level Input Voltage 2.0

Low Level Input Voltage -0.3*

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

VCC + 0.3

V

0.8 V

7

Page 8

SmartMedia 128MByte Product Manual

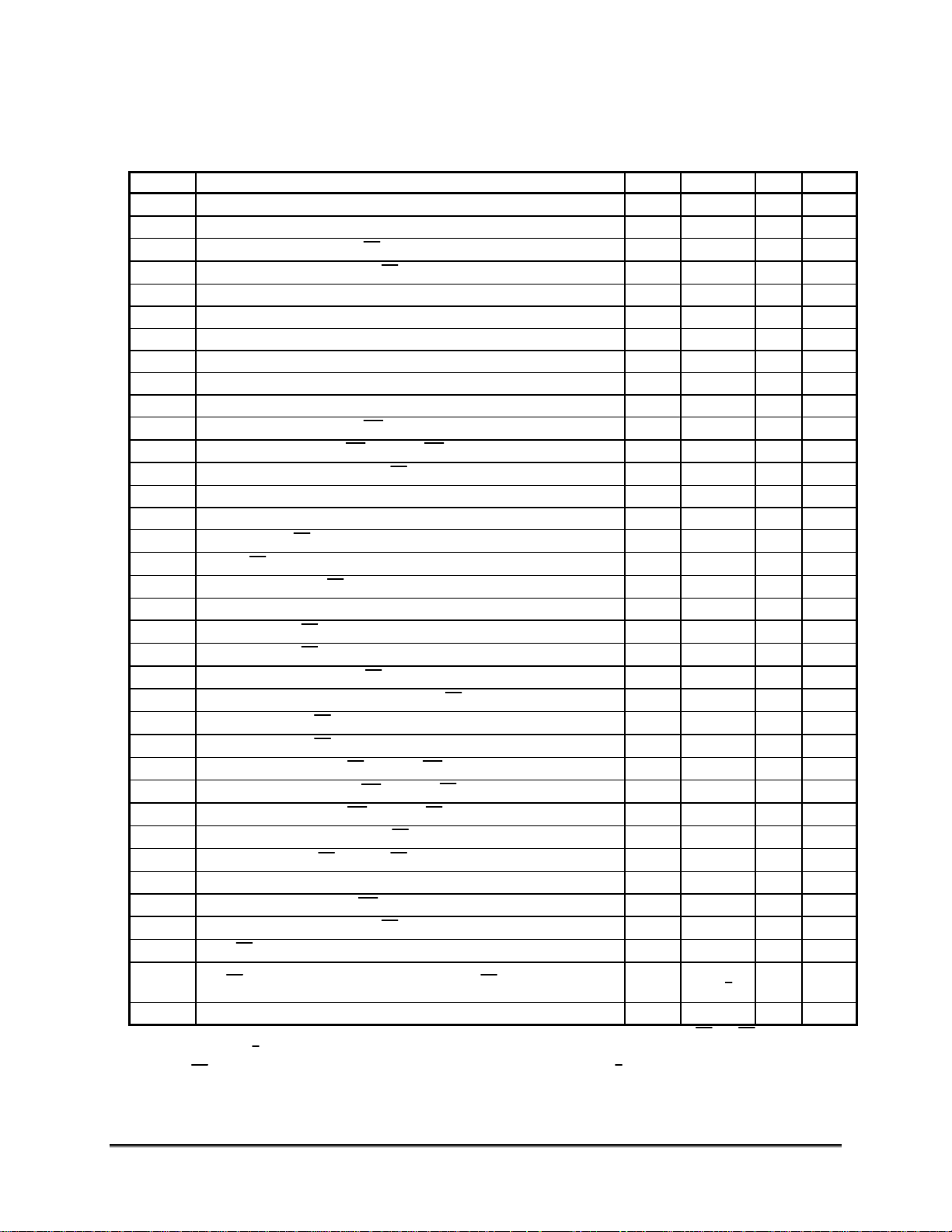

Table 1-5 DC Characteristics

(Ta = 0 to 70° C, V

= 2.7 V to 3.6 V)

CC

Symbol Parameter Condition Min. Typ. Max. Unit

IIL

ILO

I

CCO1

I

CCO3

I

CCO4

I

CCO5

I

CCO7

I

CCO8

I

CCS1

I

CCS2

VOH

VOL

Input Leakage Current

Output Leakage Current

Operating Current

(Serial Read)

Operating Current

(Command Input)

Operating Current

(Data Input)

Operating Current

(Address Input)

Programming Current

Erasing Current

Standby Current

Standby Current

High Level Output Voltage

Low Level Output Voltage

VIN = 0 V to VCC

V

= 0.4 V to VCC

OUT

= VIL, I

CE

t

t

t

t

cycle

cycle

cycle

cycle

OUT

= 50 ns

= 50 ns

= 50 ns

= 50 ns

CE = VIH

CE = VCC − 0.2 V

IOH = −400 µA

IOL = 2.1 mA

= 0 mA,

±10 µA

±10 µA

10 30 mA

10 30 mA

10 30 mA

10 30 mA

10 30 mA

10 30 mA

2.4

1 mA

100

µA

0.4 V

V

IOL (R/B )

Output current of R/B

pin

V

OL

= 0.4 V

8

mA

8

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 9

SmartMedia 128MByte Product Manual

Table 1-6 AC Characteristics and Recommended Operating Conditions

(Ta = 0 to 70°C, V

= 2.7 V to 3.6 V)

CC

Symbol Parameter Min. Max. Unit Notes

t

CLS

t

CLH

tCS

tCH

tWP

t

ALS

t

ALH

tDS

tDH

tWC

tWH

tWW

tRR

tRP

tRC

t

REA

t

CEH

t

REAID

tOH

t

RHZ

t

CHZ

t

REH

tIR

t

RSTO

t

CSTO

t

RHW

t

WHC

t

WHR

t

AR1

tCR

tR

tWB

t

AR2

tRB

t

CRY

t

RST

RE Access Time (Serial Data Access)

CE

High Time for Last Address in Serial Read Cycle

RE High to Output High Impedance

CE

Output High Impedance to

Memory Cell Array to Starting Address

ALE Low to

RE Last Clock Rising Edge to Busy (in Sequential Read)

CE

High to Ready (When interrupted by CE in Read Mode)

Device Reset Time (Read/Program/Erase)

CLE Setup Time 0

CLE Hold Time 10

CE

Setup Time

CE

Hold Time

Write Pulse Width 25

ALE Setup Time 0

ALE Hold Time 10

Data Setup Time 20

Data Hold Time 10

Write Cycle Time 50

WE High Hold Time

WP High to WE Low

Ready to

RE Falling Edge

Read Pulse Width 35

Read Cycle Time 50

RE Access Time (ID Read)

Data Output Hold Time 10

High to Output High Impedance

RE High Hold Time

RE Access Time (Status Read)

CE

Access Time (Status Read)

RE High to WE Low

WE High to CE Low

WE High to RE Low

ALE Low to

CE

Low to RE Low (ID Read)

RE Low (ID Read)

WE

High to Busy

RE Low (Read Cycle)

Note: (1) Sequential Read is terminated when t

than 30ns, R/B

(2) CE

High to Ready time depends on the pull-up resistor tied to the R/B pin. (Refer to section 5.8.)

signal stays Ready.

0

10

15

100

20

100

35 ns

35 ns

15

RE Rising Edge

0

0

30

30

100

100

50

is greater than or equal to 100 ns. If the RE to CE delay is less

CEH

30 ns

20 ns

35 ns

45 ns

25

200 ns

200 ns

1 +

(R/B)

t

r

6/10/500

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns (1)

ns

ns

ns

ns

ns

ns

ns

ns

µs

ns

µs

µs

(2)

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

9

Page 10

SmartMedia 128MByte Product Manual

Table 1-7 AC Test Conditions

Parameter Conditions

Input level 2.4 V, 0.4 V

Input pulse rise and fall time 3ns

Input comparison level 1.5 V, 1.5 V

Output data comparison level 1.5 V, 1.5 V

Output load

CE

RE

525 526 527

R/B

Figure 1-3

Table 1-8 Programming and Erasing Characteristics

(Ta = 0 to 70°C, VCC = 2.7 V to 3.6 V)

CL (100 pF) + 1 TTL

t

100 ns

CEH >

*

A

Busy

: 0 to 30_ns Busy signal is not output.

A

*

: V

or V

IH

IL

Symbol Parameter Min. Typ. Max. Unit Notes

t

PROG

t

DBSY

t

MBPBSY

N

t

BERASE

Average Programming Time

Dummy Busy Time for Multi Block

Programming

Multi Block Program Busy Time

Number of Programming Cycles on

Same Page

Block Erasing Time

200 1000

2 10

200 1000

µs

µs

µs

(1)

3

2 10 ms

Notes: (1) Refer to section 5.13.

10

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 11

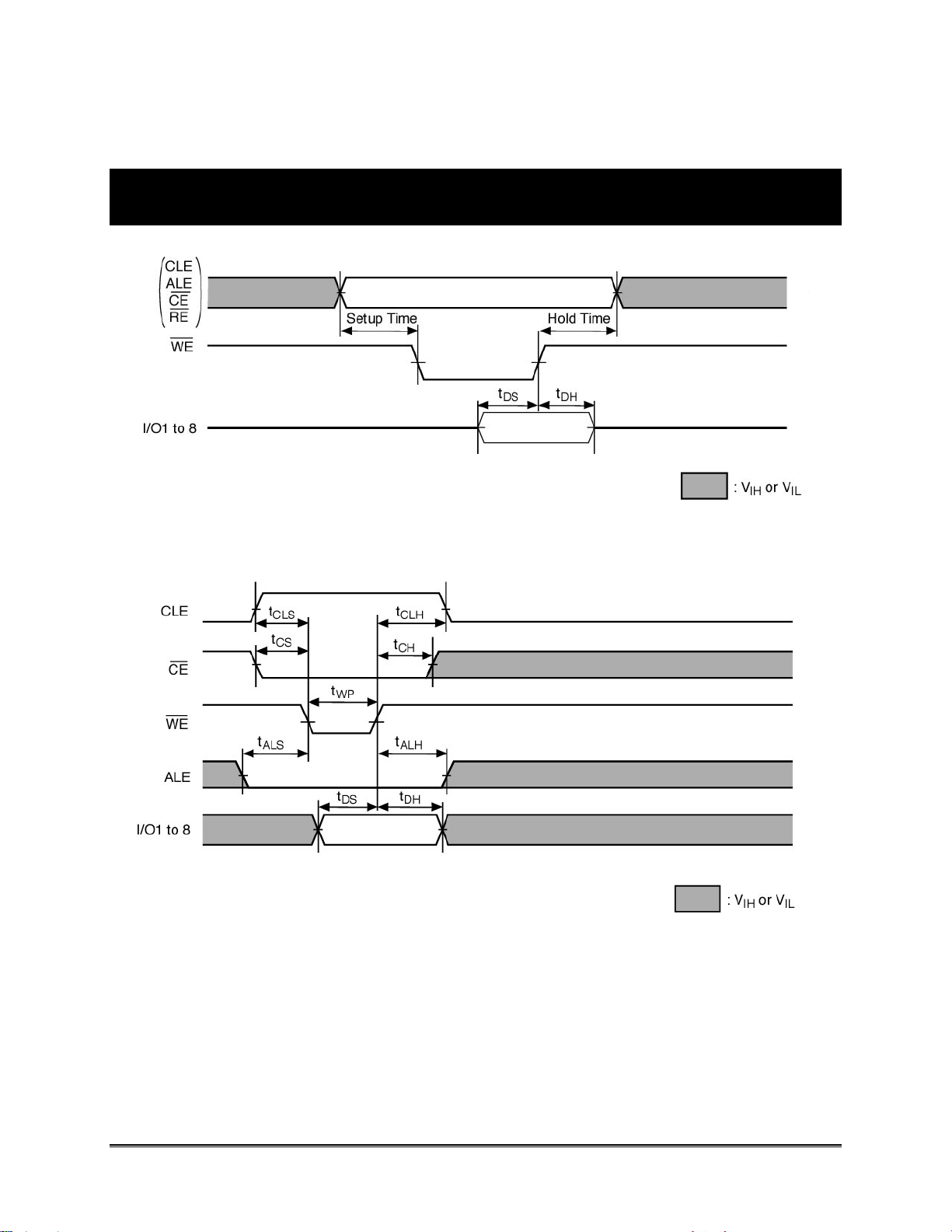

2.0 Timing Diagrams

SmartMedia 128MByte Product Manual

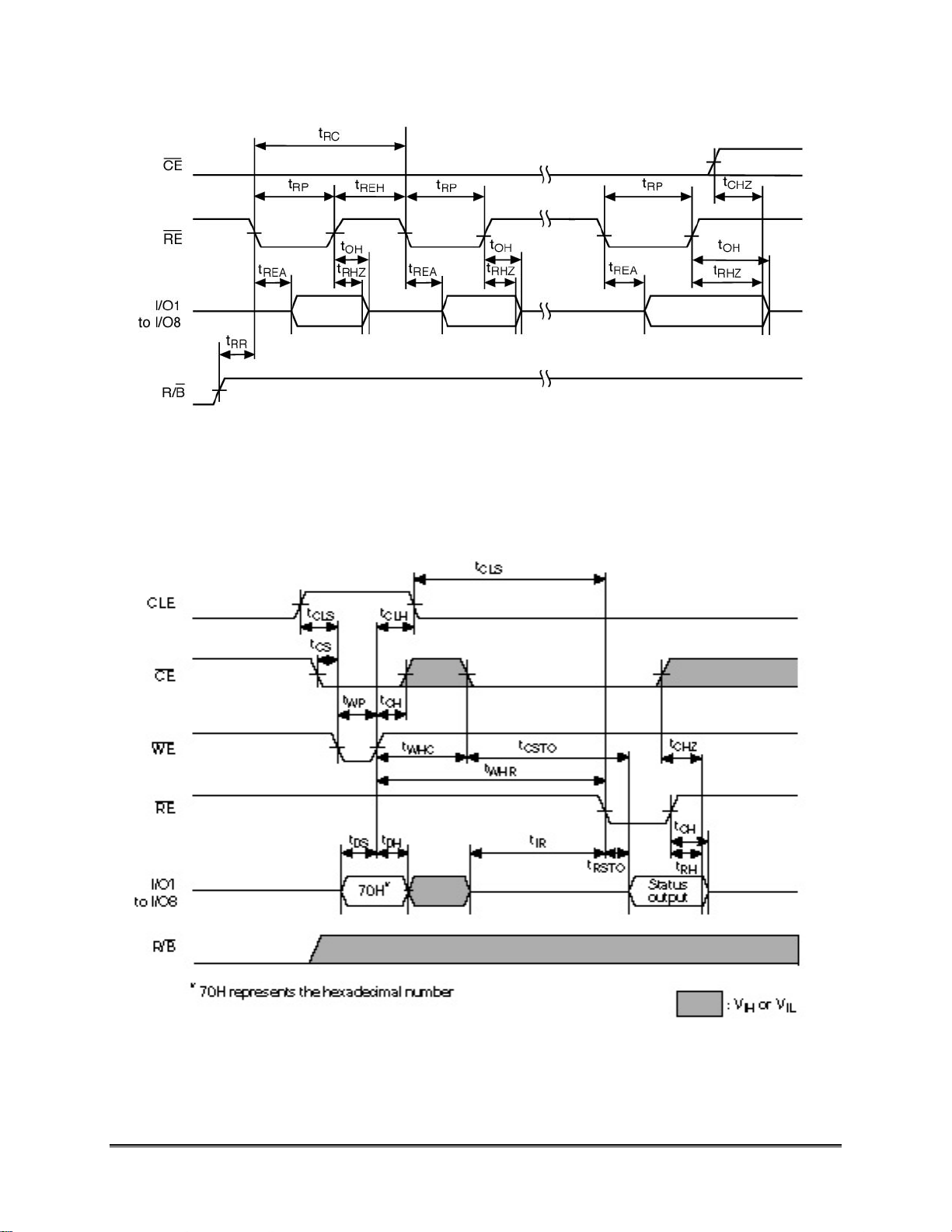

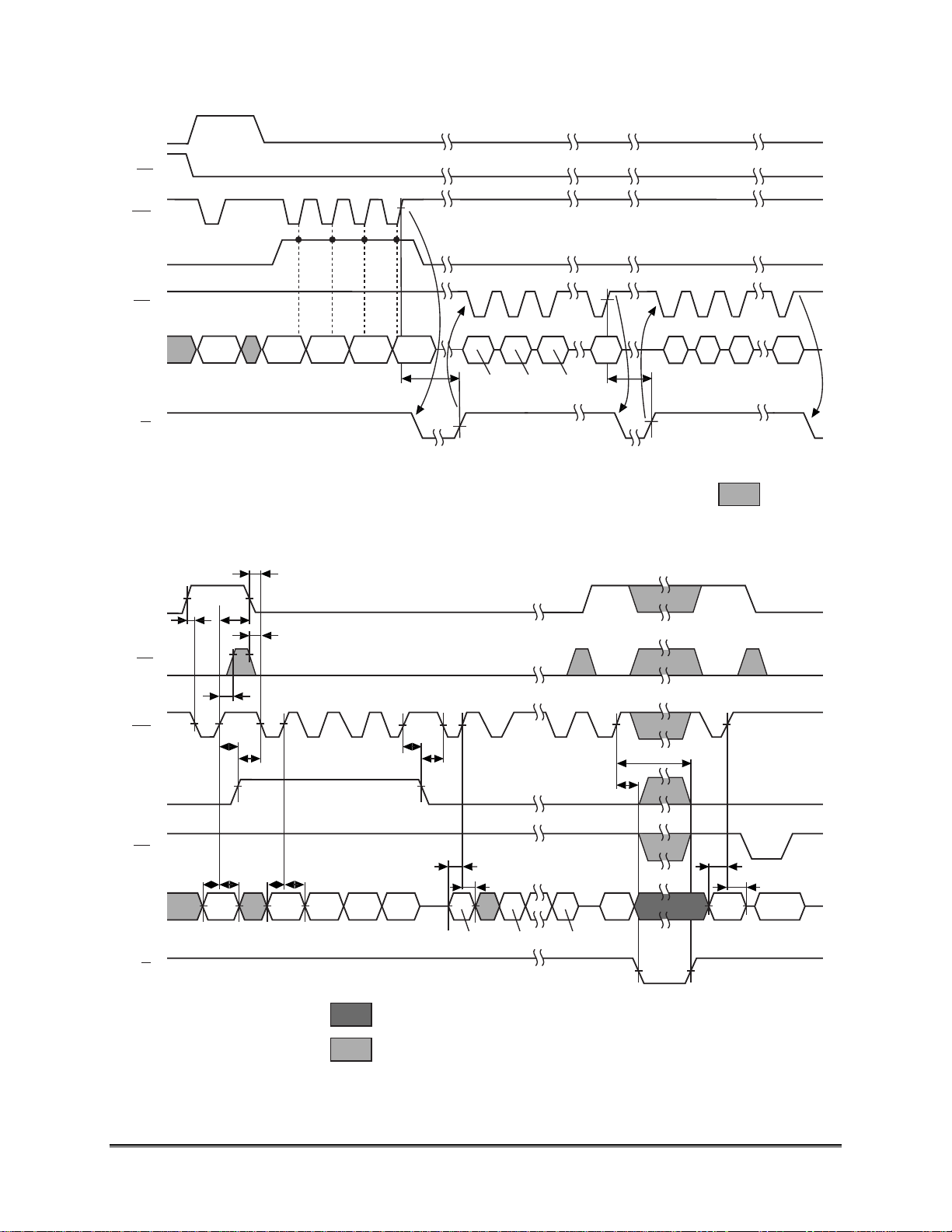

Figure 2-1 Latch Timing Diagram for Command/Address/Data

Figure 2-2 Command Input Cycle Timing Diagram

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

11

Page 12

SmartMedia 128MByte Product Manual

t

CLS

CLE

CE

WE

ALE

t

CS

t

ALS

t

WP

tDSt

t

WC

DH

t

WH

t

WP

tDSt

t

WC

DH

t

WH

t

WP

tDSt

t

WC

DH

t

WH

t

WP

tDSt

DH

t

ALH

I/O1 to

I/O8

A17 to 24A9 to 16A0 to 7

: V

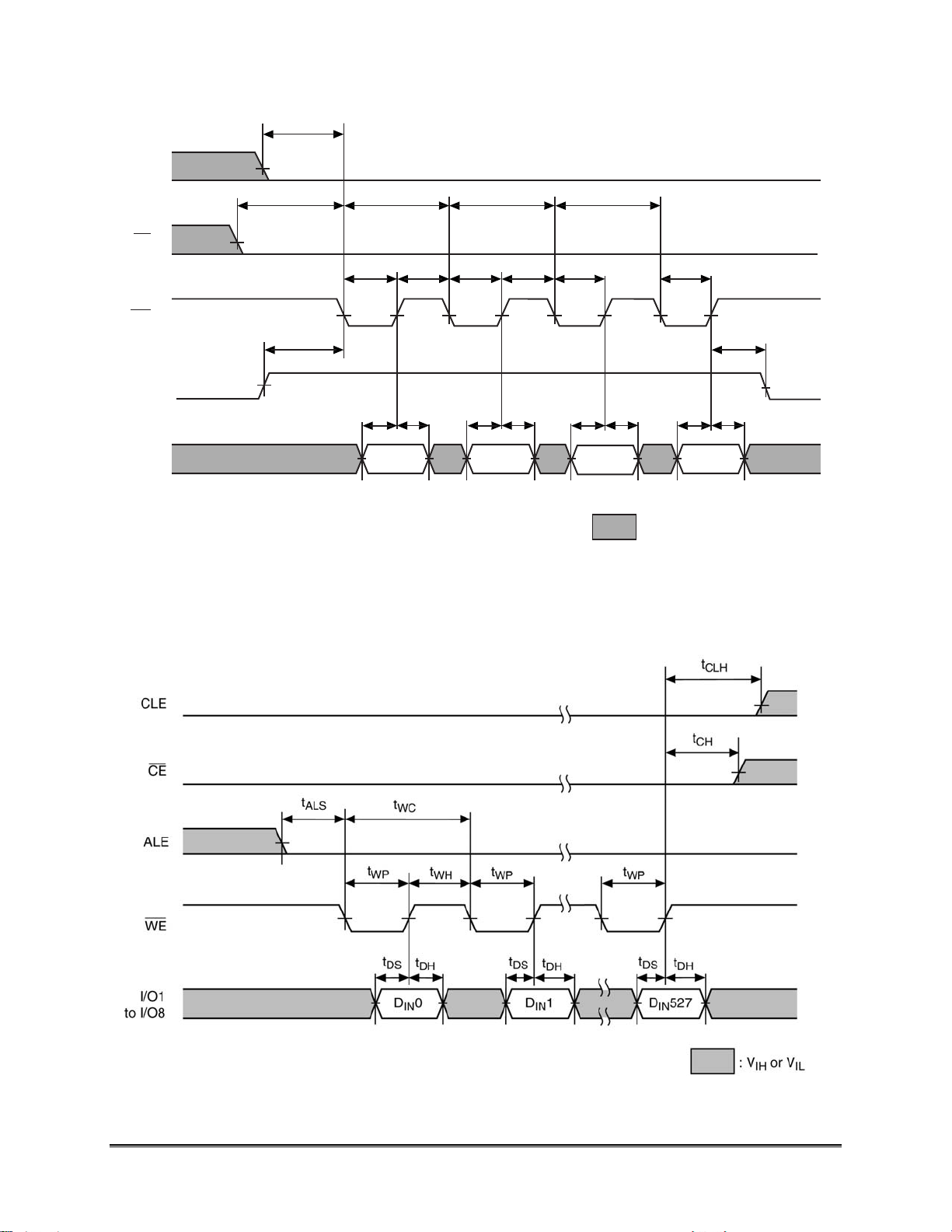

Figure 2-3 Address Input Cycle Timing Diagram

IH

A25 to 26

or V

IL

Figure 2-4 Data Input Cycle Timing Diagram

12

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 13

SmartMedia 128MByte Product Manual

Figure 2-5 Serial Read Cycle Timing Diagram

Figure 2-6 Status Read Cycle Timing Diagram

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

13

Page 14

SmartMedia 128MByte Product Manual

CLE

CE

WE

ALE

RE

I/O1

to I/O8

RY/BY

t

CLStCLH

t

CH

t

WC

t

t

ALS

ALH

A9

to 16

tDHtDStDHt

DS

to 24

DS

tDHt

00H

DS

A0

to 7

Column address

∗∗∗

N

: Read operation using 00H command N:0-255

∗∗∗

t

CS

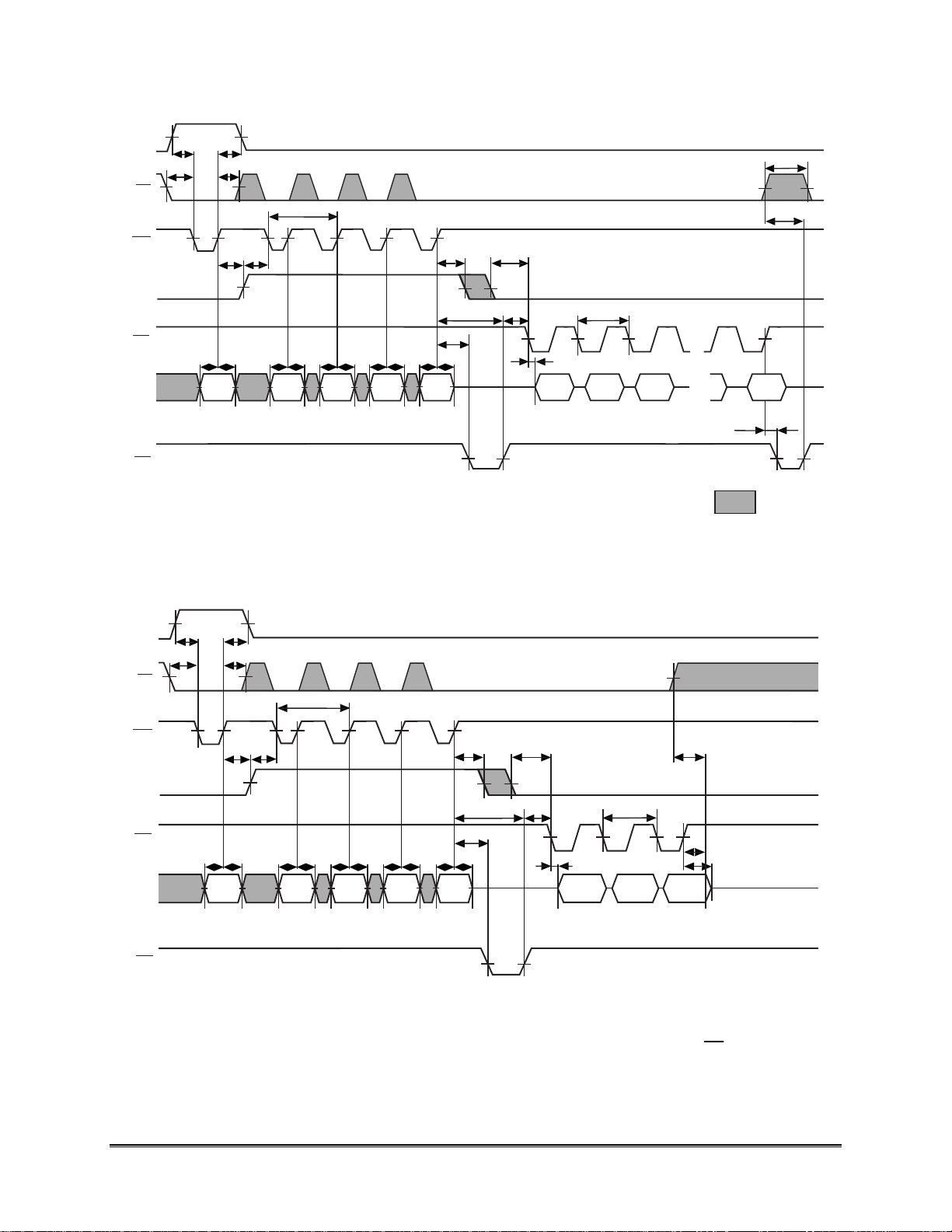

Figure 2-7 Read Cycle (1) Timing Diagram

A17

A25

to 26

t

ALH

t

WB

tDHtDStDHt

t

CEH

t

CRY

t

AR

t

t

RR

R

t

RC

¥¥¥¥

D

OUT

N

D

OUT

N+1

D

N+2

OUT

¥¥¥¥¥

D

OUT

527

t

RB

: V

or V

IH

IL

CLE

CE

WE

ALE

RE

I/O1

to I/O8

RY/BY

t

CLStCLH

t

CS

t

t

ALH

CH

t

ALS

t

WC

t

ALH

t

t

WB

DS

tDHt

00H

tDHt

A0

to 7

N

DS

to 16

∗∗∗

DS

Column address

A9

DS

A17

to 24

tDHt

tDHt

DS

A25

to 26

tDHt

***: Read operation using 00H command N:0-255

Figure 2-8 Read Cycle (1) Timing Diagram: When Interrupted by

t

AR

t

RR

R

t

D

REA

OUT

N

t

RC

D

N+1

OUT

t

CHZ

D

OUT

N+2

t

CE

RHZ

t

OH

14

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 15

SmartMedia 128MByte Product Manual

CLE

CE

WE

ALE

RE

I/O1

to I/O8

RY/BY

t

t

CLH

CLS

t

CS

∗∗∗

: Read operation using 01H command N:0-255

tDSt

01H

t

DH

CH

t

ALH

t

ALS

tDSt

DH

A9 to

A0 to

7

Column address

N

Figure 2-9 Read Cycle (2) Timing Diagram

16

A17 to

24

t

ALH

t

WB

A25 to

26

t

AR2

t

R

t

RR

D

t

RC

OUT

t

REA

D

OUT

D

OUT

256 + Ν 256 + N + 1 527

: V

or V

IH

IL

CLE

CE

WE

ALE

RE

I/O1

to I/O8

RY/BY

t

t

CLH

CLS

t

CS

∗∗∗

: Read operation using 50H command N:0-15

tDSt

50H

t

DH

CH

t

ALH

t

ALS

tDSt

DH

A9 to

A0 to

7

Column address

N

16

A17 to

24

t

ALH

t

WB

A25 to

26

t

AR2

t

R

t

RR

D

t

RC

OUT

t

REA

D

OUT

D

OUT

512 + Ν 512 + N + 1 527

: V

or V

IH

IL

Figure 2-10 Read Cycle (3) Timing Diagram

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

15

Page 16

SmartMedia 128MByte Product Manual

CLE

CE

WE

ALE

RE

A25 to

A17 to

A9 to

I/O1

to I/O8

R/B

00H

A0 to

7

Column

address

N

16

24

Page

address

M

26

N N+1 N+2 527 5270 1 2

t

R

t

R

CLE

WE

ALE

RE

I/O1

to I/O8

CE

01H

Page M

access

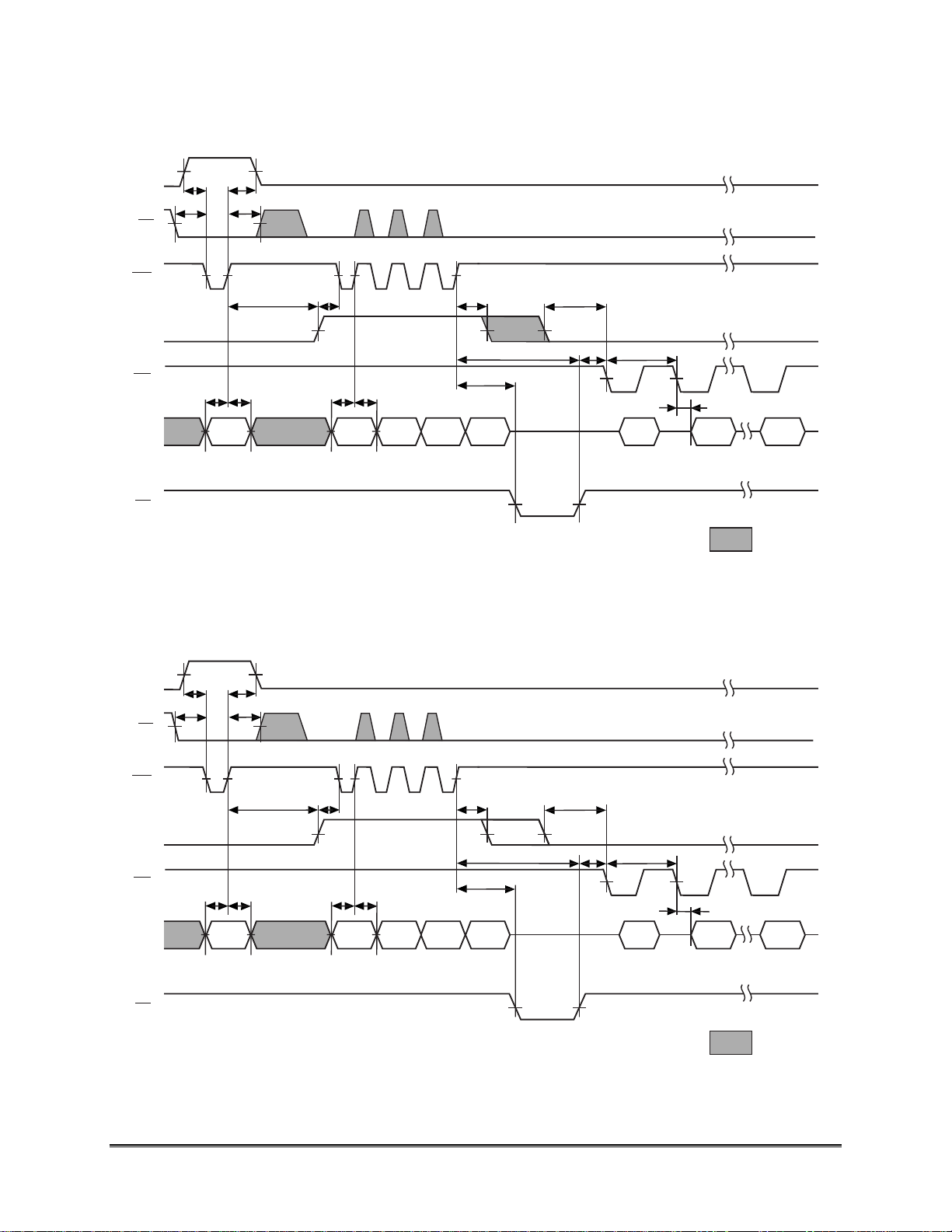

Figure 2-11 Sequential Read (1) Timing Diagram

A25 to

A17 to

A9 to

A0 to

7

Column

address

N

16

Page

address

24

26

256+N256+

t

M

R

N+1

256+

N+2

Page M + 1

access

527 5270 1 2

t

R

: V

or V

IH

IL

R/B

Page M

access

Page M + 1

access

: V

or V

IH

IL

Figure 2-12 Sequential Read (2) Timing Diagram

16

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 17

CLE

WE

ALE

RE

I/O1

to I/O8

R/B

CE

50H

A0 to

7

Column

address

N

A9 to

16

A17 to

24

Page

address

M

A25 to

26

SmartMedia 128MByte Product Manual

527 527

t

R

512+N512+

N+1

512+

N+2

t

R

512 513 514

CLE

WE

ALE

RE

I/O1

to I/O8

CE

t

CLS

tDSt

80H

t

CLS

t

CLH

t

CS

t

CH

t

ALH

t

ALS

DHtDStDH

A0 to

7

Page M

access

Page M + 1

access

Figure 2-13 Sequential Read (3) Timing Diagram

t

ALH

t

Prog

t

WB

10H 70H

A9 to

16

A17 to

24

A25 to

26

t

ALS

t

DS

t

DH

DIN0DIN1

DIN527

: V

or V

IH

IL

t

DS

t

DH

Status

output

R/B

: Do not input data while data is being output.

: V

or V

IH

IL

Figure 2-14 Auto-Program Operation Timing Diagram

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

17

Page 18

SmartMedia 128MByte Product Manual

CLE

CE

WE

ALE

RE

I/O1

to 8

R/B

t

CLS

t

CS

t

DS

60H

Auto Block

Erase Setup

command

t

CLH

t

CLS

t

ALS

t

DH

A17 to

A9 to

A16

A24

A25 to

A26

t

ALH

t

WB

Erase Start

command

t

BERASE

Busy

70HD0H

Status Read

command

Status

output

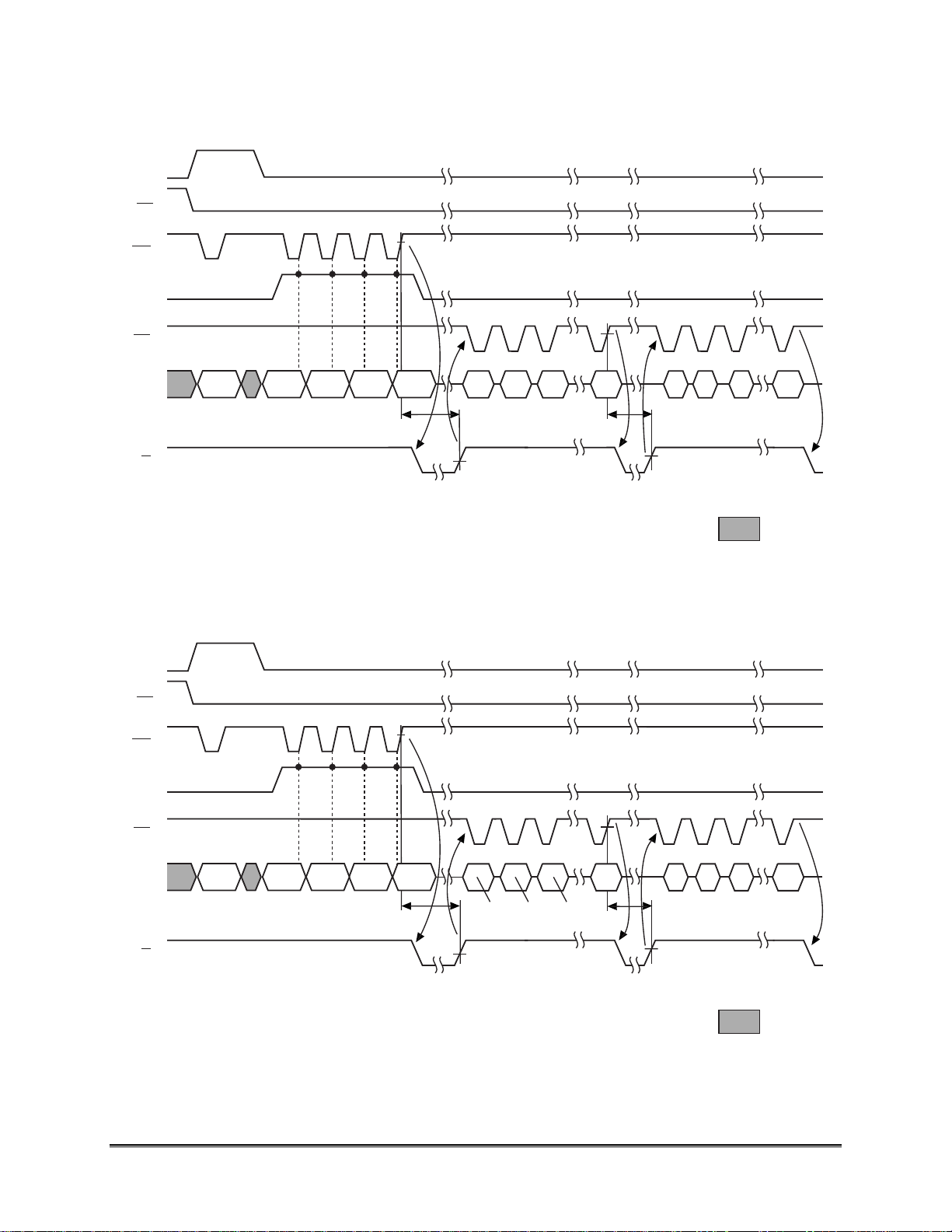

Figure 2-15 Auto Block Erase Timing Diagram

18

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 19

t

CLS

SmartMedia 128MByte Product Manual

CLE

WE

ALE

RE

I/O1

to I/O8

R/B

CE

t

t

CLH

CLS

t

CS

t

CS

t

ALH

t

CH

t

ALH

t

tDSt

DHtDStDH

80H

t

ALS

A0 to

A7

A17 to

A9 to

A24

A16

Max 3 Times Repeat Last District Input

A25 to

A26

: V

IH

t

ALS

or V

t

DS

t

DH

DIN0DIN1

IL

t

WB

11H

DIN527

Auto Program (Dummy)

1 2

DBSY

80H

A0 to

A7

31 Times Repeat

(Page 0 to 30 Programming in Multi Block)

Max 4 Blocks Programming

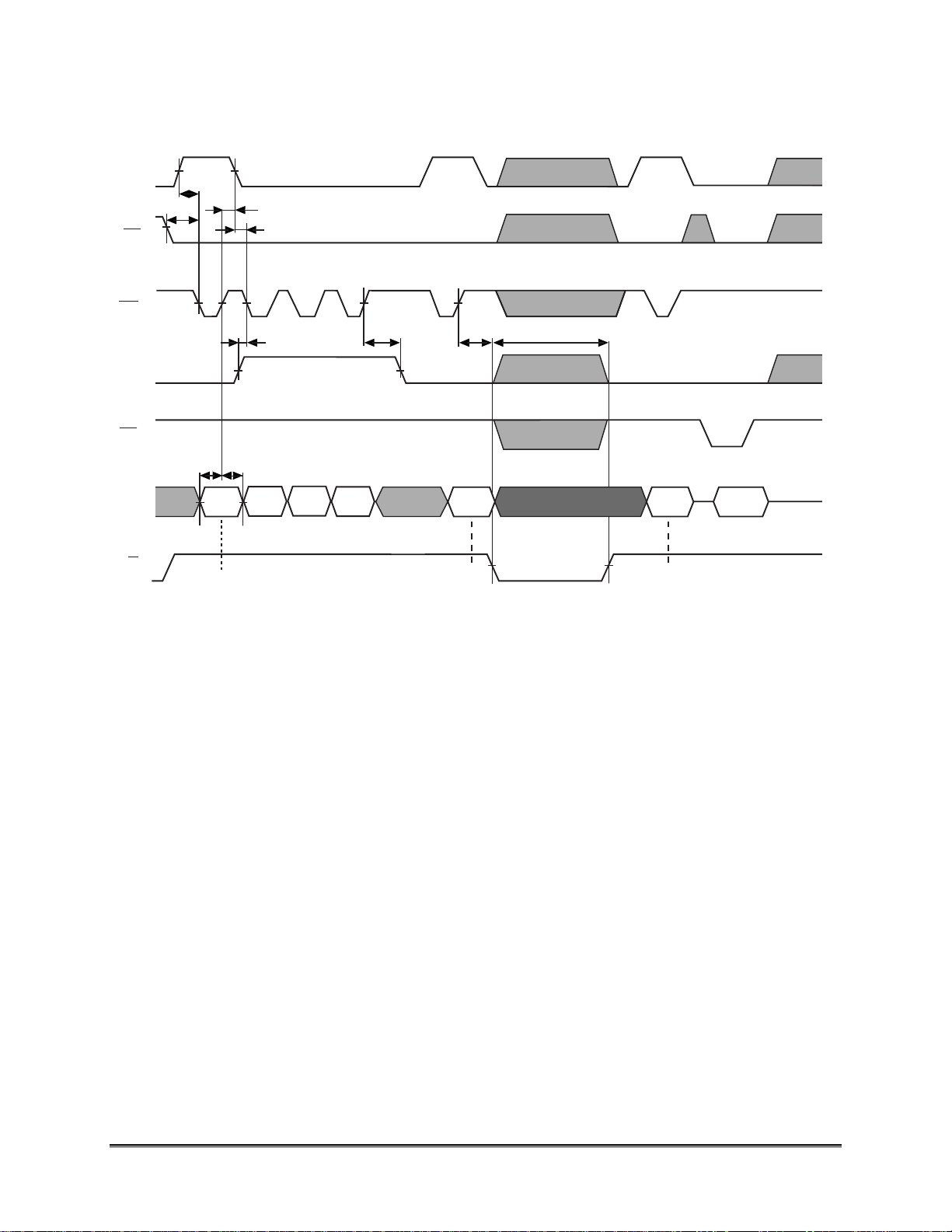

Figure 2-16 Multi Block Programming Timing

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

19

Page 20

SmartMedia 128MByte Product Manual

t

CLS

CLE

WE

ALE

RE

I/O1

to I/O8

R/B

Repeat

CE

Max 3

Times

t

CLS

tDSt

80H

t

CLH

t

CS

t

CH

t

ALH

DH

t

ALS

: V

A0 to

7

IH

or V

A9 to

16

IL

A17 to

24

t

A25 to

26

ALH

: Do not input data while data is being output.

Last District Input

t

ALS

t

DS

t

DH

DIN0DIN1

t

MBPBSY

15H 80H

DIN527

Auto Program

(multi block program)

A0 to

A7

2 3

31 Times Repeat

(Page 0 to 30 Programming in Multi Block)

Max 4 Blocks Programming

Figure 2-16 Multi Block Programming Timing (continued)

Max 3

Times

Repeat

20

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 21

t

CLS

SmartMedia 128MByte Product Manual

CLE

WE

ALE

RE

I/O1

to I/O8

R/B

CE

t

t

CLH

CLS

t

CS

t

CS

t

t

ALH

tDSt

DHtDStDH

80H

CH

t

ALS

A0 to

7

A9 to

16

A17 to

24

t

A25 to

26

: V

ALH

IH

t

ALS

or V

t

DS

t

DH

DIN0DIN1

IL

DIN527

11H

t

WB

t

DBSY

80H

A0 to

A7

Auto Program (Dummy)

Max 3 Times Repeat

43

Last District Input

(Last Pages Programming in Multi Block)

Max 4 Blocks Programming

Figure 2-16 Multi Block Programming Timing (continued)

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

21

Page 22

SmartMedia 128MByte Product Manual

t

CLS

CLE

t

CLS

t

CLH

t

CS

CE

t

CH

WE

t

ALH

t

ALS

ALE

RE

tDSt

DHtDStDH

I/O1

to I/O8

80H

A0 to

7

R/B

: V

Max

: Do not input data while data is being output.

3 Times

Repeat

(Last Pages Programming in Multi Block)

A9 to

16

or V

IH

IL

t

ALH

A25 to

A17 to

26

24

Last District Input

t

ALS

t

DS

t

DH

DIN0DIN1

t

Prog

t

WB

10H 71H

DIN527

Auto Program (True)

t

DS

t

DH

Status

output

54

Max 4 Blocks Programming Status Read

Figure 2-16 Multi Block Programming Timing (continued)

22

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 23

SmartMedia 128MByte Product Manual

CLE

CE

WE

ALE

RE

I/O1

to I/O8

R/B

t

CLS

t

CS

tDSt

60H

Auto Block

Erase Setup

command

DH

t

CLH

t

CLS

t

ALS

A9 to

A16

A17 to

A24

t

ALH

A25 to

A26

t

WB

Erase Start

command

t

BERASE

Busy

71HD0H

Status Read

command

Status

output

Max 4 Times Repeat

(1 to 4 Times Repeat)

: V

or V

IH

IL

: Do not input data while data is being output.

Figure 2-17 Multi Block Erase Timing Diagram

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

23

Page 24

SmartMedia 128MByte Product Manual

CLE

CE

WE

ALE

RE

I/O1

to I/O8

t

CLS

t

CS

tDSt

t

CH

t

DH

ALH

t

CLS

t

ALS

t

CS

t

CH

t

ALH

t

90H 00 98H

Address

input

t

CR

AR1

t

REAID

Maker

Code

t

REAID

t

REAID

79H A5H C0H

Device

Code

t

REAID

CLE

CE

WE

ALE

RE

I/O1

to I/O8

Figure 2-18 ID Read (1) Operation Timing Diagram

t

CLS

t

CS

t

CH

t

tDSt

DH

91H 00 21H

ALH

t

CLS

t

ALS

t

CS

t

CH

t

ALH

t

t

CR

AR1

t

REAID

: V

or V

IH

t

REAID

t

REAID

49H 3AH 00H

IL

t

REAID

Address

input

Character

code

Organization

code

Size

code

Figure 2-19 ID Read (2) Operation Timing Diagram

24

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 25

SmartMedia 128MByte Product Manual

Table 2-1 Extended ID Information

Device Characteristics Code Organization Code Size Code

(automatically changed)

IO1 IO0 IO3 IO2 IO1 IO0 IO7 IO6 IO5

Single chip use

2-chip module

4-chip module

8-chip module

0

0

1

1

0

1

0

1

64 MB

128 MB

256 MB

512 MB

1 GB

0

0

1

1

1

1

1

0

0

0

1

1

0

0

1

0

1

0

1

0

16KB

32KB

64KB

128KB

0

0

0

1

0

1

1

0

1

0

1

0

IO3,2 = 00 in 2LC mode The number of bits per cell and the IO2,1,0 = 010

number of chips in the multi-chip (meaning 512B-page size)

= 01 in 4LC mode module automatically change the

organization code. IO3,4 = 11

(meaning extended page

IO6,5,4 = 010 size = 16B)

This device includes x4 multi-block IO4,5 = 00

mode.

IO7 = 0 IO7,6 = 01 (meaning x8-data-bus

This device doesn’t have secondary width)

data cache.

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

25

Page 26

SmartMedia 128MByte Product Manual

3.0 Pin Functions

The SmartMedia Card is a serial access memory device which uses time-sharing input of address

information. The device pinouts are configured as shown in Figure 3-1.

123456

CLE ALE WE WP I/O2I/O1 I/O3 I/O4V

ss

22 21 20 19 18 17 16 15 14 13 12

CE RE

V

CC

R/B

GND LVD I/O8 I/O7 I/O6 I/O5 V

3.1 Pin Descriptions

7891011

VssV

ss

I/O1 to 8

GND

CC

CE

WE

RE

CLE

ALE

WP

R/B

LVD

V

CC

V

SS

I/O Port

Chip Enable

Write Enable

Read Enable

Command Latch Enable

Address Latch Enable

Write Protect

Ready/Busy

Ground Input

Low Voltage Detect

Power Supply

Ground

Figure 3-1 SmartMedia Card Pinout

PIN NAMES

Command Latch Enable: CLE

The CLE input signal is used to control loading of the operation mode command into the internal

command register. The command is latched into the command register from the I/O port on the rising

edge of the

WE signal while CLE is High.

Address Latch Enable: ALE

The ALE signal is used to control loading of either address information or input data into the internal

address/data register. Address information is latched on the rising edge of

WE if ALE is High. If ALE is

Low, input data is latched.

Chip Enable:

The device goes into a low-power Standby Mode when

signal is ignored when the device is in the Busy state (

operation, and will not enter Standby Mode even if the

CE

CE goes High during a Read operation. The CE

R/B= L), such as during a Program or Erase

CE input goes High. The CE signal must stay Low

during the Read Mode Busy state to ensure that memory array data is correctly transferred to the data

register.

Write Enable:

The

WE signal is used to control the acquisition of data from the I/O port.

26

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

WE

Page 27

SmartMedia 128MByte Product Manual

Read Enable:

The

RE signal controls serial data output. Data output will be valid when

RE

RE goes low after t

REA

. The

internal column address counter is also incremented (Address = Address + l) on this falling edge.

I/O Port: I/OI to 8

The I/O1 to 8 pins are used as ports for transferring address, command and input/output data to and

from the device.

Write Protect:

The

WP signal is used to protect the device from accidental programming or erasing. The internal voltage

regulator is reset when

WP

WP is Low. This signal is usually used for protecting the data during the

power-on/off sequence when input signals are invalid. The signal assertion during the program or erase

operation causes the operation to cancel, not interrupt, even if the card is busy.

Ready/Busy: R/B

The R/B output signal is used to indicate the operating condition of the device. The R/B signal is in Busy

R/B = L) during the Program, Erase and Read operations and will return to Ready state (R/B = H)

state (

after completion of the operation. The output buffer for this signal is an open drain.

Low Voltage Detect: LVD (SmartMedia Card only)

The LVD signal is used to detect the power supply voltage level.

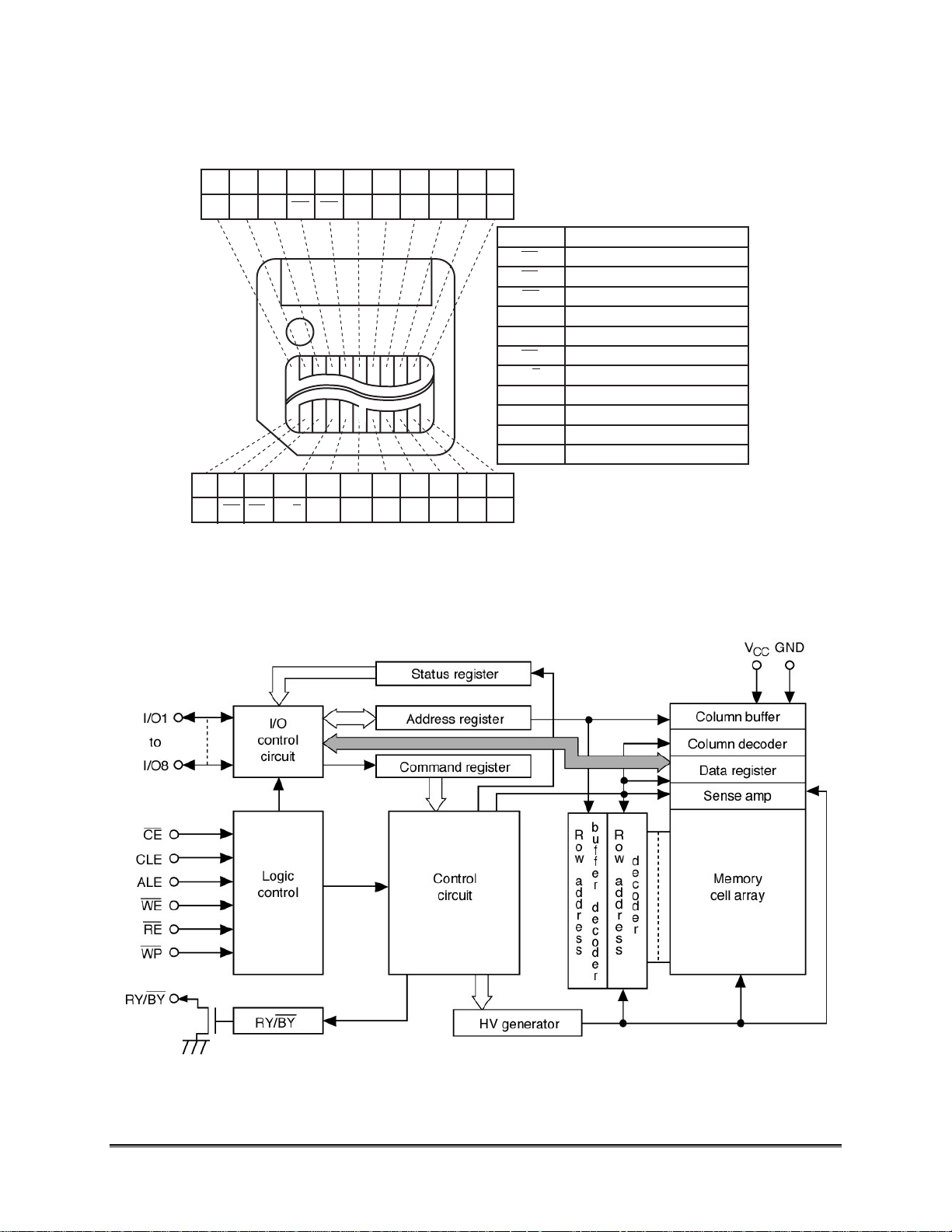

3.2 Schematic Cell Layout and Address Assignment

The Program operation works on page units while the Erase operation works on block units.

512 16

262144

pages

= 8192 blocks

Table 3-1 Addressing

I/O8 I/O7 I/O6 I/O5 I/O4 I/O3 I/O2 I/O1

First Cycle

Second Cycle

Third Cycle

Fourth Cycle

I/O1

I/O8

A page consists of 528 bytes of which 512 bytes are

used for main memory storage and 16 bytes are for

32 pages

= 1 block

8I/O

528

redundancy or for other uses.

1 page = 528 bytes

1 block = 528 bytes X 32 pages = (16K + 512) bytes

Capacity = 528 bytes X 32 pages X 8192 blocks

An address is read in via the I/O port over four

consecutive clock cycles, as shown in the following table.

Figure 3-2 Schematic Cell Layout

A7 A6 A5 A4 A3 A2 A1 A0

A16 A15 A14 A13 A12 A11 A10 A9

A24 A23 A22 A21 A20 A19 A18 A17

*L *L *L *L *L *L

A26

A25

A0 to A7: Column address

A9 to A26: Page address

(A14 to A26: Block address

A9 to A13: NAND address in block)

* : A8 is automatically set to Low or High by an 00H command or an 01H command.

* : l/O2 to l/O8 must be set to Low in the fourth cycle.

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

27

Page 28

SmartMedia 128MByte Product Manual

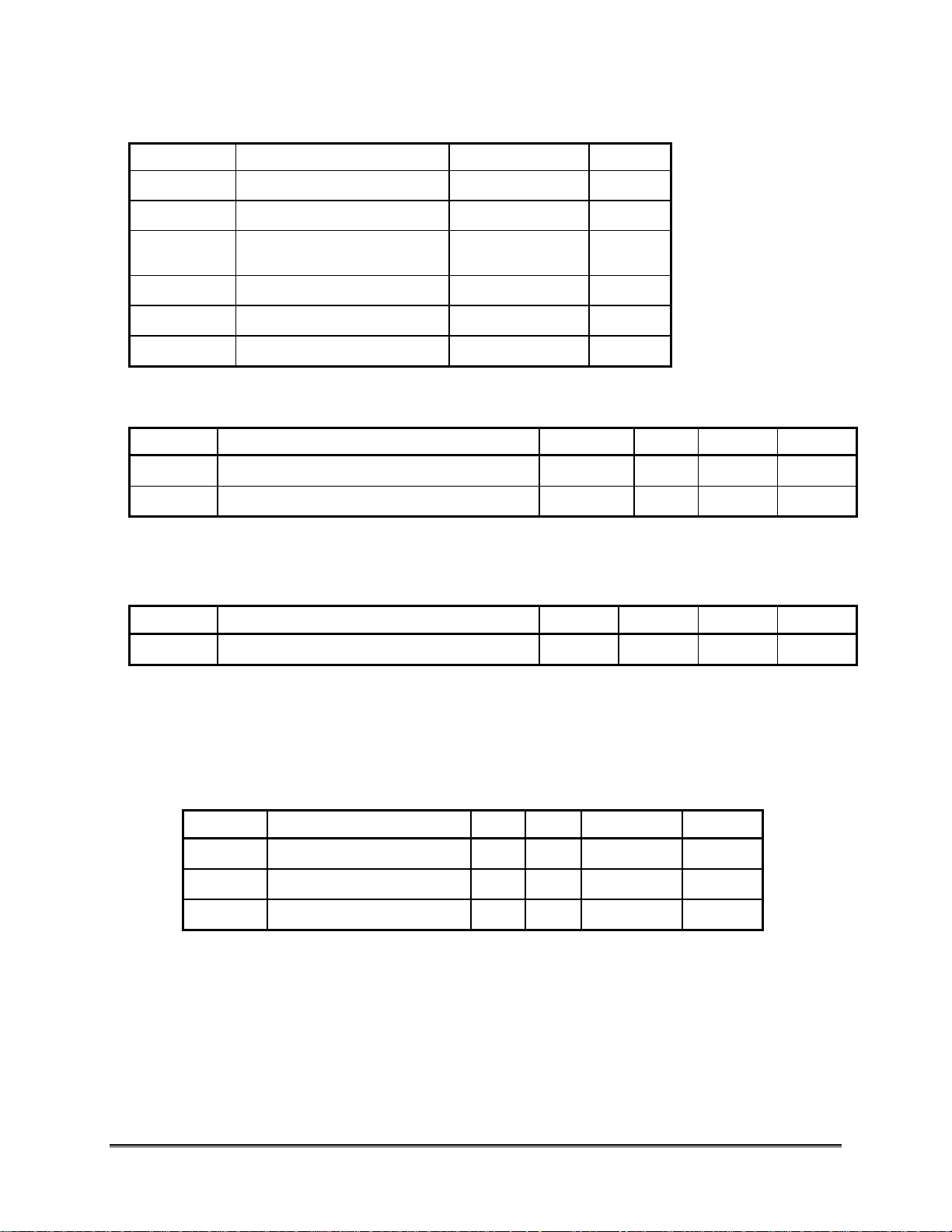

3.3 Operation Mode: Logic and Command Tables

The operation modes such as Program, Erase, Read and Reset are controlled by the different command

operations shown in Table 3-4. Address input, command input and data input/output are controlled by

the CLE, ALE,

CE , WE , RE and WP signals, as shown in Table 3-3.

Table 3-2 Logic Table

CLE ALE

Command Input

Data Input

Address input

Serial Data Output

During Programming (Busy)

During Erasing (Busy)

Program, Erase Inhibit

H: VIH, L: VIL, *: VIH or VIL

H L L H

L L L H

L H L H

L L L H

* * * * *

* * * * *

* * * * *

CE

WE RE WP

Table 3-3 Command Table (HEX)

First Cycle Second Cycle Acceptable While Busy

Serial Data Input

Read Mode (1)

Read Mode (2)

Read Mode (3)

Reset

80

00

01

50

FF

√

*

*

*

*

H

H

L

Auto Program (True)

Auto Program (Dummy)

Auto Program (Cache)

Auto Block Erase

Status Read (1)

Status Read (2)

ID Read (1)

ID Read (2)

10

11

15

60 D0

70

71

90

91

√

√

28

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 29

I/O8765432I/O1

Table 3-4 Read Mode Operation States

SmartMedia 128MByte Product Manual

CLE ALE

Output Select

Output Deselect

Standby

H: VIH, L: VIL, *: VIH or V

CE

L L L H L Output Active

L L L H H High Impedance Active

L L H H

IL

WE RE

*

I/O1 to I/O8 Power

High Impedance Standby

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

29

Page 30

SmartMedia 128MByte Product Manual

4.0 Device Operation

4.1 Read Mode (1)

Read mode (1) is set when an 00H command is issued to the Command register. Refer to Figure 4-1 below

for timing details and the block diagram.

Figure 4-1 Read Mode (1) Operation

30

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 31

4.2 Read Mode (2)

SmartMedia 128MByte Product Manual

Figure 4-2 Read Mode (2) Operation

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

31

Page 32

SmartMedia 128MByte Product Manual

4.3 Read Mode (3)

Read mode (3) has the same timing as Read modes (1) and (2) but is used to access information in the extra

16-byte redundancy area of the page. The start pointer is therefore set to a value between byte 512 and byte

527.

Figure 4-3 Read Mode (3) Operation

4.4 Sequential Read (1) (2) (3)

This mode allows the sequential reading of pages without additional address input.

Figure 4-4 Sequential Read (1) (2) (3) Operation

32

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 33

SmartMedia 128MByte Product Manual

Sequential Read modes (1) and (2) output the contents of addresses 0 to 527 as shown above, while

Sequential Read mode (3) outputs the contents of the redundant address locations only. When the page

address reaches the next block address, read command (00H/01H/50H) and address input are needed.

4.5 Status Read

The SmartMedia Card has two Status Read commands. One is Status Read (1) command 70H and the

other is Status Read (2) command 71H.

This device automatically implements the execution and verification of the Program and Erase operations.

The Status Read function is used to monitor the Ready/Busy status of the device, determine the result

(pass /fail) of a Program or Erase operation, and determine whether the device is in Protect mode. The

device status is output via the I/O port on the

RE clock after a 70H or 71H command input.

The resulting information of the Status Read (1) command 70H is outlined in the table below and the

resulting information of Status Read (2) command 71H is outlined in the explanation for Multi Block

Program and Multi Block Erase toward the end of this document.

Table 4-1 Status Output Table for Status Read (1) Command 70H

Status Output

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

I/O8

Note: In the case of Multi Block Write/Erase, I/O1 to I/O5 have an additional definition.

Pass/Fail Pass: 0 Fail: 1

Not Used 0

Not Used 0

Not Used 0

Not Used 0

Not Used 0

Ready/Busy Ready: 1 Busy: 0

Write Protect Protect: 0 Not Protected: 1

The Pass/Fail status on I/O1 is only

valid when the device is in the Ready

state.

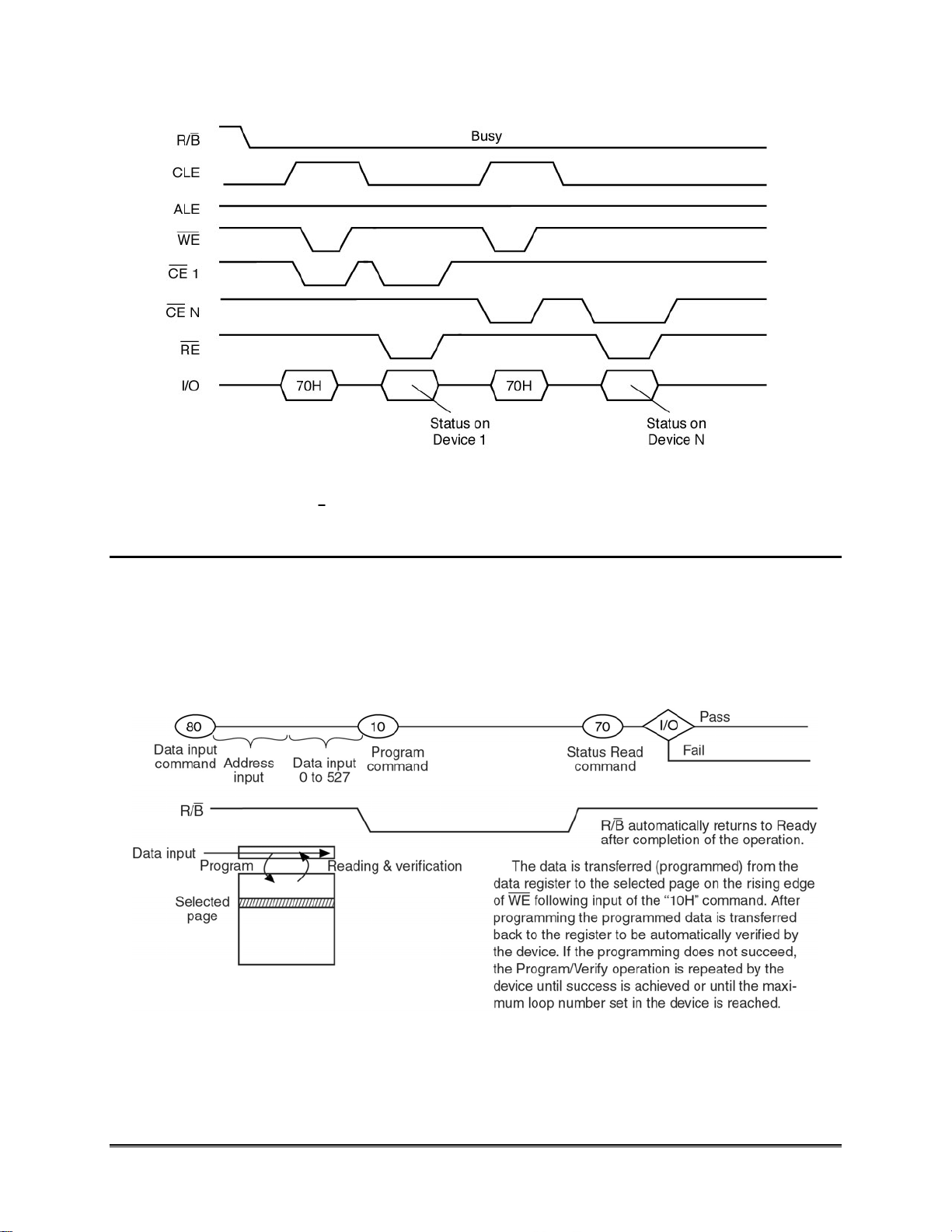

An application example with multiple devices is shown in Figure 4-5.

Figure 4-5 Application Example with Multiple Devices

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

33

Page 34

SmartMedia 128MByte Product Manual

Figure 4-6 Status Read Timing Application Example

System Design Note: If the

R/B pin signals from multiple devices are wired together as shown in Figure

4-5, the Status Read function can be used to determine the status of each individual device.

4.6 Auto Page Program

The device carries out an Automatic Page Program operation when it receives a 10H Program command

after the address and data have been input. The sequence of command, address and data input is shown

below.

Figure 4-7 Auto Page Program Operation

34

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 35

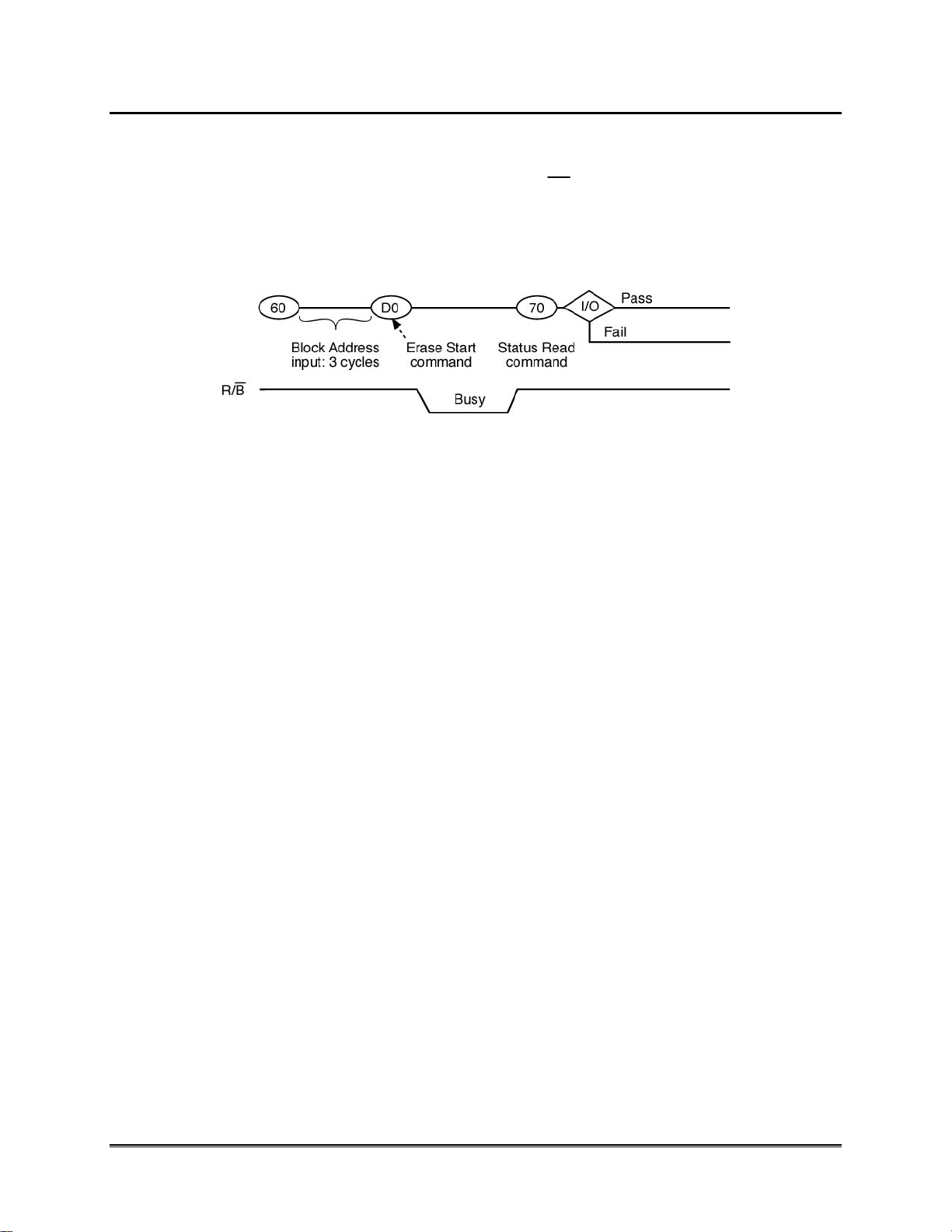

4.7 Auto Block Erase

SmartMedia 128MByte Product Manual

The Auto Block Erase operation starts on the rising edge of

WE after the Erase Start command DOH

which follows the Erase Setup command 60H. This two-cycle process for Erase operations acts as an extra

layer of protection from accidental erasure of data due to external noise. The device automatically executes

the Erase and Verify operations.

Figure 4-8 Auto Block Erase Operation

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

35

Page 36

SmartMedia 128MByte Product Manual

4.8 Multi Block Program

The device carries out a Multi Block Program operation when it receives a 15H or 10H Program command

after some sets of the address and data have been input.

In the interval of the Multi District address and the data input (512+16Byte), 11H Dummy Program

command is used when it still continues the data input into another District. The sequence of command,

address and data input is shown below.

Figure 4-9 Multi Block Program Operation

After 15H Cache Program command, physical programming starts as follows.

Starting the upper operation from the first page of the selected erase blocks, and then repeating the

operation for a total of 31 times while incrementing the page address in the blocks, and then inputting the

last page data of the blocks, the 10H command executes final programming.

36

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 37

SmartMedia 128MByte Product Manual

In this full sequence, the command sequence is below.

Figure 4-10 Command Sequence

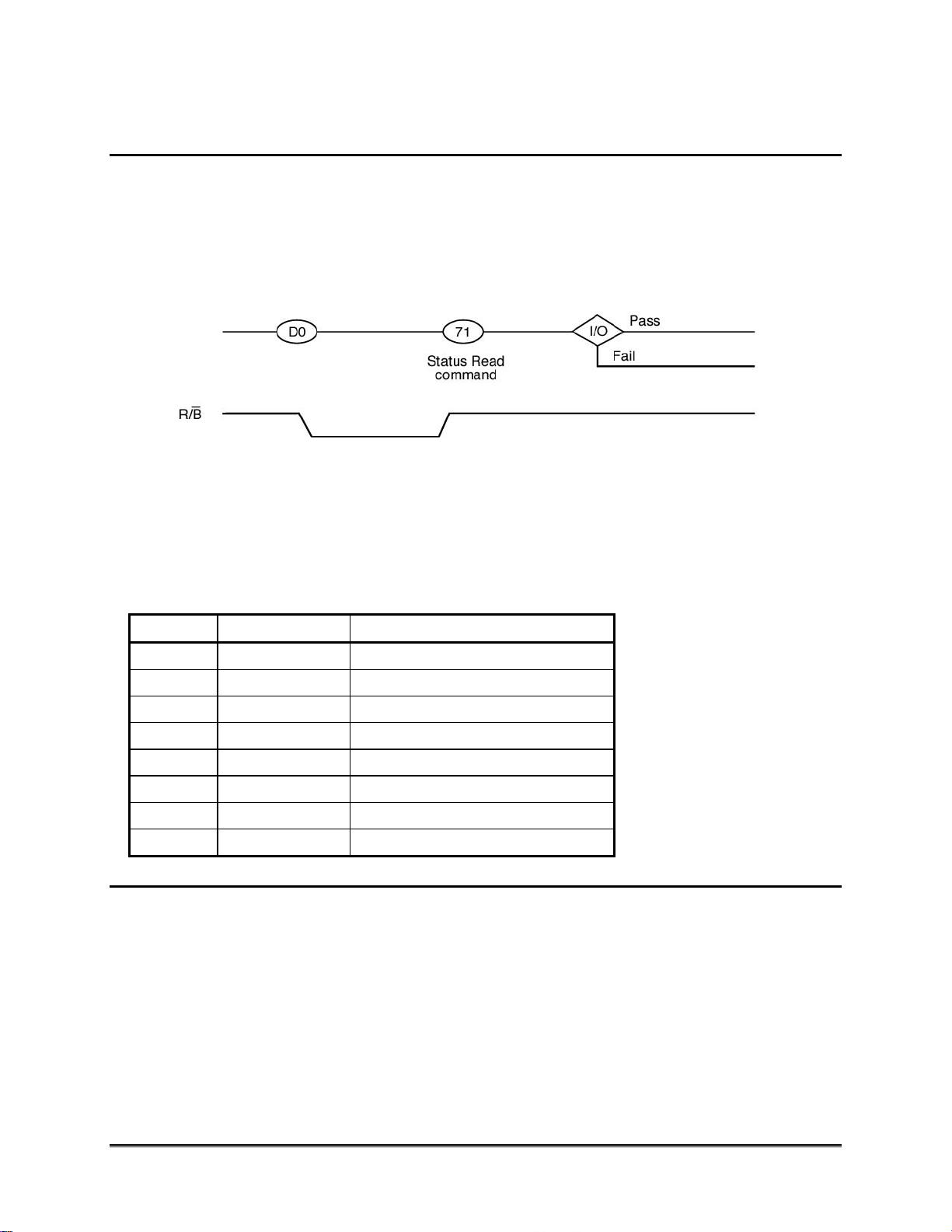

After the 10H command, the total results of the upper operation is shown through the Status Read

command.

Figure 4-11 Status Read (2) Command

The Status description is below.

Table 4-2 Status Description Table

Status Output

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

I/O8

Total Pass/Fail Pass: 0 Fail: 1

District 0 Pass/Fail Pass: 0 Fail: 1

District 1 Pass/Fail Pass: 0 Fail: 1

District 2 Pass/Fail Pass: 0 Fail: 1

District 3 Pass/Fail Pass: 0 Fail: 1

Not Used do not care

Ready/Busy Ready: 1 Busy: 0

Write Protect Protect: 0 Not Protect: 1

4.8.1 Internal Addressing in Relation with the Districts

I/O1 describes total Pass/ Fail

condition. If at least one fail occurred

in 32 times X 4 (512+16Byte) page

write operation, it shows “Fail”

condition,

I/O2 describes total Pass/ Fail

condition. If at least one fail occurred

in 32 times X 1 (512+16Byte) page

write operation in District 0 area, it

shows “Fail” condition,

I/O3, I/O4 and I/O5 are as same

manner as I/O2.

To use the Multi Block Program operation, the internal addressing should be such that at most one block is

selected within each district.

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

37

Page 38

SmartMedia 128MByte Product Manual

The device consists of two chips, each of which has four Districts. Each District consists from 1024 erase

blocks. The allocation rule is follows.

Chip0, District0 : Block0, Block4, Block8, Block12, …..,Block4092

Chip0, District1 : Block1, Block5, Block9, Block13, …..,Block4093

Chip0, District2 : Block2, Block6, Block10, Block14, …..,Block4094

Chip0, District3 : Block3, Block7, Block11, Block15, …..,Block4095

Chip1, District0 : Block4096, Block4100, Block4104, Block4108, …..,Block8188

Chip1, District1 : Block4097, Block4101, Block4105, Block4109, …..,Block8189

Chip1, District2 : Block4098, Block4102, Block4106, Block4110, …..,Block8190

Chip1, District3 : Block4099, Block4103, Block4107, Block4111, …..,Block8191

4.8.2 Address Input Restriction for the Multi Block Program Operation

In selecting the blocks for the Multi Block Program operation, the conditions below apply.

• Restriction

- Maximum one block should be selected from each District.

- The data input operation should be started from the same number page of the selected block

and the page number in the blocks should be the same number at programming time.

• Acceptance

- There is no order limitation of the District for address input.

- Any number of the District can be select for programming.

- For example, the following operation is acceptable.

- (80) [District2] (11) (80) [District0] (11) (80) [District1] (15)

No mutual address relation between the selected blocks from each District is required.

4.8.3 Operating Restriction During the Multi Block Program Operation

• Restriction—Starting from the first page of data input, until the device issues a 10H command, any

other command out of defined sequence can not be issued except Status Read and Reset

commands.

• Acceptance—The data input operation can be terminated with the 10H command instead of 15H

command in the middle of the page number in the block. In this case the Status represents the

reflected value accumulated from first page programming of this sequence and up to the last page

programming terminated by 10H command.

4.9 Status Read Operation

Until the Ready condition after the programming is terminated by a 10H command, the effective bit in the

Status data is limited to the Ready/Busy bit. In other words, Pass/Fail condition can be checked only in

the Ready condition after a 10H command.

38

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 39

SmartMedia 128MByte Product Manual

4.10 Multi District Block Erase

The device carries out a Multi District Block Erase operation when it receives a D0H command after some

sets of the address have been input. After the D0H command, the total results of the Erase operation are

shown through the Status Read (2) command 71H.

Figure 4-12 Status Read (2) Command

The Status description is below.

Table 4-3 Multi District Block Erase Status Description

Status Output

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

I/O8

Total Pass/Fail Pass: 0 Fail: 1

District 0 Pass/Fail Pass: 0 Fail: 1

District 1 Pass/Fail Pass: 0 Fail: 1

District 2 Pass/Fail Pass: 0 Fail: 1

District 3 Pass/Fail Pass: 0 Fail: 1

Not Used Do Not Care

Ready/Busy Ready: 1 Busy: 0

Write Protect Protect: 0 Not Protect: 1

I/O1 describes total Pass/ Fail

condition. If at least one fail occurred

in Max4 Blocks erase operation, it

shows “Fail” condition.

I/O2 describes Pass/ Fail condition. If

fail occurred in District 0 area, it

shows “Fail” condition,

I/O3, I/O4 and I/O5 are the same as

I/O2.

4.10.1 Internal Addressing in Relation with the Districts

To use the Multi Block Erase operation, the internal addressing should be such that at most one block is

selected within each district.

The device consists of two chips, each of which has four Districts.

Each District consists of 1024 erase blocks.

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

39

Page 40

SmartMedia 128MByte Product Manual

The allocation rule is below.

Chip0, District0 : Block0, Block4, Block8, Block12, …..,Block4092

Chip0, District1 : Block1, Block5, Block9, Block13, …..,Block4093

Chip0, District2 : Block2, Block6, Block10, Block14, …..,Block4094

Chip0, District3 : Block3, Block7, Block11, Block15, …..,Block4095

Chip1, District0 : Block4096, Block4100, Block4104, Block4108, …..,Block8188

Chip1, District1 : Block4097, Block4101, Block4105, Block4109, …..,Block8189

Chip1, District2 : Block4098, Block4102, Block4106, Block4110, …..,Block8190

Chip1, District3 : Block4099, Block4103, Block4107, Block4111, …..,Block8191

4.10.2 Address Input Restriction for the Multi District Block Erase Operation

In selecting the blocks for the Multi District Block Erase operation, the conditions below apply.

• Restriction—Maximum one block should be selected from each District.

• Acceptance—There is no order limitation of the District for the address input. Any number of the

Districts can be select for the erase operation. For example, the following operation is in

acceptance: (60) [District2] (60) [District0] (60) [District1] (D0).

No mutual address relation between the selected blocks from each District is required.

4.11 Reset

The Reset mode stops all operations. For example, in the case of a Program or Erase operation the

internally generated voltage is discharged to 0 volts and the device enters the Wait state. The address and

data registers are set as follows after a Reset:

• Address Register: All “0”

• Data Register: All “1”

• Operation Mode: Wait state

The response to an FFH Reset command input during the various device operations is as follows:

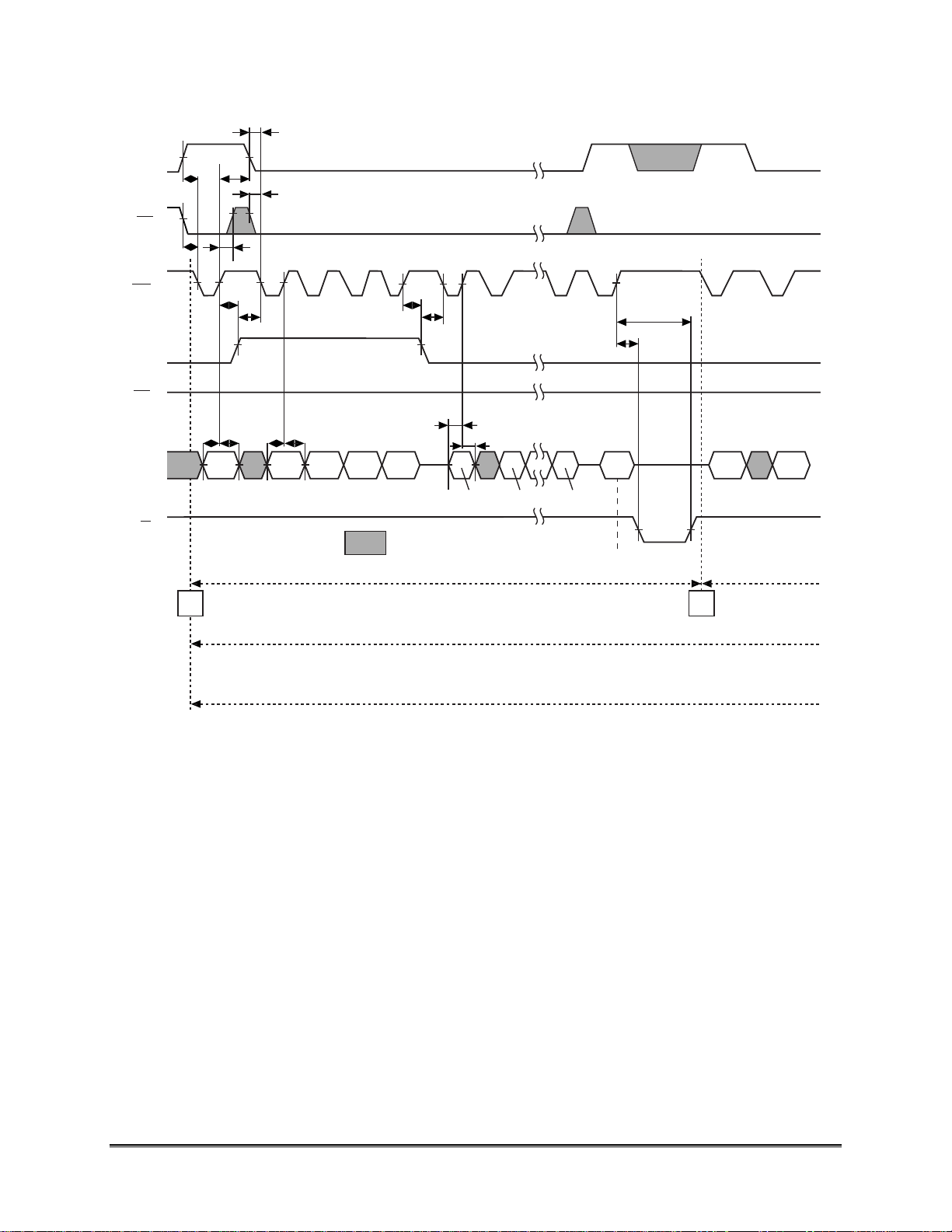

Figure 4-13 When a Reset Command (FFH) is Input During Programming

40

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 41

SmartMedia 128MByte Product Manual

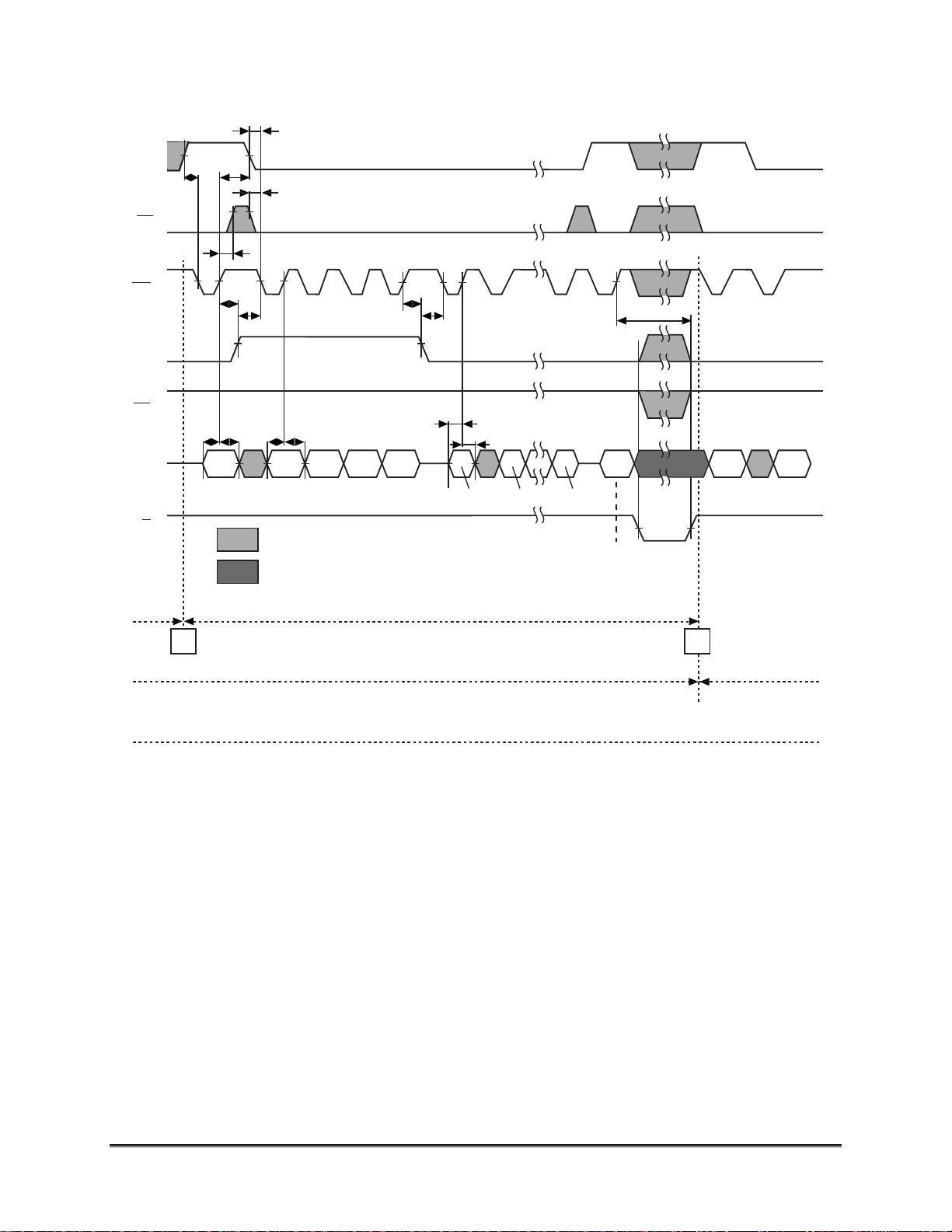

Figure 4-14 When a Reset Command (FFH) is Input During Erasing

Figure 4-15 When a Reset Command (FFH) is Input During Read Operation

Figure 4-16 When a Status Read Command (70H) is Input After a Reset

Figure 4-17 When Two or More Reset Commands are Input in Succession

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

41

Page 42

SmartMedia 128MByte Product Manual

4.12 ID Read

There are ID codes which identify the device type and the manufacturer. The ID codes can be read under

the following timing conditions:

CLE

t

t

AR1

CR

CE

WE

ALE

RE

I/O

For the specifications of the access times t

90H

ID Read command

Address

Table 4-4 Code Table

I/O8 I/O7 I/O6 I/O5 I/O4 I/O3 I/O2 I/O1 Hex Data

Maker Code

Device Code

1 0 0 1 1 0 0 0 98H

0 1 1 1 1 0 0 1 79H

t

REAID

00 98H 79H

00

REAID

, tCR and t

Maker

code

refer to the AC Characteristics.

AR1

Device

Figure 4-18 ID Read (1) Timing

code

42

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 43

SmartMedia 128MByte Product Manual

5.0 Application Notes and Comments

5.1 Prohibition of Unspecified Commands

The operation commands are listed in Table 3-3. Input of a command other than those specified in

Table 3-3 is prohibited. Stored data may be corrupted if an unknown command is entered during the

command cycle.

5.2 Restriction of Commands While in Busy State

During the Busy state, do not input any command except 70H, 71H or FFH.

5.3 Pointer Control for 00H, 01H and 50H

The device has three Read modes which set the destination of the pointer. Table 5-1 shows the destination

of the pointer, and Figure 5-1 is a block diagram of their operations.

Table 5-1 Pointer Destination

Read Mode Command Pointer

(1) 00H 0 to 255

(2) 01H 256 to 511

(3) 50H 512 to 527

The pointer is set to region A by the 00H command, to region B by the 01H command, and to region C by

the 50H command. For example, the 00H command must be input to set the pointer back to region A when

the pointer is pointing to region C. To program region C only, set the start point to region C using the 50H

command.

Figure 5-1 Pointer Control

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

43

Page 44

SmartMedia 128MByte Product Manual

Figure 5-2 Example of How to Set the Pointer

5.4 Acceptable Commands After Serial Input Command 80H

Once the Serial Input command 80H has been input, do not input any command other than the Program

Execution command 10H, 11H or 15H or the Reset command FFH.

Figure 5-3 Serial Input Command

44

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 45

SmartMedia 128MByte Product Manual

5.5 Status Read During a Read Operation

The device status can be read out by inputting the Status Read command 70H in Read mode. Once the

device has been set to Status Read mode by a 70H command, the device will not return to Read mode.

Therefore, a Status Read during a Read operation is prohibited. However, when the Read command 00H is

input during [A], Status mode is reset and the device returns to Read mode. In this case, data output starts

automatically from address N and address input is unnecessary.

Figure 5-4 Status Read During a Read Operation

5.6 Auto-Programming Failure

Figure 5-5 Auto-programming Failure

5.7 Addressing for Program Operation

Within a block, the pages must be programmed consecutively from the LSB (least significant bit) page of

the block. Random page address input is prohibited.

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

45

Page 46

SmartMedia 128MByte Product Manual

5.8 R/B: Termination for the Ready/Busy Pin ( R/B)

A pull-up resistor needs to be used for termination because the

circuit.

Figure 5-6 Termination of the Ready/Busy Pin

5.9 Status After Power-on

R/B buffer consists of an open drain

The following sequence is necessary because some input signals may not be stable at power-on.

Figure 5-7 Status After Power-on

5.10 Power-on/off Sequence

The

WP signal is useful for protecting against data corruption at power-on/off. The following timing

sequence is necessary:

2.7 V

2.5 V

V

V

CC

Don’t

care

IL

V

IH

Operation

Don’t

care

V

IL

0 V

CE, WE, RE

CLE, ALE

WP

Figure 5-8 Power-on/off Sequence

46

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 47

5.11 Note Regarding the WP Signal

SmartMedia 128MByte Product Manual

The Erase and Program operations are automatically reset when

enabled and disabled as follows:

Figure 5-9 Enable Programming

WP goes Low. The operations are

Figure 5-10 Disable Programming

Figure 5-11 Enable Erasing

Figure 5-12 Disable Erasing

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

47

Page 48

SmartMedia 128MByte Product Manual

5.12 When Five Address Cycles are Input

Although the device may read in a fifth address, it is ignored inside the chip.

Figure 5-13 Read Operation

Figure 5-14 Program Operation

48

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 49

SmartMedia 128MByte Product Manual

5.13 Several Programming Cycles on the Same Page (Partial Page Program)

A page can be divided into a maximum of three segments. Each segment can be programmed individually

as follows:

(SSFDC Forum specification permits up to MAX 2 times: The second write should be in 16Byte area of

512+16Byte.)

Figure 5-15 Partial Page Program

5.14 Note Regarding the RE Signal

The internal column address counter is incremented synchronously with the

Therefore, once the device has been set to Read mode by an 00H, 01H or 50H command, the internal

column address counter is incremented by the

RE clock input pulses start before the address input, and the pointer reaches the last column address, an

RE clock independently of the address input timing. If the

internal read operation (array to register) will occur and the device will enter Busy state. (Refer to the

following figure.) Hence the

RE clock input must start after the address input.

RE clock in Read mode.

Figure 5-16 Internal Read Operation (Array to Register)

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

49

Page 50

SmartMedia 128MByte Product Manual

5.15 Invalid Blocks (Bad Blocks)

This product occasionally contains unusable blocks. Therefore, the following issues must be recognized:

• Referring to the Block status area in the redundant area allows the system to detect bad blocks in

accordance with the physical data format issued by the SSFDC Forum. Detect the bad blocks by

checking the Block Status Area at the system power-on, and do not access the bad blocks in the

following routine. The number of valid blocks at the time of shipment is shown in the following

table.

Table 5-2 Number of Valid Blocks

Valid (Good) Block

Number

*: SSFDC Forum Spec. : 1002 MIN per Zone (each 16 k Bytes)

Min. Max. Unit

8032 8192 Block

Bad Block

Bad Block

Figure 5-17 Bad Blocks in Array

50

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 51

SmartMedia 128MByte Product Manual

Block No. = Block No. +1

No

Start

Block No. = 1

Read Check

Pass

Block No. = 4096

Read Check: to verify all pages in the block

with FF (Hex)

Fail

Bad Block *1

Yes

End

*1: No erase operation is allowed to detected bad blocks.

Figure 5-18 Bad Block Test Flow

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

51

Page 52

SmartMedia 128MByte Product Manual

5.16 Failure Phenomena for Program and Erase Operations

The device may fail during a Program or Erase operation. The following possible failure modes should be

considered when implementing a highly reliable system.

Table 5-3 Failure Modes

Failure Mode Detection and Counter Measure Sequence

Block Erase Failure Status Read after Erase → Block Replacement

Page Programming Failure Status Read after Program → Block Replacement

Single

Bit

Programming Failure

“ 1 to 0 ”

(1) Block Verify after Program → Retry

(2) ECC

• ECC: Error Correction Code

• Block Replacement

Figure 5-19 Program Fail Block Replacement

5.17 Chattering of Connector

There may be contact chattering when the SmartMedia Card is inserted or removed from a connector. This

chattering may cause damage to the data in the SmartMedia Card. Therefore, sufficient time must be

TM

allowed for contact bouncing to subside when a system is designed with SmartMedia

.

• The SmartMedia Card is formatted to comply with the Physical and Logical Data Format of the

SSFDC Forum at the time of shipping.

52

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 53

SmartMedia 128MByte Product Manual

6.0 Handling Precautions

The following precautions should be observed when handling the SanDisk SmartMedia Card:

(1) Avoid using the SmartMedia Card when the battery is low.

(2) When writing to the card, wait for the operation to complete before removing the card.

(3) The card is designed to fit easily into the system one way only. Do not force it into the slot.

(4) Do not bend the card.

(5) Do not subject the card to sudden impact.

Avoid touching the connectors so as to avoid damage from static electricity. This card should be kept

(6)

in the antistatic film case when not in use.

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

53

Page 54

SmartMedia 128MByte Product Manual

7.0 Package Dimensions

7.1 SmartMedia Card Dimensions

The SanDisk SmartMedia Card dimensions are shown below in Figure 7-1.

Figure 7-1 SmartMedia Card Dimensions

54

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 55

SmartMedia 128MByte Product Manual

Ordering Information

and

Technical Support

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

55

Page 56

This page has been left blank intentionally.

56

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 57

Ordering Information and Technical Support

Ordering Information

To order SanDisk products directly from SanDisk, call 408-542-0595.

SmartMedia Card

Model SDSM-128-101-01 128.0 MB

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

57

Page 58

Ordering Information and Technical Support

Technical Support Services

Direct SanDisk Technical Support

Call SanDisk Applications Engineering at 408-542-0405 for technical support.

SanDisk Worldwide Web Site

Internet users can obtain technical support and product information along with SanDisk news and much

more from the SanDisk Worldwide Web Site, 24 hours a day, seven days a week. The SanDisk Worldwide

Web Site is frequently updated. Visit this site often to obtain the most up-to-date information on SanDisk

products and applications. The SanDisk Web Site URL is http://www.sandisk.com.

58

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 59

SanDisk Sales Offices

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

59

Page 60

This page has been left blank intentionally.

60

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 61

SanDisk Worldwide Sales Offices

SanDisk Worldwide Sales Offices

Americas

SanDisk Corporate Headquarters

140 Caspian Court

Sunnyvale, CA 94089-9820

408-542-0500

FAX 408-542-0503

http://www.sandisk.com

Sales Offices

Western Region USA

408-542-0730

FAX 408-542-0403

Eastern Region USA & Canada

603-882-0888

FAX 603-882-2201

Central & Southern Region USA

614-760-3700

FAX 614-760-3701

Latin & South America

407-667-4880

FAX 407-667-4834

Europe

SanDisk GmbH

Karlsruher Str. 2C

D-30519 Hannover, Germany

49-511-8759185

FAX 49-511-8759187

SanDisk Northern Europe

Videroegaten 3 B

S-16440 Kista

Sweden

46-(0)8-75084-63

FAX 46-(0)8-75084-26

SanDisk Central Europe

Rudolf-Diesel-Str. 3

40822 Mettmann

Germany

49-(0)2104-953433

FAX 49-(0)2104-953434

Japan

SanDisk K.K.

8F Nisso Bldg. 15

2-17-19 Shin-Yokohama, Kohoku-ku

Yokohama 222-0033, Japan

81-45-474-0181

FAX 81-45-474-0371

Asia/Pacific Rim

89 Queensway, Lippo Center

Tower II, Suite 4104

Admiralty, Hong Kong

852-2712-0501

FAX 852-2712-9385

To order SanDisk products directly from SanDisk,

call 408-542-0595.

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

61

Page 62

This page has been left blank intentionally.

62

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Page 63

Limited Warranty

Limited Warranty

I. WARRANTY STATEMENT

SanDisk warrants its products to be free of any defects in materials or workmanship that would prevent them from

functioning properly for one year from the date of purchase. This express warranty is extended by SanDisk

Corporation.

II. GENERAL PROVISIONS

This warranty sets forth the full extent of SanDisk’s responsibilities regarding the SanDisk SmartMedia Card. In

satisfaction of its obligations hereunder, SanDisk, at its sole option, will either repair, replace or refund the purchase

price of the product.

NOTWITHSTANDING ANYTHING ELSE IN THIS LIMITED WARRANTY OR OTHERWISE, THE EXPRESS

WARRANTIES AND OBLIGATIONS OF SELLER AS SET FORTH IN THIS LIMITED WARRANTY, ARE IN LIEU

OF, AND BUYER EXPRESSLY WAIVES ALL OTHER OBLIGATIONS, GUARANTIES AND WARRANTIES OF ANY

KIND, WHETHER EXPRESS OR IMPLIED, INCLUDING WITHOUT LIMITATION, ANY IMPLIED WARRANTY OF

MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE OR INFRINGEMENT, TOGETHER WITH ANY

LIABILITY OF SELLER UNDER ANY CONTRACT, NEGLIGENCE, STRICT LIABILITY OR OTHER LEGAL OR

EQUITABLE THEORY FOR LOSS OF USE, REVENUE, OR PROFIT OR OTHER INCIDENTAL OR

CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION PHYSICAL INJURY OR DEATH,

PROPERTY DAMAGE, LOST DATA, OR COSTS OF PROCUREMENT OF SUBSTITUTE GOODS, TECHNOLOGY

OR SERVICES. IN NO EVENT SHALL THE SELLER BE LIABLE FOR DAMAGES IN EXCESS OF THE PURCHASE

PRICE OF THE PRODUCT, ARISING OUT OF THE USE OR INABILITY TO USE SUCH PRODUCT, TO THE FULL

EXTENT SUCH MAY BE DISCLAIMED BY LAW.

SanDisk’s products are not warranted to operate without failure. Accordingly, in any use of products in life support

systems or other applications where failure could cause injury or loss of life, the products should only be incorporated

in systems designed with appropriate redundancy, fault tolerant or back-up features.

III. WHAT THIS WARRANTY COVERS

For products found to be defective within one year of purchase, SanDisk will have the option of repairing or replacing

the defective product, if the following conditions are met:

A. The defective product is returned to SanDisk for failure analysis as soon as possible after the failure occurs.

B. An incident card filled out by the user, explaining the conditions of usage and the nature of the failure,

accompanies each returned defective product.

C. No evidence is found of abuse or operation of products not in accordance with the published specifications,

or of exceeding storage or maximum ratings or operating conditions.

All failing products returned to SanDisk under the provisions of this limited warranty shall be tested to the product’s

functional and performance specifications. Upon confirmation of failure, each product will be analyzed, by whatever

means necessary, to determine the root cause of failure. If the root cause of failure is found to be not covered by the

above provisions, then the product will be returned to the customer with a report indicating why the failure was not

covered under the warranty.

This warranty does not cover defects, malfunctions, performance failures or damages to the unit resulting from use in

other than its normal and customary manner, misuse, accident or neglect; or improper alterations or repairs.

SanDisk reserves the right to repair or replace, at its discretion, any product returned by its customers, even if such

product is not covered under warranty, but is under no obligation to do so.

SanDisk may, at its discretion, ship repaired or rebuilt products identified in the same way as new products, provided

such cards meet or exceed the same published specifications as new products. Concurrently, SanDisk also reserves the

right to market any products, whether new, repaired, or rebuilt, under different specifications and product

designations if such products do not meet the original product’s specifications.

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

63

Page 64

Limited Warranty

IV. RECEIVING WARRANTY SERVICE

According to SanDisk’s warranty procedure, defective product should be returned only with prior authorization from

SanDisk Corporation. Please contact SanDisk’s Customer Service department at 408-542-0595 with the following

information: product model number and description, nature of defect, conditions of use, proof of purchase and

purchase date. If approved, SanDisk will issue a Return Material Authorization or Product Repair Authorization

number. Ship the defective product to:

SanDisk Corporation

Attn: RMA Returns

(Reference RMA or PRA #)

140 Caspian Court

Sunnyvale, CA 94089

V. STATE LAW RIGHTS

SOME STATES DO NOT ALLOW THE EXCLUSION OR LIMITATION OF INCIDENTAL OR CONSEQUENTIAL

DAMAGES, OR LIMITATION ON HOW LONG AN IMPLIED WARRANTY LASTS, SO THE ABOVE LIMITATIONS

OR EXCLUSIONS MAY NOT APPLY TO YOU. This warranty gives you specific rights and you may also have other

rights that vary from state to state.

64

SmartMedia 128MByte Product Manual Rev. 1.2 © 2001 SANDISK CORPORATION

Loading...

Loading...