Samsung X430 Service Manual

GSM TELEPHONE

SGH-X430

SERVICE

Manual

GSM TELEPHONE CONTENTS

1. Specification

2. Circuit Description

3. Flow Chart of Troubleshooting

4. Exploded Views and Parts List

5. Electrical Parts List

6. Block Diagrams

7. PCB Diagrams

This Service Manual is a property of Samsung

ELECTRONICS

Electronics Co.,Ltd.

Any unauthorized use of Manual can be punished

under applicable International and/or domestic law.

ⓒ

Samsung Electronics Co.,Ltd. December. 2003

Printed in Korea.

Code No.: GH68-04389A

BASIC.

1. SGH-X430 Specification

1-1

1. GSM General Specification

GSM900

Phase 1

Freq. Band[MHz]

Uplink/Downlin k

ARFCN range 1~124 0~12 4 & 975~1023 512~885

Tx/Rx sp acing 45MHz 45MHz 95MHz

Mod. Bit rate/

Bit Period

Time Slot

Period/Frame Period

Modu lation 0.3GMSK 0.3GMSK 0.3GMSK

MS Power 33dBm~13dBm 33dBm~5dBm 30dBm~0dBm

890~915

935~960

270.833k bps

3.69 2us

576.9us

4.61 5ms

EGSM 900

Phase 2

880~915

925~960

270.833k bps

3.69 2us

576.9us

4.61 5ms

DCS1800

1710 ~1785

1805 ~1880

270.833k bps

Phase 1

3.69 2us

576.9us

4.61 5ms

Power Class 5pcl ~ 15pcl 5pcl ~ 19pcl 0pcl ~ 15pcl

Sensitivity -102 dBm -102 dBm -100 dBm

TDMA Mux 8 8 8

Cell Radius 35Km 35Km 2Km

This Document can not be used without Samsung's authorization

SAMSUNG Proprietary-Contents may change without notice

1. SGH-X430 Specification

1-2

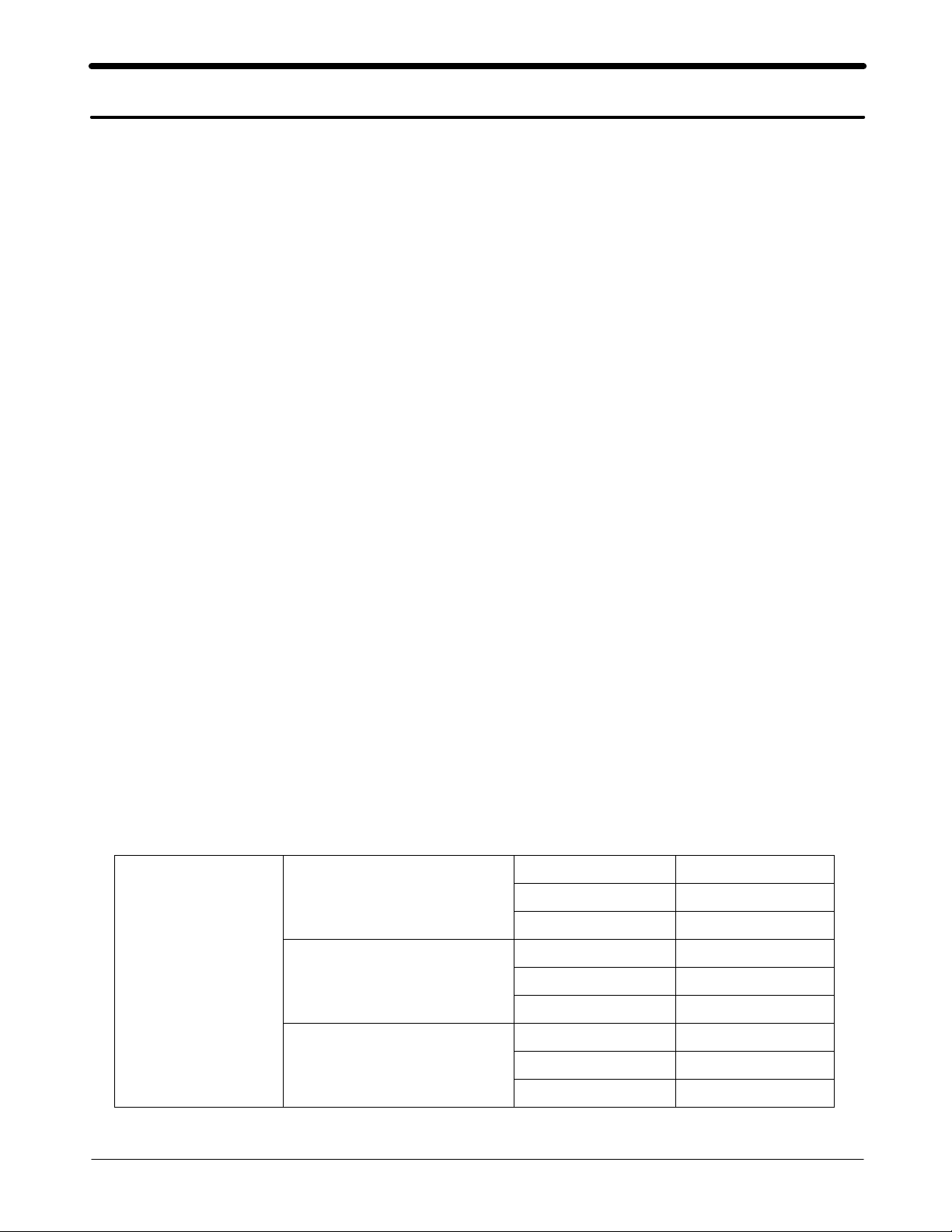

2. GSM TX power class

TX Power

control level

5 33±2 dBm

6 31±2 dBm

7 29±2 dBm

8 27±2 dBm

9 25±2 dBm

10 23±2 dBm

11 21±2 dBm

GSM900

TX Power

DCS1800

control level

0 30±3 dBm

1 28±3 dBm

2 26±3 dBm

3 24±3 dBm

4 22±3 dBm

5 20±3 dBm

6 18±3 dBm

12 19±2 dBm

13 17±2 dBm

14 15±2 dBm

15 13±2 dBm

16 11±3 dBm

17 9±3dBm

18 7±3 dBm

19 5±3 dBm

7 16±3 dBm

8 14±3 dBm

9 12±4 dBm

10 10±4 dBm

11 8±4dBm

12 6±4 dBm

13 4±4 dBm

14 2±5 dBm

15 0±5 dBm

This Document can not be used without Samsung's authorization

SAMSUNG Proprietary-Contents may change without notice

2. SGH-X430 Circuit Description

2-1

1. SGH-X430 RF Circuit Description

1) RX PART

1. ASM(U201)

Switching Tx, Rx path for GSM900, DCS1800 by logic controlling.

ð

2. ASM Control Logic (U501, U502)

Truth Table

ð

VC1 VC2

GSM Tx Mode L H

DCS Tx Mode H L

GSM / DCS Rx Mode L L

3. FILTER

To convert Electromagnetic Field Wave to Acoustic Wave and then pass the

specific frequency band.

- GSM FILTER (F100)

For filtering the frequency band between 925 ~ 960 MHz

ð

- DCS FILTER (F101)

For filtering the frequency band 1805 and 1880 MHz.

ð

4. VCTCXO (OSC100)

To generate the 13MHz reference clock to drive the logic and RF.

After additional process, the reference clock is applied to the U100 Rx IQ

demodulator and Tx IQ modulator.

The oscillator for RX IQ demodulator and Tx modulator are controlled by

serial data to select channel and use fast lock mode for GPRS high class

operation.

This Document can not be used without Samsung's authorization

SAMSUNG Proprietary-Contents may change without notice

2. SGH-X430 Circuit Description

2-2

5. Si 4205 (U100)

This chip integrates three differential-input LNAs.

The GSM input supports the E-GSM, DCS input supports the DCS1800, PCS

input supports the PCS1900. The LNA inputs are matched to the 200 ohm

differential output SAW filters through eternal LC matching network.

Image-reject mixer downconverts the RF signal to a 100 KHz intermediate

frequency(IF) with the RFLO from SI4133T frequency synthesizer.

The RFLO frequency is between 1737.8 ~ 1989.9 MHz.

The Mixer output is amplified with an analog programmable gain

amplifier(PGA), which is controlled by AGAIN.

The quadrature IF signal is digitized with high resolution A/D converts (ADC).

The SI4205 down-converts the ADC output to baseband with a digital

100 KHz quadrature LO signal.

Digital decimation and IIR filters perform channel selection to remove blocking

and reference interface signals. After channel selection, the digital output is

scaled with a digital PGA, which is controlled with the DGAIN. DACs drive a

differential analog signal onto the RXIP, RXIN, RXQP, RXQN pins to interface

to standard analog-input baseband IC.

2) TX PART

Baseband IQ signal fed into offset PLL, this function is included inside

of U100 chip.

SI4205 chip generates modulator signal which power level is about 1.5dBm

and fed into Power Amplifier(U200).

The PA output power and power ramping are well controlled by Auto

Power Control circuit. We use offset PLL below,

GSM -35dBc

DCS -35dBc

PCS -35dBc

GSM -66dBc

DCS -65dBc

PCS -66dBc

GSM -75dBc

DCS -68dBc

PCS -75dBc

Modulation

Spectrum

200kHz offset

30 kHz bandwidth

400kHz offset

30 kHz bandwidth

600kHz ~ 1.8MHz offset

30 kHz bandwidth

This Document can not be used without Samsung's authorization

SAMSUNG Proprietary-Contents may change without notice

2. SGH-X430 Circuit Description

2-3

2. Baseband Circuit description of SGH-X430

1) PSC2106

1. Power Management

Seven low-dropout regulators designed specifically for GSM applications

power the terminal and help ensure optimal system performance and long

battery life.

A programmable LDO provides support for 1.8V, 3.0V SIMs, while a

self-resetting, electronically fused switch supplies power to external

accessories. Ancillary support functions, such as two LED drivers and two

call-alert drivers, aid in reducing both board area and system complexity.

A four-wire serial interface unit(SIU) provides access to control and

configuration registers. This interface gives a microprocessor full control of

the PSC2106 and enables system designers to maximize both standby and

talk times. Error reporting is provided via an interrupt signal and status

register.

Supervisory functions. including a reset generator, an input voltage monitor,

and a thermal monitor, support reliable system design. These functions

work together to ensure proper system behavior during start-up or in the

event of a fault condition(low microprocessor voltage, insufficient battery

energy, or excessive die temperature).

2. Battery Charge Management

A battery charge management block, incorporating an internal PMOS switch,

and an 8-bit ADC, provides fast, efficient charging of single-cell Li-Ion

battery. Used in conjunction with a current-limited voltage source, this block

safely conditions near-dead cells and provides the option of having

fast-charge and top-off controlled internally or by the system's

microprocessor.

3. Backlight LED Driver

The backlight LED driver is a low-side, programmable current source

designed to control the brightness of the keyboard and LCD illumination.

LED1_DRV is controlled via LED1_[0:2] and can be programmed to sink

from 15mA to 60mA in 7.5mA steps. LED2_DRV is controlled via LED2_

[0:2] and can be programmed to sink from 5mA to 40mA in 5mA steps.

Both LED drivers are capable of sinking their maximum output current at a

worst-case maximum output voltage of 0.6V. For efficient use, the LEDs is

connected between the battery and the LED_DRV output.

This Document can not be used without Samsung's authorization

SAMSUNG Proprietary-Contents may change without notice

2. SGH-X430 Circuit Description

2-4

4. Vibrator Motor Driver

The vibrator motor driver is a low-side, programmable voltage source

designed to drive a small dc motor that silently alerts the user of an

incoming call. The driver is controlled by VIB[0:1] and can be programmed

to maintain a motor voltage of 1.3V, 2.0V, or 2.5V(relative to V

sinking up to 100mA. For efficient use, the vibrator motor should be

connected between the main battery and the VIB_DRV output.

2) Connector

1. LCD Connector

LCD is consisted of main LCD(color 65K UFB LCD). Chip select signals of

EMI part in the trident, CLCD_EN, can enable main LCD. LED_EN signal

enables white LED of main LCD and EL_EN signal enables dimming mode

of main LCD.

These two signals are from IO part of the DSP in the trident. RST signal

from 2106 initiates the initial process of the LCD.

16-bit data lines(D(0)~D(15)) transfers data and commands to LCD through

emi_filter. Data and commands use A(2) signal. If this signal is high, Inputs

to LCD are commands. If it is low, Inputs to LCD are data. The signal

which informs the input or output state to LCD, is required. But this system

is not necessary this signal. So CP_WEN signal is used to write data or

commands to LCD.

Power signals for LCD are +VBATT and VCCD.

SPK1P and SPK1N from CSP1093 are used for audio speaker. And

YMU_VIB_EN from MA-3 enables the motor.

BAT

) while

2. JTAG Connector

Trident has two JTAG ports which are for ARM core and DSP

core(DSP16000). So this system has two port connector for these ports.

Pins' initials for ARM core are 'CP_' and pins' initials for DSP core are

'DSP_'.

CP_TDI and DSP_TDI signal are used for input of data. CP_TDO and

DSP_TDO signals are used for the output of the data. CP_TCK and

DSP_TCK signals are used for clock because JTAG communication is a

synchronous. CP_TMS and DSP_TMS signals are test mode signals. The

difference between these is the RESET_INT signal which is for ARM core

RESET.

This Document can not be used without Samsung's authorization

SAMSUNG Proprietary-Contents may change without notice

2. SGH-X430 Circuit Description

2-5

3. Keypad connector

This is consisted of key interface pins in the trident, KEY_ROW[0~4] and

KEY_COL[0~4]. These signals compose the matrix. Result of matrix informs

the key status to key interface in the trident. Some pins are connected to

varistor for ESD protection. And power on/off key is seperated from the

matrix.

So power on/off signal is connected with PSC2106 to enable PSC2106.

SVC_GREEN, SVC_RED and SVC_BLUE are from OCTL of CSP1093.

These signals decide the color of LED, service indicator.

Nine key LED use the +VBATT supply voltage. These are connected to

BACKLIGHT signal in the PSC2106.

This signal enables LEDs with current control. FLIP_SNS informs the status

of folder (open or closed) to the trident. This uses the hall effect IC,

A3210ELH.

A magnet under main LCD enables A3210ELH which is on the main PCB.

4. EMI Filtering

This system uses the EMI Filter to reduce noise from LCD part. Some

control signals are connected to LCD without EMI filtering.

3) IF connetor

It is 23-pin connector, and uses 18-pin at present. They are designed to use

SDS, DEBUG, DLC-DETECT, JIG_ON, VEXT, VTEST, VF, +VBATT and GND.

They connected to power supply IC, microprocessor and signal processor IC.

4) Audio

AOUTAP, AOUTAN from CSP1093 is connected to the speaker via analog

switch. AOUTBP and AOUTBN are connected to the ear-mic speaker via

ear-jack. MICIN and MICOUT are connected to the main MIC. And AUXIN and

AUXOUT are connected to the Ear-mic.

YMU762MA3 is a LSI for portable telephone that is capable of playing high

quality music by utilizing FM synthesizer and ADPCM decorder that are

included in this device.

As a synthesis, YMU762MA3 is equipped 16 voices with differenttones. Since

the device is capable of simultaneously generating up to synchronous with the

play of the FM synthesizer, various sampled voices can be used as sound

effects.

This Document can not be used without Samsung's authorization

SAMSUNG Proprietary-Contents may change without notice

2. SGH-X430 Circuit Description

2-6

Since the play data of YMU762MA3 are interpreted at anytime through FIFO,

the length of the data(playing period) is not limited, so the device can

flexiblysupport application such as incoming call melody music distribution

service. The hardware sequencer built in this device allows playing of the

complex music without giving excessive load to the CPU of the portable

telephones. Moreover, the registers of the FM synthesizer can be operated

directly for real time sound generation, allowing, for example, utilization of

various sound effects when using the game software installed in the portable

telephone.

YMU762 includes a speaker amplifier with high ripple removal rate whose

maximum output is 550mW (SPVDD=3.6V). The device is also equipped with

conventional function including a vibartor and a circuit for controlling LEDs

synchornous with music.

For the headphone, it is provided with a stereophonic output terminal.

For the purpose of enabling YMU762MA3 to demonstarte its full capablities,

Yamaha purpose to use "SMAF:Synthetic music Mobile Application Format" as a

data distribution format that is compatible wiht multimedia. Since the SMAF

takes a structure that sets importance on the synchronization between sound

and images, various contents can be written into it including incoming call

melody with words that can be used for traning karaoke, and commercial

channel that combines texts, images and sounds, and others. The hardware

sequencer of YMU762MA3 directly interprets and plays blocks relevant to

systhesis (playing music and reproducing ADPCM with FM synthesizer) that are

included in data distributed in SMAF.

5) Memory

This system uses SHARP's memory, LRS1828.

It is consisted of 128M bits flash memory and 32M bits SCRAM. It has 16 bit

data line, D[0~15] which is connected to trident, LCD or CSP1093. It has 22

bit address lines, A[1~22]. They are connected too. CP_CSROMEN and

CO_CSROM2EN signals, chip select signals in the trident enable two memories.

They use 3 volt supply voltage, VCCD.

During wrting process, CP_WEN is low and it enables writing process to flash

memory and SCRAM. During reading process, CP_OEN is low and it output

information which is located at the address from the trident in the flash

memory or SCRAM to data lines. Each chip select signals in the trident select

memory among 2 flash memory and SCRAM. Reading or writing procedure is

processed after CP_WEN or CP_OEN is enabled. Memories use FLASH_RESET,

which is buffered signal of RESET from PSC2106, for ESD protection. A[0]

signal enables lower byte of SCRAM and UPPER_BYTE signal enables higher

byte of SCRAM.

This Document can not be used without Samsung's authorization

SAMSUNG Proprietary-Contents may change without notice

2. SGH-X430 Circuit Description

2-7

6) Trident

Trident is consisted of ARM core and DSP core. It has 20K*16bits RAM

144K*16bits ROM in the DSP. It has 4K*32bits ROM and 2K*32bits RAM in the

ARM core. DSP is consisted of timer, one bit input/output unit(BIO), JTAG, EMI

and HDS(Hardware Development System). ARM core is consisted of EMI,

PIC(Programmable Interrupt Controller), reset/power/clock unit, DMA controller,

TIC(Test Interface Controller), peripheral bridge, PPI, SSI(Synchronous Serial

Interface), ACCs(Asynchronous communications controllers), timer, ADC,

RTC(Real-Time Clock) and keyboard interface.

DSP_AB[0~8], address lines of DSP core and DSP_DB[0~15], data lines of

DSP core are connected to CSP1093. A[0~20], address lines of ARM core and

D[0~15], data lines of ARM core are connected to memory, LCD and YMU762.

ICP(Interprocessor Communication Port) controls the communication between

ARM core and DSP core.

CSROMEN, CSRAMEN and CS1N to CS4N in the ARM core are connected to

each memory. WEN and OEN control the process of memory. External

IRQ(Interrupt ReQuest) signals from each units, such as, YMU, Ear-jack,

Ear-mic and CSP1093, need the compatible process.

Some PPI pins has many special functions. CP_KB[0~9] receive the status

from key FPCB and are used for the communicatios using data link

cable(DEBUG_DTR/RTS/TXD/RXD/CTS/DSR).

And UP_CS/SCLK/SDI, control signals for PSC2106 are outputted through PPI

pins. It has signal port for charging(CHG_DET), SIM_RESET and FLIP_SNS with

which we knows open.closed status of folder. It has JTAG control

pins(TDI/TDO/TCK) for ARM core and DSP core. It recieves 13MHz clock in

CKI pin from external TCXO and receives 32.768KHz clock from X1RTC.

ADC(Analog to Digital Convertor) part receives the status of temperature,

battery type and battery voltage. And control signals(DSP_INT, DSP_IO and

DSP_RWN) for DSP core are used. It enables main LCD with DSP IP pins.

7) CSP1093

CSP1093 integrates the timing and control functions for GSM 2+ mobile

application with the ADC and DAC functions. The CSP1093 interfaces to the

trident, via a 16-bit parallel interface. It serves as the interface that connects

a DSP to the RF circuitry in a GSM 2+ mobile telephone. DSP can load 148

bits of burst data into CSP1093’s internal register, and program CSP1093’s

event timing and control register with the exact time to send the burst. When

the timing portion of the event timing and control register matches the internal

quarter-bit counter and internal frame counter, the 148 bits in the internal

This Document can not be used without Samsung's authorization

SAMSUNG Proprietary-Contents may change without notice

2. SGH-X430 Circuit Description

2-8

register are GMSK modulated according to GSM 2+ standards. The resulting

phase information is translated into I and Q differential output voltages that can

be connected directly to an RF modulator at the TXOP and TXON pins. The

DSP is notified when the transmission is completed. For receiving baseband

data, a DSP can program CSP1093’s event timing and control register with the

exact time to start receiving I and Q samples through TXIP and TXIN pins.

When that time is reached, the control portion of the event timing and control

register will start the baseband receive section converting I and Q sample

pairs. The samples are stored in a double-buffered register until the register

contains 32 sample pairs. CSP1093 then notifies the DSP which has ample time

to read the information out before the next 32 sample pairs are stored. The

voice band ADC converter issues an interrupt to the DSP whenever it finishes

converting a 16-bit PCM word. The DSP then reads the new input sample and

simultaneously loads the voice band output DAC converter with a new PCM

output word. The voice band output can be connected directly to a speaker via

AOUTAN and AOUTAP pins and be connected to a Ear-mic speaker via

AOUTBN and AOUTBP pins.

8) X-TAL(13MHz)

This system uses the 13MHz TCXO, TCO-9141B, Toyocom. AFC control signal

form CSP1093 controls frequency from 13MHz x-tal. It generates the clock

frequency. This clock is fed to CSP1093,Trident,YMU762 and Silab solution.

This Document can not be used without Samsung's authorization

SAMSUNG Proprietary-Contents may change without notice

Loading...

Loading...