Samsung TL7231MD Datasheet

TL7231MD

FULL LAYER-III ISO/IEC 11172-3 AUDIO DECODER

n Single-chip ISO/IEC 11172-3 Layer

III Audio Decoder

n Supports All MPEG Bit Rates

Including Free Format

n Supports 32/44.1/48KHz Sampling

Frequencies for MPEG Bit Stream

n Supports Single Channel, Dual

Channel, Stereo, and Joint Stereo

n Any Combination of Intensity

Stereo and MS Stereo is

supported.

n Serial Bit Stream Input

n 8-bit Host Interface Port

n Digital Volume Control

n Digital Bass/Treble Control

n 6-Band Equalizer Function

n Voice Record/Playback Capability

n On-chip DAC with 1-bit Sigma Delta

Modulation

n Supports Off-chip DAC Interface

n On-chip ADC with 12-bit Resolution

n Power Management to Reduce

Power Consumption

n PLL for Internal Clocks and for

Output PCM Clock Generation

n Single 16.9344MHz External Clock

Input

n 3.0 V Operation

n Small Footprint 100-pin Thin Quad

Flat Package

DESCRIPTION

TL7231MD is a single-chip ISO/IEC 11172-3 Layer III audio decoder, capable of decoding

compressed elementary bit streams as specified in ISO/IEC standard. Since it integrated onchip ADC and on-chip DAC, it can provide you more small and cheaper solution for MP3 player

application. It is designed to be well suited for portable audio appliances.

TL7231MD receives the input data bit stream through a serial data interface. The decoded

signal is 16-bit serial PCM format that can be sent directly to DAC. The generated PCM data

can be sent to on-chip DAC or off-chip DAC according to user preference. The off-chip DAC

interface is programmable to adapt the PCM output of TL7231MD to the most common DACs

used on the market.

An 8-bit host interface port is provided to receive control information from and send status

information to host. 8-bit microcontrollers such as those of Intel or Motorola can be connected

easily.

TL7231MD has the capability of compressing voice signals. It can receive voice signals through

on-chip ADC. The compressed voice signals are transmitted to or received from host through

serial data interface. It can also reproduce the voice signals from the compressed voice signals.

September 1999 1/37

TL7231MD

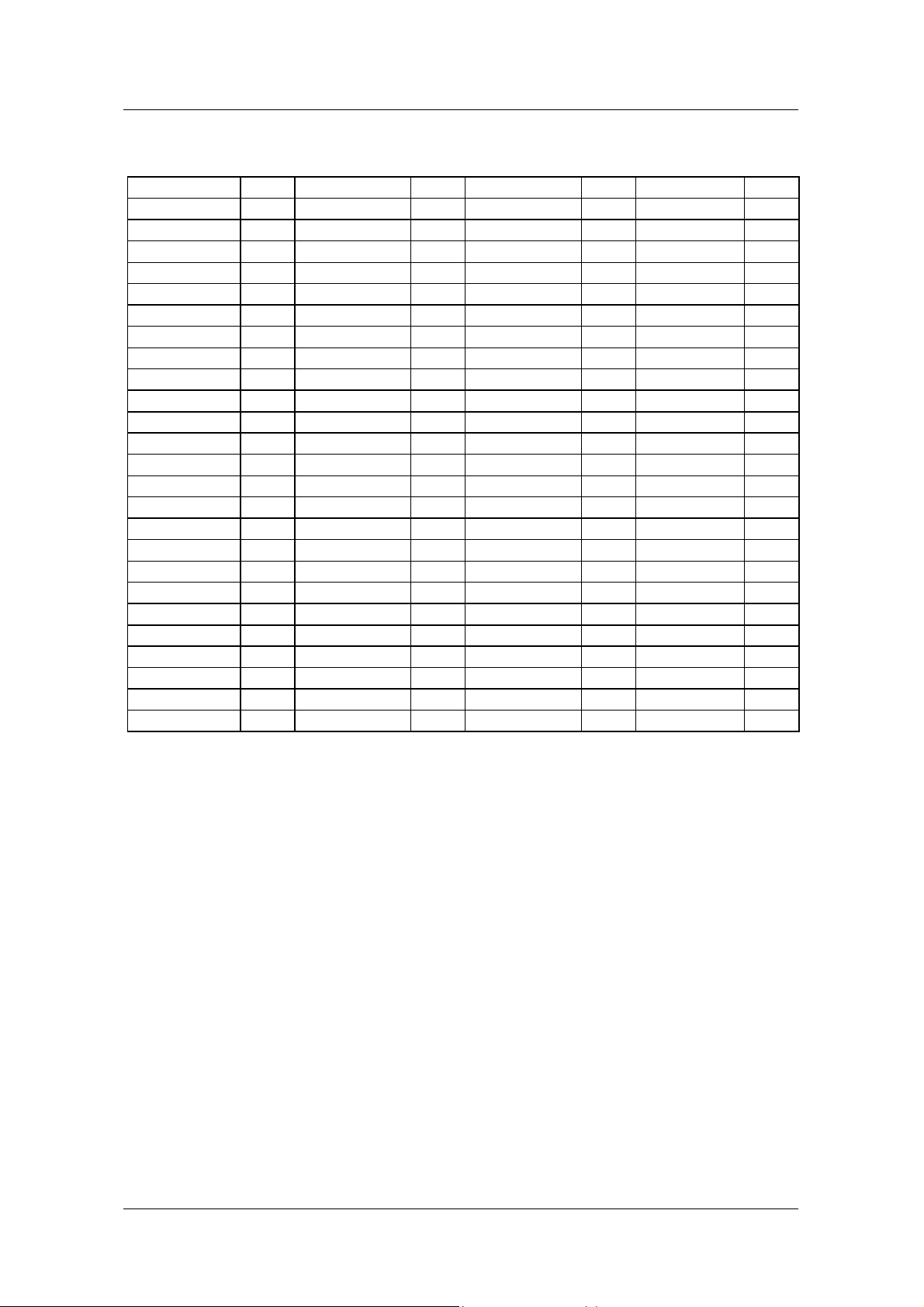

FUNCTIONAL BLOCK DIAGRAM

CPUXI

CPUXO

FILTER

RESET

WAKEUP

PWRDN

CONSTANT

ROM

DATA READ0

DATA READ1

DATA WRITE0

DATA WRITE1

DMA BUS

RESET/

CLOCK

UNIT

INPUT

BUFFER

OUTPUT

BUFFER

BUS CONTROL UNIT

READ DATA1

READ DATA0

WRITE DATA0

WRITE DATA1

WORKING

SPACE

DMA

CONTROLLER

CRC

SERIAL0

PROGRAM

ROM

M

U

X

HOST

INTERFACE

SERIAL1

DAC

HD7:0

HALE

HRD#

HWR#

HSEL#

CLKXRM

DXRM

REQSTRM

DACMSCK

DACBCK

DACLRCK

DACSDATA

DACDEEM

DACMUTE#

AOUTL

AOUTR

DSP Core Unit

TIMER0

ADC

ADCAIN

TIMER1

Figure 1. Functional Block Diagram of TL7231MD

2/37 SAMSUNG Electronics Co.

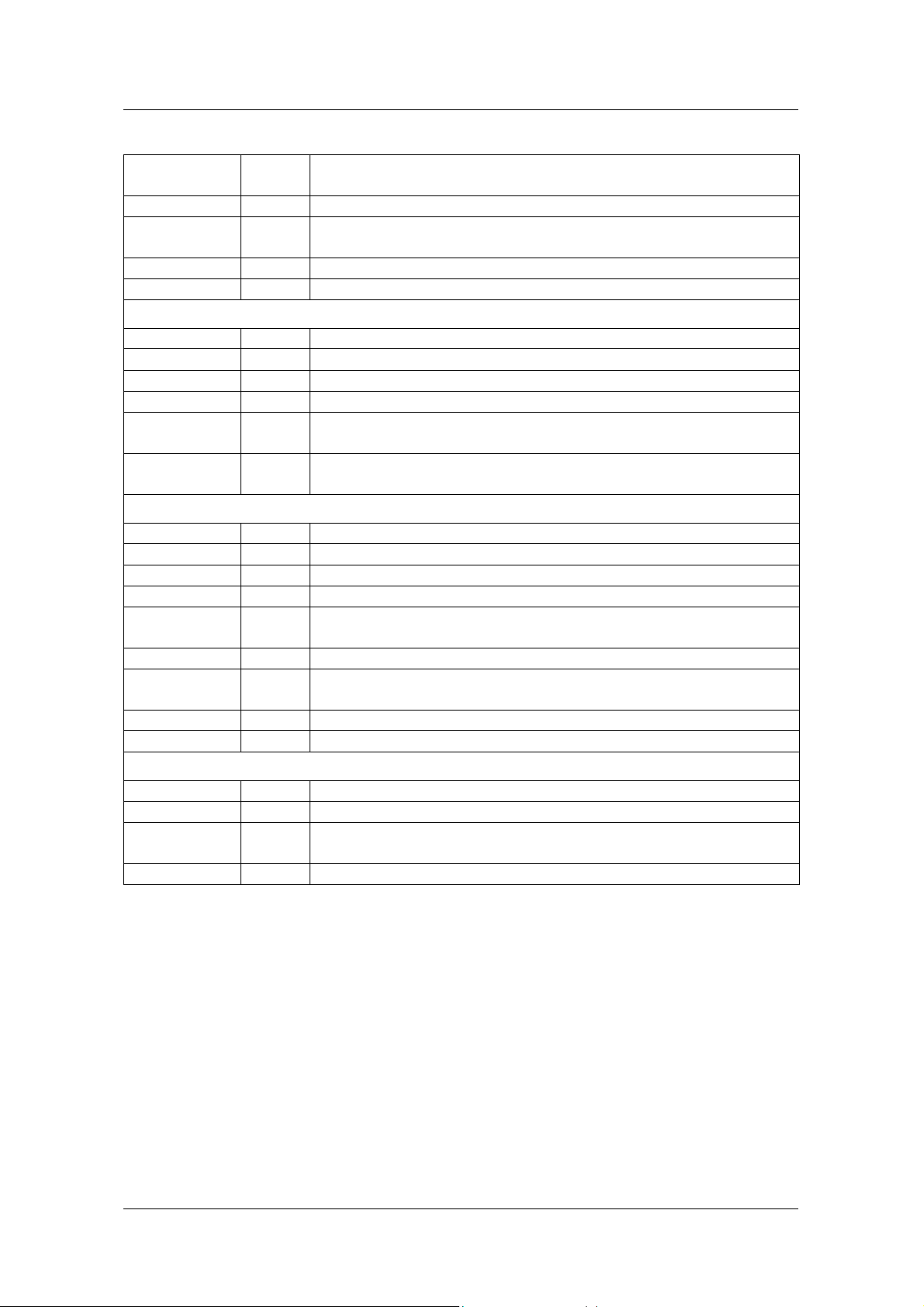

PIN DESCRIPTION

DACVREF

AOUTL

DACVBB

VSS

97

98

99

DACVSSA

DACVDDA

DACVHALF

AOUTR

DACVSSD

DACVDDD

ADCAIN

ADCVSSA

ADCVBB

ADCVDDA

ADCREFN

ADCREFP

ADCVSSD

ADCVDDD

PLLVDDA

PLLVSSA

PLLVBB

FILTER

CPUXO

CPUXI

VDD

VSS

BCLK

VDD

VSS

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26272829303132333435363738394041424344454647484950

NC

VSSNCVSS

95

96

NC

NC

NC

VSS

VDDIO

VDD

89

90

91

92

93

94

VSSIO

86

87

88

TL7231MD

TOP VIEW

DACMUTE#

DACDEEM

84

85

DACSDATA

DACLRCK

DACBCK

81

82

83

DACMSCK

VSS

79

80

VSS

78

VSS

77

VSS

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

TL7231MD

VSS

VSS

VSS

VSS

VDD

NC

NC

NC

VDD

VSS

VDDIO

VSSIO

CLKXRM

DXRM

REQSTRM

VDD

HALE

HSEL#

HRD#

HWR#

HD7

HD6

HD5

HD4

HD3

VDDIO

VSSIO

RESET

PWRDN

WAKEUP

VSS

VSS

VSS

VSS

VSS

VSS

VDD

VSS

VDDIO

NCNCNC

VSSIO

NC

VSS

VSS

VSS

HD0

HD1

HD2

Figure 2. 100-pin Thin Quad Flat Package (TQFP)

SAMSUNG Electronics CO. 3/37

TL7231MD

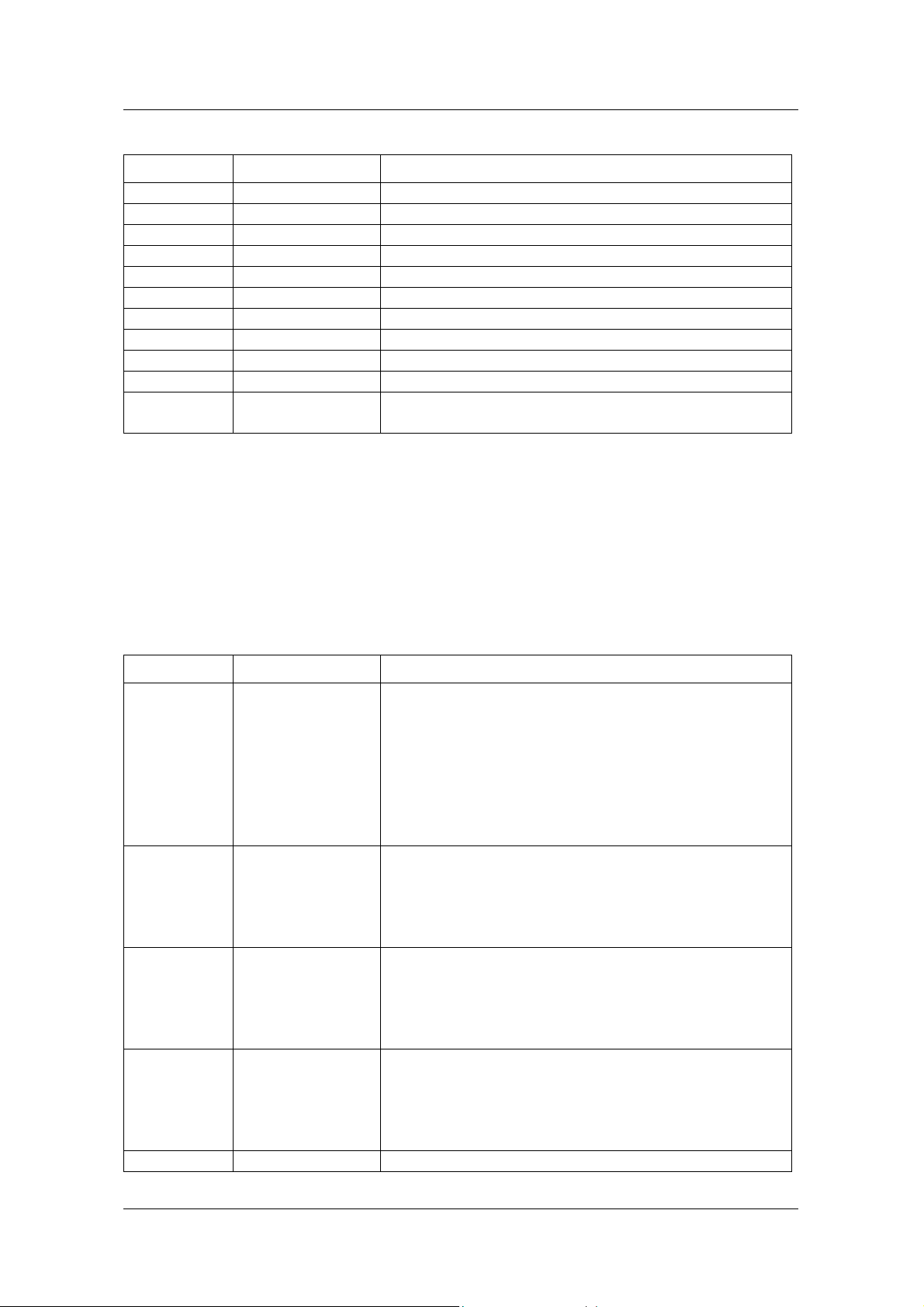

PIN

1 DACVSSA 26 VDDIO 51 HD3 76 VSS

2 DACVDDA 27 VSSIO 52 HD4 77 VSS

3 DACVHALF 28 RESET 53 HD5 78 VSS

4 AOUTR 29 WAKEUP 54 HD6 79 VSS

5 DACVSSD 30 PWRDN 55 HD7 80 DACMSCK

6 DACVDDD 31 VSS 56 HWR# 81 DACBCK

7 ADCAIN 32 VSS 57 HRD# 82 DACLRCK

8 ADCVSSA 33 VSS 58 HSEL# 83 DACSDATA

9 ADCVBB 34 VSS 59 HALE 84 DACDEEM

10 ADCVDDA 35 VSS 60 VDD 85 DACMUTE#

11 ADCREFN 36 VSS 61 REQSTRM 86 VSSIO

12 ADCREFP 37 VDD 62 DXRM 87 VDDIO

13 ADCVSSD 38 VSS 63 CLKXRM 88 VSS

14 ADCVDDD 39 VDDIO 64 VSSIO 89 VDD

15 PLLVDDA 40 VSSIO 65 VDDIO 90 NC

16 PLLVSSA 41 NC 66 VSS 91 NC

17 PLLVBB 42 NC 67 VDD 92 NC

18 FILTER 43 NC 68 NC 93 VSS

19 CPUXO 44 NC 69 NC 94 NC

20 CPUXI 45 VSS 70 NC 95 VSS

21 VDD 46 VSS 71 VDD 96 NC

22 VSS 47 VSS 72 VSS 97 VSS

23 BCLK 48 HD0 73 VSS 98 DACVBB

24 VDD 49 HD1 74 VSS 99 AOUTL

25 VSS 50 HD2 75 VSS 100 DACVREF

NAME PIN

Table 1. Pin Locations with Pin Names

NAME PIN NAME PIN

NAME

4/37 SAMSUNG Electronics Co.

NAME PIN NAME PIN NAME PIN

ADCAIN 7 DACVSSA 1 NC 92 VSS 34

ADCREFN 11 DACVSSD 5 NC 94 VSS 35

ADCREFP 12 DXRM 62 NC 96 VSS 36

ADCVBB 9 FILTER 18 PLLVBB 17 VSS 38

ADCVDDA 10 HD0 48 PLLVDDA 15 VSS 45

ADCVDDD 14 HD1 49 PLLVSSA 16 VSS 46

ADCVSSA 8 HD2 50 PWRDN 30 VSS 47

ADCVSSD 13 HD3 51 REQSTRM 61 VSS 66

AOUTL 99 HD4 52 RESET 28 VSS 72

AOUTR 4 HD5 53 VDD 21 VSS 73

BCLK 23 HD6 54 VDD 24 VSS 74

CLKXRM 63 HD7 55 VDD 37 VSS 75

CPUXI 20 HALE 59 VDD 60 VSS 76

CPUXO 19 HRD# 57 VDD 67 VSS 77

DACBCK 81 HSEL# 58 VDD 71 VSS 78

DACDEEM 84 HWR# 56 VDD 89 VSS 79

DACLRCK 82 NC 41 VDDIO 26 VSS 88

DACMSCK 80 NC 42 VDDIO 39 VSS 93

DACMUTE# 85 NC 43 VDDIO 65 VSS 95

DACSDATA 83 NC 44 VDDIO 87 VSS 97

DACVBB 98 NC 68 VSS 22 VSSIO 27

DACVDDA 2 NC 69 VSS 25 VSSIO 40

DACVDDD 6 NC 70 VSS 31 VSSIO 64

DACVHALF 3 NC 90 VSS 32 VSSIO 86

DACVREF 100 NC 91 VSS 33 WAKEUP 29

Table 2. Pin Functions with Location

TL7231MD

NAME PIN

SAMSUNG Electronics CO. 5/37

TL7231MD

Signal Name Type Description

CPUXI I CPU Clock In. 16.9344MHz crystal clock input.

CPUXO O CPU Clock Out. 16.9344MHz crystal clock output.

FILTER O

BCLK O Processor Clock Output.

RESET I Chip Reset. Reset input to the chip. Internal pull down.

WAKEUP I

PWRDN I

Table 3. Pin Descriptions

Internal PLL Interface

Charge Pump Out. External capacitor should be connected

between this pin and analog ground.

Clock Signal

Reset & Power Down Control

Wake Up. When high, chip is waked up from SLEEP state. This pin

should be remained active at least 1 clock cycle and inactive before

the host issues next SLEEP command. Internal pull down.

Power Down. This pin controls PWRDOWN state. When high, chip

goes to very low power consumption state. After deactivation,

WAKEUP pin should be remained low at least 150µs. Internal pull

down.

(Restriction: This pin should be active ONLY in SLEEP state.

Otherwise, Chip reset should be activated.)

MCU Serial Interface

CLKXRM I Serial Clock. MCU serial interface clock.

Serial Data. When MCU transmits data, this data pin is sampled at

negative edge of CLKXRM. When MCU receives data, Data is valid

DXRM I/O

REQSTRM O

HSEL# I HIP Enable. When Low, HIP is selected.

HALE I

HRD# I

HWR# I

HD[7:0] I/O HIP Address/Data Bus. Multiplexed address lines and data lines.

ADCAIN I

ADCREFP I

ADCREFN I ADC Internal Reference Bottom Bias. Connect this pin to ground.

from negative edge of CLKXRM to next negative edge of CLKXRM.

DXRM should be sampled at positive edge of CLKXRM. After reset,

TL7231MD is set to transmit the most significant bit first.

Request Bit Stream Data. MCU must check this pin to determine to

continue receiving or transmitting. MCU should transmit or receive

data during this signal active.

MCU HIP(Host Interface Port) Interface

HIP Address Latch Enable. When High, HD[7:0] should have HIP

address, which is sampled at negative edge of this signal.

HIP Read Enable. When low, data is loaded to HD[7:0], which

should be sampled at positive edge of this signal.

HIP Write Enable. Data at HD[7:0] is sampled at positive edge of

this signal.

Internal ADC Interface

ADC Analog Input. Analog input spans between ADCREFP and

ADCREFN.

ADC Internal Reference Top Bias. Connect this pin to voltage

between ADCVDDA and 2.0V.

6/37 SAMSUNG Electronics Co.

TL7231MD

ADCVDDA PWR

ADC Supply Voltage for Analog Circuit. Connect this pin to the

+3.0V supply voltage.

ADCVSSA GND ADC Ground for Analog Circuit. Connect this pin to ground.

ADCVDDD PWR

ADC Supply Voltage for Digital Circuit. Connect this pin to the

+3.0V supply voltage.

ADCVSSD GND ADC Ground for Digital Circuit. Connect this pin to ground.

ADCVBB GND ADC Analog/Digital Bulk Bias. Connect this pin to ground.

External DAC Interface

DACMSCK O DAC Master Clock. 384×Fs clock.

DACBCK O DAC Bit Clock. 32×Fs clock.

DACLRCK O DAC Sample Rate Clock. Fs clock.

DACSDATA O DAC Serial Data. Serial data.

DACDEEM O

DACMUTE# O

DAC Deemphasis. When deemphasis is on, this signal is high. It

can be set/clear through HIP commands.

DAC Mute. Analog output mute. When external DAC is set to mute

on, this signal is low. It can be set/clear through HIP commands.

Internal DAC Interface

AOUTL O Analog Output for Left-Channel.

AOUTR O Analog Output for Right-Channel.

DACVHALF I/O DAC Reference Voltage Output for Bypass.

DACVREF I/O DAC Reference Voltage Output for Bypass.

DACVDDA PWR

DAC Supply Voltage for Analog Circuit. Connect this pin to the

+3.0V supply voltage.

DACVSSA GND DAC Ground for Analog Circuit. Connect this pin to ground.

DACVDDD PWR

DAC Supply Voltage for Digital Circuit. Connect this pin to the

+3.0V supply voltage.

DACVSSD GND DAC Ground for Digital Circuit. Connect this pin to ground.

DACVBB GND DAC Pad Bulk Bias. Connect this pin to ground.

Power/Ground Pins

VDD PWR Supply Voltage. Connect this pin to the +3.0V supply voltage.

VSS GND Circuit Ground. Connect this pin to ground.

VDDIO PWR

Supply Voltage for I/O Buffers. Connect this pin to the +3.0V

supply voltage.

VSSIO GND Circuit Ground for I/O Buffers. Connect this pin to ground.

SAMSUNG Electronics CO. 7/37

TL7231MD

FUNCTIONAL DESCRIPTION

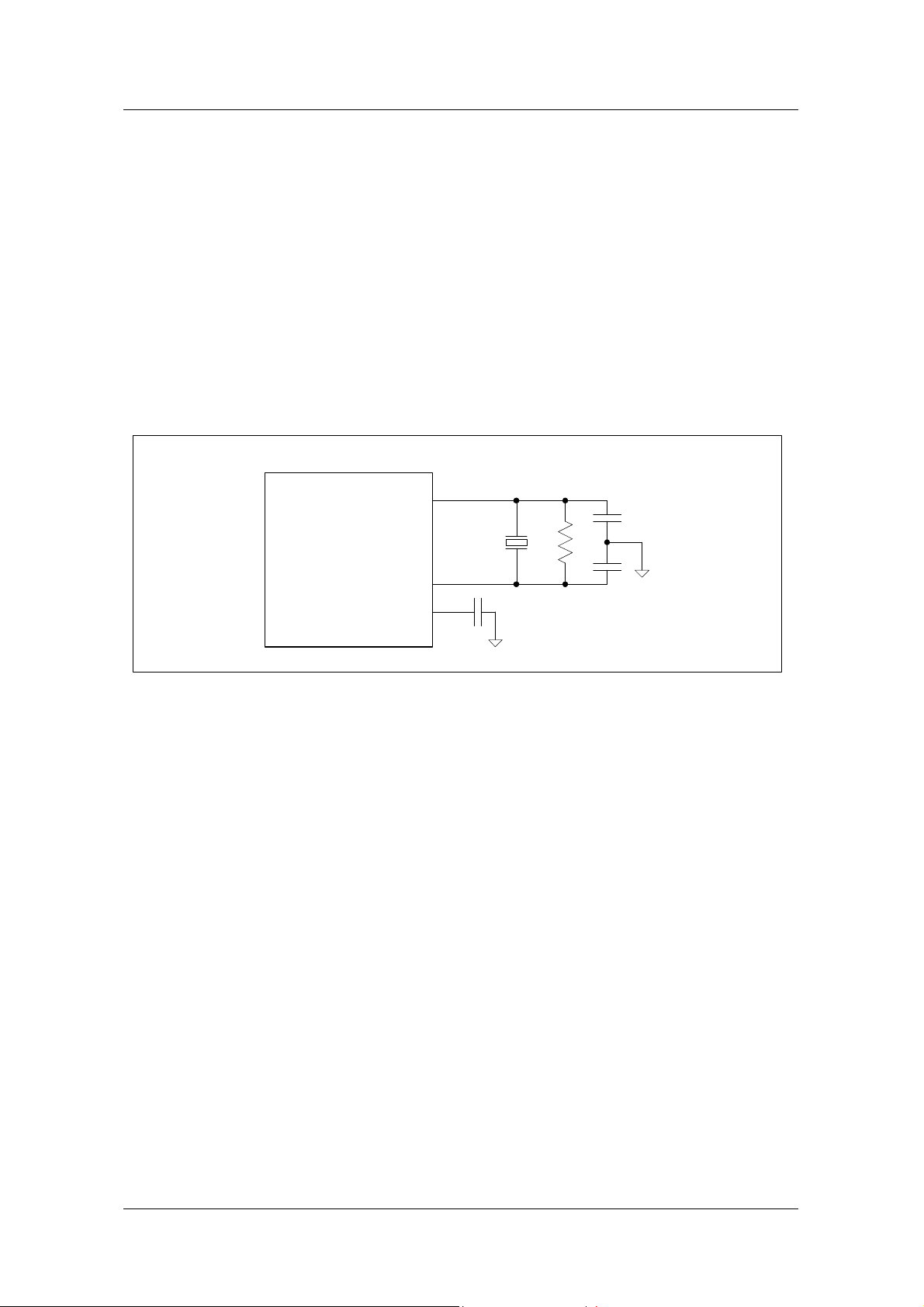

RESET/CLOCK UNIT

TL7231MD is driven by a single clock at the frequency of 16.9344MHz. The clock is derived

from an external source or from an industry standard crystal oscillator, generating input

frequency of 16.9344MHz. The clock generation unit has a PLL, and all the internal clock

signals including internal DAC/ADC clocks are generated with the input clock.

When TL7231MD is in power-on-reset, RESET signal should be active at least 150µs till the

internal PLL is stabilized. To reset TL7231MD during normal operation, RESET signal should be

active at least 16 cycles.

TL7231MD

CPUXI

30p

16.9344MHz

CPUXO

1M

30p

FILTER

820p

Figure 3. Clock Circuit

DSP CORE LOGIC

The core logic of TL7231MD is a 32-bit floating-point DSP processor. The independent multiplier

and accumulator of TL7231MD can achieve high performance. Internal registers are 40-bit

registers that store values with a 32-bit mantissa and an 8-bit exponent. These registers can

serve as both the source and destination for any arithmetic operation. Since all the data

input/output transactions are managed by DMA, there is no computational overhead due to data

transactions.

SERIAL INTERFACE

The serial interface of TL7231MD is used to receive MPEG bit stream data or transmit/receive

voice data. It is configured to transfer 8 bits of data per word. It can be configured to be LSBfirst or MSB first transfer mode. LSB-first means that the data bits are transmitted and received

least-significant bit (LSB) first. MSB-first means that the data bits are transmitted and received

most-significant bit (MSB) first. The clock for the serial interface should be generated externally.

The related signals are CLKXRM, DXRM, and REQSTRM. REQSTRM is used for

synchronization between microcontroller and TL7231MD, and data is transferred during

REQSTRM active.

8/37 SAMSUNG Electronics Co.

When microcontroller tries to send data to TL7231MD, it should check whether REQSTRM is

active or not. If the signal is active, microcontroller sets its serial interface to transmit mode and

send serial clock and serial data. After transmitting each byte, microcontroller should check

REQSTRM to decide whether next byte is to be transmitted or not.

When microcontroller tries to receive data from TL7231MD, it should check whether REQSTRM

is active or not. If the signal is active, microcontroller sets its serial interface to receive mode

and send serial clock and receive serial data from TL7231MD. After receiving each byte,

microcontroller should check REQSTRM to decide whether TL7231MD will transmit next byte or

not.

TL7231MD

HOST INTERFACE PORT (HIP)

Host interface port is used to send commands to and receive status information from

TL7231MD. HIP of TL7231MD is a parallel I/O port that makes a connection to a host processor

easily. Through the HIP, TL7231MD can be used as a memory-mapped peripheral to a host

processor. The HIP can be thought of as an area of dual-port memory that allows

communication between the computational core of the TL7231MD and host. The HIP is

completely asynchronous. The host processor can write data into the HIP while the TL7231MD

is operating at full speed. HIP transfers are managed using interrupt scheme.

HIP contains 21 registers. Four of them are data-in registers (HDI0/HDI1/HDI2/HDI3) and one of

them is a status register (HSR4). The remaining 16 registers are data-out registers

(HDO0/…/HDO15). Data written into HDIs by host are read by TL7231MD. Through these

registers host can give necessary commands to TL7231MD. A command is written into a HDI0,

and the required parameters of the command are written into the HDI1/HDI2/HDI3. The status

register (HSR4) keeps the information whether data written into the data-in registers are read by

TL7231MD. The status register is managed automatically by TL7231MD and can be read by

host. TL7231MD starts HIP command processing when HDI0 register is written. So if any

command requires parameters, user should write parameters first, and then write command.

Serial ID number can be used to check whether given command has been accepted or not.

TL7231MD can receive the serial ID value through HDO0 when TL7231MD has accepted the

given command. Thus when commands are given to TL7231MD with different serial ID numbers,

it can be examined which command is being processed. Serial ID number itself hasn’t any

special meaning. If this feature is not needed, it is not required to send ID values with

commands. Then the value of HDO0 is undetermined. There is an exception for the ID number

convention. If you use HIP command 0Dh(Revision Code), TL7231MD returns the TL7231MD

revision number, not the ID number.

HDOs are written by TL7231MD and can be read by host. All HIP registers should be memorymapped into the memory space of the host processor. The address space of those registers is

shown in Table 4. The usable commands are listed in Table 6. The contents reported by HDOs

are shown from Figure 4 to Figure 16.

Table 4. Address of Host Interface Port Registers

SAMSUNG Electronics CO. 9/37

TL7231MD

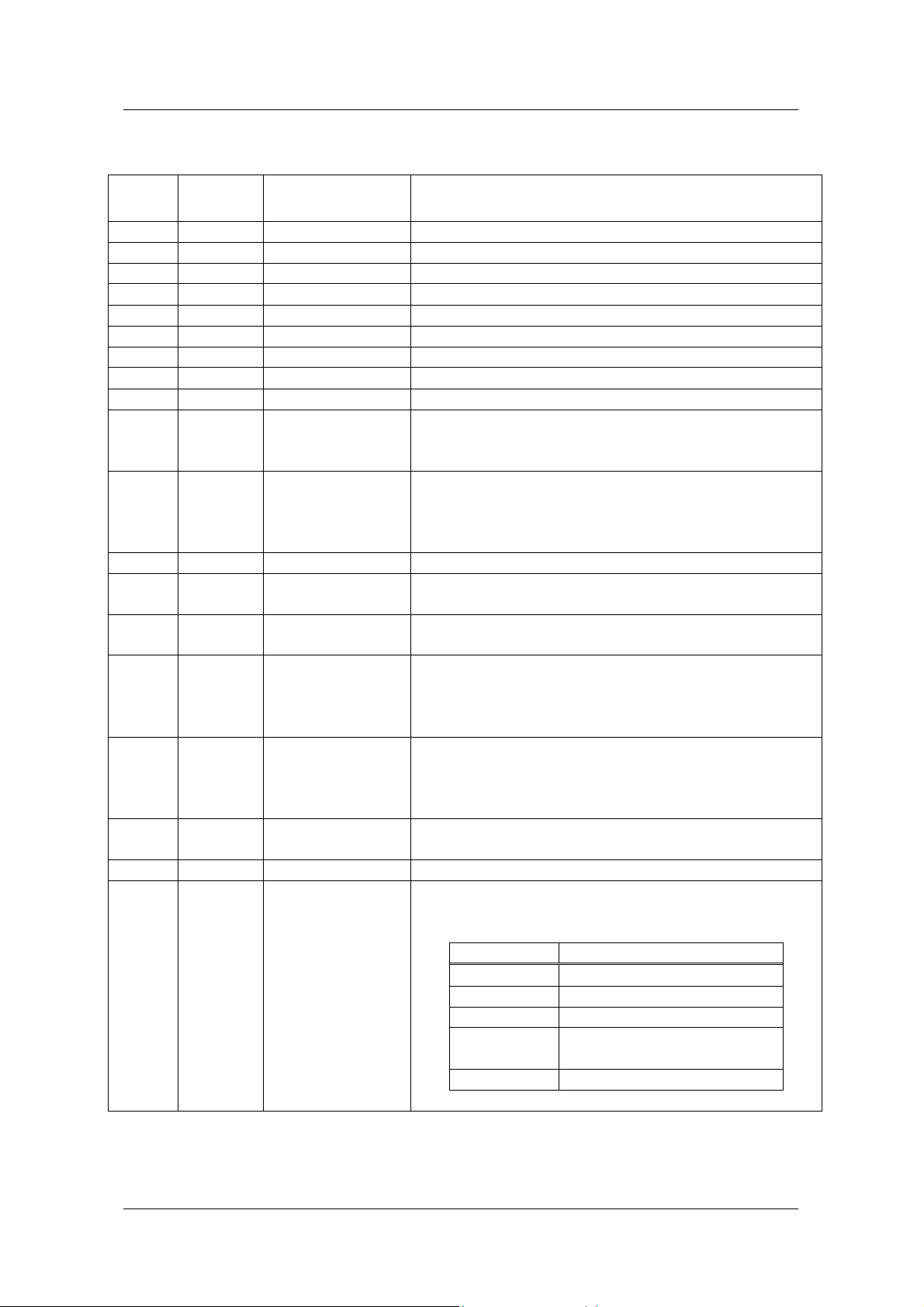

ADDRESS REGISTERS DESCRIPTION

0h HDI0 Command

1h HDI1 Serial ID Number

2h ~ 3h HDI2/HDI3 Parameters if needed

4h HSR4 Status Register (Fig. 4)

10h HDO0 Command Serial ID Number (Fig. 5)

11h HDO1 Decoder State (Fig. 6)

12h HDO2 IO Status (Fig.7)

13h HDO3 IO Status (Fig. 8)

14h HDO4 Volume (Fig. 9)

15h HDO5 Serial Interface Mode (Fig. 10)

16h ~ 1Fh HDO6 ~ HDO15 The information provided by these registers depends on

The information provided by HDO6 to HDO15 depends on the mode setting of TL7231MD.

Refer to Table 5. The mode can be set by using HIP command 19h(Report Format). For this

command, refer to Table 6.

Table 5. The contents of HDO6 ~ HDO15 according to mode setting

ADDRESS REGISTERS DESCRIPTION

16h HDO6 Mode0: 00h

17h HDO7 Mode0: 00h

18h HDO8 Mode0: 00h

19h HDO9 Mode0: 00h

1Ah HDO10 Mode0: 00h

the mode setting of TL7231MD. (Refer to Table 5)

Mode1: Tone Control Status. When tone control is

enabled, 1 is reported. Otherwise, 0 is reported.

Mode2: MP3 Frame Count (Fig. 11)

Mode3: Voice Data Code Count (Fig. 11)

Mode4: Equalizer Control Status. When equalizer control

is enabled, 1 is reported. Otherwise, 0 is

reported.

Mode1: Tone Control - Prescaling Information

Mode2: MP3 Frame Count (Fig. 11)

Mode3: Voice Data Code Count (Fig. 11)

Mode4: EQ Control – Prescaling Information

Mode1: Tone Control – Bass Cutoff Frequency

Mode2: MP3 Frame Count (Fig. 11)

Mode3: Voice Data Code Count (Fig. 11)

Mode4: EQ Control – Band1 Gain

Mode1: Tone Control – Bass Gain

Mode2: MP3 Frame Count (Fig. 11)

Mode3: Voice Data Code Count (Fig. 11)

Mode4: EQ Control –Band2 Gain

10/37 SAMSUNG Electronics Co.

Mode1: Tone Control – Treble Cutoff Frequency

Mode2: The most recently synchronized frame header of

MP3 bit stream. (Fig. 12)

Mode3: 00h

Mode4: EQ Control – Band3 Gain

1Bh HDO11 Mode0: 00h

Mode1: Tone Control – Treble Gain

Mode2: The most recently synchronized frame header of

MP3 bit stream. (Fig. 13)

Mode3: 00h

Mode4: EQ Control – Band4 Gain

1Ch HDO12 Mode0: 00h

Mode1: 00h

Mode2: The most recently synchronized frame header of

MP3 bit stream. (Fig. 14)

Mode3: 00h

Mode4: EQ Control – Band5 Gain

1Dh HDO13 Mode0: 00h

Mode1: 00h

Mode2: Bass Boost Information (Fig. 15)

Mode3: 00h

Mode4: EQ Control – Band6 Gain

1Eh HDO14 Mode0: 00h

Mode1: 00h

Mode2: DAC Output Valid (Fig. 16)

Mode3: 00h

Mode4: 00h

1Fh HDO15 Mode0: 00h

Mode1: 00h

Mode2: CRC Error Count

Mode3: 00h

Mode4: 00h

TL7231MD

SAMSUNG Electronics CO. 11/37

TL7231MD

COMM

AND

00h None Stop Stop execution and go into WAIT state.

01h None MP3 Decoding Execute MP3 decoding.

04h None Voice Encoding Execute voice encoding (16Kbps).

05h None Voice Decoding Execute voice decoding (16Kbps).

06h None Voice Encoding Execute voice encoding (24Kbps).

07h None Voice Decoding Execute voice decoding (24Kbps).

08h None Voice Encoding Execute voice encoding (32Kbps).

09h None Voice Decoding Execute voice decoding (32Kbps).

0Dh None Revision Code Report the TL7231MD revision number in HDO0.

0Fh None Sleep Go into SLEEP state. This command should be used in

10h None Mute ON When using internal DAC, The output voltage level of

11h None Mute OFF Mute is disabled.

12h None Internal ADC Use Internal ADC. External ADC interfaces are disabled.

14h None Internal DAC Use internal DAC. After reset, it is set to use internal

15h None External DAC Use external DAC. Internal DAC is disabled. The

16h 1byte External DAC

17h None MSB First Serial Interface MSB-first mode. This is the default mode

18h None LSB First Serial Interface LSB-first mode

19h 1byte Report Format

PARAME

TER

Format

Table 6. Host Interface Port Commands

MEANING DESCRIPTION

WAIT state. If this command is used during algorithm

execution, TL7231MD becomes unstable.

AOUTL/AOUTR is GND. When using external DAC,

DACMUTE# becomes active. After reset, TL7231MD is

set to be mute on.

After reset, it is the default value.

DAC.

waveform of I/O pin related to external DAC is controlled

according to External DAC Format or External DAC

Format 2.

Set the waveform of I/O pin related to external DAC. The

parameter value of External DAC Format command

should be as follows: {0, 0, 0, 0, 0, I2S, PL, PB}. For the

meaning of I2S, PL, and PB, refer to Figure 8.

after reset.

The reported contents of HDO6 to HDO15 are changed

according to parameter of this command.

Parameter Reporting Contents

0 all 00h

1 Tone Control Information

2 MP3 Decoding Information

3 Voice Encoding/Decoding

Information

4 Equalizer Control Information

12/37 SAMSUNG Electronics Co.

Loading...

Loading...