Samsung SGH-D730 Service Manual

MITs TELEPHONE

SGH-D730

MITs TELEPHONE

CONTENTS

1. Specification

2. Flow Chart of Troubleshooting

3. Exploded Views and Parts List

4. Electrical Parts List

5. PCB Diagrams

6. Block Diagrams

1. SGH-D730 Specification

1-1. GSM General Specification

GSM900

Phase 1

Freq. Band[MHz]

Uplink/Downlink

ARFCN range 1~124

Tx/Rx spacing 45MHz 45MHz 95MHz 80MHz

Mod. Bit rate/

Bit Period

Time Slot

Period/Frame

Period

Modulation 0.3GMSK 0.3GMSK 0.3GMSK 0.3GMSK

MS Power 33dBm~13dBm 33dBm~5dBm 30dBm~0dBm 30dBm~0dBm

890~915

935~960

270.833kbps

3.692us

576.9us

4.615ms

EGSM 900

Phase 2

880~915

925~960

0~124 &

975~1023

270.833kbps

3.692us

576.9us

4.615ms

DCS1800

Phase 1

1710~1785

1805~1880

512~885 512~810

270.833kbps

3.692us

576.9us

4.615ms

PCS1900

1850~1910

1930~1990

270.833kbps

3.692us

576.9us

4.615ms

Power C l ass 5 p c l ~ 15pcl 5pcl ~ 19pcl 0pcl ~ 15pcl 0pcl ~ 15pcl

Sensitivity -102dBm -102dBm -100dBm -100dBm

TDMA Mux 8 8 8 8

Cell Radius 35Km 35Km 2Km -

2

1-

SGH-D730 Speclflcation

1-2. GSM Tx Power Class

TX Power

control level

5 33±2 dBm

6 31±2 dBm

7 29±2 dBm

8 27±2 dBm

9 25±2 dBm

10 23±2 dBm

11 21±2 dBm

12 19±2 dBm

13 17±2 dBm

14 15±2 dBm

15 13±2 dBm

16 11±3 dBm

17 9±3dBm

18 7±3 dBm

19 5±3 dBm

GSM900

TX Power

control level

0 30±3 dBm

1 28±3 dBm

2 26±3 dBm

3 24±3 dBm

4 22±3 dBm

5 20±3 dBm

6 18±3 dBm

7 16±3 dBm

8 14±3 dBm

9 12±4 dBm

10 10±4 dBm

11 8±4dBm

12 6±4 dBm

13 4±4 dBm

14 2±5 dBm

DCS1800

TX Power

control level

0 30±3 dBm

1 28±3 dBm

2 26±3 dBm

3 24±3 dBm

4 22±3 dBm

5 20±3 dBm

6 18±3 dBm

7 16±3 dBm

8 14±3 dBm

9 12±4 dBm

10 10±4 dBm

11 8±4dBm

12 6±4 dBm

13 4±4 dBm

14 2±5 dBm

PCS1900

15 0±5 dBm

2

1-

15 0±5 dBm

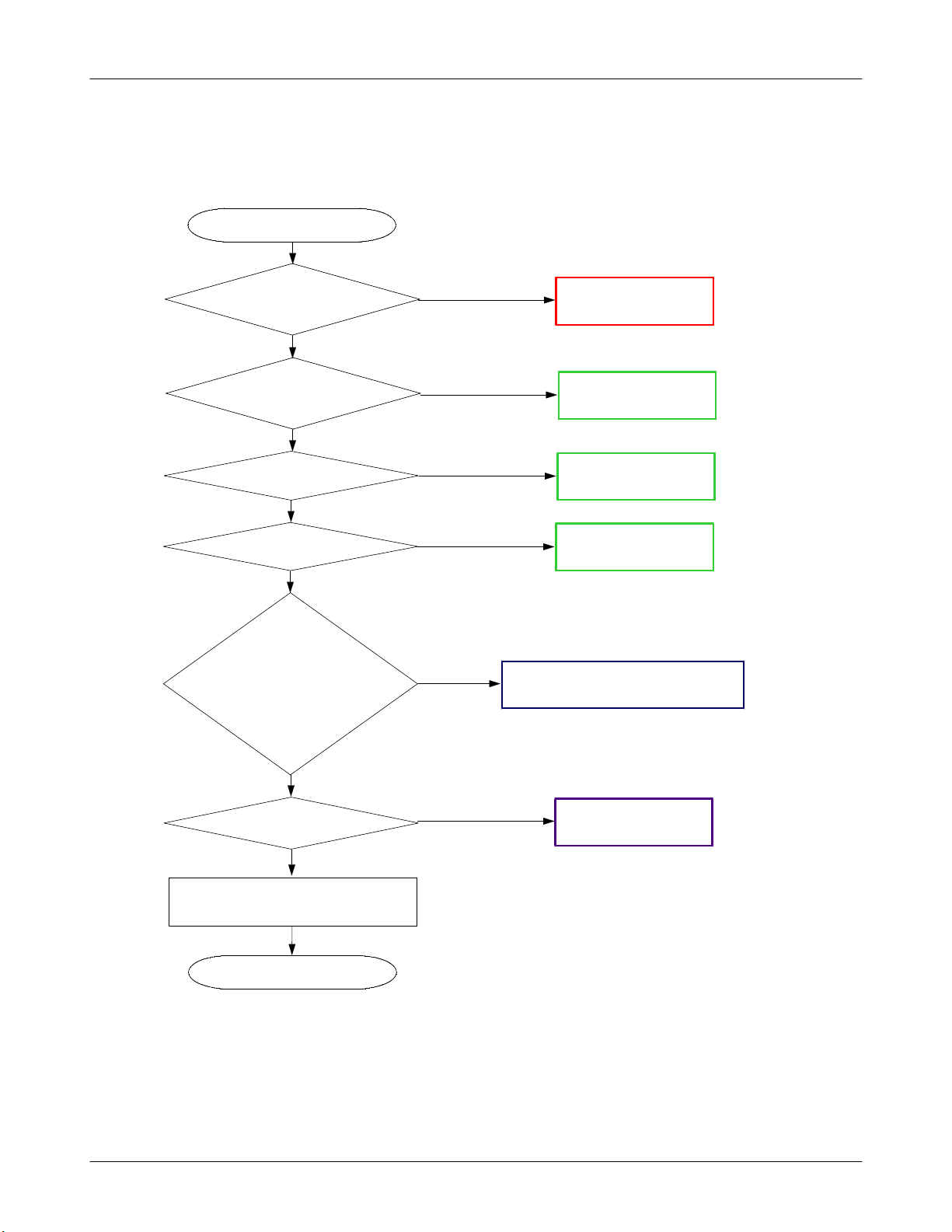

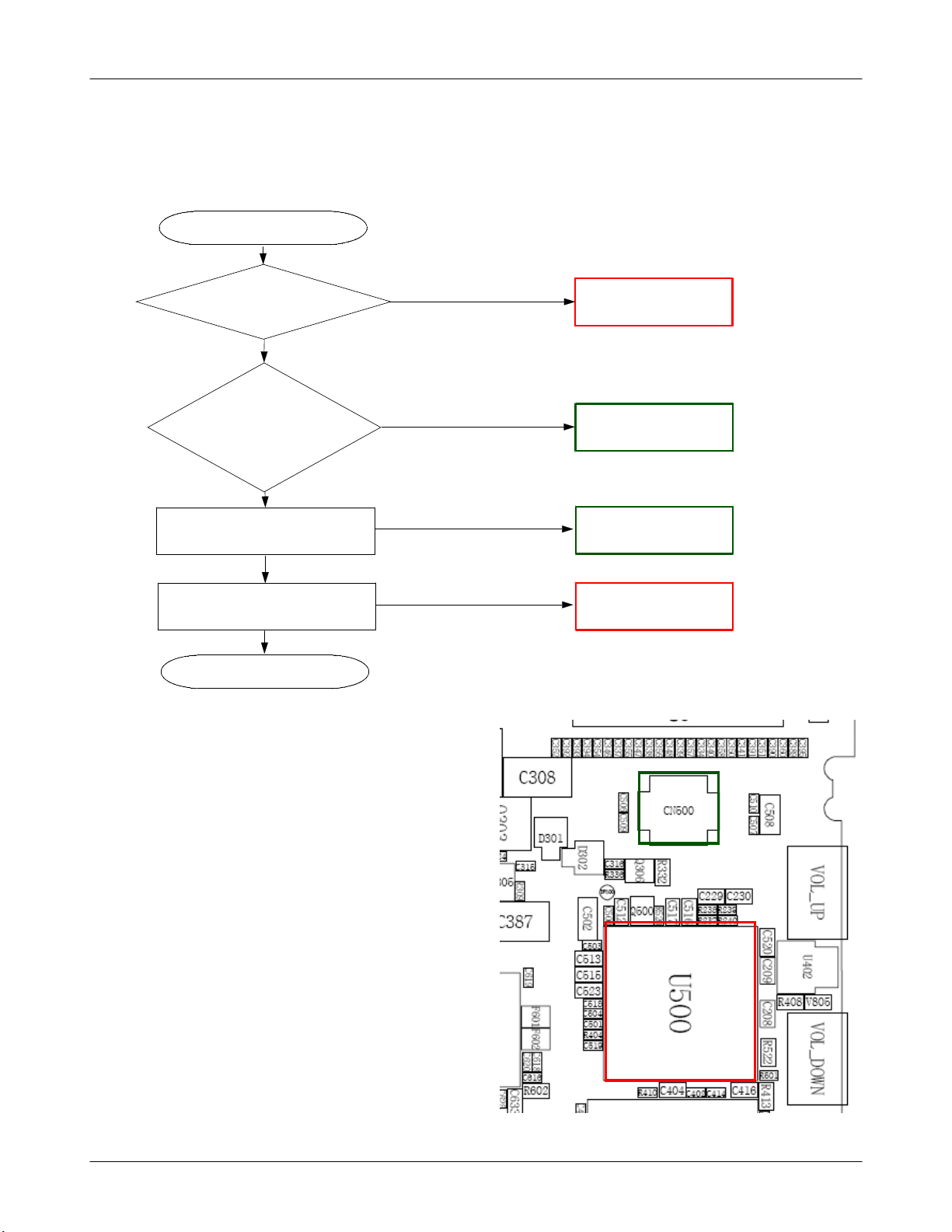

2. SGH-D730 Flow Chart of Troubleshooting and Circuit Diagrams

2-1.Baseband

2-1-1. Power ON

'Power On' does not work

Check the current

consumtion more than

100mA

YES

Check the Vbat(battery+O)

Voltagemorethan3.3V

YES

Check the pin

4 of Q303 is more

than 3.3V

YES

Check the pin

1 of Q303 is more

than 3.3V

YES

U100 pin A19

=3.0V

YES

U100 pin B14

=1.8V

NO

NO

NO

NO

NO

NO

Downloader again

Charge the Battery

①

Check CN304, C387

②

Check Q303, Q305 and D302

③

Check U308, U100 and C109

④

Check U308, U100 and C106

YES

U100 pin A15

=1.6V

NO

⑤

Check U304, U100 and C101

YES

Check the clock signal

at pin1 of OSC100

Freq=12MHz

NO

⑥

Check the clock generation circuit

YES

'Power On' does not work

END

2-1

SAMSUNG Proprietary-Contents may change without notice

This Document can not be used without Samsung's authorization

(OSC100)

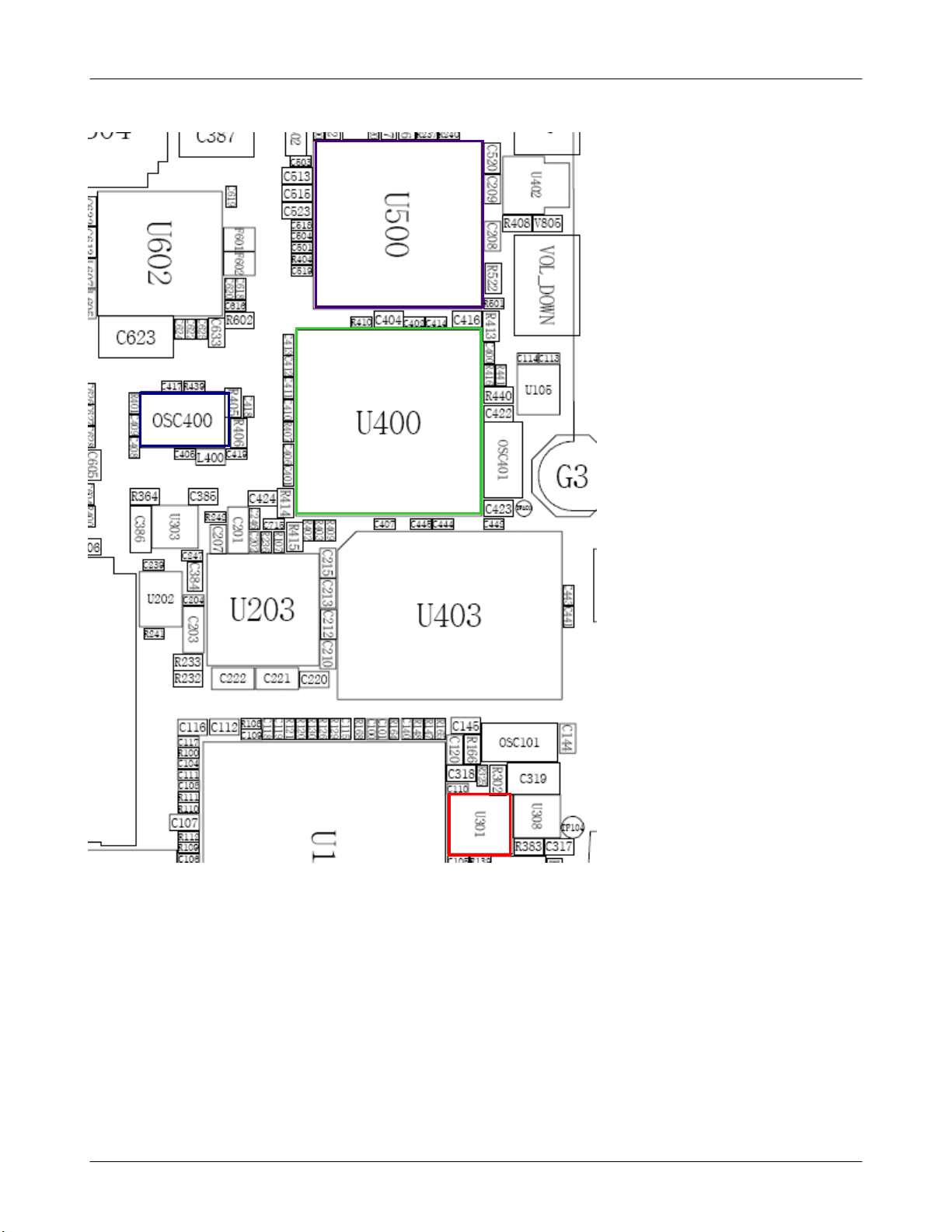

SGH-D730 Flow Chart of Troubleshooting and Circuit Diagrams

2-2

SAMSUNG Proprietary-Contents may change without notice

This Document can not be used without Samsung's authorization

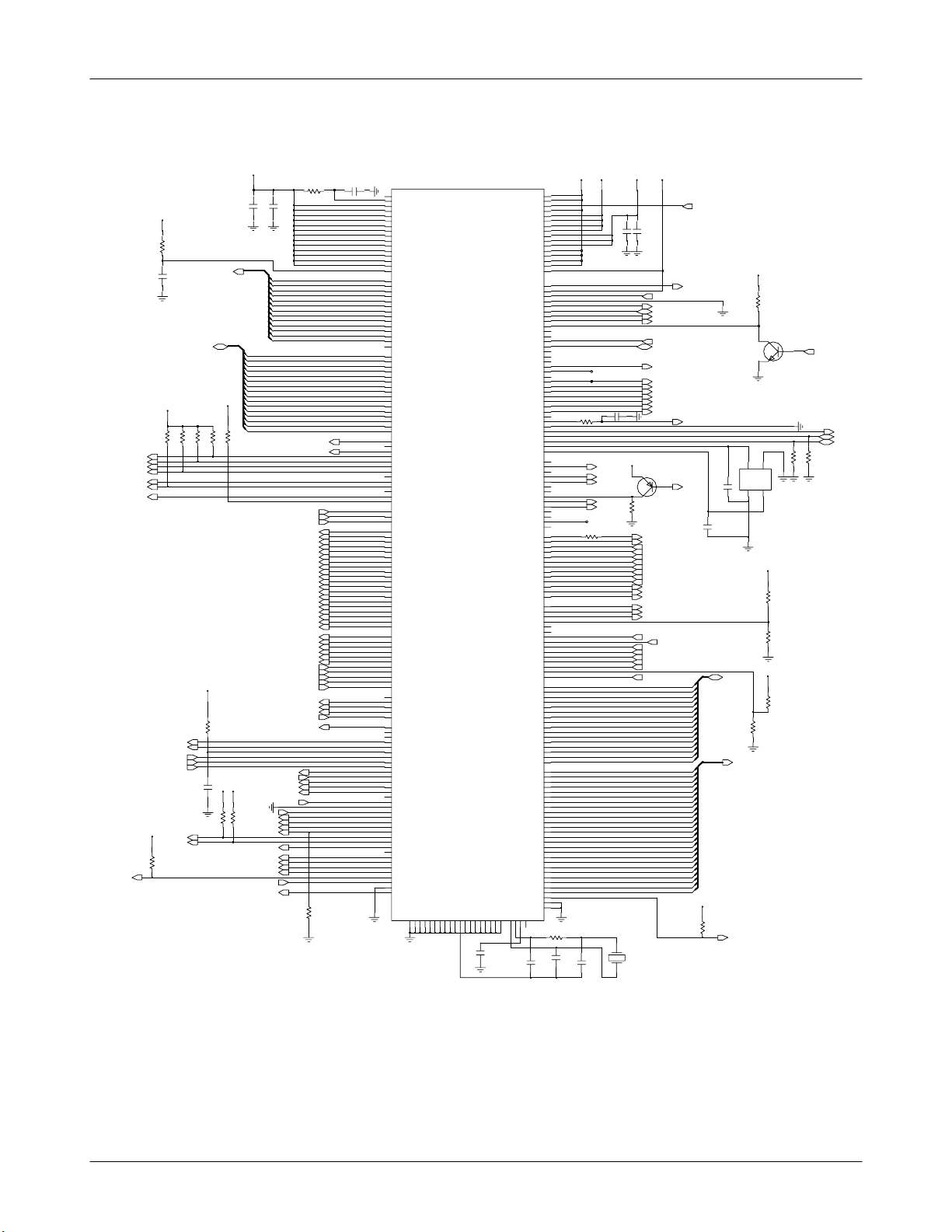

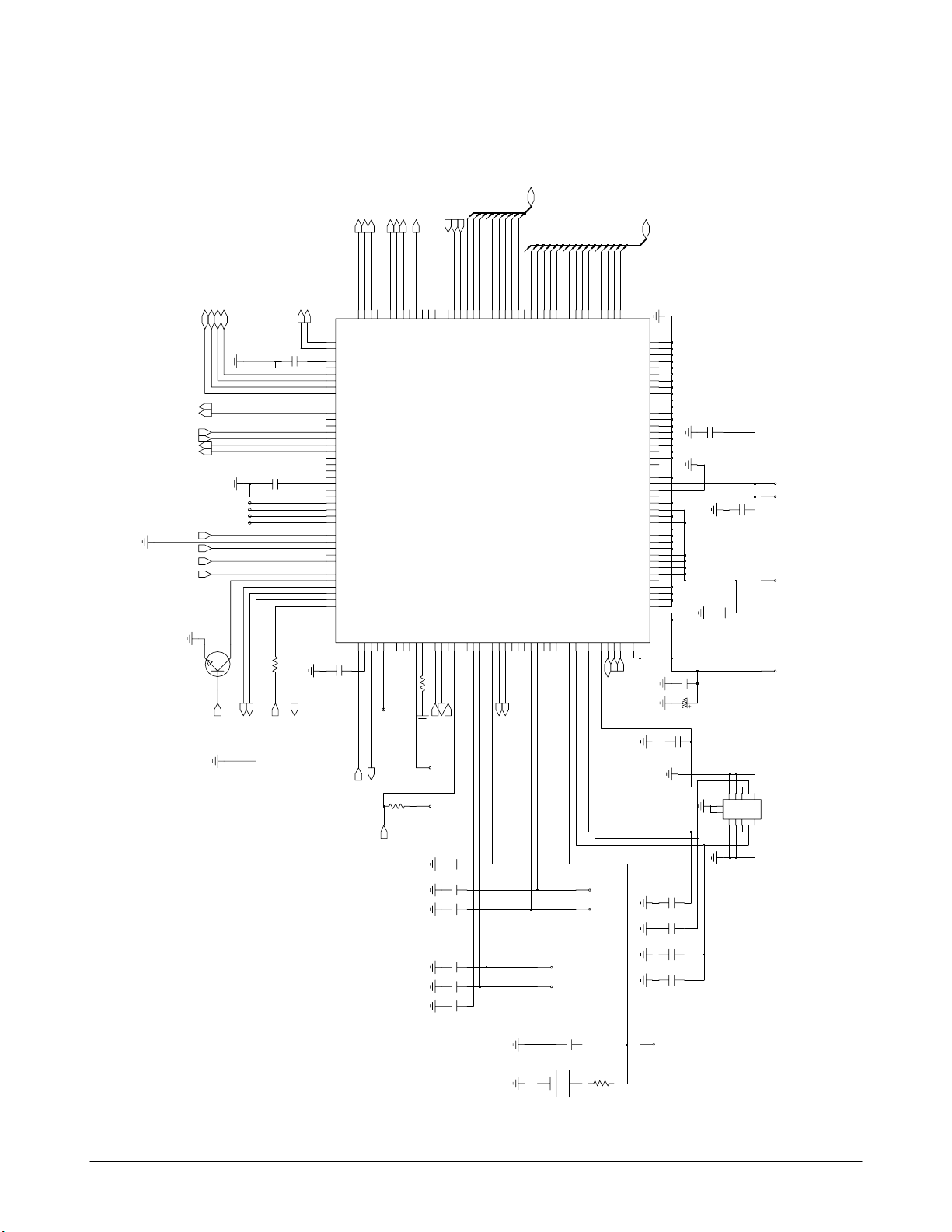

SGH-D730 Flow Chart of Troubleshooting and Circuit Diagrams

M

LCD_VDD_EN

nSCAS

nCS_SDRAM0

VDD_15D

C100

SD(0:15)

R112

VDD_30D

C101

SA(0:12)

SD(0)

SD(1)

SD(2)

SD(3)

SD(4)

SD(5)

SD(6)

SD(7)

SD(8)

SD(9)

VDD_30D

SD(10)

SD(11)

SD(12)

SD(13)

SD(14)

SD(15)

R108

R129

VDD_30D

VDD_30D

OMAP_TDI

OMAP_TDO

R148

R147

OMAP_TMS

OMAP_TCK

OMAP_TRST

OMAP_RTCK

BT_REQ

CAM_EN

OPEN_SENSE

PH_WAKEUP

BT_CTS

CLK32K_OMAP

VDD_15D

R100

C104

VDD_18D

R110

R111

R109

nSWE

LDQM

SCLK

UDQM

SCKE

CODEC_CSB

LCD_SCL

CAM_SCL

CAM_SDA

CODEC_SDO

C115

VDD_30D

OMAP_EMU0

OMAP_EMU1

R139

SA(0)

SA(1)

SA(2)

SA(3)

SA(4)

SA(5)

SA(6)

SA(7)

SA(8)

SA(9)

SA(10)

SA(11)

SA(12)

CODEC_SDI

CODEC_SCK

LCD_CS

PH_PWR_ON

VIB_EN

AP_AT_nDSR

BT_RXD

AP_AT_RXD

DEBUG_RXD

LCD_ENABLE

LCD_DOTCLK

LCD_VSYNC

LCD_R4

LCD_R3

LCD_R2

LCD_R1

LCD_R0

LCD_G5

LCD_G4

LCD_G3

LCD_G2

LCD_G1

LCD_G0

LCD_B4

LCD_B3

LCD_B2

LCD_B1

LCD_B0

LCD_HSYNC

KB_nSCAN(5)

KB_nSCAN(4)

KB_nSCAN(3)

KB_nSCAN(2)

KB_nSCAN(1)

KB_nSCAN(0)

KB_nIN(4)

KB_nIN(3)

KB_nIN(2)

KB_nIN(1)

KB_nIN(0)

IIS_SCLK

IIS_LRCK

IIS_SDO

IIS_SDI

AP_AT_nDTR

R164

SBANK_1

SBANK_0

R165

C140

L1

Y21

A15

Y20

Y9

M2

AA3

A3

A9

E2

B13

B20

J21

R20

W12

A11

A2

B2

B6

A1

G10

B9

G12

G11

G9

B12

B8

H10

H9

H11

D6

C6

C5

D7

D5

C7

C4

D8

C10

D14

D11

C13

C11

D13

D12

C12

C3

D4

B3

B4

H8

G8

C8

D9

C9

D10

C14

H12

J20

V14

R9

L14

B15

C15

B18

D15

C16

A17

G13

B17

C17

D16

D17

C18

B19

A20

H13

G14

C19

B21

D18

C20

G19

C21

E18

D19

D20

F18

E19

E20

H14

F19

G18

G20

G21

H15

H18

H20

T20

T19

V8

N15

U19

U20

T18

V20

U18

W21

V19

N14

P15

W16

W19

AA20

V18

Y19

AA19

V17

W18

Y18

V16

W17

Y17

AA17

P14

W14

V15

W15

Y15

R14

P13

R13

VPP

VDDA

VDD_1

VDD_2

VDD_3

VDD_4

VDD1

VDD2_1

VDD2_2

VDD2_3

VDD3_1

VDD3_2

VDD3_3

VDD3_4

VDD_RTC

CDD_DLL

SADD_0

SADD_1

SADD_2

SADD_3

SADD_4

SADD_5

SADD_6

SADD_7

SADD_8

SADD_9

SADD_10

SADD_11

SADD_12

SADD_13

SDATA_0

SDATA_1

SDATA_2

SDATA_3

SDATA_4

SDATA_5

SDATA_6

SDATA_7

SDATA_8

SDATA_9

SDATA_10

SDATA_11

SDATA_12

SDATA_13

SDATA_14

SDATA_15

SBANK_1

DQS_L

SBANK_0

NSCAS

NSWE

CS_SDRAM

NSDQML

SDCLKX

SDCLK

NSDQMU

DQS_H

SDCLK_EN

ARM_BOOT

RX1

RX2

RX3

LCD_AC

LCD_PCLK

LCD_VSYNC

LCD_PIX-EL_15

LCD_PIX-EL_14

LCD_PIX-EL_13

LCD_PIX-EL_12

LCD_PIX-EL_11

LCD_PIX-EL_10

LCD_PIX-EL_9

LCD_PIX-EL_8

LCD_PIX-EL_7

LCD_PIX-EL_6

LCD_PIX-EL_5

LCD_PIX-EL_4

LCD_PIX-EL_3

LCD_PIX-EL_2

LCD_PIX-EL_1

LCD_PIX-EL_0

LCD_HSYNC

KBC_5

KBC_4

KBC_3

KBC_2

KBC_1

KBC_0

KBR_4

KBR_3

KBR_2

KBR_1

KBR_0

MCBSP1_CLKS

MCBSP1_BCLK

MCBSP1_SYNC

MCBSP1_DOUT

MCBSP1_DIN

ARMIO_5

ARMIO_4

ARMIO_3

ARMIO_2

ARMIO_1

MPU_NRE-SET

SCL

SDA

WIRE_SDI

WIRE_SDO

WIRE_SCLK

Z_STATE1

Z_STATE2

Z_STATE3

BVLZ

NRE-SET_OUT

CONF

TDI

TDO

TMS

TCK

NTRST

NEMU0

NEMU1

RTCK

MCSI1_SYNC

MCSI1_BCLK

MCSI1_DOUT

MCSI1_DIN

UARTS_CLKREQ

UARTS_CLKIO

CTS1

CLK32K_IN

CLK32K_OUT

1

S

S

V

5

B

U100

0

5

1

6

7

2

8

3

4

1

1

1

7

1

8

1

1

1

1

9

2

3

4

S

S

S

S

S

S

V

V

V

7

3

6

1

1

B

A

B

1

5

6

S

S

S

S

S

S

S

S

S

S

S

S

S

S

S

S

S

S

S

S

S

S

S

S

S

S

S

S

V

V

V

V

V

V

V

V

V

V

V

V

V

V

1

1

1

2

0

3

7

1

1

2

3

0

1

0

2

2

2

1

2

2

2

A

A

K

Y

N

U

F

K

A

R

G

A

Y

A

A

W

A

C143

9

1

S

S

V

1

B

VDDSHV1_1

VDDSHV1_2

VDDSHV2

VDDSHV3

VDDSHV4_1

VDDSHV4_2

VDDSHV4_3

VDDSHV4_4

VDDSHV5_1

VDDSHV5_2

VDDSHV5_3

VDDSHV6

VDDSHV7

VDDSHV8

VDDSHV9

VDDSHV_RTC

WA-KEUP_INT

ON_NOFF

NRESPWRON

RE-SET_MODE

MMC_CLK

MMC_CMD

MCSI2_CLK

MCSI2_DIN

MCSI2_DOUT

MMC_DAT3

MMC_DAT2

MMC_DAT1

MMC_DAT0

MCSI2_SYNC

MCBSP2_DIN

MCBSP2_XSYNC

MCBSP2_CLKR

MCBSP2_CLKX

MCBSP2_RSYNC

MCBSP2_DOUT

0_STATE1

0_STATE2

0_STATE3

0_STATE4

0_STATE5

COM_MCLK_REQ

COM_MCLK_OUT

BDCLK2

USB_PUEN

USB_DP

USB_DM

OSC1_IN

OSC1_OUT

NFCS_3

NFCS_2

NFCS_1

NFCS_1B

NFCS_2B

NFBE_1

NFBE_0

CAM_EXCLK

CAM_LCLK

CAM_D_7

CAM_D_6

CAM_D_5

CAM_D_4

CAM_D_3

CAM_D_2

CAM_D_1

CAM_D_0

CAM_VS

CAM_HS

CAM_RSTZ

GPIO_62

GPIO_15

GPIO_14

GPIO_13

GPIO_12

GPIO_11

GPIO_9

GPIO_8

GPIO_7

GPIO_6

GPIO_4

GPIO_3

GPIO_2

GPIO_1

GPIO_0

FDATA_15

FDATA_14

FDATA_13

FDATA_12

FDATA_11

FDATA_10

FDATA_9

FDATA_8

FDATA_7

FDATA_6

FDATA_5

FDATA_4

FDATA_3

FDATA_2

FDATA_1

FDATA_0

FADD_25

FADD_24

FADD_23

FADD_22

FADD_21

FADD_20

FADD_19

FADD_18

FADD_17

FADD_16

FADD_15

FADD_14

FADD_13

FADD_12

FADD_11

FADD_10

FADD_9

FADD_8

FADD_7

FADD_6

FADD_5

FADD_4

FADD_3

FADD_2

FADD_1

T

R

U

D

N

E

O

I

E

T

_

_

L

V

K

K

I

2

R

2

F

3

3

_

E

C

C

S

O

S

S

E

D

O

O

L

R

3

5

3

1

j

1

e

1

v

A

A

NFADV

NSRAS

A19

E21

AA2

Y7

B14

B10

A7

A5

R1

H2

C2

AA11

Y16

L21

U21

V12

W13

Y12

R12

P12

V11

P11

Y10

AA9

W9

W11

W10

V10

R11

V9

P10

W7

V7

Y6

W6

AA5

AA15

Y14

W5

V6

M18

Y5

CTS2

R10

V5

Y4

W4

P9

R8

Y2

W3

V4

NFWP

W2

NFWE

W1

NFRP

U4

NFOE

N8

M4

M3

Y1

P3

M8

L3

L4

V2

FRDY

N3

FCLK

H19

J15

J18

J19

J14

K18

K19

K15

K14

L19

L18

L15

M19

M7

M20

N21

N19

N18

N20

W8

Y8

M15

P19

P20

P18

M14

R19

R18

V3

T4

U3

U1

P8

T3

T2

R4

R3

R2

P7

P4

P2

N7

N2

N4

E1

L7

K3

K4

L8

F2

J3

J4

J2

K7

H3

H4

K8

G2

G3

G4

F3

J7

E3

F4

D2

E4

C1

D3

J8

H7

1

NC1

2

NC2

C120

VDD_18D

VDD_18D

VDD_30DVDD_30D

VDD_SHV2

C102

C103

PH_ACTIVE

OHP_nRESET

MMC_SCLK

MMC_CMD

BT_nSHDN

PWR_HOLD

SW_RST_INT

MMC_DAT

TP103

TP104

R107

NFWE

NFOE

NFCS_3

nBAT_LOW

FLASH_EN

TP101

R168

R166

C144

C145

LCD_RESET

PDA_ACTIVE

BT_RTS

BT_TXD

AP_AT_nRTS

AP_AT_TXD

DEBUG_TXD

AP_AT_nCTS

33PFC715

VDD_30D

2

3

R122

1

1

0

1

C

S

2

O

Q102

1

CAM_MCLK

CAM_PCLK

Y7

Y6

Y5

Y4

Y3

Y2

Y1

Y0

CAM_VSYNC

CAM_HSYNC

CAM_RESET

KB_LED_EN

LCD_BL_EN

PH_OFF_nRDY

JACK_SENSE

USB_nINSERTED

MMC_nInserted

ON_SW_SENSE

PDA_WAKEUP

FLIP_SENSE

JACK_nSEND_END

LCD_SDI

CD_CLK_12M

BP_VF

FD(15)

FD(14)

FD(13)

FD(12)

FD(11)

FD(10)

FD(9)

FD(8)

FD(7)

FD(6)

FD(5)

FD(4)

FD(3)

FD(2)

FD(1)

FD(0)

FA(25)

FA(24)

FA(23)

FA(22)

FA(21)

FA(20)

FA(19)

FA(18)

FA(17)

FA(16)

FA(15)

FA(14)

FA(13)

FA(12)

FA(11)

FA(10)

FA(9)

FA(8)

FA(7)

FA(6)

FA(5)

FA(4)

FA(3)

FA(2)

FA(1)

VDD_18D

R144

VDD_30D

R123

3

Q101

1

OSC100

JIG_ON

PUEN

USB_DP

USB_D

R113

R114

2

2

1

GND1

HOT

GND2

C141

HOT

4

3

C142

VDD_30D

R120

R121

VDD_30D

FD(0:15)

R126

R130

FA(1:25)

nSRAS

2-3

SAMSUNG Proprietary-Contents may change without notice

This Document can not be used without Samsung's authorization

SGH-D730 Flow Chart of Troubleshooting and Circuit Diagrams

RTC_nALARM

VRTC

V_IN

VBAT

Q303

R324

4

5

6

EMD6

U305

3

2

1

9

0

3

R

3

G

3

2

V_IN

1256

4

S

Q305

C308

3

1

3

C315

D301

D302

C309

VDD_30D

1

2

1

2

C316

PWR_HOLD

JIG_ON

R336

1

Q306

3

2

PWR_ON_AP

R332

ON_SW_SENSE

VDD_15D

7

1

6

C

R613

1

2

3

4

5

VIN

AVIN

EN

NC

NC

U604

SW

PGND

MODE/SYNC

AGND

VOUT

GND

11

10

9

8

7

6

L600

8

1

6

C

2-4

SAMSUNG Proprietary-Contents may change without notice

This Document can not be used without Samsung's authorization

2-1-2. Initial

Initial Failure

Check the

pin 2 of

U301 is "High"

YES

Check the

pin F4 of

U400 is "High"

SGH-D730 Flow Chart of Troubleshooting and Circuit Diagrams

①

NO

Check U301

②

NO

Check the U400

YES

U400 pin B14

=3.0V

YES

U400 pin C16

=1.8V

YES

Check the clock

signals at

pin3 and pin5 of

OSC400

Freq=13MHz

YES

Check the pin C12

of U500 is "High"

YES

NO

NO

NO

NO

③

Check the U400

④

Check the U400

⑤

Check the clock generation circuit

(OSC400)

⑥

Check U500

Check and resolder LCD connector CN303

if there is solder bridge between the pins

YES

END

SAMSUNG Proprietary-Contents may change without notice

This Document can not be used without Samsung's authorization

2-5

SGH-D730 Flow Chart of Troubleshooting and Circuit Diagrams

⑥

②③④

⑤

①

2-6

SAMSUNG Proprietary-Contents may change without notice

This Document can not be used without Samsung's authorization

AT_nDTR

SGH-D730 Flow Chart of Troubleshooting and Circuit Diagrams

VDD_18D

VRTC

VCCD

VDD_18D

C411

7

1

R

VDD_18D

D

D

V

C410

VCCD

6

6

6

5

7

6

4

3

1

1

4

1

2

1

1

R

T

R

R

G

E

B

E

D

D

D

D

D

D

D

D

D

D

D

D

D

D

V

V

V

V

V

V

V

I

O

S

K

S

I

O

C

S

M

M

A

_

_

_

N

T

K

P

P

P

S

A

L

S

C

C

C

D

C

/

/

/

/

_

_

1

2

0

9

0

0

2

2

2

1

A

A

M

M

A

A

P

P

S

S

P

P

X

X

X

X

X

X

6

2

0

4

1

2

J

1

1

L

L

K

U

N

5

1

1

1

1

2

1

1

1

8

1

B

E

E

N

U

U

P

E

U

M

L

E

E

E

E

E

E

E

E

E

L

D

D

D

D

D

D

D

D

D

P

D

D

D

D

D

D

D

D

D

D

V

V

V

V

V

V

V

V

V

_

S

S

V

K

L

C

K

0

2

3

_

C

1

0

1

Q

M

M

A

M

M

R

M

_

W

W

S

O

O

T

D

P

P

B

_

_

/

1

_

/

_

_

T

7

6

3

5

4

8

7

M

2

2

S

2

2

2

1

1

A

A

A

A

A

W

A

A

R

P

P

F

P

P

P

P

P

P

X

X

X

X

X

X

X

X

X

2

4

6

5

4

5

3

3

4

7

1

1

F

E

H

H

R

G

G

M

P

N

6

0

1

1

F

G

L

L

P

D

_

D

D

V

A

Q

E

R

_

T

_

3

3

A

P

X

7

1

M

1

0

1

1

C

E

F

A

A

E

S

D

R

S

D

V

V

V

X

XCPTSTSTOP_CKO

B

Q

E

R

_

T

_

K

4

C

3

T

_

A

P

P

C

X

X

7

D

C407

C406

VREF

CLK13M_TR

TR_RST

2

7

1

8

1

F

C

D

I

B

C

K

T

T

C

S

R

R

V

F12

TDO

TRST

TDI

TMS

TCK

CKO

IOBIT#2

IOBIT#1

INT#0

IO7

RWN

AB#8

AB#7

AB#6

AB#5

AB#4

AB#3

AB#2

AB#1

AB#0

DB#15

DB#14

DB#13

DB#12

DB#11

DB#10

DB#9

DB#8

DB#7

DB#6

DB#5

DB#4

DB#3

DB#2

DB#1

DB#0

XTIC_MODE

XAG3

XAG2

XAG1

XAG0

XBSWN

X1RTC

X2RTC

XRTCALARM_N

XOSC32OUT

N

T

S

S

O

I

R

D

D

M

T

T

T

T

_

_

_

_

P

P

P

P

C

C

C

C

X

X

X

X

3

8

7

9

1

F

C

G

D

TP403

TP404

TP405

TP406

TP407

DSP_TDO

F15

H12

DSP_TDI

G12

DSP_TMS

H13

DSP_TCK

G15

L12

K11

N4

R12

U5

T17

DSP_AB(8)

T14

DSP_AB(7)

R14

DSP_AB(6)

P12

DSP_AB(5)

P11

DSP_AB(4)

N11

DSP_AB(3)

R13

DSP_AB(2)

M10

DSP_AB(1)

U13

DSP_AB(0)

P10

DSP_DB(15)

R11

DSP_DB(14)

T11

DSP_DB(13)

U11

DSP_DB(12)

M8

DSP_DB(11)

N8

DSP_DB(10)

N7

DSP_DB(9)

P7

DSP_DB(8)

M6

DSP_DB(7)

R7

DSP_DB(6)

T7

DSP_DB(5)

U7

DSP_DB(4)

P6

DSP_DB(3)

R6

DSP_DB(2)

U6

DSP_DB(1)

P5

DSP_DB(0)

D12

M12

D11

E11

A11

B11

B7

A7

D10

E8

C6

ARM_TDO

ARM_TRSTN

ARM_TDI

ARM_TMS

ARM_TCK

SW_RST_INT

BT_REQ

AT_nDSR

PH_ACTIVE

FLASH_RESET

SIMRST

UP_CS

UP_SCLK

UP_SDO

UP_SDI

PH_PWR_OFF

PWR_KEEP

ARM_TRSTN

R441

R407

DSP_INT

DSP_IO

DSP_AB(0:8)

DSP_DB(0:15)

VDD_30D

R410

RTC_nALARM

CLK32K

C422

SVC_BLUE

DSP_RWN

VCCB

U402

1

2

VO

VS

GND

R408

3

R404

BP_VF

TR_RST

OSC401

VBAT

R414

C424C423

R415

T

C

E

A6

B5

F8

F7

C5

D6

E7

D5

C4

B4

B3

C1

C2

D2

D3

E3

M9

T5

P2

N2

1

2

C

N

XCP_D0

XCP_D1

XCP_D2

XCP_D3

XCP_D4

XCP_D5

XCP_D6

XCP_D7

XCP_D8

XCP_D9

XCP_D10

XCP_D11

XCP_D12

XCP_D13

XCP_D14

XCP_D15

XCP_A0_BEON

XCP_A1

XCP_A2

XCP_A3

XCP_A4

XCP_A5

XCP_A6

XCP_A7

XCP_A8

XCP_A9

XCP_A10

XCP_A11

XCP_A12

XCP_A13

XCP_A14

XCP_A15

XCP_A16

XCP_A17

XCP_A18

XCP_A19

XCP_A20

XCP_A21

XCP_CSROMEN

XCP_CSRAMEN

XPA0/CS1N

XPA1/CS2N

XPA2/CS3N

XPA3/CS4N

XCP_WEN

XPA4/OEN

XPA5/WAITN

XPA6/BE1N

XPA7/IRQ1

XPA8/IRQ2

XPA9/IRQ3

XPA10/IRQ4

T

E

D

_

C

L

D

0

5

4

7

3

0

1

7

1

1

7

1

1

9

8

1

6

1

L

N

L

H

J

L

L

M

L

L

K

2

S

S

S

S

S

S

S

D

N

C

N

2

5

0

S

S

S

S

S

S

S

D

N

A

S

S

V

V

V

V

V

V

V

V

_

C

C

5

_

_

3

3

2

A

2

3

P

A

A

X

_

P

6

X

3

A

P

X

6

1

9

1

1

1

7

6

K

S

S

V

5

3

2

6

7

C

A

H

J

F

G

A

G

H

A

S

S

S

S

S

S

S

S

D

D

S

S

S

S

S

S

S

S

D

D

V

V

V

V

V

V

V

V

V

V

U400

3

1

0

4

2

T

T

T

T

T

0

N

I

S

/

0

B

K

_

P

C

X

5

4

L

L

X

3

2

1

4

X

U

U

U

U

U

T

R

N

N

N

N

O

O

O

O

I

O

I

I

I

S

S

S

S

S

S

S

S

S

/

/

/

/

/

/

/

/

/

9

2

7

8

6

5

4

1

3

B

B

B

B

B

B

B

B

B

K

K

K

K

K

K

K

K

K

_

_

_

_

_

_

_

_

_

P

P

P

P

P

P

P

P

P

C

C

C

C

C

C

C

C

C

X

X

X

X

X

X

X

X

X

4

4

3

3

3

3

1

2

T

T

T

P

N

U

R

M

0

1

A

A

D

D

R

R

I

I

/

/

2

1

1

1

A

A

P

P

X

X

1

5

K

N

1

1

0

0

1

M

M

0

X

X

X

X

O

O

M

M

I

I

T

R

I

I

T

R

_

_

_

/

/

_

_

_

8

9

3

5

6

4

0

1

2

2

1

1

1

1

3

3

A

A

A

A

A

A

A

A

P

P

P

P

P

P

P

P

X

X

X

X

X

X

X

X

5

1

4

3

3

1

6

3

L

F

F

E

H

G

G

G

A(22)

A(23)

D(0:15)

A(0:20)

A(21)

CP_CSROMEN

CP_CSRAMEN

R409

CP_CSROM2EN

CP_WEN

CP_OEN

UPPER_BYTE

CP_INT

JACK_SENSE

PH_WAKEUP

VCCD

R416

R440

PDA_WAKEUP

AT_nRTS

AT_nCTS

SDS_TXD

SDS_RXD

SIMDATA

AT_TXD

AT_RXD

SIMCLK

PH_OFF_nRDY

PDA_ACTIVE

R402

R403

D(0)

D(1)

D(2)

D(3)

D(4)

D(5)

D(6)

D(7)

D(8)

D(9)

D(10)

D(11)

D(12)

D(13)

D(14)

D(15)

B13

A(0)

F11

A(1)

E14

A(2)

D15

A(3)

B15

A(4)

C14

A(5)

A16

A(6)

A15

A(7)

B17

A(8)

C17

A(9)

D16

A(10)

F14

A(11)

G14

A(12)

G13

A(13)

G17

A(14)

J12

A(15)

K12

A(16)

K13

A(17)

K14

A(18)

L14

A(19)

L15

A(20)

L16

A12

A13

M15

M14

M11

N14

C13

P16

P15

T15

R413

2-7

SAMSUNG Proprietary-Contents may change without notice

This Document can not be used without Samsung's authorization

SGH-D730 Flow Chart of Troubleshooting and Circuit Diagrams

D

S

P

_

A

B

(

0

:

8

F

T

L

X

A

_

P

S

B

C

D

H

A

S

N

S

S

S

E

E

D

Y

S

T

R

R

_

N

E

X

S

D

C

R

_

_

E

E

E

L

A

L

L

K

N

E

N

T

T

R

R

R

R

T

T

T

T

X

X

X

X

_

_

_

_

I

I

Q

Q

N

P

N

P

PATUOA

NATUOA

PNICIM

NNICIM

PTUOCIM

NTUOCIM

KCIAD

NRIAD

IDIAD

ODIAD

K23KLC

CM_M31KLC

TNI_PSD

NO_GIJ

3

2

Q

5

0

0

X

P

O

W

A

E

F

R

C

S

E

R

C

K

9D

C

5

1

9

C

5

2

0

R

5

0

1

CFA

7E

PXT

5B

2FERAR

6B

1FERAR

7D

PIXTXR

6D

NIXTXR

7C

PQXTXR

6C

NQXTXR

11P

PATUOA

21N

NATUOA

21R

PBTUOA

21P

NBTUOA

41N

PNICIM

41M

NNICIM

51N

PTUOCIM

51P

TUOCIM

N

51M

PNIXUA

41L

NNIXUA

31K

31L

31R

MCVXV

31M

PGERV

41R

NGERV

4R

KCIAD

4P

NRIAD

6L

IDIAD

6M

ODIAD

4N

KLC_CTR

1D

QANEOX

6R

CM

5P

7CN

3P

RTNID

41C

51C

7L

9K

O_TESER

01N

EDOM

9M

01L

QRTNI

R

9L

T

C

_

A

L

M

N

C

5

1

8

G

C

C

B

B

A

A

1

3

2

3

1

2

6

S

S

S

O

O

O

E

E

E

C

C

C

R

R

R

T

T

T

D

L

L

L

L

L

E

E

7

6

5

A

1

2

PTUOXUA

NTUOXUA

2WS_RWP

N1WS_RWP

FUB_1WSP

PEEK_RWP

A

A

D

D

NE_GNR_BIV

C

C

C

C

H

H

_

_

_

A

A

C

V

_

I

U

U

S

R

R

R

E

X

X

E

E

E

N

1

2

S

F

F

A

H

F

E

D

E

D

1

1

1

9

1

1

1

2

0

0

0

4

5

S

_

_

D

P

R

R

_

S

E

X

R

P

S

_

W

_

E

E

I

T

N

O

N

D

D

D

S

S

S

P

P

P

_

_

_

A

A

A

B

B

B

(

(

(

1

0

2

)

)

)

A

E

4

5

O

O

C

C

T

T

L

L

4

3

C

H

_

B

V

V

D

B

E

R

A

X

V

T

T

E

E

1

1

3

1

K

C

R

P

E

L

L

L

F

6

5

2

3

1

6

5

5

3

A

A

R

O

A

I

O

R

O

|

O

B

B

B

E

W

C

C

C

1

2

0

S

T

T

T

N

E

L

L

L

0

2

1

T

N

_

C

S

P

S

S

C

C

S

D

S

L

V

V

D

K

O

N

L

L

I

V

_

D

D

_

_

_

P

A

P

P

P

O

O

S

C

S

S

S

_

_

C

C

C

C

C

2

1

J

G

M

L

F

E

N

K

1

8

1

1

8

7

1

7

2

4

4

R

5

2

0

1

1

T

C

P

P

H

H

_

_

P

P

W

W

R

R

_

_

O

O

N

F

F

C

P

W

P

P

_

_

R

I

R

N

_

S

K

T

T

E

E

P

P

5

0

0

R

V

R

T

C

E

_

F

n

A

L

A

R

M

U

P

_

C

S

U

U

U

P

P

P

_

_

_

S

S

S

D

D

C

O

I

L

K

V

B

A

T

V

C

C

R

D

5

2

2

C

5

2

3

C

5

1

5

C

5

1

2

C

5

1

3

C

5

1

6

C

5

1

7

)

D

D

D

D

D

D

S

S

S

S

S

S

P

P

P

P

P

P

_

_

_

_

_

_

A

A

A

A

A

A

B

B

B

B

B

B

(

(

(

(

(

(

8

7

6

5

4

3

)

)

)

)

)

)

D

D

D

S

S

S

P

P

P

_

_

_

D

D

D

B

B

B

(

(

(

0

1

2

)

)

)

M

M

N

N

K

K

K

K

2

1

7

5

2

1

1

2

A

A

D

A

A

D

D

A

A

B

B

B

B

B

B

B

B

3

V

L

D

O

_

3

A

1

3

B

4

5

6

7

8

0

1

2

U

5

0

0

V

V

V

V

V

V

V

V

L

L

L

L

L

L

L

L

D

D

D

D

5

5

4

4

S

S

S

S

O

O

O

O

_

_

_

_

_

_

_

_

B

A

A

B

6

7

4

5

A

C

D

A

B

B

B

1

1

1

1

1

9

1

4

2

2

1

0

0

D

G

C

S

S

M

_

_

T

T

X

X

_

_

E

E

N

N

D

S

P

_

D

B

(

0

:

1

5

)

D

D

D

D

D

D

D

D

D

D

S

S

S

S

S

P

P

P

P

P

_

_

_

_

_

D

D

D

D

D

B

B

B

B

B

(

(

(

(

(

7

6

5

4

3

)

)

)

)

)

G

G

K

H

J

J

3

5

6

4

3

5

D

D

D

D

D

B

B

B

B

B

3

4

7

6

5

L

L

R

E

E

I

V

N

D

D

I

G

B

1

2

_

_

_

_

V

D

D

D

D

R

R

R

R

R

T

V

V

V

V

C

C

F

F

G

H

G

1

1

1

1

1

1

3

5

2

1

2

3

V

R

F

V

C

C

D

C

5

1

1

N

P

E

O

G

S

1

2

M

R

B

5

0

4

0

1

4

_

I

V

0

2

N

D

D

D

S

S

S

S

S

S

S

S

P

P

P

P

P

P

P

P

_

_

_

_

_

_

_

_

D

D

D

D

D

D

D

D

B

B

B

B

B

B

B

B

(

(

(

(

(

(

(

(

1

9

1

8

1

1

1

1

2

)

1

)

0

5

4

3

)

)

)

)

)

)

D

D

E

E

F

F

F

F

4

2

1

3

2

3

2

3

D

D

D

D

D

D

D

D

B

B

B

B

B

B

B

B

8

1

9

1

1

1

1

1

2

1

3

4

5

0

S

S

I

I

M

M

S

I

_

_

M

V

C

R

S

_

L

S

I

I

M

K

O

T

K

K

K

J

1

1

1

1

1

1

2

4

V

C

C

B

V

C

C

A

2

6CN

1

5CN

01K

71SDNG

01J

61SDNG

9J

51SDNG

8J

41SDNG

7J

31SDNG

9H

21SDNG

8H

11SDNG

7H

01SDNG

6H

9SDNG

01G

8SDNG

9G

7SDNG

8G

6SDNG

7G

5SDNG

01F

4SDNG

9F

3SDNG

8F

2SDNG

7F

1SDNG

31D

3CDA_XU

A

4B

LTCO_DNG

4C

LTCO_DDV

31P

VDNG

11L

VDDV

6F

BDNG

6A

BDDV

01M

DDNG

11N

DDDV

6P

4SSV

2R

3SSV

4K

2SSV

5G

1SSV

4J

2OI_DDV

5N

1OI_DDV

6N

3DDV

3M

2DDV

3J

1DDV

11F

RUCH_DNG

51K

2CSP_DNG

51B

1CSP_DNG

8E

QDNG

31B

76DDV

01C

5DDV

U

U

P

P

V

V

U

_

_

D

D

P

C

R

D

D

_

L

S

3

1

I

K

O

T

4

2

C

J

R

P

N

1

1

1

3

1

9

1

0

0

S

S

I

I

M

M

S

C

R

I

M

L

S

K

T

D

A

T

A

C

5

1

0

C

5

0

9

C

5

0

8

C

5

0

7

V

R

T

C

205R

C

5

0

4

V

C

C

D

V

C

C

A

C

5

0

0

V

C

C

D

C

5

0

1

V

B

A

C

5

0

3

C

5

0

2

C

5

0

6

1

0

N

1

0

C

1

2

N

9

1

C

1

9

T

8

2

4

6

C

8

2

4

6

N

5

0

7

1

3

5

0

7

1

3

5

2-8

SAMSUNG Proprietary-Contents may change without notice

This Document can not be used without Samsung's authorization

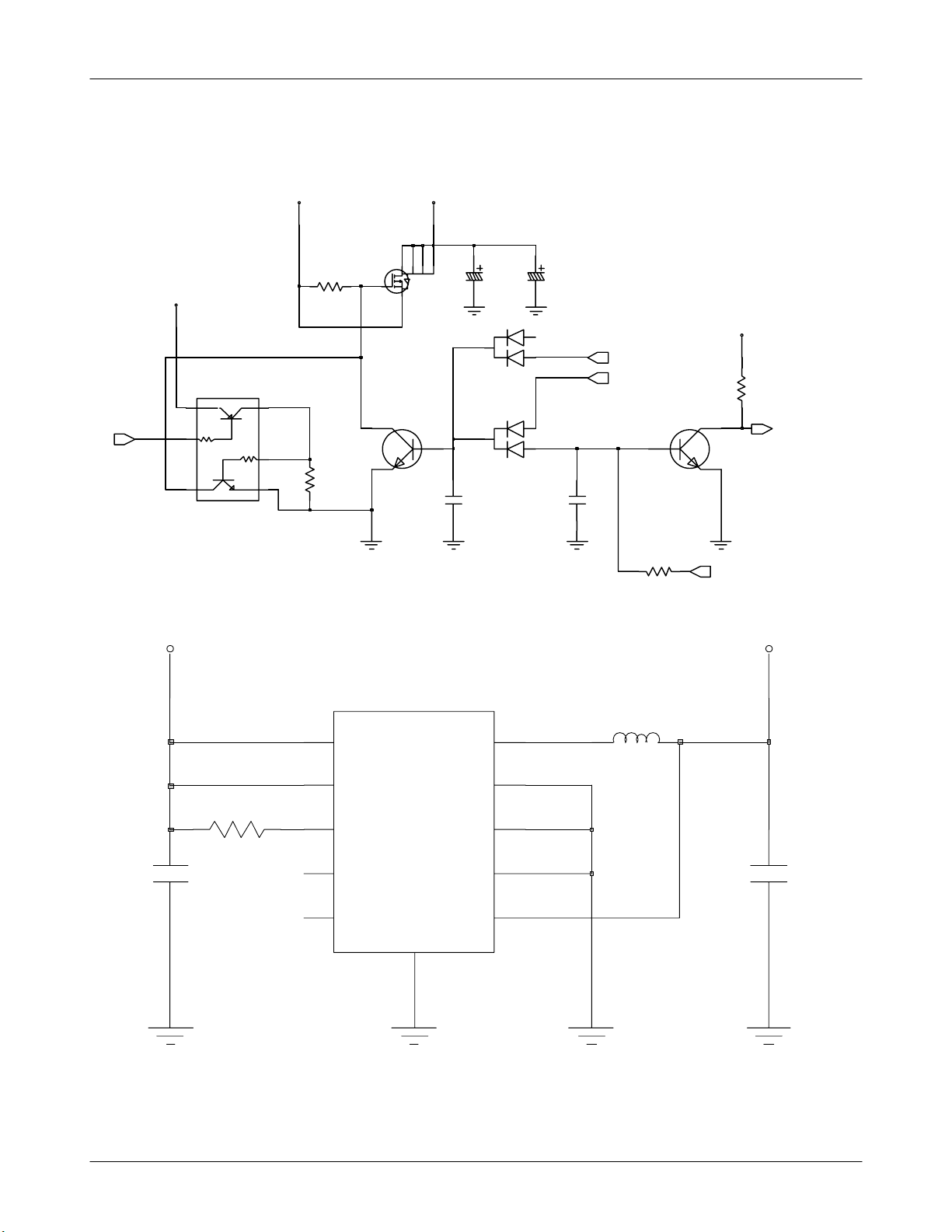

SGH-D730 Flow Chart of Troubleshooting and Circuit Diagrams

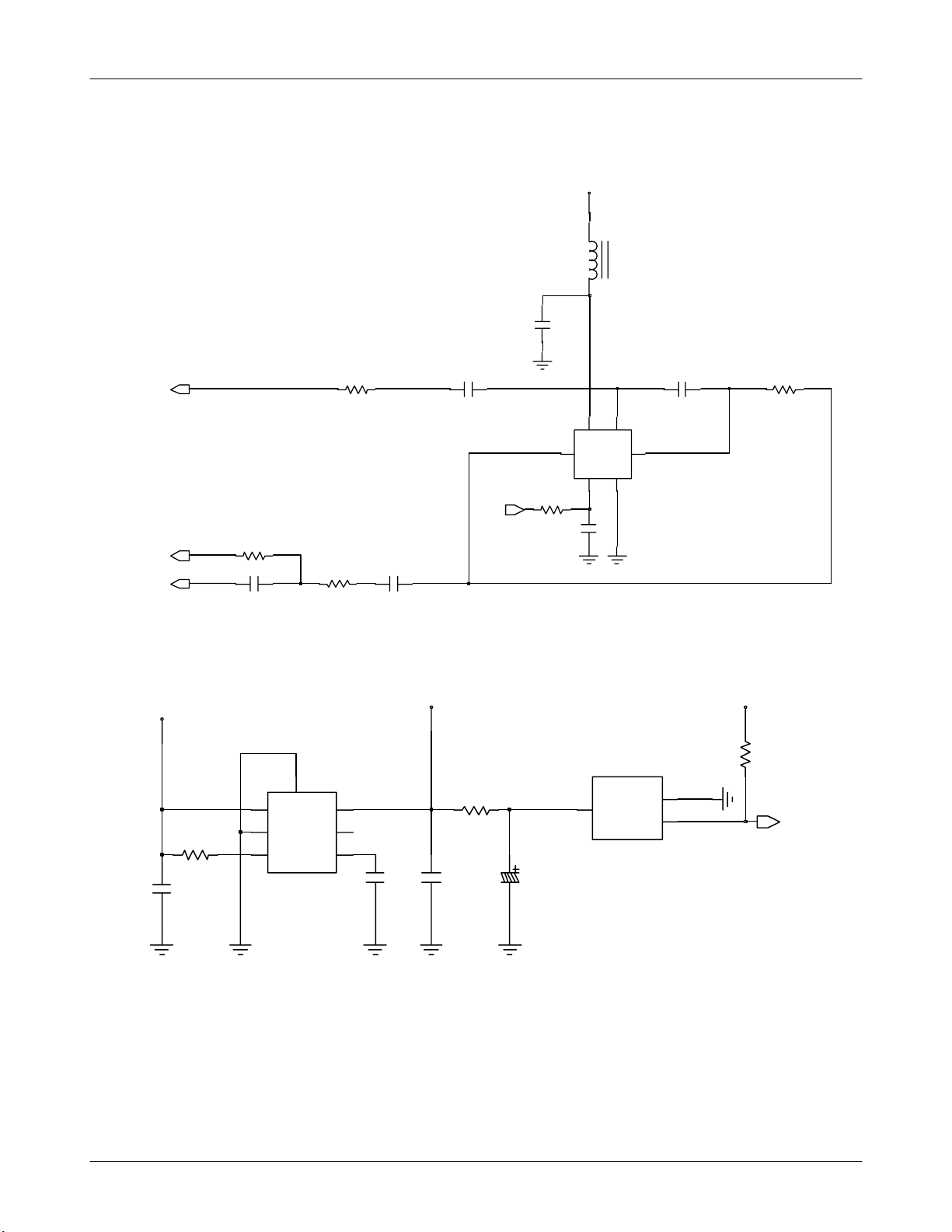

VRF

L400

C405

CLK13M_RF

CLK13M_TR

CLK13M_MC

C319

V_IN

R302

R405

C418

5

OSC400

GND

VOUT

C409

R401

VDD_30D

R383

1

2

OHP_nRESET

C408

AFC

R439

C417

6

VCC

VCONT

1

34

OUT

BUFFINBUFFOUT

2

GND

R406

R400

C419

VDD_30D

U301

7

D

N

G

IN

3

GND

2

EN

OUT

BYP

4

NC

5

61

C317

U308

C318

R325

C310

3

VDD

2-9

SAMSUNG Proprietary-Contents may change without notice

This Document can not be used without Samsung's authorization

SGH-D730 Flow Chart of Troubleshooting and Circuit Diagrams

2-1-3. Sim Part

Phone can't access

SIM card

Check the pin 3 of

CN500

Voltage = 3V

YES

NO

①

Check the circuit related to

U500

Check the SIM

connector's

(CN500)

connector's to SIM

card

YES

Check the circuit around CN500

input circuitry

YES

Check the circuit around

U500 output

and voltage supply circuitry

YES

END

NO

NO

NO

②

resolder or change

CN500

③

Check the related circuit of

CN500

④

Check the related circuit of

U500

②

③

④

①

2-10

SAMSUNG Proprietary-Contents may change without notice

This Document can not be used without Samsung's authorization

2-1-4. Charging Part

Abnormal charging part

Check the pin 23,24 of

CN301 is Vbat

YES

Check the pin 8 of

CN301

is GND

YES

END

SGH-D730 Flow Chart of Troubleshooting and Circuit Diagrams

①

NO

Check CN301

②

NO

Check CN301

①

②

2-10

This Document can not be used without Samsung's authorization

SGH-D730 Flow Chart of Troubleshooting and Circuit Diagrams

VDD_30D

VDD_30D

R303

R304

DEBUG_TXD

DEBUG_RXD

JIG_ON

SDS_TXD

SDS_RXD

OMAP_TRST

OMAP_TDO

OMAP_TDI

OMAP_TCK

OMAP_TMS

USB_DP

USB_DM

PUEN

U300

1

DXIN

2

GND5VBUS

34

DYIN

DXOUT

DYOUT

6

DLC_DETECT

OMAP_RTCK

ZD306

1

2

0

3

V

7

2

8

3

VDD_USB

VBAT

C301

CN301

1

1

2

R376

R377

R367

R368

R369

R370

R371

R372

R373

R374

R375

JIG_ON

SDS_TXD

SDS_RXD

BATTERY_ID

OMAP_TRST

OMAP_TDO

OMAP_TDI

OMAP_TCK

OMAP_TMS

DLC_DETECT

R381

USB_5V

USB_D+

USB_DVBAT

6

VBAT

5

4

ZD304

ZD302

C302

DEBUG_TXD

DEBUG_RXD

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

2-12

SAMSUNG Proprietary-Contents may change without notice

This Document can not be used without Samsung's authorization

Loading...

Loading...